Cadence Allegro

Cadence应用如何在allegro中使用skill

Cadence应⽤如何在allegro中使⽤skillCadence软件应⽤:如何在Allegro中执⾏SkillHow to Perform Skills in Allegro ToolsDoc Scope : Allegro SkillDoc Number : SFTEC11005Author : Daniel ZhongCreate Date : 2011-11-09Rev : 1.00⽬录1Skill简介 (3)2在Allegro命令⾏中加载和调⽤Skill (3)2.1命令⾏加载Skill (3)2.2命令⾏调⽤Skill (4)3在Allegro启动时加载Skill (5)3.1allegro.ilinit⽂件 (5)3.2编辑allegro.ilinit (7)4在Allegro菜单栏上调⽤Skill (8)4.1Allegro系列⼯具的菜单⽂件(.men) (8)4.2菜单⽂件搜索路径 (10)4.3定制菜单 (11)1Skill简介Skill是Allegro软件⼆次开发的接⼝,⽤此语⾔编译的⽂件可以在Allegro中载⼊和调⽤。

我们可以通过编写不同的Skill程序⽂件,在Allegro⼯具中实现各种原有命令不能实现或不⽅便实现的功能。

Skill语⾔的语法结构和C++语⾔类似,⼯程师如果有⼀定C语⾔编程基础,使⽤Skill语⾔时就会很⽅便了。

对于Skill程序的⽤户,不需要对Skill语⾔有过多的了解,只需要知道如何在Allegro中加载和调⽤Skill即可,本⽂就是介绍了如何加载和调⽤Skill,可以采⽤两种⽅式:■在Allegro命令⾏中加载和调⽤■在Allegro启动⾃动加载,在Allegro菜单上调⽤2在Allegro命令⾏中加载和调⽤Skill本章介绍如何在Allegro命令⾏中加载和调⽤Skill,分为以下两个⼩节:■命令⾏加载Skill■命令⾏调⽤Skill2.1命令⾏加载Skill以本站资源下载中的⼀个skill程序clinecut.il为例,将此⽂件移动或复制allegro设计⽂件(.brd)所在⽬录。

Cadence Allegro OrCAD V16.5 安装步骤

Cadence Allegro / OrCAD V16.5安装步骤步骤一:安装License Server - (Server端)安装前注意事项 :1. 请确认所登入的帐号拥有本机完整的Administrator管理者的权限,若是安装在 Vista或 Win 7 作业系统中,请先将使用者帐户控制设定( UAC ) 调降至最低。

2. 请将以安装在作业系统中的防毒软体及防火墙暂时关闭,以免干扰安装作业。

3. 如果所购买的软体版本或 License 有需要加挂DongleKey认证※※※请务必先安装License Server/驱动程式再插上Dongle Key※※Í USB 硬体锁Í Parallel Port硬体锁Note01:Allegro V16.5支援作业平台.Windows 2008 R2 Server; Windows XP Professional SP3.Windows Vista (32 and 64 bit) , Starter 和 Home Basic 除外.Windows 7 (32 and 64 bit) (Home Premium, Professional, Enterprise, and Ultimate)**Windows Vista及 Windows 7 作业系统不支援 FLEXid 8 黑色Print Port KEYNote02:Allegro/OrCAD V16.5不支援 Windows NT 及Windows 2000 及Windows XP Home EditionNote03:Allegro/OrCAD V16.5 不支援IPF chip ( Intel Itanium 64-bit ) ,HP PA RISCNote04:在Windows server不能以 Windows Remote Desktop(类似终端机 terminal services)的方式执行Note05 : 电脑名称不允许使用中文名称◆伺服器端的授权伺服器安装【Step A1】﹕将Allegro / OrCAD V16.5 版的安装光碟放进DVD光碟机中,系统会自动执行操作介面(如果没有自动执行,则可直接对DVD光碟中执行setup.exe后),进入安装主画面,如下图所示。

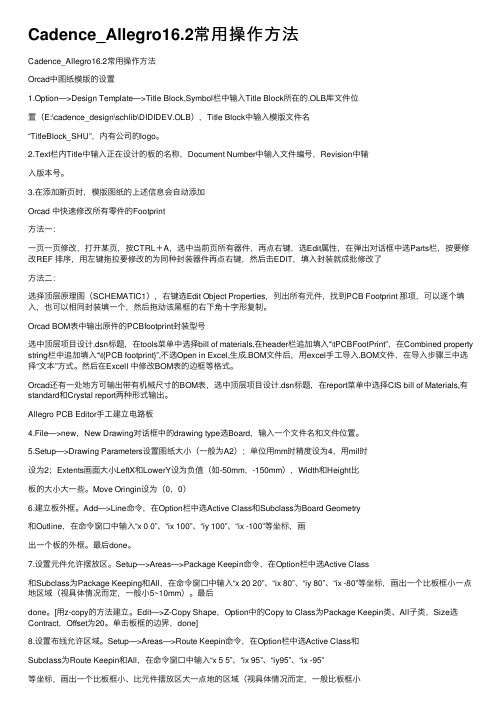

Cadence_Allegro16.2常用操作方法

Cadence_Allegro16.2常⽤操作⽅法Cadence_Allegro16.2常⽤操作⽅法Orcad中图纸模版的设置1.Option—>Design Template—>Title Block,Symbol栏中输⼊Title Block所在的.OLB库⽂件位置(E:\cadence_design\schlib\DIDIDEV.OLB),Title Block中输⼊模版⽂件名“TitleBlock_SHU”,内有公司的logo。

2.Text栏内Title中输⼊正在设计的板的名称,Document Number中输⼊⽂件编号,Revision中输⼊版本号。

3.在添加新页时,模版图纸的上述信息会⾃动添加Orcad 中快速修改所有零件的Footprint⽅法⼀:⼀页⼀页修改,打开某页,按CTRL+A,选中当前页所有器件,再点右键,选Edit属性,在弹出对话框中选Parts栏,按要修改REF 排序,⽤左键拖拉要修改的为同种封装器件再点右键,然后击EDIT,填⼊封装就成批修改了⽅法⼆:选择顶层原理图(SCHEMATIC1),右键选Edit Object Properties,列出所有元件,找到PCB Footprint 那项,可以逐个填⼊,也可以相同封装填⼀个,然后拖动该⿊框的右下⾓⼗字形复制。

Orcad BOM表中输出原件的PCBfootprint封装型号选中顶层项⽬设计.dsn标题,在tools菜单中选择bill of materials,在header栏追加填⼊“\tPCBFootPrint”,在Combined property string栏中追加填⼊“\t{PCB footprint}”,不选Open in Excel,⽣成.BOM⽂件后,⽤excel⼿⼯导⼊.BOM⽂件,在导⼊步骤三中选择“⽂本”⽅式。

然后在Excell 中修改BOM表的边框等格式。

Orcad还有⼀处地⽅可输出带有机械尺⼨的BOM表,选中顶层项⽬设计.dsn标题,在report菜单中选择CIS bill of Materials,有standard和Crystal report两种形式输出。

CadenceAllegro16.5详细教程ppt课件

Load logic data

Manufacturin g outputs check plots aperture files Gerber data NC drill data silkscreens Assembly drawings fabrications drawings reports Autorename backannotatio n

4

主要产品介绍

为了适应不同用户的需要,Cadence软件包中提供了Allegro PCB

Designer、OrCAD PCB Designer Standard和OrCAD PCB Designer Professional 3种PCB设计软件版本。 (1)Allegro PCB Designer:是应用最广泛的一种版本。产品由Base模 块和Option附加模块组成,通过一个完全集成式的设计流程进行PCB Layout设计。 (2)OrCAD PCB Designer:分为Professional和Standard版本,与 Allegro PCB Designer相比,不具有电气约束驱动规则( Professional 版本只有差分约束规则)、DFX检查、不允许修改电气拓扑结构、没 有扩展的Option功能、自动布线器最多支持到6层。

2

Lesson1 Allegro 环境介绍

学习要点: PCB Layout流程介绍 PCB设计主要产品介绍 工作界面介绍 视窗缩放控制介绍 鼠标Stroke功能介绍 主要文件类型

3

PCB Layout流程

HDL/schemat ic design capture Define board mechanical stackup Set/check CBD rules and constraints

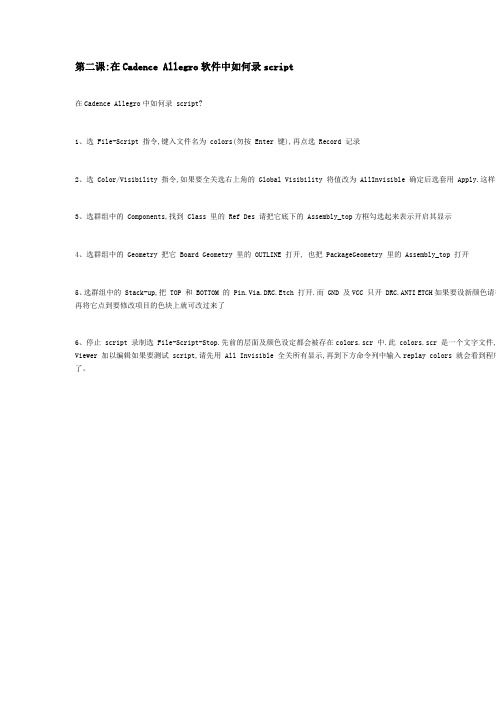

在Cadence Allegro软件中如何录script

第二课:在Cadence Allegro软件中如何录script

在Cadence Allegro中如何录 script?

1、选 File-Script 指令,键入文件名为 colors(勿按 Enter 键),再点选 Record 记录

2、选 Color/Visibility 指令,如果要全关选右上角的 Global Visibility 将值改为 AllInvisible 确定后选套用 Apply.这样会

3、选群组中的 Components,找到 Class 里的 Ref Des 请把它底下的 Assembly_top方框勾选起来表示开启其显示

4、选群组中的 Geometry 把它 Board Geometry 里的 OUTLINE 打开, 也把 PackageGeometry 里的 Assembly_top 打开

5、选群组中的 Stack-up,把 TOP 和 BOTTOM 的 Pin.Via.DRC.Etch 打开.而 GND 及VCC 只开 DRC.ANTI ETCH如果要设新颜色请在再将它点到要修改项目的色块上就可改过来了

6、停止 script 录制选 File-Script-Stop.先前的层面及颜色设定都会被存在colors.scr 中.此 colors.scr 是一个文字文件, Viewer 加以编辑如果要测试 script,请先用 All Invisible 全关所有显示,再到下方命令列中输入replay colors 就会看到程序了。

Cadence Allegro教程-17个步骤

Allegro教程-17个步骤Allegro® 是Cadence 推出的先进 PCB 设计布线工具。

Allegro 提供了良好且交互的工作接口和强大完善的功能,和它前端产品Cadence® OrCAD® Capture 的结合,为当前高速、高密度、多层的复杂 PCB 设计布线提供了最完美解决方案。

Allegro 拥有完善的 Constraint 设定,用户只须按要求设定好布线规则,在布线时不违反 DRC 就可以达到布线的设计要求,从而节约了烦琐的人工检查时间,提高了工作效率!更能够定义最小线宽或线长等参数以符合当今高速电路板布线的种种需求。

软件中的 Constraint Manger 提供了简洁明了的接口方便使用者设定和查看 Constraint 宣告。

它与 Capture 的结合让 E.E. 电子工程师在绘制线路图时就能设定好规则数据,并能一起带到Allegro工作环境中,自动在摆零件及布线时依照规则处理及检查,而这些规则数据的经验值均可重复使用在相同性质的电路板设计上。

Allegro 除了上述的功能外,其强大的自动推挤 push 和贴线 hug 走线以及完善的自动修线功能更是给用户提供极大的方便;强大的贴图功能,可以提供多用户同时处理一块复杂板子,从而大大地提高了工作效率。

或是利用选购的切图功能将电路版切分成各个区块,让每个区块各有专职的人同时进行设计,达到同份图多人同时设计并能缩短时程的目的。

用户在布线时做过更名、联机互换以及修改逻辑后,可以非常方便地回编到 Capture 线路图中,线路图修改后也可以非常方便地更新到 Allegro 中;用户还可以在 Capture 与 Allegro 之间对对象的互相点选及修改。

对于业界所重视的铜箔的绘制和修改功能, Allegro 提供了简单方便的内层分割功能,以及能够对正负片内层的检阅。

对于铺铜也可分动态铜或是静态铜,以作为铺大地或是走大电流之不同应用。

(完整word版)Cadence allegro菜单解释

Cadence allegro菜单解释-—file已有 320 次阅读 2009—8-16 19:17 |个人分类:工作|关键词:Cadence allegro file 菜单解释每一款软件几乎都有File菜单,接下来详细解释一下allegro与其他软件不同的菜单。

new新建PCB文件,点new菜单进入对话框后,drawing type里面包含有9个选项,一般我们如果设计PCB就选择默认第一个board即可。

如果我们要建封装库选package symbol即可,其他7个选项一般很少用,大家可以理解字面意思就可以知道什么意思了。

open打开你所要设计的 PCB文件,或者封装库文件。

recent designs打开你所设计的PCB文件,一般是指近期所设计的或者打开过的PCB文件。

save保存save as另存为,重命名。

importimport 菜单包含许多项,下面详细解释一下我们经常用到的命令。

logic 导入网表,详细介绍在allegro基础教程连载已经有介绍,在此不再详细介绍。

artwork 导入从其他PCB文件导出的。

art的文件。

一般很少用词命令。

命令IPF和stream 很少用,略。

DXF 导入结构要素图或者其他DXF的文件。

导入方法如下:点import/DXF后,在弹出的对话框选择,在DXF file里选择你要导入的DXF的路径,DXF units 选择MM,然后勾选use default text table和incremental addition,其他默认即可.再点edit/view layers弹出对话框,勾选select all,DXF layer filter选择all,即为导入所有层的信息,然后在下面的class里选择board geometry,subclass选择assembly_notes,因为一般导入结构要素图都是导入这一层,然后点ok,进入了点import/DXF后弹出的对话框,然后点import即可将结构要素图导入.IDF IFF Router PCAD 这四个命令也很少用,略。

Cadence Allegro SPB简介与安装方法

Cadence Allegro SPB 简介与安装方法Cadence 新一代的Cadence 15.5系统互连设计平台优化并加速了高性能高密度的互连设计。

Cadence Allegro 平台所需的关键技术,以建立从IC 制造、封装和PCB 的一整套完整设计流程。

Cadence Allegro 可提供新一代的协同设计方法,以便建立跨越整个设计链 ——包括I/O 缓冲区、IC 、封装及PCB 设计人员的合作关系。

Cadence 公司著名的软件有:Cadence Allegro ;Cadence LDV ;Cadence IC5.0;Cadence orCAD 等。

功能强大的布局布线设计工具——Allegro PCB ,它是业界领先的PCB 设计系统。

Allegro PCB 是一个交互的环境,用于建立和编辑复杂的、多层印制电路板。

Allegro PCB 丰富的功能将满足当今世界设计和制造的需求。

针对目标按时完成系统协同设计,Cadence Allegro 平台使能协同设计高性能的集成电路、封装和印制电路板的互连,降低成本并加快产品上市时间。

Cadence Allegro 系统互连平台能够跨集成电路、封装和PCB 协同设计高性能互连。

应用平台的协同设计方法,工程师可以迅速优化I/O 缓冲器之间和跨集成电路、封装和PCB 的系统互联。

该方法能避免硬件返工并降低硬件成本和缩短设计周期。

约束驱动的Allegro 流程包括高级功能用于设计捕捉、信号完整性和物理实现。

由于它还得到Cadence Encounter 与Virtuoso 平台的支持,Allegro 协同设计方法使得高效的设计链协同成为现实。

CADENCE PSD 14.1安装方法1. 建立C:\CadenceLM 目录,将光盘Crack 中的所有文件Copy 到该目录;2. 运行Cadence_PSD.exe ,选中“FlexLM Server”,点击“Generate”生成License.dat 文件,在该目录下可以看到;3. 运行光盘setup.exe 安装,选“NetWork Licensing”安装;4. 安装License Manager ,需要license 文件的时候,把路径指到C:\CadenceLM ,5. 安装完成,重新启动6. 打开控制面板,打开FlexLM ,激活服务器,在Status 项可以看到服务是否启动7. 再次运行光盘setup.exe 安装,选“NetWork Licensing”安装;8. Install Products,选择你需要的选项进行安装,询问License 的时候把路径指到C:\CadenceLM ;9. 安装完成,重启动即可使用!!Cadence 14.2 安装方法(详解)1. 在C 盘根目录创建Cadence 文件夹,再在其中创建License_manager 文件夹, 把license.dat 文件拷贝到License_manager 文件夹中,并编辑它的第一行: SERVER your computer name ANY 270012. 打开“控制面板”--“系统”--“高级”--环境变量,新建用户环境变量,变量名LM_LICENSE_FILE ,变量值27001 your computer name3. 运行CD1的Setup.exe4. 选择Network Licensing5. 选择License Manager 安装6. 然后会出现错误窗口,不用管它。

Cadence.Allegro.SPB.v16.2破解及安装步骤(已验证可行)

Cadence.Allegro.SPB.v16.2破解及安装步骤(已验证可行)严正声明:该破解及安装方法仅用于交流学习该软件,请不要以任何形式用于商业目的,本人不承担任何由个人或企业将此软件用于商业目的而引发的一切法律纠纷所带来后果,如需用于商业目的,请向Cadence 公司购买授权;否则后果自负。

从上一年到现在,一共安装了Cadence.Allegro.SPB.v16.2四次,非常痛惜,由于种种原因,前三次都以失败而告终,通过网上的安装经验及自己的摸索,功夫不负有心人,终于在今天下午将Candence Allego SPB16.2安装成功。

现把安装经验及注意事项分享如下:1.简介Cadence? Allegro是 Cadence 推出的先进 PCB 设计布线工具。

Allegro 提供了良好且交互的工作接口和强大完善的功能,和它前端产品 Capture 的结合,为当前高速、高密度、多层的复杂 PCB 设计布线提供了最完美解决方案。

Allegro 拥有完善的 Constraint 设定,用户只须按要求设定好布线规则,在布线时不违反 DRC 就可以达到布线的设计要求,从而节约了烦琐的人工检查时间,提高了工作效率!更能够定义最小线宽或线长等参数以符合当今高速电路板布线的种种需求。

2. 安装及破解步骤步骤:一、下载好所需的安装光盘镜像文件,VeryCD网站上有有两个版本,一个是ISO 文件(共有3个ISO文件,占用空间1630MB左右);另个版本是两个BIN文件(占用空间1.10GB左右),本人所用的是第二个版本。

二、将上述文件(两个版本都可以)加载到虚拟光驱中,并打开,运行setup.exe 文件。

三、点击setup 进入安装界面,首先点击Licence Manger.如图所示:四、在首次安装LICENSE MANAGER的时候,安装程序会要求给出LICENSE FILE LOCATION,不要填任何东西,直接点击CANCLE结束这个对话框,如下图所示:五、将LICENSE.DAT复制到CADENCE文件夹中,然后用记事本打开它,将this_host改成你的计算机名称,并保存;六、查看计算机名称,如下图所示,我的计算机名称是 WWW-97F34E33509,而不是 WWW-97F34E33509. 就是说名称不包含末尾的句号!七、将cdslmd.exe复制到刚刚安装的LICENSE MANAGER文件夹中,覆盖原有的相同程序。

Cadence Allegro 16.3和PADS 9.2冲突解决办法

记事本格式Cadence Allegro 16.3和PADS 9.2冲突解决办法。

问题现象:如果同时安装Cadence Allegro/Orcad 16.3和PADS 9.2后,运行“Design Entry CIS”都提示找不到msvcr90.dll。

解决这种冲突问题的方法如下:这个是环境变量path引起的。

先装PADS 9.2后装Cadence Allegro/Orcad 16.3会导致启动路径默认为Mentor的文件路径,将系统环境变量下面的系统变量path中mentor相关的都调整到后面就可以了。

修改后PTCH路径:%CDSROOT%\tools\bin;%CDSROOT%\tools\libutil\bin;%CDSROOT%\tools\fet\bin;%CDSRO OT%\tools\pcb\bin;%CDSROOT%\tools\specctra\bin;%CDSROOT%\tools\PSpice;%CDSROOT %\tools\PSpice\Library;%CDSROOT%\tools\Capture;%CDSROOT%\OpenAccess\bin\win32\ opt;C:\MentorGraphics\9.2PADS\SDD_HOME\common\win32\bin;C:\MentorGraphics\9.2P ADS\SDD_HOME\common\win32\lib;C:\Program Files\Common Files\MicrosoftShared\Windows Live;C:\Program Files (x86)\Common Files\Microsoft Shared\Windows Live;C:\Program Files (x86)\Intel\iCLS Client\;C:\Program Files\Intel\iCLS Client\;%SystemRoot%\system32;%SystemRoot%;%SystemRoot%\System32\Wbem;%SYSTEMR OOT%\System32\WindowsPowerShell\v1.0\;C:\ProgramFiles\Intel\WiFi\bin\;C:\Program Files\CommonFiles\Intel\WirelessCommon\;C:\Program Files\ThinkPad\BluetoothSoftware\;C:\Program Files\ThinkPad\Bluetooth Software\syswow64;C:\Program Files\Intel\Intel(R) Management Engine Components\DAL;C:\ProgramFiles\Intel\Intel(R) Management Engine Components\IPT;C:\Program Files(x86)\Intel\Intel(R) Management Engine Components\DAL;C:\Program Files(x86)\Intel\Intel(R) Management Engine Components\IPT;C:\Program Files(x86)\Intel\OpenCL SDK\2.0\bin\x86;C:\Program Files (x86)\Intel\OpenCLSDK\2.0\bin\x64;C:\Program Files\Common Files\Lenovo;C:\Program Files(x86)\Common Files\Ulead Systems\MPEG;C:\Program Files (x86)\WindowsLive\Shared;C:\SWTOOLS\ReadyApps;C:\Program Files (x86)\Symantec\VIP Access Client\;C:\Program Files (x86)\CommonFiles\Lenovo;%MGC_HOME%/bin;%MGC_HOME%/lib;%MGC_HOMEBS%\bin;%MGC_HOMEBS%\lib修改前PTCH路径:C:\MentorGraphics\9.2PADS\SDD_HOME\common\win32\bin;C:\MentorGraphics\9.2PADS\SDD_HOME\common\win32\lib;C:\Program Files\Common Files\Microsoft Shared\Windows Live;C:\Program Files (x86)\Common Files\Microsoft Shared\Windows Live;C:\Program Files (x86)\Intel\iCLS Client\;C:\Program Files\Intel\iCLSClient\;%SystemRoot%\system32;%SystemRoot%;%SystemRoot%\System32\Wbem;%SYSTEMR OOT%\System32\WindowsPowerShell\v1.0\;C:\ProgramFiles\Intel\WiFi\bin\;C:\Program Files\CommonFiles\Intel\WirelessCommon\;C:\Program Files\ThinkPad\BluetoothSoftware\;C:\Program Files\ThinkPad\Bluetooth Software\syswow64;C:\Program Files\Intel\Intel(R) Management Engine Components\DAL;C:\ProgramFiles\Intel\Intel(R) Management Engine Components\IPT;C:\Program Files(x86)\Intel\Intel(R) Management Engine Components\DAL;C:\Program Files(x86)\Intel\Intel(R) Management Engine Components\IPT;C:\Program Files(x86)\Intel\OpenCL SDK\2.0\bin\x86;C:\Program Files (x86)\Intel\OpenCLSDK\2.0\bin\x64;C:\Program Files\Common Files\Lenovo;C:\Program Files(x86)\Common Files\Ulead Systems\MPEG;C:\Program Files (x86)\WindowsLive\Shared;C:\SWTOOLS\ReadyApps;C:\Program Files (x86)\Symantec\VIP Access Client\;C:\Program Files (x86)\CommonFiles\Lenovo;%MGC_HOME%/bin;%MGC_HOME%/lib;%MGC_HOMEBS%\bin;%MGC_HOMEBS%\lib;; %CDSROOT%\tools\bin;%CDSROOT%\tools\libutil\bin;%CDSROOT%\tools\fet\bin;%CDSRO OT%\tools\pcb\bin;%CDSROOT%\tools\specctra\bin;%CDSROOT%\tools\PSpice;%CDSROOT %\tools\PSpice\Library;%CDSROOT%\tools\Capture;%CDSROOT%\OpenAccess\bin\win32\ opt以下为网上资料(供参考):Cadence Allegro 16.3和PADS 9.2冲突解决办法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cadence Allegro

创建电路板

导入网表

元器件布局

设置层叠结构

设置布线规则

布线操作

铺铜与分割点电源层

∙调整丝印

∙丝印字符尽量遵循从左至右、从下往上的原则,对于电解电容、二极管等极性的器件在每个功能单元内尽量保持方向一致。

PCB板上的安装孔丝印用H1、H2……Hn进行标识。

器件焊盘上无丝印(即丝印不可上焊盘);为了保证搪锡的锡道连续性,要求需搪锡的锡道上无丝印;为了便于器件插装和维修,器件位号不应被安装后器件所遮挡;丝印不能压在导通孔、焊盘上,以免开阻焊窗时造成部分丝印丢失,影响识别。

丝印间距应大于5mil。

∙有极性元器件其极性在丝印图上标识清楚,极性方向标记应易于辨认。

PCB板上应有42*6的条形码丝印框,条形码的位置应考虑方便扫描。

PCB板名、日期、版本号等制成板信息丝印位置应明确。

PCB板文件上应有板名、日期、版本号等制成板信息丝印,位置明确、醒目。

板边3mm不走线

定位光标中心距板边大于8mm BGA周围5mm无元器件

板边5mm为禁止布线

插接件周围5mm无元器件。