《数字电路-分析与设计》第七章习题及解答(部分2) 北京理工大学出版社

第7章 信号处理电路 习题解答

7.3简述电荷放大器有什么特点,应用于何种场合。

解:电荷放大器应用于压电式加速度传感器、压力传感器等的后端放大。

上述两种传感器属于电容性传感器,这类传感器的阻抗非常高,呈容性,输出电压很微弱;他们工作时,将产生正比于被测物理量的电荷量,积分运算电路可以将电荷量转换成电压量,电路如下图所示。

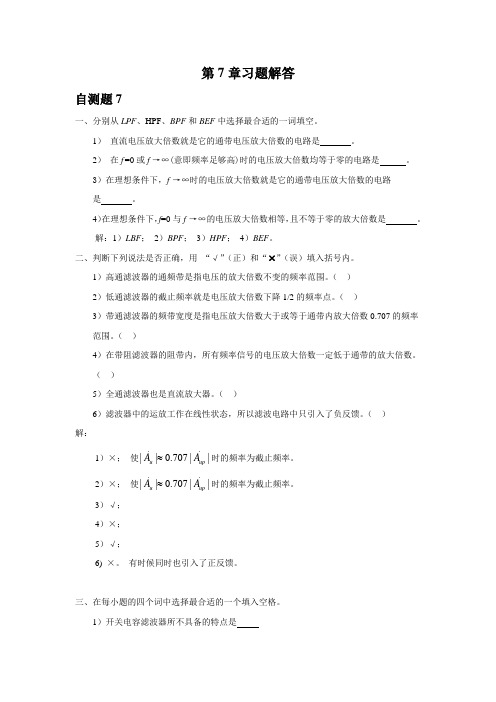

解:1)LBF;2)BPF;3)HPF;4)BEF。

二、判断下列说法是否正确,用 “√”(正)和“ ”(误)填入括号内。

1)高通滤波器的通频带是指电压的放大倍数不变的频率范围。()

2)低通滤波器的截止频率就是电压放大倍数下降1/2的频率点。()

3)带通滤波器的频带宽度是指电压放大倍数大于或等于通带内放大倍数0.707的频率范围。()

其中 ;

该滤波器为二阶低通滤波电路,幅频特性如下图:

7.7试说明图P7-8所示各电路属于哪种类型的滤波电路,是几阶滤波电路。

(1)

(2)

图P7-7

解:

图(1)所示电路二阶带通滤波器或者二阶带阻滤波器。

前一个运放为高通滤波器(截止频率f1),后一个运放为低通滤波器(截止频率f2),如果 ,则f1<f2,该滤波器为二阶带通滤波器;如果 ,则f1>f2,该滤波器为二阶带阻滤波器。

电容性传感器可等效为因存储电荷而产生的电动势Ut与一个输出电容Ct串联,如图中虚线框内所示。根据集成运放的特点,可得到输出电压为: 。

7.4简述隔离放大器有什么特点,应用于何种场合。

解:隔离放大器通常应用于远距离信号传输。

在远距离信号传输的过程中,常因强干扰的引入使放大电路的输出有很强的干扰背景,甚至将有用信号淹没,造成系统无法正常工作。隔离放大器将电路的输入侧和输出侧在电气上完全隔离,它既可切断输入侧和输出侧电路间的直接联系,避免干扰混入输出信号,又可使有用信号畅通无阻。目前集成隔离放大器有变压器耦合式、光电耦合式和电容耦合式三种。

第7章习题及答案

1第七章 习题及解答7-11如图7.45所示,主存中有两个空白区。

现有如下程序序列:程序1要求50KB ;程序2要求60KB ;程序3要求70KB 。

若用首次适应算法和最佳适应算法来处理这个程序序列,试问:哪一种算法可以分配得下 ? 简要说明分配过程 (假定分区描述器所占用的字节数已包含在程序所要求的主存容量中) 。

图7.45答:(1) 首次适应法:程序1要求50KB ,在起始地址为150KB ,大小为120 KB 的空白区进行分割。

120KB -50KB=70KB ,分割后剩70KB 的空白区。

程序2要求60KB ,在剩余的70KB 空白区进行分割。

70KB -60KB=10KB ,分割后剩 10KB 的空白区。

程序3要求70KB ,在起始地址为300KB ,大小为78KB 的空白区进行分割。

78KB -70KB=8KB ,分割后剩8KB 的空白区。

因此首次适应法可满足该程序序列的需求。

(2) 最佳适应法程序1要求50KB ,在起始地址为300KB ,大小为78 KB 的空白区进行分割。

78KB -50KB=28KB ,分割后剩28KB 的空白区。

程序2要求60KB ,在起始地址为150KB ,大小为120KB 的空白区进行分割。

120KB -60KB=60KB ,分割后剩60KB 的空白区。

程序3要求70KB ,。

此时系统中有大小为 28KB 和60KB 的两个空白区,它们均不能满足程序3 的需求。

因此最佳适应法不能满足该程序序列的需求。

150K B300K B 主存7-12已知主存有256KB 容量,其中OS 占用低址20KB ,可以有这样的一个程序序列。

程序1要求 80KB ;程序2要求16KB ;程序3要求140KB 。

程序1完成;程序3完成。

程序4要求 80KB ;程序5要求120KB 。

试分别用首次适应算法和最佳适应算法分别处理上述程序序列 (在存储分配时,从空白区高址处分割作为已分配区),并完成以下各步骤。

数字逻辑课后答案第七章

= FC4 ⋅ F4F3 ⋅ F4F2

据此,可画出逻辑电路图如图3所示。 图3

7. 试用4路数据选择器实现余3码到8421码的转换。 解答 假定用ABCD表示余3码,WXYZ表示8421码,并选择A、B作为选择变量,可求出各4路 数据选择器的数据输入端分别为:

W : D0 = D1 = 0, D2 = CD, D3 = 1 X : D0 = 0, D1 = CD, D2 = CD, D3 = 0 Y : D0 = 0, D1 = D2 = C ⊕ D, D3 = 0 Z : D0 = 0, D1 = D2 = D, D3 = 1

D80 D40 D20 D10

×

1010

D80 D40 D20 D10

D80 D40 D20 D10

+

D8 D4 D2 D1

B6 B5 B4 B3 B2 B1 B0

据此,可得到实现预定功能的逻辑电路如图2所示。

B6 B5 B4 B3

B2 B1 B0

T693 0

D40 D40 0 D80 0

T693 0

w团队一直秉承用心为大家服务的宗旨以关注学生的学习生活为出发点旨在为广大学生朋友的自主学习提供一个分享和交流的平台

课后答案网,用心为你服务!

大学答案 --- 中学答案 --- 考研答案 --- 考试答案 最全最多的课后习题参考答案,尽在课后答案网()! Khdaw团队一直秉承用心为大家服务的宗旨,以关注学生的学习生活为出发点,

所示。 表3

CP

Q0Q1Q2 F(DR)

0

101

1

1

110

1

2

111

0

3

011

0

4

001

0

《数字电路与逻辑设计》习题课 (2)

状态定义: S0:初始状态。 S1:收到五角硬币。 S2:收到一元硬币。 S3:收到一元五角硬币。 并入S0状态。

00/00 AB/YZ

S0

01/10 10/11

01/00 10/00

S2

S1 00/00 01/00

00/00 例1原始状态转移图

例2、分析图所示计数器电路,说明是模长为多少的 计数器,并列出状态转移表。

6

C

&

1 1

A & ?

Z

X

&

N

A X

&

1 & J

1

C

R 1 & K

解:1)分析电路结构:该电路是由七个与非门 及一个JKFF组成,且CP下降沿触发,属于米 勒电路,输入信号X1,X2,输出信号Z。

2)求触发器激励函数:J=X1X2,K=X1X2 触发器次态方程:

Qn+1=X1X2Qn+X1X2Qn=X1X2Qn+(X1+X2)Q

第六章复习

计数器的分析

❖ 同步、异步分析步骤:由电路触发器激励 函数(公式和图解)状态转移表分析模 长和自启动性。 用图解法,注意高低位顺序,一般数码越高 位权越高:Q3Q0

❖ 移存型计数器属于同步计数器,只要求出第 一级触发器的次态方程和初始状态,就可以 写出状态转移表。

计数器的设计

❖ 同步计数器的设计:状态转移表激励函数 和输出函数(自启动性检查)电路图。

❖ 7490只能异步级联,M=100。

❖ 74194级联可实现8位双向移存器

MSI实现任意进制计数器(M<N)

❖ 反馈法:异步清0法和同步置数法。注意: 用LD端置全1(置最大数法)时,反馈状 态对应编码中出现0的端口需通过非门送入 反馈门。

习题解答第7章

A. ; B. ;

C. ; D.

解:由求解一阶电路的三要素法 可知在原电路中 V, V。当初始状态不变而输入增加一倍时,有

V

二、填空题

1.换路前电路已处于稳态,已知 , , , . 时,开关由 掷向 ,则图7—3所示电路在换路后瞬间的电容电压 V, V。

作用时的响应为

作用时的响应为

总的零状态响应为

8.图7—14所示电路中,激励为单位冲激函数 A,求零状态响应 。

解:设激励为 ,用三要素法求电路的单位阶跃响应。

,

,

电流的单位阶跃响应为

根据单位冲激响应和单位阶跃响应的关系,可得电路中的 :

9.图7—15所示电路中, , ,求 时的响应 。

解:应用叠加原理求解此题.

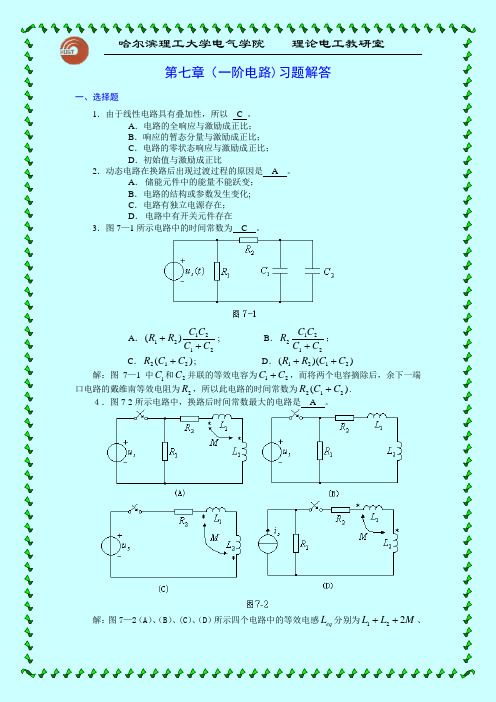

第七章(一阶电路)习题解答

一、选择题

1.由于线性电路具有叠加性,所以C。

A.电路的全响应与激励成正比;

B.响应的暂态分量与激励成正比;

C.电路的零状态响应与激励成正比;

D.初始值与激励成正比

2.动态电路在换路后出现过渡过程的原因是A。

A.储能元件中的能量不能跃变;

B.电路的结构或参数发生变化;

C.电路有独立电源存在;

解: 由 时刻电路得:

,

换路后,电容 , 构成纯电容的回路(两电容并联),电容电压发生强迫跃变,此时应由电荷守恒原理求解换路后瞬刻的电容电压。由 得:

……①

…… ②

由以上两式解得

2.图7—4所示电路的时间常数 .

解:将储能元件开路,独立电源置 后,可得求戴维南等效电阻的电路如图7—4(a)所示。由于电路中含有受控源,因此需用外加电压法求戴维南等效电阻 .由图7—4(a)得

电子科大-数电-数字逻辑设计第七章(3)

5 精品资料

T触发器

在每个时钟脉冲有效沿都会改变状态(zhuàngtài)(翻转)

T(toggle)

Q

触发器

T Q

EN Q TQ

具有使能端的 T触发器

T Q

6 精品资料

利用(lìyòng)D、J-K触发器实现T触 发器

利用(lìyò ng)D触发器 利用J-K触发器实现

精品资料

关于(guānyú)电路结构和逻辑功能

电路构成的不同形式

下一状态Q* 与 现态Q及输入之间 在稳态下的逻辑关系

同一逻辑功能的触发器可用不同电路结构实现 主从结构的D触发器、维持(wéichí)阻塞结构的

D触发器 用同一电路结构可做成不同逻辑功能的触发器 维持(wéichí)阻塞结构的:D触发器、J-K触发器

27 27

精品资料

例:时钟同步状态机(D触发器)

下一状态逻辑 产生激励信号

状态存储器 输出逻辑

EN EN

输入(shūrù ) EN’

D0

Q0

MAX 输出(sh

Q0

Q0’

D1

Q1

Q1

激励

Q1’

CLK

28 28

时钟信号

精品资料

当前状态

EN3、由激励方EENN程’ 和触发器特征方程

D0

Q0

得到转移方程(状态方程)

MAX

D触发器Q特0 征方程:Q* = D

Q0* =QQ00’ ·EN’ + Q0’·EN

D1

Q1

Q1* =QQ11·EN’ + Q1’·Q0·EN

Q+1’Q1·Q0’·EN

《数字电路-分析与设计》第一章习题及解答 北京理工大学出版社

第一章习题1-1 例1.2.12中转换前后两个数的绝对值哪个大?为什么?答:转换前大。

因为转换后舍去了后边的小数位。

1-2 将下列二进制数分别转换为八进制数、十六进制数和十进制数。

11001101.101,10010011.1111解:(11001101.101)2 =(11 001 101.101)2= ( 315.5)8=(1100 1101.1010)2 =( CD.A)16=(128+64+8+4+1+0.5+0.125)10=(205.625)10(10010011.1111)2 =(1001 0011.1111)2= (93.F)16=(10 010 011.111 100)2 =( 223.74)8=(128+16+2+1+0.5+0.25+0.125+0.0625)10=(147.9375)101-3 将下列十进制数转换为二进制、八进制和十六进制数。

121.56,73.85解:1. 0Å1Å3Å7Å15Å30Å60Å121 0.56Æ0.12Æ0.24Æ0.48Æ0.96Æ0.921 1 1 1 0 0 1 1 0 0 0 1所以:(121.56)10=(1111001.10001)2=(171.42)8=(79.88)162. 0Å1Å2Å4Å9Å18Å36Å73 0.85Æ0.7Æ0.4Æ0.8Æ0.6Æ0.2Æ0.41 0 0 1 0 0 1 1 1 0 1 1 0(73.85)10=(1001001.11011)2=(111.66)8=(49.D8)161-4 将下列十六进制数转换为二进制、八进制和十进制数。

89.0F,E5.CD解:(89.0F)16=(10001001.00001111)2=(211.036)8=(8*16+9+15/256)10=(137. 0.05859375)10 1-5 试求例1.2.17的转换误差,比较例1.2.12的转换误差,哪个大?为什么?答:例1.2.12的误差大。

数字电路第7章

数字电路与逻辑设计

用D触发器构成的异步四位二进制加计数器

Q0 CP Q D C F0 Q Q D C F1 Q Q1 Q D C F2 Q Q2 Q D C F3 Q Q3

RD

CP Q0 Q1 Q2 Q3

1 0 0 0

0 1 0 0

1 1 0 0

0 0 1 0

1 0 1 0

0 1 1 0

6人 2人 4人 3人

3人 4人 4人 2人

57.1% 36% 34.6% 33.3%

26人 17人 16人 17人

1人 4人 6人 6人

1人 4人 4人 2人

时序逻辑电路

数字电路与逻辑设计

7.1 概述 7.2 时序逻辑电路的分析方法和设计思路 7.4 集成计数器 7.5 寄存器

数字电路与逻辑设计

4 作状态转换真值表

计数脉冲

0 1 2 3 4 5 6 7 8 Q2 0 0 0 0 1 1 1 1 0 Q1 0 0 1 1 0 0 1 1 0 Q0 0 1 0 1 0 1 0 1 0

无论是时序波形图还是状态转 换真值表,都反映了该计数器是 从状态000开始计数,每来一个 计数脉冲,二进制数值便加1, 计满归零。 输入第8个计数脉冲时计满归零 作为整体,该电路可称为模8加 模 计数器 、或八进制 八进制加计数器。

1 1 1 0

0 0 0 1

1 0 0 1

0 1 0 1

1 1 0 1

0 0 1 1

1 0 1 1

0 1 1 1

1 1 1 1

0 0 0 0

分析:图中各位触发器均为上升沿触发的D触发器。由于 分析: 各位D触发器的输入D端与它们各自输出的非联在一起,所 以,F0在每一个时钟脉冲上升沿到来时翻转一次。 F1在Q0由 1变0时翻转, F2在Q1由1变0时翻转, F3在Q2由1变0时翻。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第七章 习题答案 7-11 1、米里型状态机 2、输出方程: 01QXQZ

驱动方程: 011QQXD 10QXD 状态方程: 01111QQXDQn 1010QXDQn 3、状态转换表: X nQ1 nQ0 11nQ 10nQ Z

0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 1 0 0 0 1 0 0 0 1 0 1 0 1 1 1 0 1 1 0 1 0 1 1 1 1 1 0 0 4、状态转换图:

5、时序图:已知:X=1011111001110 初始: 0001QQ nnQQ

01

X/Z 00nQQ

01

01nQQ

01

11nQQ

01

10nQQ

01

1/0 1/0

1/0 0/0

0/0

1/1

0/0 0/0

X Q1n Q0n Z

CP 7-14 7-32 一、次态K图,D触发器: 1、根据状态转换表,有:

1212313QXQQQQXQn 1212122312QXQQQXQQXQQXQn 111QXQn 2、求驱动方程:对于D就是状态方程:

12123133QXQQQQXQDn

12121223122QXQQQXQQXQQXQDn

1111QXQDn 3、检查启动特性: X nQ3 nQ2 nQ1 13nQ 12nQ 11n

Q

0 1 0 1 0 1 0 0 1 1 0 0 0 1 0 1 1 1 0 1 0 1 1 0 1 0 1 0 1 1 1 0 0 1 0 1 1 1 1 1 0 0

001/0 000/1 010/0 001/0 011/1 000/0 100/0 010/1 100/0 010/1

0 0 1 0 1 0 0 1 0 1

00 00 01 11 10 01 11 10

3

XQ

12QQ

ZQQQnnn/111213

00 3XQ12QQ00 01 11 10 01 11 10 能够自启动。 二、次态K图,JK触发器:

1、求状态方程: 1212313QXQQQQXQn

1212122312QXQQQXQQXQQXQn

111QXQn 与采用D触发器一样。与JK触发器的特性方程相比QKQJQn1 2、得JK触发器的驱动方程:

12312313QQQXQQQXQn

∴ )(123QQXJ 13K 132XQQXJ 1112QXQXQXK

XJ1 11K

3、检查启动特性: (与前相同,略)

7-38 设计一个二位多功能计数器: 1、列状态转换驱动表:

输入 现态 驱动 输出 CP 1C 0C nQ1 nQ0 11KJ 00KJ

11nQ 10n

Q

1 0 0 0 0 0 1 0 1 2 0 0 0 1 1 1 1 0 3 0 0 1 0 0 1 1 1

001/0 000/1 010/0 001/0 011/1 000/0 100/0 010/1 100/0 010/1

3XQ12QQ00

00 01 11 10

01 11

10 4 0 0 1 1 1 1 0 0 5 0 1 1 1 0 1 1 0 6 0 1 1 0 1 1 0 1 7 0 1 0 1 0 1 0 0 8 0 1 0 0 1 1 1 1 9 1 0 0 0 0 1 0 1 10 1 0 0 1 1 0 1 1 11 1 0 1 1 0 1 1 0 12 1 0 1 0 1 0 0 0 13 1 1 0 0 0 1 0 1 14 1 1 0 1 1 0 1 1 15 1 1 1 1 1 1 0 0 16 1 1 1 0

2、从四变量K图求驱动方程:

00100011QCCQCQCJ 其它K图略: 001001001011QCCQCCQCCCCK 1110QCQJ

1110QCCK

逻辑电路图,略。 7-50 1、采用JK触发器:(驱动表法——自选) a 建立状态图: M=7 k=3 , 无外加输入信号X=0,设进位输出信号为C。

1 1 1 1

000 001 011 010 110 111 101 Q3Q2Q1 /0 /0 /0 /0 /0 /0 /1

X/C

01CC 01QQ 00 01 11 10

00 01 11

10 b 状态转换驱动表: 现态 次态 输出 驱动 nQ3 nQ2 nQ1 13nQ 12nQ 11n

Q

C

33KJ 22KJ 11KJ

0 0 0 0 0 1 0 0 0 1 0 0 1 0 1 1 0 0 1 0 0 1 1 0 1 0 0 0 0 1 0 1 0 1 1 0 0 1 0 0 1 1 0 1 1 1 0 0 0 1 1 1 1 1 0 1 0 0 1 0 1 0 1 0 0 0 1 1 0 1 1 0 0

c 从K图求驱动方程: 输出方程: 13QQC

123QQJ

23QK 132QQJ 132QQK

1

111 1

12QQ 3Q 00 01 11 10

0

1

12QQ 3Q 00 01 11 10

1 0

111 1

12QQ 3Q 00 01 11 10

1 0

111 1

12QQ 3Q 00 01 11 10

1 0 321QQJ 23231QQQQK d 检查启动状态: 未用态 驱动 次态 输出 3Q 2Q 1Q 33KJ 22KJ 11KJ

13nQ 12nQ 11n

Q

C

1 0 0 0 1 0 0 1 1 0 0 1 0 可自启动。 e 画出完整的状态转换图:

f 画出电路逻辑图。(略) 7-55 设初始状态:0001QQ

70124012201270126012501240123012201210120012DSSSDSSSDSSSDSSSDSSSDSSSDSSSDSSSDSSSDSSSDSSSZ

111 1 1

12QQ 3Q 00 01 11 10

1 0

111 1 1

12QQ 3Q 00 01 11 10

1 0

000 001 011 010 110 111 101 Q3Q2Q1 /0 /0 /0 /0 /0 /0 /1

X/C

100 /0