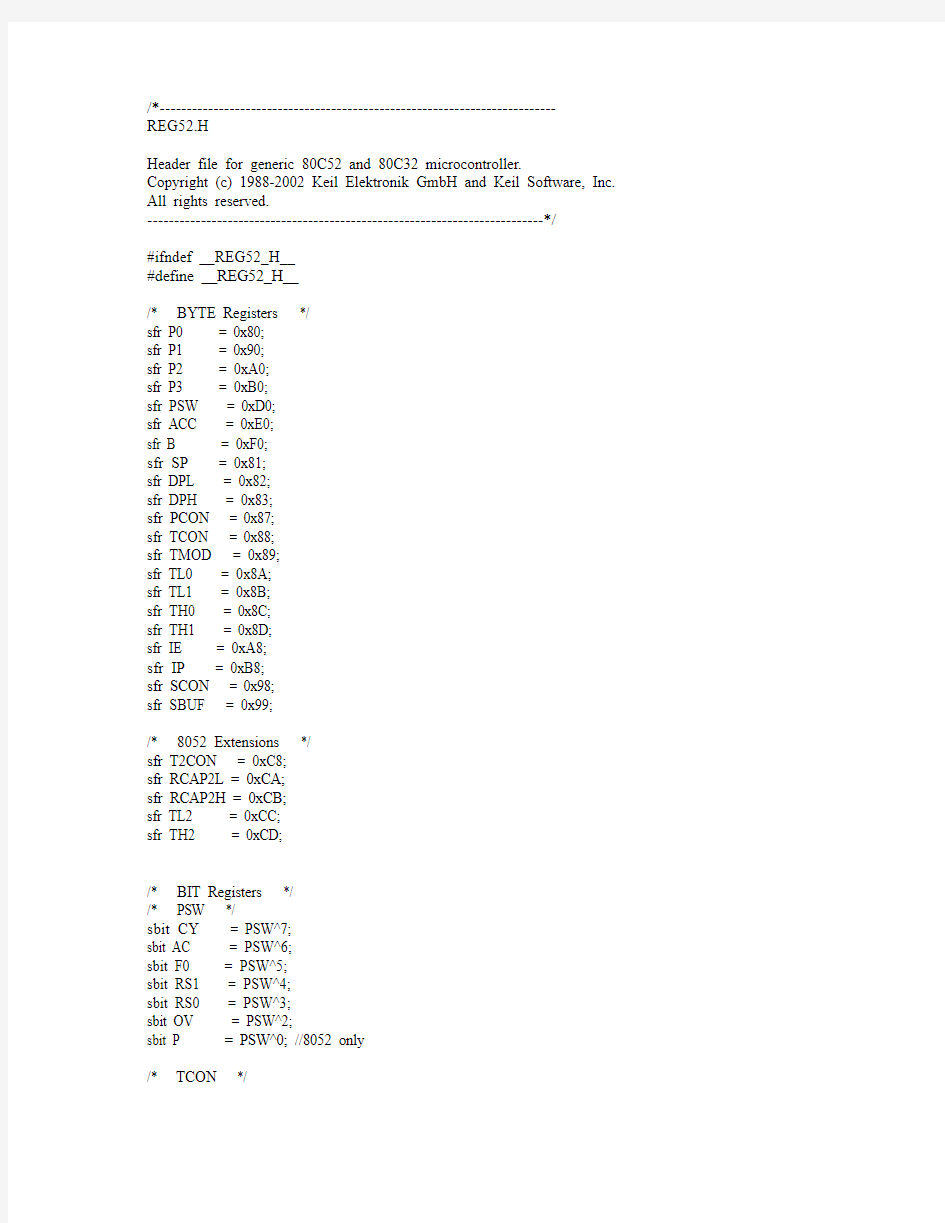

89c52头文件

/*--------------------------------------------------------------------------

REG52.H

Header file for generic 80C52 and 80C32 microcontroller.

Copyright (c) 1988-2002 Keil Elektronik GmbH and Keil Software, Inc. All rights reserved.

--------------------------------------------------------------------------*/

#ifndef __REG52_H__

#define __REG52_H__

/* BYTE Registers */

sfr P0 = 0x80;

sfr P1 = 0x90;

sfr P2 = 0xA0;

sfr P3 = 0xB0;

sfr PSW = 0xD0;

sfr ACC = 0xE0;

sfr B = 0xF0;

sfr SP= 0x81;

sfr DPL = 0x82;

sfr DPH = 0x83;

sfr PCON = 0x87;

sfr TCON = 0x88;

sfr TMOD = 0x89;

sfr TL0 = 0x8A;

sfr TL1 = 0x8B;

sfr TH0 = 0x8C;

sfr TH1 = 0x8D;

sfr IE = 0xA8;

sfr IP= 0xB8;

sfr SCON = 0x98;

sfr SBUF = 0x99;

/* 8052 Extensions */

sfr T2CON = 0xC8;

sfr RCAP2L = 0xCA;

sfr RCAP2H = 0xCB;

sfr TL2 = 0xCC;

sfr TH2 = 0xCD;

/* BIT Registers */

/* PSW */

sbit CY= PSW^7;

sbit AC = PSW^6;

sbit F0 = PSW^5;

sbit RS1 = PSW^4;

sbit RS0 = PSW^3;

sbit OV = PSW^2;

sbit P = PSW^0; //8052 only

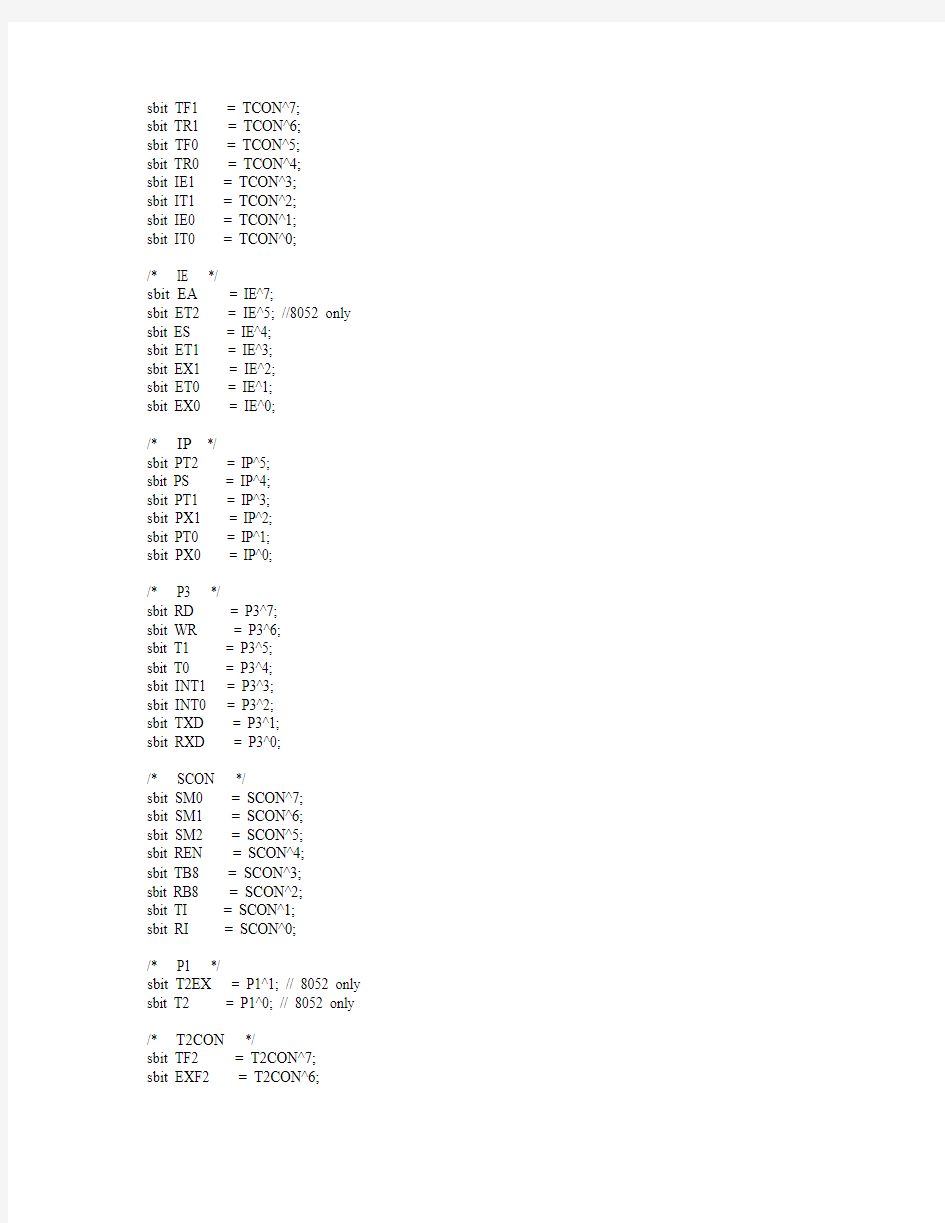

/* TCON */

sbit TF1 = TCON^7;

sbit TR1 = TCON^6;

sbit TF0 = TCON^5;

sbit TR0 = TCON^4;

sbit IE1 = TCON^3;

sbit IT1 = TCON^2;

sbit IE0 = TCON^1;

sbit IT0 = TCON^0;

/* IE */

sbit EA= IE^7;

sbit ET2 = IE^5; //8052 only sbit ES = IE^4;

sbit ET1 = IE^3;

sbit EX1 = IE^2;

sbit ET0 = IE^1;

sbit EX0 = IE^0;

/* IP*/

sbit PT2 = IP^5;

sbit PS = IP^4;

sbit PT1 = IP^3;

sbit PX1 = IP^2;

sbit PT0 = IP^1;

sbit PX0 = IP^0;

/* P3 */

sbit RD = P3^7;

sbit WR = P3^6;

sbit T1 = P3^5;

sbit T0 = P3^4;

sbit INT1 = P3^3;

sbit INT0 = P3^2;

sbit TXD = P3^1;

sbit RXD = P3^0;

/* SCON */

sbit SM0 = SCON^7;

sbit SM1 = SCON^6;

sbit SM2 = SCON^5;

sbit REN = SCON^4;

sbit TB8 = SCON^3;

sbit RB8 = SCON^2;

sbit TI = SCON^1;

sbit RI = SCON^0;

/* P1 */

sbit T2EX = P1^1; // 8052 only sbit T2 = P1^0; // 8052 only /* T2CON */

sbit TF2 = T2CON^7;

sbit EXF2 = T2CON^6;

sbit RCLK = T2CON^5; sbit TCLK = T2CON^4; sbit EXEN2 = T2CON^3; sbit TR2 = T2CON^2; sbit C_T2 = T2CON^1; sbit CP_RL2 = T2CON^0; #endif

波特率自适应的RS-485中继器设计

麓!誊萋囊霉毫螽囊篓蔷要毫曩囊枣鼍鬟蔓一鬻薹萋j鼍雾冀簪耋薹攀羔。川篓囊萋i薹鬻波特率自遁应的RS一485中继嚣设计 ■河北理工大学张习加李成群 引言 RS一485收发器采用平衡发送和差分接收,因此具有 抑制共模干扰的能力;加上接收器具有高灵敏度,能检测 低达200mV的电压,故传输信号能在千米以外得到恢 复。使用RS一485总线,一对双绞线就能实现多站联网, 构成分布式系统,且设备简单、价格低廉,能进行长距离通 信,因而得到了广泛的应用。由于在双绞线上的电平损 耗,RS一485标准通信的最大传输距离是1200m,因此更 远距离的应用中必须使用中继器。网络节点数与所选芯 片驱动能力和接收器的输入阻抗有关。RS一485标准规 定了最大总线负载为32个单位负载,若应用中总线负载 大于32个单位负载则必须使用中继器。 1RS一485中继器原理[1’2] Rs一485是半双工方式,两线双向传送差分信号,具 有多点、双向通信能力,即允许多个发送器和接收器连接 到同一条总线上,传输线上信号的传输方向不定。因此, 识别和控制好传输线上的信号传递方向是设计RS~485 中继器的关键。 RS一485标准规定:数据信号采用差分传输方式 (differential出ivermode),也称为“平衡传输”。它使用一 对双绞线,将其中一根线定义为A,另一根线定义为B,如 图1所示。 使能 A B f痞 I稍 f瘤 I自 +6V 许电平范围 +2V A—B电平范围 一2V 许电平范围 一6V 图1RS一485发送器的示意图 通常情况下,RS一485发送器A、B之间的正电平在+2~+6V,是一种逻辑状态;负电乎在一6~一2V,是另一种逻辑状态。在RS一485发送器件中,一般有一个“使能”控制信号,用于控制发送器与传输线的切断和连接。当“使能”端为低电平时,发送器输出处于高阻状态,称作“第三态”。它是有别于逻辑“1”与“o”的第三种状态。 对于RS一485接收器,也作出与发送器相对的规定,收、发端通过平衡双绞线将A—A与B—B对应相连。当在接收端A、B之间有大于+200mV的电平时,输出为正逻辑电平;小于一2。omV时,输出为负逻辑电平。在接收器的接收平衡线上,电平范围通常为200mV~6V,如图2所示。 A B 使能 电平范围 传输电平范围 图2RS一485接收器的示意图 RS一485接收器同样定义逻辑1(正逻辑电平)为B>A的状态,逻辑o(负逻辑电平)为A>B的状态,A、B之间的压差不小于200mV。在RS~485接收器件中,一般也有一个“使能”控制信号,用于控制接收器与传输线的切断和连接。当“使能”端为高电平时,接收器与传输线切断,接收器输出为高电平;当“使能”端为低电平时,接收器输出电平与总线信号的逻辑电平一致。 RS一485中继器原理图如图3所示。正常工作时主要有三个状态:空闲状态,数据从RS一485收发器Ul边的总线往RS一485收发器U2边的总线传送(简称“数据右传状态”),数据从RS一485收发器U2边的总线往RS一485收发器U1边的总线传送(简称“数据左传状态”)。(1)空闲状态 当中继器上电启动运行或总线上没有数据传送时,中继器工作在空闲状态。RS一485收发器U1、U2均为接收数据状态,U1、U2的ENl、EN2引脚均为低电平。 (2)数据右传状态 当RS一485收发器U1边检测到连接其A、B引脚总 62《牛I;机与嵌入式系'毛应用》adv@mesnet.com.cn(广告专用) 万方数据

用CPLD实现串行通信时的波特率自动侦测

用CPLD实现串行通信时的波特率自动侦测 杨李莎1朱华福 2 (1.长安大学研究生部,陕西西安 710064;2.云南昆船设备有限公司昆明 650236) 摘要:本文介绍了一种利用CPLD实现波特率自动侦测的方法,文章最后给出其仿真结果关键词:串行通信波特率自动侦测复杂可编程逻辑器件 Abstract: In this paper, it introduces a way to automatically detect baud rate by using CPLD, and in the end indicates it’s emulation results . Key words: serial communication baud rate auto detected CPLD 1、引言 串行数据通信是应用极为广泛的技术,通过数据传输控制或监测中心可以对远端设备进行控制和监测设备的工作状态。串行外设都会用到RS-232C 异步串行接口.传统上采用专用的集成电路即UART实现,如TI、EXAR、EPIC 的550、452等系列,但是我们一般不需要使用完整的UART的功能,而且对于多串口的设备或需要加密通讯的场合使用UART也不是最合适的。如今的许多的电器都有串口,主要用于软件的升级或者用于自诊断。通常单机设备的串行通信波特率设置都是采用硬件拨码的方式进行的,对于一些拨码开关特别多的设备来说难于记忆,因此能否寻求一种波特率自适应的方法来解决这个问题呢?回答是肯定的,本文就介绍一种用复杂可编程逻辑器件来实现波特率自动侦测的方法。系统只设计了数据接收模块,利用VHDL语言对其进行编程,最后给出其仿真结果。 2、系统设计 2.1系统介绍 图1所示为数据接收模块结构框图,数据接收模块由波特率发生基准时钟、开始位下降沿检测、接收控制、串并转换器、锁存器、缓冲器等部分组成。为了能准确地侦测出接收数据的波特率,数据接收模块中采用了波特率发生基准时钟,首先用基准时钟对RXD端的数据进行接收采样,然后按波特率自动侦测原理进行波特率自动侦测,最后产生一个与发送端发送的数据相同的波特率,利用波特率进行通信。 1【作者简介】杨李莎(1981—)女,长安大学研究生部04级交通信息工程及控制专业硕士研究生,主要从事高速公路和城市道路的交通控制及管理研究。

波特率自适应

波特率自适应方案 一、波特率自适应概念 电表检测PC 机通信的波特率,并自动匹配通信。 二、方案 1、 点对点自适应通信,即PC 机与单一电表进行自适应通信。 如果我们想利用PC 机(波特率为1200bps )对未知波特率的电表通信,则需要进行下面几个步骤。 1.1 第一步:PC 机需要以1200bps 发送“ 55H 55H ” 1.2 第二步:等待未知波特率的电表应答。如果自适应成功则应答字符为:“80H ”,这时未知波特率的电表将更波特率为1200bps 。如果无应答,应答字符有误,或者在500ms 内未应答则此次自适应过程失败。重复第一步和第二步,重复三次都未应答则自适应失败。 1.3 第三步:成功自适应则可以利用1200bps 对电表进行通信。自适应失败只能将电表的波特率修改成1200bps 才能通信。 如果想用其他的波特率通信,请重复上面步骤 流程图 PC (1200)发送5555H → 电表回复80H → 1200正常通讯 →若要修改波特率 ↑ ↓ ← 电表未回复80H 2、 点对多自适应通信,即广播方式让总线上的电表统一波特率 流程图 3、 电表单片机自适应波特率原理 在不同波特率下发送一位数据的时间是不一样的,利用这个原理,确认在1200、2400、4800、9600状态下发送一个字节所需要的时间段B1、B2、B3、B4,将其存储到单片机中。 PC 机以广播方式1200bps 发送5555H 等待500ms 再次广播 发送55H 等待500m PC 机以 1200bps 抄读系统表

当PC机发送数据到电表时,单片机利用定时器测量接收一个字节的时间A,然后将A与B1,B2,B3,B4进行比对,假如A在B1范围内,那么单片机将电表波特率设置为1200,修改波特率结束。 流程图如下所示: 广播或者PC发送5555H(1200波特率) 单片机接收到第一个字节数据 55H,产生接收中断1 定时器开始工作,每产生一次定 时器中断就对变量A进行累加 单片机接收到第二个字节数据 55H,产生接收中断2 关闭定时器,将变量A与 B1/B2/B3/B4进行比对,确认A 属于范围B1 单片机将电表波特率改为1200 波特率修改成功

单片机波特率自适应

单片机从机的波特率自适应设置 一、硬件原理图 说明:DB9接到PC机的串口上。晶体震荡器可以用诸如11.0592MHz,14.7456MHz,对本文的介绍没有影响等等。这里,单片机为机为,PC机为主机。 二、自动设置理论原理 AT89C52的串行口有4种工作方式,方式1、3最常用。T2的波特率发生方式类似于常数自动重装入方式。用X16代替(RCAP2H,RCAP2L),则串行口方式1、3的波特率公式为: 波特率=fosc/[32 x (65536-X16 )]..……………………..……..…(A) 由(A)可得,单片机每接收1bit需要的时间为 接受1bit的时间=[32 x (65536- X16 )]/ fosc……………………(B) 单片机A T89C52为12分频指令系统,所以其机器周期为: 机器周期= 12/fosc……………………………………….….….……(C ) 我们可以很容易得到单片机接收1bit所需要的机器周期,假定为NUM,则由(B),(C)得NUM x 12/ fosc=[32 x (65536- X16)]/ fosc…………………………...(D) 由(D)可得,波特率定时时间常数为: X16=NUM x 3/8……………………………….…………………….….(E) 由此,关键需要得到单片机接受1 bit的机器周期数NUM。 三、自动检测主机信息的方法 不失一般性,假定串行通讯的字符协议为1起始位,8数据位,无奇偶校验位,1停止位,如下(图2)所示,

由定时器2工作原理(图3)知道,C/T2=0,TR2=0,则其加1计数,其计数速率为fosc/12,每加1需要的时间等于12/fosc,刚好就是一个机器周期。所以,只要我们在传输数据的某位开始处启动定时器,在传输该位结束时停止计数器,然后获取该范围的计数值,就是我们上面公式(E)中的NUM。 (定时器2工作原理,图3) 由图2知,如果主机(PC机)发给单片机01H(十六进制),则单片机P3.0接收数据如下波形(图4)。起始位开始时,启动定时器T2,当高电平来到时,关闭定时器T2,则计数值就等于NUM。 四、软件实现 1.流程图 这里给出获取定时常数的流程图,按主机发0x01来设计的 获取8bit数据的定时计数值(图5)计算定时时间常数(图6)

串口通讯误码分析及波特率自适应技术

串口通讯误码分析及波特率自适应技术 -------------------------------------------------------------------------------- 串口通讯误码分析及波特率自适应技术(非典) 为讨论方便,只论证1位起始位+8位数据+1位停止位的误码问题 现设:发送方每位传输时间为TCK 接收方每位传输时间为RCK 起始位L(低电平),停止位H(高电平) 空闲状态为X(高电平),数据位DX(D0..D7) 通讯数据流为XXXXXLDDDDDDDDHXXXXXLDDDDDDDDHXXXX... 采样一般采用串口通讯公认的“中部三中取二”算法 当收发双方采用事先约定固定波特率串口通讯时,由于双方系统 时钟差异和线路传输时延,将会出现以下3种问题: 1. TCK=RCK时(可以稍有偏差) 发送数据流为XXXXXLDDDDDDDDHXXXXXLDDDDDDDDHXXXX... 接收数据流为XXXXXLDDDDDDDDHXXXXXLDDDDDDDDHXXXX... 故在这种情况下不会出现误码现象。 (别拍砖!这连腹中胎儿都“知道”,不敢“卖弄是非”) 2. TCK

【CN110048923A】一种多模块多波特率自适应的高速串行异步通信解决方法【专利】

(19)中华人民共和国国家知识产权局 (12)发明专利申请 (10)申请公布号 (43)申请公布日 (21)申请号 201910317377.2 (22)申请日 2019.04.19 (71)申请人 博能传动(苏州)有限公司 地址 215100 江苏省苏州市相城经济开发 区如元路100号 (72)发明人 支萌辉 尹泉 蒋生成 (74)专利代理机构 苏州智品专利代理事务所 (普通合伙) 32345 代理人 吕明霞 (51)Int.Cl. H04L 12/40(2006.01) (54)发明名称 一种多模块多波特率自适应的高速串行异 步通信解决方法 (57)摘要 本发明公开了一种多模块多波特率自适应 的高速串行异步通信解决方法,包括主机模块、 从机模块和高速串行异步通信模块,所述主机模 块包括ARM处理器、FPGA处理器一和并行总线一 模块,所述从机模块包括FPGA处理器二、DSP处理 器和并行总线二模块,所述主机模块和从机模块 通过高速串行异步通信模块相连;所述FPGA处理 器一与FPGA处理器二之间采用一问一答的主从 半双工高速串行异步通信模式,所述主机模块的 波特率预定义,从机模块通过波特率自适应算法 检测不同主机模块的波特率,并切换为所检测到 的波特率以实现与相应主机模块之间的通信。本 发明同一从机模块适用于不同的主机模块,让电 机驱动器模块化成为可能。权利要求书2页 说明书4页 附图1页CN 110048923 A 2019.07.23 C N 110048923 A

权 利 要 求 书1/2页CN 110048923 A 1.一种多模块多波特率自适应的高速串行异步通信解决方法,包括主机模块(1)、从机模块(2)和高速串行异步通信模块(3),其特征在于:所述主机模块(1)包括ARM处理器(11)、FPGA处理器一(12)和并行总线一模块(13),所述从机模块(2)包括FPGA处理器二(21)、DSP 处理器(22)和并行总线二模块(23),所述主机模块(1)和从机模块(2)通过高速串行异步通信模块(3)相连;所述FPGA处理器一(12)与FPGA处理器二(21)之间采用一问一答的主从半双工高速串行异步通信模式,所述主机模块(1)的波特率预定义,从机模块(2)通过波特率自适应算法检测不同主机模块(1)的波特率,并切换为所检测到的波特率以实现与相应主机模块(1)之间的通信。 2.根据权利要求1所述的一种多模块多波特率自适应的高速串行异步通信解决方法,其特征在于:所述ARM处理器(11)可以通过专用存储器接口或通用IO接口对FPGA处理器一(12)进行数据读写操作,所述ARM处理器(11)通过并行总线一模块(13)将需要发送给从机模块(2)的数据写入FPGA处理器一(12),所述ARM处理器(11)也可通过所述并行总线一模块(13)读取FPGA处理器一(12)中的数据。 3.根据权利要求1所述的一种多模块多波特率自适应的高速串行异步通信解决方法,其特征在于:所述FPGA处理器一(12)通过其内部的双端口RAM构建数据交互缓冲区,双端口RAM的一个端口由ARM处理器(11)控制,另一个端口由FPGA处理器二(21)的内部逻辑控制,所述FPGA处理器一(12)是高速串行异步通信的发起者,FPGA处理器一(12)包括向从机模块(2)定时发送数据以及接收和解析来自从机模块(2)的数据。 4.根据权利要求1所述的一种多模块多波特率自适应的高速串行异步通信解决方法,其特征在于:所述FPGA处理器二(21)通过其内部的双端口RAM构建数据交互缓冲区,双端口RAM的一个端口由DSP处理器(22)控制,另一个端口由FPGA处理器一(12)的内部逻辑控制,所述FPGA处理器二(21)包括向主机模块(1)定时发送数据以及接收和解析来自主机模块(1)的数据。 5.根据权利要求1所述的一种多模块多波特率自适应的高速串行异步通信解决方法,其特征在于:所述DSP处理器(22)可以通过专用存储器接口或通用IO接口对FPGA处理器二(21)进行数据读写操作,所述DSP处理器(22)通过并行总线二模块(23)读取缓存在FPGA处理器二(21)中的数据,所述DSP处理器(22)也可以将需要反馈给主机模块(1)的数据通过并行总线二模块(23)写入FPGA处理器二(21)。 6.根据权利要求1所述的一种多模块多波特率自适应的高速串行异步通信解决方法,其特征在于:所述高速串行异步通信模块(3)是主机模块(1)和从机模块(2)之间数据交互的通道,主机模块(1)定时将数据发送给从机模块(2),从机模块(2)接收到数据后,对接收数据进行校验和解析,并将主机模块(1)需要的数据反馈回去,从而实现主从模块间一问一答的半双工通信;所述高速串行异步通信模块(3)采用半双工的485物理链路层实现,且主机模块(1)采用预定义的波特率,不同类型的主机模块(1)可以定义不同的波特率。 7.根据权利要求1所述的一种多模块多波特率自适应的高速串行异步通信解决方法,其特征在于:所述主机模块(1)按照串行异步通信方式依次发送帧头、有效数据和CRC校验数据,其中帧头信号中带有波特率信息,该波特率信息通过帧头信号中的低电平宽度来表示,从机模块(2)通过检测低电平的宽度来识别不同主机模块(1)的波特率,从机模块(2)实时动态地检测每一帧数据的帧头信号,从而实现在从机模块(2)不断电的前提下对主机模 2