密脚间距QFP集成电路引线成形工艺研究

电子元器件封装分类型

1 双列直插封装(DIP)20世纪60年代,由于IC集成度的提高,电路引脚数不断增加,有了数十个I/O引脚的中、小规模集成电路(MSI、SSI),相应的封装形式为双列直插(DIP)型,并成为那个时期的主导产品形式。

70年代,芯片封装流行的是双列直插封装(DIP)、单列直插封装(SIP)、针栅阵列封装(PGA)等都属于通孔插装式安装器件。

通孔插装式安装器件的代表当属双列直插封装,简称DIP(Dualln-LinePa ckage)。

这类DIP从封装结构形式上可以分为两种:其一,军品或要求气密封装的采用陶瓷双例直插DIP;其二,由于塑料封装具有低成本、性价比优越等特点,因此,封装形式大多数采用塑料直插式PD IP。

塑料双便直插封装(PDIP)是上世纪80年代普遍使用的封装形式,它有一个矩形的塑封体,在矩形塑封体比较长的两侧面有双列管脚,两相邻管脚之间的节距是2.54mm,引线数为6-84,厚度约为2.0~3.6,如表2所示。

两边平等排列管脚的跨距较大,它的直插式管脚结构使塑封电路可以装在塑料管内运输,不用接触管脚,管脚从塑封体两面弯曲一个小角度用于插孔式安装,也便于测试或器件的升级和更换。

这种封装形式,比较适合印制电路板(PCB)的穿孔安装,具有比50年代的TO型圆形金属封装,更易于对PC B布线以及操作较为方便等特点。

这种封装适合于大批量低成本生产,便于自动化的线路板安装及提供高的可靠性焊接。

同时,塑料封装器件在尺寸、重量、性能、成本、可靠性及实用性方面也优于气密性封装。

大部分塑封器件重量大约只是陶瓷封装的一半。

例如:14脚双列直插封装(DIP)重量大约为1g,而14脚陶瓷封装重2g。

但是双列直插封装(DIP)效率较低,大约只有2%,并占去了大量有效安装面积。

CQFP器件焊点开裂失效分析_张伟

CQFP器件焊点开裂失效分析_张伟CQFP器件焊点开裂失效分析张伟,孙守红,孙慧,韩振伟(长春光学精密机械与物理研究所吉林长春 130033)摘要:CQFP器件由于其可靠性⾼的优势已经⼴泛应⽤于军事、航天航空领域,但是在实际使⽤中,特别是在温度和⼒学条件下容易出现焊点脱落和引脚断裂等问题。

针对在⼯作中遇到的⼀次典型焊点开裂失效案例进⾏分析,对问题产⽣的根源进⾏了定位,对焊点开裂的失效机理进⾏了分析,最后简要介绍了提⾼CQFP器件焊接可靠性的⼀些⼯艺措施。

关键词:CQFP;可靠性;失效分析中图分类号:TN6 ⽂献标识码:A ⽂章编号:1001-3474(2012)06-0347-04Failure Analysis for Solder Joint Cracking of CQFP DevicesZHANG Wei, SUN Shou-hong, SUN Hui, HAN Zhen-wei(Changchun Institute of Optics, Fine Mechanics and Physics, Chinese Academy of Sciences, Changchun 130033, China) Abstract: CQFP devices has been widely used in military and aerospace field due to its advantages of high reliability, but in actual situation, especially in temperature, mechanical solder joints under the conditions prone to fall off, pin breakage and other issues. Based on a typical case of solder joint cracking failure, analyze root cause of the problem, and finally some process measures to improve the reliability of CQFP have been introduced.Key words: CQFP; Reliability; Failure analysisDocument Code: A Article ID: 1001-3474(2012)06-0347-04陶瓷四⾯扁平封装器件CQFP(Ceramic Quad Flat Pack)是⼀种先进的器件封装形式,采⽤了陶瓷基板和镀⾦引线,如图1所⽰,具有很⾼的可靠性,⼴泛应⽤于军事和航空航天印制板组装领域[1,2]。

封装标准JEDEC标准

半导体封装根据不同的用途,半导体的封装可以分为多种类型。

半导体的封装标准包括 JEDEC 和JEITA 标准,但有许多来自不同半导体制造商的封装不属于上述标准。

另外,JEDEC 和JEITA 这两种标准的名称也并非总是被用于制造商的产品目录和数据表中,除此以外,不同制造商之间的描述系统也不统一。

本页提供关于以下半导体封装描述规则的基本信息。

• 对那些明显具有相同封装的产品必须尽可能提供统一的一般性描述;如DIL →DIP 等。

• 如果制造商无法使用通用的名称,或者如果封装类型是众所周知的情况,则可使用制造商的描述;如PENTAWATT 等。

•作为一般性规则,必须在封装描述之后加上标有指示针脚数量的数字;如DIP24、SOT23-5等。

注:本页中所提供的信息仅供参考。

请在使用前确认制造商数据表中的所有数据。

DIP主要分类 主要分类说明 次级分类 次级分类说明有时也称为“DIL”,但在本网站上,它们被统称为“DIP”,是指引脚从封装的两侧引出的一种通孔贴装型封装。

尽管针脚间距通常为2.54毫米 (100密耳),但也有些封装的针脚间距为1.778毫米 (70密耳)。

DIP 拥有6-64个针脚,封装宽度通常为15.2毫米(600密耳)、10.16毫米(400密耳)、或7.62毫米(300密耳),但请注意,即使针脚数量相同,封装的长度也会不一样。

DIP(双列直插式封装) 塑料DIP 封装。

有时也称为“PDIP”,但在本网站上它们被统称为“DIP”。

CDIP(陶瓷DIP) 陶瓷DIP 封装。

有时也称为“CERDIP”,但在本网站上它们被统称为“CDIP”。

WDIP(窗口DIP)一种带有消除紫外线的透明窗口的DIP 封装,通常是一种使用玻璃密封的陶瓷封装。

不同制造商的描述可能会有所不同,但ST (ST Microelectronics )公司称之为“FDIP”。

在本网站上,它们被统称为“WDIP”。

功率DIP 能够通过引脚散除IC 所产生的热量的一种DIP 封装类型。

芯片常用封装及尺寸说明

A、常用芯片封装介绍来源:互联网作者:关键字:芯片封装1、BGA 封装(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配 LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚 LSI 用的一种封装。

封装本体也可做得比 QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚 BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚 QFP 为40mm 见方。

而且 BGA 不用担心 QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为 1.5mm,引脚数为225。

现在也有一些 LSI 厂家正在开发500 引脚的 BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国 Motorola 公司把用模压树脂密封的封装称为 OMPAC,而把灌封方法密封的封装称为 GPAC(见 OMPAC 和 GPAC)。

2、BQFP 封装(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和 ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见 QFP)。

3、碰焊PGA 封装(butt joint pin grid array)表面贴装型 PGA 的别称(见表面贴装型 PGA)。

4、C-(ceramic) 封装表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷 DIP。

我国引线框架的生产情况

我国引线框架的生产情况我国内引线框架生产企业主要集中在长三角、珠三角,随着国外大封装测试厂家在中国境内投资办厂,国内引线框架的需求也将有迅速增长。

国内引线框架主要企业介绍如下:(1)先进半导体物料科技有限公司(ASM Assembly Materials Limited)ASM 于 1968 年成立,公司总部位于荷兰的比尔托芬,是一家跨国公司,拥有雄厚的技术基础,ASM 公司主要生产半导体用设备和材料,是全球 15 家顶级半导体设备制造商之一。

在美国、日本、香港、中国、新加坡、马来西亚都设有分公司。

在深圳设有分公司,生产引线框架。

(2)深圳赛格高技术投资股份有限公司(SHIC)公司与德国、荷兰柏狮(POSSEHL)电子集团合资兴办深圳赛格柏狮电子有限公司(PSE),注册资本 1104.36 万美元,主营半导体集成电路引线框架、半导体精密模具制造等业务,产品畅销海内外。

(3)铜陵丰山三佳微电子有限公司公司是由韩国丰山微电子株式会社与三佳电子集团有限责任公司共同投资2000 万美元建立的一家高科技企业,韩国丰山公司以技术、设备和资金入股,占51%的股份,三佳集团以厂房、设备和资金入股,占 49%的股份。

公司引进国际先进的技术和生产装备,生产 IC、TR 类引线框架和硬质合金级进冲模具,已建成年产 40 亿只引线框架的规模。

(4)三井高科技(上海)有限公司三井高科技(上海)有限公司、三井高科技(天津)有限公司、三井高科技电子(东莞)有限公司都是日本三井高科技股份公司在中国大陆独资开设的三家分立器件及集成电路引线框架、高精度马达转子定子叠片的专业生产厂家。

是专业生产集成电路引线框架,高精度金属模的企业,也是目前国内唯一具有 240 只脚 IC 引线框架生产能力的生产厂家,包括照相蚀刻 IC 引线框架、密冲压 IC 引线框架。

三井高科技(上海)有限公司成立于 1996 年 3 月,1998 年 6 月开始批量生产。

电子元器件的封装

电子元器件的封装1947年晶体管出现之后,其封装的设计随之展开,最早的一批晶体管封装的型号是以TO开头的。

曾经有过一种有着特定的工业或军事应用的金属壳多极管封装TO-39(见图5),有现在最常见的塑料三极管封装TO-92(见图6),还有电子爱好者常用的直插式稳压芯片LM7805所使用的TO-220封装(见图7),还有直引脚贴片式封装的TO—89(见图8),TO 系列封装几乎一统天下了。

1958年美国德州仪器公司(TI)工程师杰克.基尔比发明了集成电路,一些集成电路芯片还仍然使用TO系列封装,但随着集成电路晶片面积越来越大、引脚越来越多,TO封装已经吃不消了。

于是20世纪70年代出现了新的封装设计——双列直插封装(DP)(见图9),我花了好长时间搜索DIP封装的发明者或研发它的公司,可是什么也没找到就连DIP封装发明的准确日期也没找到。

乍看DIP封装好像是一只多脚虫,引脚间距为2.54mm,引脚数量可以从6个到64个,一般用“DIP”字样加上引脚数量表达封装形式,如“DP20”就是有20个引脚的DIP封装。

安装在带有过孔的PCB板上。

从下面这张DIP封装的图片上可以看到;封装中间是集成电路晶片,晶片周围用很细的金属导线把晶片上的接口电极导到封装外的引脚上。

DIP封装有陶瓷和塑料两种封装材料;DP封装坚固可靠,英特尔公司最早生产的4004、8008处理器均采用了DIP封装。

DIP封装一出现几乎就统治了市场,几乎所有的直插式芯片都有DIP封装的产品,直到现在我们还在使用着,你手边的40脚的51单片机就是DIP40封装的。

另外还有一种不常用的芯片封装叫SIP,意思是单列直插封装,现在几乎看不到了,大家知道一下就行了。

DIP封装好是好,可就是太大了,当用于小型手持设备时,DIP封装就显得笨拙了,于是飞利浦公司开发出了SOP小外型封装。

SOP封装(见图10)引脚间距为1.27mm,引脚数在8~44脚,SOP属于表面贴装元器件,无需过孔,可以直接焊在印制电路板表面。

集成电路芯片封装技术第1章

(50~90)%

封装效率

封装效率

=2-7%(1970-) =10-30%(1980-)

封装效率

=20-80%(1990-)

封装效率

=50-90%(1993-)

封装效率的改进

35

表2.封装厚度的变化

封装形式

封装厚度

(mm)

PQFP/PDIP TQFP/TSOP UTQFP/UTSOP

解决途径:

1、降低芯片功耗:双极型-PMOS-CMOS-???

2、增加材料的热导率:成本

微电子技术发展对封装的要求

三、集成度提高 适应大芯片要求

热膨胀系数(CTE)失配—热应力和热变形

解决途径:

1、采用低应力贴片材料:使大尺寸IC采用CTE接近

Si的陶瓷材料,但目前环氧树脂封装仍为主流

2、采用应力低传递模压树脂 消除封装过程中的热应

目的

使各种元器件、功能部件相组合形成功能电路

难易程度

依据电路结构、性能要求、封装类型而异

需考虑的问题

ห้องสมุดไป่ตู้保护

苛刻的工程条件(温度、湿度、振动、冲击、放射性等)

超高要求

超高性能 (3D IC)

超薄型、超小型

超多端子连接

超高功率(采用热冷、金属陶瓷复合基板等)

电子封装实现的四种功能

① 信号分配:

② 电源分配:

何将聚集的热量散出的问

题

封装保护

芯片封装可为芯片和其他连

接部件提供牢固可靠的机械

支撑,并能适应各种工作环

境和条件的变化

确定封装要求的影响因素

成本

电路在最佳

性能指标下

的最低价格

外形与结构

28种芯片封装技术的详细介绍

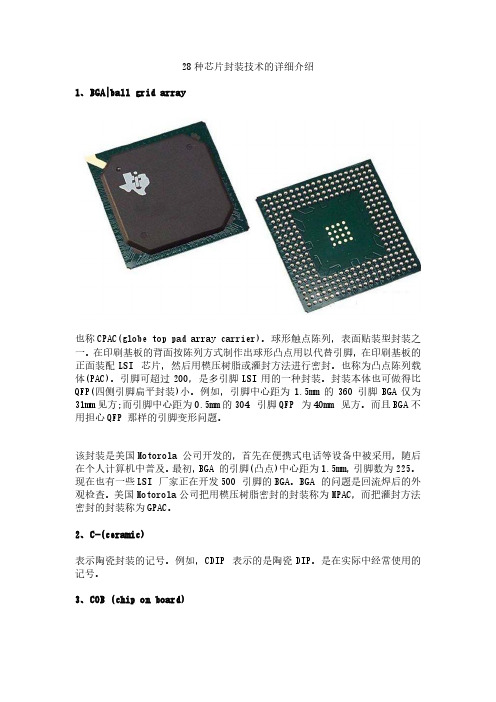

28种芯片封装技术的详细介绍1、BGA|ball grid array也称CPAC(globe top pad array carrier)。

球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm的360引脚BGA仅为31mm见方;而引脚中心距为0.5mm的304 引脚QFP 为40mm 见方。

而且BGA不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,随后在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

美国Motorola公司把用模压树脂密封的封装称为MPAC,而把灌封方法密封的封装称为GPAC。

2、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

3、COB (chip on board)COB (chip on board)板上芯片封装,是裸芯片贴装技术之一,半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可靠性。

虽然COB 是最简单的裸芯片贴装技术,但它的封装密度远不如TAB和倒片焊技术。

4、DIP(dual in-line package)DIP(dual in-line package)双列直插式封装。

插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。

欧洲半导体厂家多用DIL。

DIP 是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目前 的形式来看 ,虽然集 成电路O ) c封装 工业似乎正

把注意力集 中于无 引脚封装 的发展(  ̄ B A Q N 诸 IG 与 F 3 等) ,但是 引脚 产 品 ,特 别是方形 表面贴装封装 器件

仍然在I 市场上扮演重要 的角色 ,更 应值得一提 的是 C

图1集成 电路 引线成形前后图示 .

sine, h n cu 3 0 3 C ia c cs C a g h n1 0 3 , hnl e

A s r c : a - r n h s po e so a k g , u lyo h a - r n ld e t fe t h l b i b ta t C l df mi i t el t rc s f C p c a e q ai f e I l df migwi i c l a fc er i i y l e o gs a I t t Ce o l r y t ea l t

摘 要 :集成 电路引线成形 原本是集 成电路封装 的后道工序 ,成形质量将 直接影 响电子 装联产 品的可靠 性 ,其关 键工艺点在 于成形 的肩宽 、站高 、焊接长 度和共 面度等关键工艺参数的选择以及 成形工艺装备 的合理

配置与优化 。论述 了目前表面贴装密脚间距 Q P F 封装器 件在应用 中遇 到的引线成形 问题 ,介绍 了该类器件成形 中的相关技术要求及 目前国内外器件成形的现状 ,提出了引线手工成形的解 决方案 。

o l toi asmb rdcs tekyp itstesl t no eh o g aa tr a o t hud regh Sa dof F o fe crn se l po u t h e o h e ci f cn l yprmees b u o le l t, tn f o t e c y , ni e o t o s n , ln t, o ln rya dtera o al al aina do t i t no rc s q imet T epo l fe dfr n bu e gh c p ai n h e sn be lc t n pi z i f oe se u a t o o m ao p p n. h rbe o a - mi a o t ms l o g

关键词 : 密脚间距 ;引线成型 ;封装 ;肩宽 ;站高

中图分类号: N 0 T 4 5文献 标识码: 文章编 号:0 1 37 ( 1) — 3 1 0 A 10— 4 42 0 6 04 — 5 0 0

S u yo e df r n e h oo yf r ie t d fL a - mi gT c n lg o Fn - o

D c me t o e A ril l : 0 13 7 (000 .3 10 o u n d : A t e D 10 .4 42 1)60 4 .5 C c

2 世 纪9 年 代 以来 ,随 着 电 子技 术 的不 断 进 0 0 步 ,半 导体封 装技术 得到 了很 大 的发展 ,尤其 是高 可靠性产 品高性 能化 和小 型化 的要 求更 加促进 了高 密度 、高集成 化I 芯 片封装技 术 的发展 ,使得 大规 c 模 集成电路在电子学系统 中得到 了广泛 的应用 _ 1 _ ,从

21年 sT c n lg lc r n c r c s e h oo y 31 4

密脚 间距 QF 集成 电路 引线成形工艺研究 P

干 龙 ,孙 守 红

( 中国科学院长春光学精密机械与物理研 究所 ,吉林 长春 10 3 3 0 3)

以下几点 :首先 ,高 端器件 大多配 有适 配器 ,设 计 者 可根据 实 际需 求在 不进行 焊接 的前提 下进行 程序

烧 录和模 拟仿 真等试 验 ;其 次 ,该 类芯 片的 出现给

设计者在P B C 设计过程 中留有较大 的选择空间 。这就

集成 电路引脚 的切筋 打弯 工作原本 应是 集成 电路封 装 的后道 1序 ,但事 实上越来 越 多的未经 过引 线成 二 形 的集成 电路进 入到用 户手 中 。其 主要原 因分 析有

s raemo n iep c F eiei tea pc t nweed c s e . h eea ttc nc le urme t n ttso ufc utF .i hQ Pd vc n h p l ai r i u sd T erl n eh i q i nsa dsau f n t i o s v ar e

p t h QF ic P

WANG ul n , Y ・ g SUN S o ・ o g o h uh n

l h n c u s i t f p i , ie c a i n h sc ,hn s c d myo C a g h n n t u e t s F Me h nc a d y is i e a e f I t oO c n s P C e A

d met n train l b u u hdvcsl dfr igweei rd cd A h a et , u owads l in f a d o si a di en t a a o t c eie a - mn r t u e . ttes m i p tfr r ou o so n c n o s e o no me t h la - r n . e df mig o K ywod : ie i h La- r n ; ak g;o yl gh Sa dof e rs F - t ;e df mig P ca eB d n t; tn f n pc o e