折叠式共源共栅运算放大器的设计报告

折叠共源共栅放大器的偏置电路

折叠共源共栅放大器的偏置电路折叠共源共栅放大器是一种在射频放大器中常用的电路配置。

它的优点在于高增益、低功耗以及良好的频率响应特性。

本文将对折叠共源共栅放大器的偏置电路进行详细介绍,以期帮助读者更好地理解和应用这一电路配置。

首先,让我们了解一下什么是折叠共源共栅放大器。

折叠共源共栅放大器是一种双管式场效应管放大电路,由一个共源级和一个共栅级组成。

其中,N沟道MOSFET管作为共源级,P沟道MOSFET管作为共栅级。

这种配置的结构有助于提高电路的增益和带宽,并减少功耗。

接下来,我们来讲解一下折叠共源共栅放大器的偏置电路。

偏置电路是为了确保放大器工作在合适的工作点,提供适当的电压和电流,以保证其输入和输出信号的线性放大。

在折叠共源共栅放大器中,偏置电路的主要作用是为共源级和共栅级提供合适的静态工作点。

通常,折叠共源共栅放大器的偏置电路由电阻、电流源和电压源组成。

偏置电路的设计需要考虑到静态工作点的稳定性、功耗以及适应频率响应的要求。

在具体的偏置电路设计中,首先确定共源级和共栅级的工作电流,然后根据电路的需要,选择恰当的电流源和电阻来提供所需的电流和电压。

在选择电源时,需要考虑到电源电压的稳定性和噪声特性。

根据需求,可以选择直流耦合和交流耦合的方式来连接共源级和共栅级。

在折叠共源共栅放大器的偏置电路中,还需要注意的是温度的影响。

由于温度会对电子元件的特性产生影响,因此需要考虑到温度变化对偏置电路的稳定性和性能的影响。

可以采取一些温度补偿的措施,如使用温度补偿电阻、温度补偿电压源等,以保持电路的稳定性。

总结起来,折叠共源共栅放大器的偏置电路在射频放大器中起着至关重要的作用。

通过合理设计偏置电路,可以保证放大器的性能和稳定性。

因此,了解和掌握折叠共源共栅放大器的偏置电路对于从事射频电路设计和应用的工程师来说是非常重要的。

希望本文所介绍的内容能够对读者有所启发和指导,让大家能够更好地理解和应用折叠共源共栅放大器的偏置电路。

采用折叠式结构的两级全差分运算放大器的设计

目录1. 设计指标 (1)2. 运算放大器主体结构的选择 (1)3. 共模反馈电路(CMFB)的选择 (1)4. 运算放大器设计策略 (2)5. 手工设计过程 (2)5.1 运算放大器参数的确定 (2)5.1.1 补偿电容Cc和调零电阻的确定 (2)5.1.2 确定输入级尾电流I0的大小和M0的宽长比 (3)5.1.3 确定M1和M2的宽长比 (3)5.1.4确定M5、M6的宽长比 (3)5.1.5 确定M7、M8、M9和M10宽长比 (3)5.1.6 确定M3和M4宽长比 (3)5.1.7 确定M11、M12、M13和M14的宽长比 (4)5.1.8 确定偏置电压 (4)5.2 CMFB参数的确定 (4)6. HSPICE仿真 (5)6.1 直流参数仿真 (5)6.1.1共模输入电压范围(ICMR) (5)6.1.2 输出电压范围测试 (6)6.2 交流参数仿真 (6)6.2.1 开环增益、增益带宽积、相位裕度、增益裕度的仿真 (6)6.2.2 共模抑制比(CMRR)的仿真 (7)6.2.3电源抑制比(PSRR)的仿真 (8)6.2.4输出阻抗仿真 (9)6.3瞬态参数仿真 (10)6.3.1 转换速率(SR) (10)6.3.2 输入正弦信号的仿真 (11)7. 设计总结 (11)附录(整体电路的网表文件) (12)采用折叠式结构的两级全差分运算放大器的设计1. 设计指标5000/ 2.5 2.551010/21~22v DD SS L out dias A V VV V V VGB MHz C pF SR V s V V ICMR V P mWµ>==−==>=±=−≤的范围2. 运算放大器主体结构的选择图1 折叠式共源共栅两级运算放大器运算放大器有很多种结构,按照不同的标准有不同的分类。

从电路结构来看, 有套筒式共源共栅、折叠式共源共栅、增益提高式和一般的两级运算放大器等。

共源共栅运算放大器的设计

共源共栅运算放大器的设计共源共栅运算放大器,也称为共源共栅放大器或共栅源跟随器,是常用的运算放大器电路结构。

它由共源放大器和共栅放大器组成,可以提供高增益、宽带宽并具有高输入电阻和低输出阻抗的特点。

下面将详细讨论共源共栅运算放大器的设计。

设计目标:1.高增益:希望放大器具有高增益,以提供较大的放大倍数。

2.宽带宽:希望放大器具有较宽的频带,以传输更高频率的信号。

3.高输入电阻:希望放大器具有较高的输入电阻,以不对被测电路产生影响。

4.低输出阻抗:希望放大器具有较低的输出阻抗,以不对后级电路产生影响。

设计步骤:1.选择晶体管:选择性能良好、参数稳定的晶体管作为放大器的关键部件。

常用的晶体管有MOSFET和JFET,选用适合的型号,使其性能满足设计的要求。

2.偏置电路设计:根据晶体管的工作条件,设计偏置电路以保证放大器的工作稳定性。

通常采用电流源和电阻网络来实现晶体管的偏置。

3.增益极化设计:确定放大器的增益级数和增益大小,并选择适当的分压比例和电阻值,使得输出电压能够满足要求。

同时考虑增益的稳定性,防止输出波形失真。

4.频率补偿设计:由于共源共栅放大器的频率响应受到极点和零点的影响,需要设计频率补偿电路来提高带宽。

常用的频率补偿方法有米勒补偿电容和并联补偿电容等。

5.输入和输出阻抗设计:通过选择合适的电路参数和组件数值,使得输入电阻和输出电阻达到所需的要求。

一般采用反馈电阻网络来实现输入和输出阻抗的调节。

6.功耗和温度设计:考虑到功耗和温度对放大器性能的影响,需要进行功耗和热量分析,并选择适当的散热器来保证放大器的长期稳定工作。

7.电源设计:根据放大器的电源需求,选择适当的电源电压和电源过滤电路,以保证放大器的工作正常和稳定性。

以上是共源共栅运算放大器的设计步骤。

在设计过程中,需要综合考虑各种因素,并根据具体的应用场景和要求进行优化。

通过合理的设计和调试,可以获得性能良好的共源共栅运算放大器。

采样保持电路中全差分运算放大器的设计与仿真

采样保持电路中全差分运算放大器的设计与仿真采样保持电路中全差分运算放大器的设计与仿真1 引言运算放大器是许多模拟系统和混合信号系统的一个完整部分,伴随着每一代CMOS 工艺,由于电源电压和晶体管沟道长度的减小,为运算放大器的设计不断提出新的挑战。

在采样保持电路的设计中,运算放大器是最关键的模块之一,其带宽,摆率,增益,噪声,失调等性能直接决定了采样保持电路模块的速度,精度等性能。

2 折叠共源共栅结构电路结构。

图1 折叠共源共栅运算放大器运算放大器采用折叠共源共栅结构,采用NMOS 输入差分对MN1 和MN2。

MN0 为输入差分对的尾电流源,向MN1 和MN2 提供直流偏置。

MP1 和MP2 为电流源,向输入管和共源共栅管提供直流偏置。

MP3 和MP4 为共源共栅管,用来提高运算放大器的增益。

MN3,MN4,MN5 和MN6 是共源共栅电流镜负载,采用共源共栅结构可以提高输出阻抗。

与套筒式结构相比,折叠共源共栅结构放大器输出摆幅增大了一个过驱动电压,另外较大的共模输入范围是我们选择折叠共源共栅结构的主要原因。

3 开关电容共模反馈(CMFB)电路由于采用全差分结构,而在高增益的全差分运算放大器中,输出共模电平对器件的特性和适配相当敏感,而且不能通过差模反馈来达到稳定,因此设计时增加了共模反馈电路模块,来稳定输出共模电平。

共模反馈电路。

共模反馈电路与主运放的连接。

图 2 共模反馈电路该结构与电阻检测方式,运用MOSFET 作为源级跟随器和可变电阻的检测技术相比有明显优点。

其工作流程如下,时钟信号在Φ1 相位时,为C1 充电,确定C1 两端的电压,在Φ2 相位时,将C1 与C2 并联,根据Vo1 和Vo2 平均值的大小确定输出共模电平。

例如,(Vo1+Vo2)/2>VREF,则输出共模电平cmctl bias v > v ,从而使尾电流减小,最终导致输出(Vo1+Vo2)/2 减小,连续几个周期调整后,将使(Vo1+Vo2)/2≈Vref。

一种低压低功耗CMOS折叠-共源共栅运算放大器的设计

一种低压低功耗CMOS折叠-共源共栅运算放大器的设计程春来,柴常春,唐重林【摘要】设计了一种低压低功耗CMOS折叠-共源共栅运算放大器。

该运放的输入级采用折叠-共源共栅结构,可以优化输入共模范围,提高增益;由于采用AB类推挽输出级,实现了全摆幅输出,并且大大降低了功耗。

采用TSMC 0.18 μm CMOS工艺,基于BSIM3V3 Spice模型,用HSpice对整个电路进行仿真,结果表明:与传统结构相比,此结构在保证增益、带宽等放大器重要指标的基础上,功耗有了显著的降低,非常适合于低压低功耗应用。

目前,该放大器已应用于14位∑-Δ模/数转换电路的设计中。

【期刊名称】现代电子技术【年(卷),期】2007(030)024【总页数】4【关键词】运算放大器;折叠-共源共栅;AB类输出;低压低功耗1 引言在生物科学、空间技术、电池供电设备以及各种高阻抗传感器的应用中,经常需要集成电路在低电压和弱电流的条件下工作[1]。

采用低电压供电的模拟电路不但能减少电路的功耗,而且能增强电路的稳定性[2]。

因此,低功耗乃至在微功耗芯片的研制和生产日益得到研究机构和生产部门的关注。

运算放大器是模拟电路中最重要和最通用的单元电路之一,同时也是许多模拟系统和数模混合信号系统中的一个完整模块[3]。

随着CMOS工艺的不断进步,电源电压和特征尺寸持续减小,运放的设计己经成为模拟IC设计中的制约因素之一,设计方法也面临着挑战。

为适应低压低功耗的设计要求,本文基于超深亚微米工艺,设计一个低压低功耗的CMOS折叠-共源共栅运算放大器单芯片,在讨论运放的工作原理及特点的基础上,采用TSMC 0.18 μm CMOS工艺,基于BSIM3V3 Spice模型,用HSpice对整个电路进行仿真。

结果表明:与传统结构相比,此结构在保证增益、带宽等放大器重要指标的基础上,功耗有了显著的降低,非常适合于低压低功耗应用。

目前,该放大器已在14位∑-Δ模/数转换电路的设计中得到应用。

共源共栅放大器实验报告材料

实验名称:共源共栅放大器设计实验目的:1.了解共源共栅级放大器的基本工作原理及相关优缺点2.学会CMOS电路中的基本参数的设计和分析参数之间的折中关系3. 共源共栅放大器设计及仿真实验设备及型号:orcd仿真软件实验原理及实验步骤:实验原理:共栅级的输入信号可以是电流,共源级可以可以将电压信号转换为电流信号。

共源共栅级的级联叫做共源共栅结构。

共源共栅级的输出阻抗很高通过计算Rout可得Rout约=(gm1+gmb2)r o2r o1也就是说M2将M1的增益提高至原来的(gm1+gmb2)r o2倍其还可以扩展为三个或多个以获得更高的输出电阻但这需要额外的电压余度共源共栅结构不仅可以作为放大器而且可以作为恒定电流源高的输出阻抗接近一个理想电流源本次需要仿真的pmos 共源共栅负载的nmos 共源共栅放大器即是如此。

在某种意义上,共源共栅晶体管结构“屏蔽”输入器件使它不受输出节点电压变化的影响。

这种共源共栅结构屏蔽特性在许多电路中是非常有用的 实验步骤:由于共源共栅放大器的电路图已给出,所以电路设计省略 2.按所给设计图绘制相应电路图所得电路图如下0.65FREQ = 1kVAMP VOFF = 03.根据题目要求先对其进行相应仿真 1)设置静态工作点和器件参数。

如此处静态输出电压Vout=3v Vcc=6v Vb1=5.13v Vb2=4.88v Vb3= 0.904v 等2):设定静态电流。

①设定长L=2u②调试WL主要是调试W,要使静态电流为100uA,L固定以后,就调节W来达到需要的电流。

此处用快速扫描的方法来调试出所需W的大小待所需各个管的w值扫描出后③bias point 仿真检验电流i是否达到要求。

3)根据题目要求进行相应的交流仿真。

以下是相关的扫描实验数据扫描w的值测得MN1 管w的值为104.5u测得MN2 管w的值为92.7u注:此时测得的MN2管w的值是加了一个稳定电压Va=0.25v的当没加Va时测得MN2 管w的值为90.1u测得MP2 管w的值为179.5u测得MP1管w的值为205ubias point 仿真检验。

运算放大器实验报告---修改版

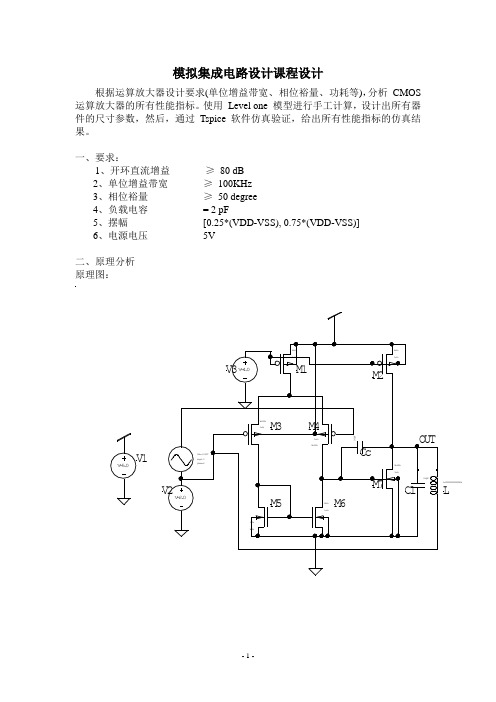

模拟集成电路设计课程设计根据运算放大器设计要求(单位增益带宽、 相位裕量、 功耗等),分析 CMOS 运算放大器的所有性能指标。

使用 Level one 模型进行手工计算,设计出所有器件的尺寸参数,然后,通过 Tspice 软件仿真验证,给出所有性能指标的仿真结果。

一、要求:1、开环直流增益 ≥ 80 dB2、单位增益带宽 ≥ 100KHz3、相位裕量 ≥ 50 degree4、负载电容 = 2 pF5、摆幅 [0.25*(VDD-VSS), 0.75*(VDD-VSS)]6、电源电压 5V二、原理分析 原理图:LV 1V 00000000000000V =5.0实验原理:电路选用二级米勒补偿,其中一级放大主要是放大增益,二级是放大摆幅,将电路分三部分来看左边:用直流电压为m1,m2提供偏置电压中间:m3,m4,m5,m6,m1一路选用差分放大电路作为一级放大 右边:m2,m7一路是提高输出摆幅电路部分 Cc 为补偿电容,而电感L 起稳压作用 为达到设计指标,对运算放大器的每个moS 管都要在饱和区工作,通过对原理图的小信号分析得到这种结构的增益为Gain = gm1×gm6/(gds2 + gds4)/(gds6 + gds7)表示,其中gds2 , gds4, gds6 , gds7,分别为M2,M4,M6,M7管的相关电导。

gm1,gm6分别M1、M6的跨导。

而输出电压摆幅为Vincm.max=Vdd-|V GS3|+Vthn ,Vincm.min=V od5-V GS1=V od5+V od1+Vthn1,其中Vod1、Vod5分别为M1和M5的过驱动电压。

21()(1)2D n ox GS TH DS WI C V V V Lμλ=-+2()112()()D m n oxGS TH DS GS THDDDSGS TH on n oxGS TH I W g C V V V L V V I L I V V V R WC V V Lμγλγμ=-==-∝-=-饱和饱和=时三、设计步骤:1. 由已知的C L 并根据转换速率的要求(或功耗要求)选择I SS (I 9)的范围;2. 计算满足频率要求的R out 范围,否则,改变I SS ;3. 设计W 3/L 3( W 4/L 4)、W 5/L 5( W 6/L 6 )满足上ICMR (或输出摆幅)要求;4. 设计W 2/L 2 、 W 7/L 7满足增益要求;满足下ICMR (或输出摆幅)要求;5. 若达不到设计要求,重复上述过程。

增益增强共源共栅放大器的设

增益增强共源共栅放大器的设

本文设计了一种采用增益增强结构的带开关电容共模反馈的折叠式共源共栅跨导运算放大器,可用于流水线结构的A/D中。

出于对性能及版图因素的考虑,采用了单端放大器作为增益提高辅助放大器。

并通过改进共模负反馈电路,使得放大器输出共模反馈电压稳定更快,抖动更小。

本设计在Cadence环境下对运放的电路和版图进行了仿真。

结果表明,放大器的各项性能参数达到了理想的效果。

1 电路结构的分析与设计

CMOS跨导运算放大器常用结构有两级放大结构、套筒结构和折叠共源共栅结构等形式。

两级放大结构的运放电路结构虽然具有高增益、高摆幅等优点,但由于每一级至少引入一个极点,为了保障整个放大器的相频特性满足要求,需要额外的频率补偿电路,从而提升了放大器的电流和功耗,限制了放大器带宽,同时降低了放大器速度,因此不能满足本设计中对于运放带宽和速度的要求。

套筒式结构虽然具有较高的增益、较好频率特性及较低功耗,但是受到结构限制,其输出摆幅和共模输入范围小,不满足设计要。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.1折叠式共源共栅运算放大器的设计

电容改至1.8cp

静态工作点

3.2.5 运算放大器的仿真

1. 小信号低频电压增益分析

运放的小信号相频和幅频特性是仿真运放的开环小信号放大倍数,运放的放大倍数随频率的变化趋势;运放的相位随频率的变化趋势;运放的相位裕度;运放的单位增益带宽。

通过仿真这些特性来鉴别运放的放大能力,稳定性和工作带宽。

运放的输出端接2pF的负

载电容,在电源电压为5V ,共模输入电压为2.5V ,在运放输入端接差分交流信号1V ,两输入端的输入交流信号相位相反的条件下做交流小信号分析,可以得到运放的小信号相频和幅频特性如图(3.4)所示。

电路图连接如图3.3,仿真程序见附录1.1

2.5V

AC.1

图3.3 低频小信号特性仿真电路连接图

图3.4 低频小信号电压增益分析图

该运算放大器的小信号低频电压增益可以看出是112.793dB 。

满足设计指标。

2. 单位增益带宽

程序跟测量小信号低频电压增益时相同,仿真波形如图3.5所示。

该运算放大器的单位增益带宽可以看出100.927MHz.满足设计指标。

图3.5 低频小信号单位带宽分析图

3. 相位裕度仿真:

从图上看出相位裕度为180°-127°=53°,满足设计指标。

程序和测量小信号低频电压增益时相同。

仿真波形如图3.6。

图3.6 相位裕度分析图

4. 转换速率(slew rate)

运放的转换速率是分析运放在大信号作用下的反映速度。

仿真运放的转换速率可将运放的输出端和反相输入端相连构成单位增益结构。

运放的同相输入端输入2V到3V的

阶跃信号,利用仿真软件对该电路做瞬态分析得到的输出波形见图3.8,从仿真波形得到:在输出上升曲线的10%和90%处,其电压分别为2.9V和2.1V;时间分别为10.7ns和3.32ns。

运放的转换速率SR=(2.9V-2.1V)/( 10.7nS—3.32nS)=108.4 V/μs,满足运放的转换速率的指标要求。

电路图如图3.7仿真程序见附录1.2。

图3.7 仿真转换速率电路图

图3.8 转换速率分析图

5. 共模抑制比

运放的共模抑制比是测试运放对共模信号的抑制能力。

仿真方法是在运放的开环状态下,在运放的的同相和反相输入端同时加入一个幅度为1V的交流小信号源,对电路进行交流小信号分析,仿真结果如图(3.10)所示。

从仿真结果可得,运放的低频共模电压增益为-3.29dB。

因为运放的共模抑制比(dB为单位)等于其差模电压增益(dB)减去共模电压增益(dB),差模电压增益是95.7dB,所以运放的共模抑制比近似为98.99dB,大于运放的指标要求值。

电路图如图3.9, 仿真程序见附录1.3。

2.5V

图3.9 仿真共模抑制比电路图

3.10 共模抑制比分析图

6. 输入共模电压范围

运放的共模输入范围是运放的输入输出跟随特性。

运放的电源为5V,运放的反相端和输出相连,构成缓冲器;同相端加直流扫描从0到5V,经仿真得到的运放输入输出跟随特性如图(3.12)所示。

电路图如图3.11。

仿真程序见附录1.4。

图3.11 仿真输入共模电压范围电路图

7.电压输出范围

运放的输出电压摆幅特性是仿真运放的输出电压最大值和最小值[15]。

运放的输出电压摆幅特性仿真电路如图(3.13)所示。

电路图如图3.12.仿真程序见附录1.5。

10M

图3.13 运放的输出电压摆幅特性仿真电路

正输入端接2.5V的直流电压,Vin1 输入端加从0到5V的直流扫描电压,经仿真得到的运放输出电压摆幅特性见图(3.14)。

图3.14 电压输出范围分析图

从图上可以看出输出电压的范围是:0.0379V—4.99V,符合指标要求。

8.运放的静态功耗

运放的静态功耗是指当运放在输入平衡状态下电路消耗的总电流和总电压的乘积。

在电源电压5V,运放的两输入端输入共模电压2.5V时,运放各支路的静态电流之和为

3.268mA,则运放的静态功耗为16.34mW,小于指标的要求。