数电第四章 作业答案PPT课件

《数字电子技术基础》第四章习题答案

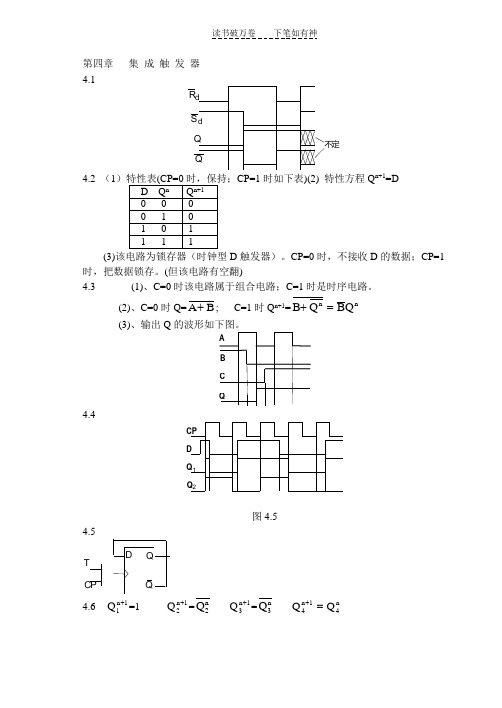

第四章 集 成 触 发 器 4.1R d S d Q Q不定4.2 (1CP=1时如下表)(2) 特性方程Q n+1=D(3)该电路为锁存器(时钟型D 触发器)。

CP=0时,不接收D 的数据;CP=1时,把数据锁存。

(但该电路有空翻)4.3 (1)、C=0时该电路属于组合电路;C=1时是时序电路。

(2)、C=0时Q=A B +; C=1时Q n+1=B Q BQ nn+= (3)、输出Q 的波形如下图。

A B C Q4.4CP D Q 1Q 2图4.54.5 DQ QCPT4.6 Q 1n 1+=1 Q 2n 1+=Q 2n Q n 13+=Q n 3 Q Q 4n 14n+=Q1CP Q2Q3Q44.7 1、CP 作用下的输出Q 1 Q 2和Z 的波形如下图; 2、Z 对CP 三分频。

DQ QCPQ1DQ QQ2ZRd CP Q1Q2Z14.8由Q D J Q KQ J Q KQ n 1n n n n +==+=⋅得D 触发器转换为J-K 触发器的逻辑图如下面的左图;而将J-K 触发器转换为D 触发器的逻辑图如下面的右图CPD Q QJKQ QDQ QJ KCP4.9CP B CA4.10CP X Q1Q2Z4.11 1、555定时器构成多谐振荡器 2、u c, u o 1, u o 2的波形u c u o 1u o 2t t t 1.67V3.33V3、u o 1的频率f 1=1074501316..H z ⨯⨯≈ u o 2的频率f 2=158H z4、如果在555定时器的第5脚接入4V 的电压源,则u o 1的频率变为1113001071501232....H z ⨯⨯+⨯⨯≈4.12 图(a)是由555定时器构成的单稳态触发电路。

1、工作原理(略);2、暂稳态维持时间t w =1.1RC=10ms(C 改为1μF);3、u c 和u o 的波形如下图:u ou ct t tu i (ms)(ms)(ms)5 10 25 30 45 503.33V4、若u i 的低电平维持时间为15m s ,要求暂稳态维持时间t w 不变,可加入微分电路4.13由555定时器构成的施密特触发器如图(a)所示 1、电路的电压传输特性曲线如左下图; 2、u o 的波形如右下图;3、为使电路能识别出u i 中的第二个尖峰,应降低555定时器5脚的电压至3V 左右。

数字电子技术第4章组合逻辑电路习题解答

习题4.1写出图所示电路的逻辑表达式,并说明电路实现哪种逻辑门的功能。

习题4.1图解:B A B A B A B A B A F ⊕=+=+= 该电路实现异或门的功能4.2分析图所示电路,写出输出函数F 。

习题4.2图解:[]B A B BB A F ⊕=⊕⊕⊕=)(4.3已知图示电路及输入A 、B 的波形,试画出相应的输出波形F ,不计门的延迟.图解:B A B A B A AB B AB A AB B AB A F ⊕=•=•••=•••=4.4由与非门构成的某表决电路如图所示。

其中A 、B 、C 、D 表示4个人,L=1时表示决议通过。

(1) 试分析电路,说明决议通过的情况有几种。

(2) 分析A 、B 、C 、D 四个人中,谁的权利最大。

习题4.4图解:(1)ABD BC CD ABD BC CD L ++=••=B AC & && & D L B A =1 =1=1FF A B & &&& & F B A(3)4.5分析图所示逻辑电路,已知S 1﹑S 0为功能控制输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。

习题4.5图解:(1)011011)(S S B S A S S B S A L ⊕⊕+⊕=⊕⊕•⊕= (2)4.6试分析图所示电路的逻辑功能。

习题4.6图解:(1)ABC C B A F )(++=10电路逻辑功能为:“判输入ABC 是否相同”电路。

4.7已知某组合电路的输入A 、B 、C 和输出F 的波形如下图所示,试写出F 的最简与或表达式。

习题4.7图解:(1)根据波形图得到真值表:C AB BC A C B A F ++=4.8、设∑=)14,12,10,9,8,4,2(),,,(m D C B A F ,要求用最简单的方法,实现的电路最简单。

1)用与非门实现。

2)用或非门实现。

3) 用与或非门实现。

数电第3-4章作业精品PPT课件

Y

M-A2 A-A1 B-A0

1

0 Y M ABC M ABC MABC

0

0 MABC MABC MABC

0

0 0

Y M ABC M ABC MABC

1 MABC MAB

0

0 0 1

D0 C

D3 C

0 1DΒιβλιοθήκη CD6 CD7 1

11

10

00 1 0 X

1X X 1 X

ML B

M S A BC

M L B M S A BC

A

MS

C

B

ML

4.10 解:

Z1 Z2

Y1 Y2

Y4 Y5

Y7 Y8

m1 m2

m4 m5

m7 m8

Z3

Y3

Y6

Y9

m3

m6

m9

Z1 m1 m4 m7

Z1 PQ

Z3 m3 m6 m9

Z3 PQ

MN

00

01

11

10

00 0 0 1 0

01 0 0 0 1

11 X X X X 10 0 1 X X

Z3 MQ N PQ NPQ

4.12试画出用3线-8线译码器74HC138和门电路产生 如下多输出逻辑函数的逻辑图。

YY21

AC ABC

ABC

BC

演讲人:XXXXXX 时 间:XX年XX月XX日

MN

00

01

11

10

00 0 1 0 0

01 1 0 1 0

11 X X X X 10 0 0 X X

Z2 m2 m5 m8

Z2 PQ

数字电子技术基础教材第四章答案

习题44-1 分析图P4-1所示得各组合电路,写出输出函数表达式,列出真值表,说明电路得逻辑功能。

解:图(a):;;真值表如下表所示:其功能为一位比较器。

A>B时,;A=B时,;A<B时,图(b):真值表如下表所示:功能:一位半加器,为本位与,为进位。

图(c):真值表如下表所示:功能:一位全加器,为本位与,为本位向高位得进位。

图(d):;;功能:为一位比较器,A<B时,=1;A=B时,=1;A>B时,=14-2 分析图P4-2所示得组合电路,写出输出函数表达式,列出真值表,指出该电路完成得逻辑功能。

解:该电路得输出逻辑函数表达式为:因此该电路就是一个四选一数据选择器,其真值表如下表所示:,当M=1时,完成4为二进制码至格雷码得转换;当M=0时,完成4为格雷码至二进制得转换。

试分别写出,,,得逻辑函数得表达式,并列出真值表,说明该电路得工作原理。

解:该电路得输入为,输出为。

真值表如下:由此可得:完成二进制至格雷码得转换。

完成格雷码至二进制得转换。

4-4 图P4-4就是一个多功能逻辑运算电路,图中,,,为控制输入端。

试列表说明电路在,,,得各种取值组合下F与A,B得逻辑关系。

解:,功能如下表所示,两个变量有四个最小项,最多可构造种不同得组合,因此该电路就是一个能产生十六种函数得多功能逻辑运算器电路。

4-5 已知某组合电路得输出波形如图P4-5所示,试用最少得或非门实现之。

解:电路图如下:4-6 用逻辑门设计一个受光,声与触摸控制得电灯开关逻辑电路,分别用A,B,C表示光,声与触摸信号,用F表示电灯。

灯亮得条件就是:无论有无光,声信号,只要有人触摸开关,灯就亮;当无人触摸开关时,只有当无关,有声音时灯才亮。

试列出真值表,写出输出函数表达式,并画出最简逻辑电路图。

解:根据题意,列出真值表如下:由真值表可以作出卡诺图,如下图:C AB 00 10 11 100 1由卡诺图得到它得逻辑表达式为: 由此得到逻辑电路为:4-7 用逻辑门设计一个多输出逻辑电路,输入为8421BCD 码,输出为3个检测信号。

数字电子技术课件第4章习题PPT(老版)

4-2、分析图中电路的逻辑功能,写出Yl、Y2的 逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

A B C Y1 Y2

Y1 ABC (A B C) AB BC AC ABC ABC ABC ABC

Y2 AB BC AC

逻辑功能: 为一全加器,Y1为和,Y2为进位 A B C Y1 Y2

4-1、分析图中电路的逻辑功能,写出输出的逻辑函数式, 列出真值表,说明电路逻辑功能的特点。

A B C Y

Y ABC ABC ABC ABC

逻辑功能:A,B,C有奇数个0 时输出为1

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

1 0 0 1 0 1 1 0

4-11、用8选1数据选择器产生逻辑函数 (A,B,C对应A2,A1,A0) 。

Y ACD A BCD BC BC D

C B A

4-12、用8选1数据选择器设计一个函数发生器电路, 它的功能表如下(S1,S0,A对应A2,A1,A0) 。

S1 S0 Y0 0 1 10 1 0 14-9、下图是用两个4选1数据选择器组成的逻辑电路, 试写出输出Z与输入M、N、P、Q之间的逻辑函数式。 已知数据选择器的逻辑函数式为

Y [ D0 A1 A0 D1 A1 A0 D2 A1 A0 D3 A1 A0 ] S

4-10、试用4选1数据选择器产生逻辑函数

Y AB C A C BC

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

0 1 1 0 1 0 0 1

0 0 0 1 0 1 1 1

数字电路逻辑设计第四章【可编辑PPT】

★74LS148 8-3线优先编码器 应用2

用编码器构成A/D转换器

图4.15为74LS148构 成的A/D转换器。这个 电路主要由比较器、寄 存器和编码器3部分组成。

输入信号(模拟电压), 同时加到7个比较器的反 相端,基准电源经串联 电阻分压为8级,量化单 位q=UR/7,各基准电压 分别加到比较器的同相 端。

Y S I0 N I1 N I2 N I3 N I4 N I5 N I6 N I7 N ST YEXYS ST

8线–3线优先编码器真值表如下表所示(反码形式)

输入

输出

ST IN 0 IN 1 IN 2 IN 3 IN 4 IN 5 IN 6 IN 7

Y 2 Y 1 Y 0 Y EX Y s

0 1 2 3 4 5 6 7 EN

HPRI/BIN 低位片

YS

Y0

Y1

Y2

YEX

0 1 2 3 4 5 6 7 EN

HPRI/BIN 高位片

YS

Y0

Y1

Y2

YEX

&

&

&

Y0

Y1

Y2

&

Y3

YEX

中规模优先编码器

常用的中规模优先编码器有: 8线-3线优先编码器:CT54148/CT74148、 CT54LS148/CT74LS148、CC4532 10线-4线优先编码器:CT54147/CT74147、 CT54LS147/CT74LS147、CC40147

74LS148是8-3线优先编码器

74LS148编码器功能表

输入

EI I7 I6 I5 I4 I3 I2 I1 I0

1 XXXXXXXX 0 1 1 1 1 1 11 1 0 0 XXXXXXX 0 1 0 XXXXXX 0 1 1 0 XXXXX 0 1 1 1 0 XXXX 0 1 1 1 1 0 XXX 0 1 1 1 1 1 0 XX 01111110X 011111110

数字电子技术第四章的PPT(徐丽香,第二版)ppt课件

Y=D0;当S1S0=01时,Y=D1;

当S1S0=10时,Y=D2;当

S1S0=11时,Y=D3。

ppt精选版

四路选择器 33

数据选择器在智能小区的应用

ppt精选版

34

端

传 送

0 1

(3).数据选择器和分配器的应用

000

由译码器连1 译码

0 pp禁t精选止版译码

如果A>B=0表示,则表示中断请求对象级别比现行处理的 事件级别低,比较器不发出中断信号,直到计算机处理完当 前的事件后再将现行状态寄存器中的状态清除,转向为别的 低级中断服务。

ppt精选版

40

4.6 加法器

4.6.1半加器 半加器可如组合逻辑电路分析的例3.1中介绍 的用与非门组成,也可以如图 (a)由异或门及 与门组成。

成电路来实现组合逻辑电路时,方法与使用小

规模集成电路基本一样。

ppt精选版

50

实验四 编码、译码和显示驱动电 路综合实验

一、实验目的

熟悉编码器、七段译码器、LED和数据选 择器等中规模集成电路的典型应用。

ppt精选版

51

二、实验仪器及器件

1.数字实验箱

2.BCD码(9~4线)优先编码器74HC147 1块

ppt精选版

41

4.6.2全加器

1.1位全加器

全加器的真值表

输入

输出

Ai

Bi

Ci

Si

Ci+1

全加器:进行加数、被加 0

0

0

0

0

数和低位来的进位信号相 0

0

1

1

0

加,并根据求和结果输出 0

1

0

1

《数电》教材习题答案 第4章习题答案

思考题与习题4-1 触发器的主要性能是什么?它有哪几种结构形式?其触发方式有什么不同?触发器是一种存储电路,具有记忆功能。

在数字电路系统中起着重要作用。

依据不同的标准,触发器可以划分为多种不同类型。

从结构上来分,触发器分为基本触发器,时钟触发器,主从触发器以及边沿触发器。

基本触发器为异步(或直接)触发,时钟触发器为CP电平触发,主从和边沿触发器为边沿触发。

4-2 试分别写出RS触发器、JK触发器、D触发器、T触发器和T′触发器的状态转换表和特性方程。

(略)4-3 已知同步RS触发器的R、S、CP端的电压波形如图T4-3所示。

试画出Q、Q端的电压波形。

假定触发器的初始状态为0。

图T4-34-4 设边沿JK触发器的初始状态为0,CP、J、K信号如图T4-4所示,试画出触发器输出端Q、Q的波形。

图T4-44-5电路如图T4-5(a)所示,输入波形如图T4-5(b)所示,试画出该电路输出端G的波形,设触发器的初始状态为0。

图T5-24-6 试画出图T4-6所示波形加在以下两种触发器上时,触发器输出Q的波形:(1)下降沿触发的触发器(2)上升沿触发的触发器图T4-64-7 已知A、B为输入信号,试写出图T4-7所示各触发器的次态逻辑表达式。

图T4-7nn n n n n n n nn n )b (n )a (Q B Q B Q Q B AQ Q Q B AQ Q K Q J Q B A D Q ⋅=+=++=⋅+=+=⊕==++11 4-8 设图T4-8所示中各TTL 触发器的初始状态皆为0,试画出在CP 信号作用下各触发的输出端Q 1-Q 6的波形。

图T4-84-9 试对应画出图T4-9所示电路中Q 1、Q 2波形。

(初始状态均为0)图T4-94-10 一逻辑电路如图T4-10所示,试画出在CP 作用下3210Y Y Y Y 、、、的波形。

(CT74LS139为2线—4线译码器。

)图T4-104-11由边沿D触发器和边沿JK触发器组成图T4-11(a)所示的电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

BIN/OCT

0

B0

1

1

B1

2

2

B2

4

3

4

1

&

5

EN 6

7

MUX

A0 A1

01}G

0 3

A2

1ST

EN

1D0 0

1D1 1

1Y

1 1D2 2 1D3 3

≥1

Y

2ST 2D0

2D1 2D2

2Y

2D3

74HC4539

图 题解4.23.

17

︷︷

︷︷

︷︷

︷︷

COMP

A0

0

A1 A2

1 2

A

A3

3

0 A>B A>B

3

F

0 A>B 1 A=B

A>B A=B

≥1

F

1

0

0 A<B A<B

0 1

1 2

B

0

3

1

0

0

18

.

19

f0

f1

f2

f3

f4

f5

f6

f7

≥1

&

&

&

&

&

&

&

A>B A=B A<B

︷A

A>B 0

︷A=B 1 B A<B 0

3210 3210

x3 x0 y3 y0

A>B A=B A<B

⑴ F (A ,B ,C ) m (2 ,4 ,5 ,7 ) ⑶ F(A ,B ,C )(AB )(BC )

D 0 D 1 D 3 D 6 0 ,D 2 D 4 D 5 D 7 1 D 0D 1D 4D 5D 71

D 2D 3D 60

.

9

F ( A ,B ,C ,D ) B C A C D A C D A B C D A B C D

(2) F3~F0=0100+0001+1= 0110. , CN+1=0 ,OVR=0

21

.

1

注意输出下标!!

.

2

.

3

F1(A,B,C,D)m(2,3,9,13) F2(A,B,C,D)m(1,3,5,7,9) F3(A,B,C,D)m(2,3,11,12)

F1(D,C,B,A)m(4,9,11,12) F2(D,C,B,A)m(8,9,10,11,12,14) F3(D,C,B,A)m(3,4,12,13)

MUX

0 1

A

EOY Y0

MUX

0

1A

Y1

1

Y2

图 题. 解4.11

13

.

14

.

15

.

16

4.23试用一片双4选1数据选择器74HC4539和一片3线-8线译码器 74138构成一个3位并行数码比较器。要求:电路输入为两个3位 二进制数,输出为1位,当输入两数相同时,输出为0,不同时 输出为1。数据选择器74HC4539功能表见图4.34(b)所示,译码器 74138功能表如表4.6所示。

.

4

F1(C,B,A)m(0,2,4,6)A F2(C,B,A)m(1,3,5,7)A

.

5

F1m(1,2,4,7)

F2m(3,5,6,7)

.

6

注意8421BCD码的 取值范围约束!!

.

7

.

8

4.9 试用8选1数据选择器74151实现下列逻辑函数。74151逻 辑符号如图4.37(a)所示。

A>B 0

︷A

︷A=B 1 B A<B 0

3210 3210

x3 x0 z3 z0 图 题解4.27

A>B A=B A<B

A>B 0

︷A

︷A=B 1 B A<B 0

3210 3210

y3 y0 z3 z0

.

20

(1) F3~F0=0100+1110+1=0011, CN+1=1,OVR=0

.

10

F ( A , B , C , D ) m ( 0 , 2 , 3 , 5 , 6 , 7 , 8 , 9 ) d ( 1 0 : 1 5 )

.

11

.

12

HPRI / BCD

X0

1

1

X1

2 (1) 2

X2

3

X3

4

EO

HPRI / BCD

X4

1

1

X5

2 (2) 2

X6

3

X7

4

EO

&

F

1 A=B A=B

0 A<B A<B

0

0

0 1

1 2

B

0

3

COMP

A0

0

A1 A2

1 2

A

A3

3

1 A>B

A>B

F

0 A=B

A=B

0 A<B

A<B

1

0

0 1

1 2

B

0

3

COMP

COMP

A0

0

A1 A2

1 2

A

A3

3

0 A>B A>B

1 A=B A=B 0 A<B A<B

1

A0

0

A1 A2

1 2

A

A3