《数字逻辑》作业

数字逻辑课程三套作业及答案

数字逻辑课程作业_A一、单选题。

1.(4分)如图x1-229(D)。

A. (A)B. (B)C. (C)D. (D)知识点:第五章解析第五章译码器2.(4分)如图x1-82(C)。

A. (A)B. (B)C. (C)D. (D)知识点:第二章解析第二章其他复合逻辑运算及描述3.(4分)N个触发器可以构成最大计数长度(进制数)为(D)的计数器。

A. NB. 2NC. N2次方D. 2N次方知识点:第九章解析第九章计数器4.(4分)n个触发器构成的扭环型计数器中,无效状态有(D)个。

A. A. nB.C. C.2n-1D. D.2n-2n知识点:第九章解析第九章集成计数器5.(4分)如图x1-293(A)。

A. (A)B. (B)C. (C)D. (D)知识点:第十一章解析第十一章数字系统概述6.(4分)如图x1-317(D)。

A. (A)B. (B)C. (C)D. (D)知识点:第二章解析第二章其他复合逻辑运算及描述7.(4分)EPROM是指(C)。

A. A、随机读写存储器B. B、只读存储器C. C、光可擦除电可编程只读存储器D. D、电可擦可编程只读存储器知识点:第十章解析第十章只读存储器8.(4分)如图x1-407(B)。

A. (A)B. (B)C. (C)D. (D)知识点:第十一章解析第十一章数字系统概述9.(4分)为实现将JK触发器转换为D触发器,应使(A)。

A. J=D,K=D非B. B. K=D,J=D非C. =K=DD. =K=D非知识点:第六章解析第六章各种触发器的比较10.(4分)一位8421BCD码计数器至少需要(B)个触发器。

A. 3B.C.D.知识点:第九章解析第九章计数器11.(4分)为把50Hz的正弦波变成周期性矩形波,应当选用(A)。

A. A、施密特触发器B. B、单稳态电路C. C、多谐振荡器D. D、译码器知识点:第六章解析第六章集成触发器12.(4分)下列描述不正确的是(A)。

詹瑾瑜数字逻辑练习题

詹瑾瑜数字逻辑练习题一、基本逻辑门(1) 与门(2) 或门(3) 非门(4) 异或门(1) A·A(2) A + A(3) A·A' + A·B(4) (A + B)'·(A + B)二、组合逻辑电路A |B | Y0 | 0 | 10 | 1 | 01 | 0 | 01 | 1 | 1(1) Y = A·B + C(2) Y = (A + B)'·C(1) Y = A·B + A·B' + A'·B(2) Y = (A + B)' + (A' + B')三、时序逻辑电路(1) SR触发器(2) D触发器(3) JK触发器当前状态 | 输入X | 下一个状态A | 0 | BA | 1 | CB | 0 | AB | 1 | DC | 0 | AC | 1 | BD | 0 | CD | 1 | D四、数字电路设计1. 设计一个38线译码器,并给出其真值表。

2. 设计一个4位二进制加法器,并说明其工作原理。

3. 设计一个序列检测器,检测序列为“1101”。

五、数字电路分析(1) 电路由两个与门、一个或门和一个非门组成,输入为A、B、C,输出为Y。

(2) 电路由一个42线优先编码器和一个24线译码器组成,输入为I0、I1、I2、I3,输出为Y0、Y1、Y2、Y3。

2. 给出一个数字时钟的原理框图,并简要说明其工作原理。

(1) 同步序列发生器(2) 异步序列发生器六、数字电路应用(1) 计算机处理器(2) 通信系统(3) 家用电器2. 举例说明数字电路在生活中的一个实际应用,并简述其工作原理。

七、数字电路故障诊断1. 列出数字电路常见的故障类型及其原因。

2. 描述如何使用逻辑笔进行数字电路的故障检测。

(1) 一个4位二进制加法器的输出始终为零。

(2) 一个38线译码器的某个输出始终为高电平。

数字逻辑第一次大作业

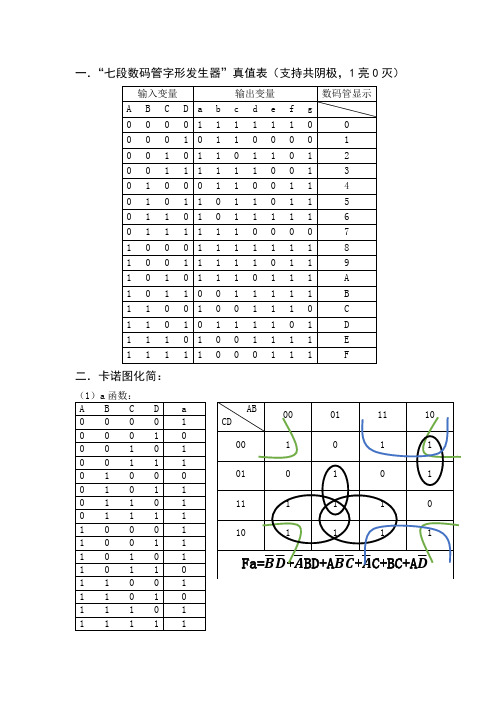

一.“七段数码管字形发生器”真值表(支持共阴极,1亮0灭)二.卡诺图化简:三.在Quartus 中,建工程,采用原理图设计方法,画整体电路图,设定I/O ,编译纠错第一次编译出错,Input与Output中部分名称重复,改Input中“A”为“In-A”,B、C、D同理。

第二次编译通过。

四.在Quartus中,对所设计的电路进行整体功能仿真:五.仅采用与非门实现的解决方案:根据摩根代换定律,将a~f的表达式改为与非式,在Quartus中重新用原理图的方法画出整体电路图,设定I/O,根据新表达式在电路中适当添加非门,编译纠错。

并对电路功能进行整体仿真。

六.支持共阳极数码管的解决方案:将a~f的输出信号按位取反。

即在各信号输出之前添加非门。

七.填写真值表:八.自定义三个4变量功能函数(不能重复前面的三变量函数功能),填写真值表:九.小结:首先明白了数码管工作原理后,通过写出a~f输出变量的表达式熟练了将真值表在卡诺图上表示的方法。

(由于BD字样不易显示,选用小写b和d)之后在摸索中掌握了Quartus中原理图的使用方法。

第一次编译得知在定义名称时字母不区分大写小写,A与a 将被视为重复命名。

第二次只是有几个warnings,给忽略了。

进行仿真时,由于和原理图设计是分两次进行的,在选择“Node Finder...”插入节点时系统没有自动选中我之前保存的bdf文件,显示“No node available”。

重新打开之前的工程文件重试后成功。

在仿真时不知道是否应该将ABCD连续设置16次分别观察是否显示0~F,还是将输入信号设为随即信号,整体观察。

后来一想没啥区别,后者逐个信号竖向观察就能知道显示的数字对不对,还更方便。

观察仿真波形发现,在固定输入信号时,确实输出的信号符合要求。

选做题没想出好方法,觉得只有同时连两条线路才可实现。

其实已开始对这个软件真是无从下手。

多亏几个朋友对我的帮助,我才掌握了基本使用方法。

数字逻辑题目及答案

1.表示任意两位无符号十进制数至少需要()二进制数。

A.6 B.7 C.8 D.92.余3码10001000对应的2421码为()。

A.01010101 B.10000101 C.10111011 D. 11101011 3.下列四个数中与十进制数(72)10相等的是( ) A.(01101000)2 B.(01001000)2C.(01110010)2D.(01001010)24.某集成电路芯片,查手册知其最大输出低电平UOLmax=0.5V,最大输入低电平UILmax=0.8V,最小输出高电平UOHmin=2.7V,最小输入高电平UIHmin=2.0V,则其高电平噪声容限UNH=( ) A.0.3V B.0.6V C.0.7V D.1.2V5.标准或-与式是由()构成的逻辑表达式。

A.与项相或 B. 最小项相或 C. 最大项相与 D.或项相与6、对于TTL或非门多余输入端的处理,不可以()。

A、接电源B、通过0.5kΩ电阻接地C、接地D、与有用输入端并联7.下列四种类型的逻辑门中,可以用()实现三种基本逻辑运算。

A. 与门B. 或门C. 非门D. 与非门8.以下电路中可以实现线与功能的有()。

A.与非门B.三态输出门C.传输门D.漏极开路门9.要使JK触发器在时钟作用下的次态与现态相反,JK端取值应为()。

A.JK=00 B. JK=01 C. JK=10 D. JK=1110.设计一个四位二进制码的奇偶校验器,需要()个异或门。

A.2 B. 3 C. 4 D. 511.相邻两组编码只有一位不同的编码是( )A.2421BCD码 B.8421BCD码 C.余3码 D.循环码12.下列电路中,不属于时序逻辑电路的是( )A.计数器 B.全加器 C.寄存器 D.RAM13.一个4位移位寄存器,现态为0111,经右移1位后其次态为( )A.0011或1011 B.1101或1110C.1011或1110D.0011或111114.为了将正弦信号转换成与之频率相同的脉冲信号,可采用( ) A.多谐振荡器 B.移位寄存器C.单稳态触发器D.施密特触发器15.一个6位地址码、8位输出的ROM,其存储矩阵的容量为( )bit.A.64×8 B.48 C.256 D.816.某8位DAC,当输入全为1时,输出电压为5.10V,当输入D=(10000000)2时,输出电压为( )A.5.10V B.2.56V C.1.28V D.都不是17.PROM是一种__________可编程逻辑器件。

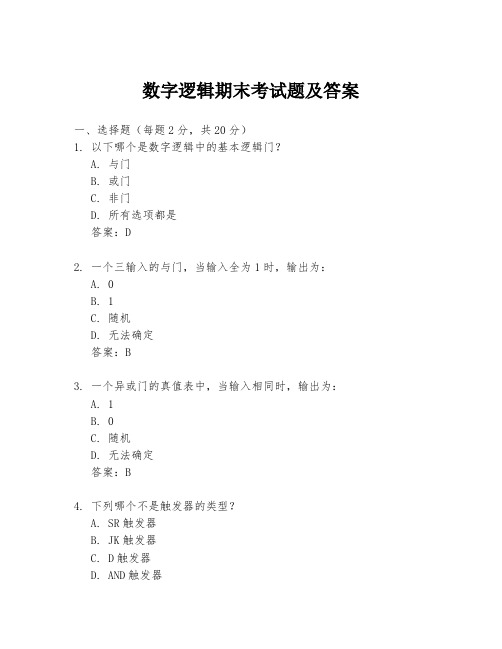

数字逻辑期末考试题及答案

数字逻辑期末考试题及答案一、选择题(每题2分,共20分)1. 以下哪个是数字逻辑中的基本逻辑门?A. 与门B. 或门C. 非门D. 所有选项都是答案:D2. 一个三输入的与门,当输入全为1时,输出为:A. 0B. 1C. 随机D. 无法确定答案:B3. 一个异或门的真值表中,当输入相同时,输出为:A. 1B. 0C. 随机D. 无法确定答案:B4. 下列哪个不是触发器的类型?A. SR触发器B. JK触发器C. D触发器D. AND触发器答案:D5. 在数字电路中,同步计数器和异步计数器的主要区别在于:A. 计数范围B. 计数速度C. 计数精度D. 计数方式答案:B6. 一个4位二进制计数器,其最大计数值为:A. 15B. 16C. 32D. 64答案:A7. 以下哪个不是数字逻辑设计中常用的简化方法?A. 布尔代数简化B. 卡诺图简化C. 逻辑门替换D. 逻辑表简化答案:C8. 在数字电路中,一个信号的上升沿指的是:A. 信号从0变为1的瞬间B. 信号从1变为0的瞬间C. 信号保持不变D. 信号在变化答案:A9. 一个D触发器的Q输出端在时钟信号上升沿时:A. 保持不变B. 翻转状态C. 跟随D输入端D. 随机变化答案:C10. 以下哪个不是数字逻辑中的状态机?A. Moore机B. Mealy机C. 有限状态机D. 无限状态机答案:D二、填空题(每空2分,共20分)11. 在布尔代数中,逻辑与操作用符号______表示。

答案:∧12. 一个布尔函数F(A,B,C)=A∨B∧C的最小项为______。

答案:(1,1,1)13. 在数字电路设计中,卡诺图是一种用于______的工具。

答案:布尔函数简化14. 一个4位二进制加法器的输出端最多有______位。

答案:515. 一个同步计数器在计数时,所有的触发器都______时钟信号。

答案:接收16. 一个JK触发器在J=K=1时,其状态会发生______。

13福师《数字逻辑》在线作业一

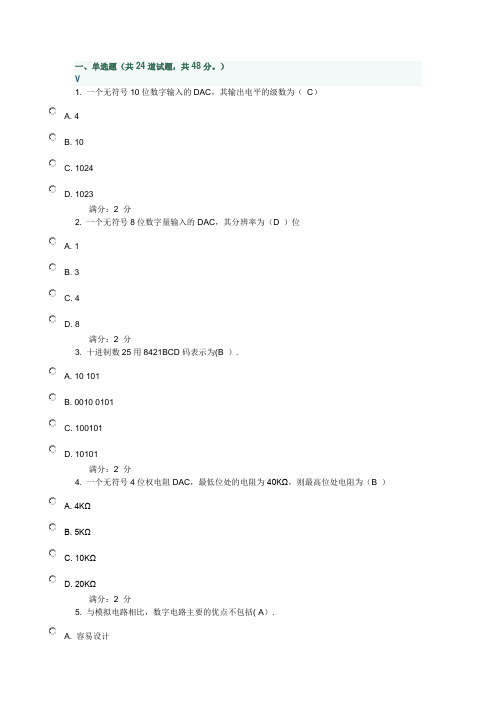

一、单选题(共 24 道试题,共 48 分。

)V1. 一个无符号10位数字输入的DAC,其输出电平的级数为(C)A. 4B. 10C. 1024D. 1023满分:2 分2. 一个无符号8位数字量输入的DAC,其分辨率为(D )位A. 1B. 3C. 4D. 8满分:2 分3. 十进制数25用8421BCD码表示为(B ).A. 10 101B. 0010 0101C. 100101D. 10101满分:2 分4. 一个无符号4位权电阻DAC,最低位处的电阻为40KΩ,则最高位处电阻为(B )A. 4KΩB. 5KΩC. 10KΩD. 20KΩ满分:2 分5. 与模拟电路相比,数字电路主要的优点不包括( A).B. 通用性强C. 保密性好D. 抗干扰能力强满分:2 分6. CMOS数字集成电路与TTL数字集成电路相比不具备的优点是(B ).A. 微功耗B. 高速度C. 高抗干扰能力D. 电源范围宽满分:2 分7. 在何种输入情况下,“与非”运算的结果是逻辑0( D).A. 全部输入是0B. 任一输入是0C. 仅一输入是0D. 全部输入是1满分:2 分8. 不属于矩形脉冲信号的参数有( D).A. 周期B. 占空比C. 脉宽D. 扫描期满分:2 分9. 在数字系统里,当某一线路作为总线使用,那么接到该总线的所有输出设备(或器件)必须具有(B )结构,否则会产生数据冲突。

A. 集电极开路B. 三态门D. 拉电流满分:2 分10. 逻辑表达式Y=AB可以用(C )实现A. 正或门B. 正非门C. 正与门D. 或非门满分:2 分11. 三极管作为开关使用时,下列选项不能提高开关速度是(B).A. 降低饱和深度B. 增加饱和深度C. 采用有源泄放回路D. 采用抗饱和三极管满分:2 分12. 逻辑变量的取值1和0不可以表示(C ).A. 开关的闭合、断开B. 电位的高、低C. 数量的多少D. 电流的有、满分:2 分13. 以下电路中常用于总线应用的有(A).A. TSL门B. OC门C. 漏极开路门D. CMOS与非门满分:2 分14. 以下表达式中符合逻辑运算法则的是(D ).A. C·C=C2B. 1+1=10C. 0<1D. A+1=1满分:2 分15. 与十进制数(53.5 )10等值的数或代码为( A).A. (0101 0011.0101 )8421BCDB. (36.8 )16C. (100101.1 )2D. (65.7 )8满分:2 分16. 以下各电路中,(B )可以产生脉冲定时器A. 多谐振荡器B. 单稳态触发器C. 施密特触发器D. 石英晶体多谐振荡器满分:2 分17. TTL电路在正逻辑系统中,以下各种输入中(D )相当于输入逻辑“0”A. 悬空B. 通过电阻2.7kΩ接电源C. 通过电阻2.7kΩ接地D. 通过电阻510Ω接地满分:2 分18. A+BC= (A ).A. A+BB. A+CC. (A+B )(A+C )D. B+C满分:2 分19. 欲设计0,1,2,3,4,5,6,7这几个数的计数器,如果设计合理,采用同步二进制计数器,最少应使用(B )级触发器A. 2B. 3C. 4D. 8满分:2 分20. TTL集成电路采用的是(B )控制,其功率损耗比较大A. 电压B. 电流C. 灌电流D. 拉电流满分:2 分21. 以下代码中为无权码的为( C).A. 8421BCD码B. 5421BCD码C. 余三码D. 2421码满分:2 分22. 以下电路中可以实现“线与”功能的有(C ).A. 与非门B. 三态输出门C. 集电极开路门满分:2 分23. 要使TTL与非门工作在转折区,可使输入端对地外接电阻RI(C).A. >RONB. <ROFFC. ROFF<RI<ROND. >ROFF满分:2 分24. 常用的BCD码有(C ).A. 奇偶校验码B. 格雷码C. 8421码D. 汉明码满分:2 分二、多选题(共 5 道试题,共 10 分。

数字逻辑题目及其答案和解析(1)一共60道题

第一部分:1.在二进制系统中,下列哪种运算符表示逻辑与操作?A) amp;B) |C) ^D) ~解析:正确答案是 A。

在二进制系统中,amp; 表示逻辑与操作,它仅在两个位都为1时返回1。

2.在数字逻辑中,Karnaugh 地图通常用于简化哪种类型的逻辑表达式?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是B。

Karnaugh 地图通常用于简化或门的逻辑表达式,以减少门电路的复杂性。

3.一个全加器有多少个输入?A) 1B) 2C) 3D) 4解析:正确答案是 C。

一个全加器有三个输入:两个加数位和一个进位位。

4.下列哪种逻辑门可以实现 NOT 操作?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是 D。

与非门可以实现 NOT 操作,当且仅当输入为0时输出为1,输入为1时输出为0。

5.在数字逻辑中,Mux 是指什么?A) 多路复用器B) 解码器C) 编码器D) 多路分配器解析:正确答案是 A。

Mux 是指多路复用器,它可以选择输入中的一个,并将其发送到输出。

6.在二进制加法中,下列哪个条件表示进位?A) 0 + 0B) 0 + 1C) 1 + 0D) 1 + 1解析:正确答案是 D。

在二进制加法中,当两个位都为1时,会产生进位。

7.在数字逻辑中,一个 JK 触发器有多少个输入?A) 1B) 2C) 3D) 4解析:正确答案是 B。

一个 JK 触发器有两个输入:J 和 K。

8.下列哪种逻辑门具有两个输入,且输出为两个输入的逻辑与?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是 A。

与门具有两个输入,只有当两个输入都为1时,输出才为1。

9.在数字逻辑中,下列哪种元件可用于存储单个位?A) 寄存器B) 计数器C) 锁存器D) 可编程逻辑门阵列解析:正确答案是 C。

锁存器可用于存储单个位,它可以保持输入信号的状态。

10.一个带有三个输入的逻辑门,每个输入可以是0或1,一共有多少种可能的输入组合?A) 3B) 6C) 8D) 12解析:正确答案是 C。

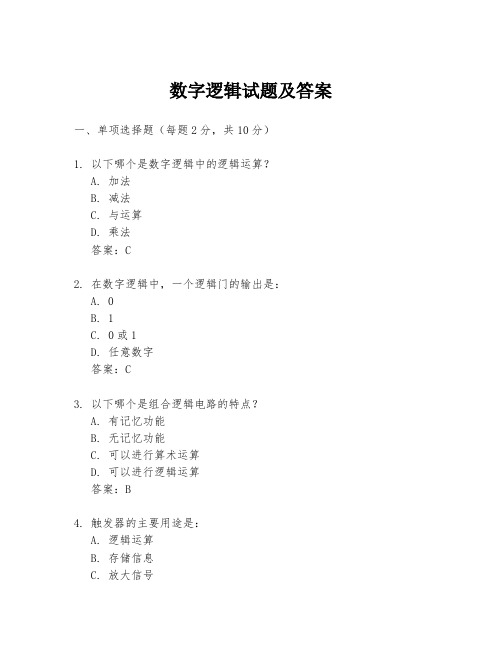

数字逻辑试题及答案

数字逻辑试题及答案一、单项选择题(每题2分,共10分)1. 以下哪个是数字逻辑中的逻辑运算?A. 加法B. 减法C. 与运算D. 乘法答案:C2. 在数字逻辑中,一个逻辑门的输出是:A. 0B. 1C. 0或1D. 任意数字答案:C3. 以下哪个是组合逻辑电路的特点?A. 有记忆功能B. 无记忆功能C. 可以进行算术运算D. 可以进行逻辑运算答案:B4. 触发器的主要用途是:A. 逻辑运算B. 存储信息C. 放大信号D. 转换信号答案:B5. 一个4位二进制计数器可以计数到:A. 8B. 16C. 32D. 64答案:B二、多项选择题(每题3分,共15分)1. 下列哪些是数字逻辑中常用的逻辑门?A. 与门B. 或门C. 非门D. 异或门E. 与非门答案:ABCDE2. 在数字逻辑中,以下哪些可以作为信号的表示?A. 电压B. 电流C. 电阻D. 电容E. 电感答案:AB3. 以下哪些是数字电路的基本组成元素?A. 逻辑门B. 电阻C. 电容D. 触发器E. 运算放大器答案:ABD4. 在数字逻辑中,以下哪些是常见的电路类型?A. 组合逻辑电路B. 时序逻辑电路C. 模拟电路D. 混合信号电路E. 微处理器答案:ABD5. 以下哪些是数字电路设计时需要考虑的因素?A. 电路的复杂性B. 电路的功耗C. 电路的可靠性D. 电路的成本E. 电路的尺寸答案:ABCDE三、填空题(每题2分,共10分)1. 在数字逻辑中,一个逻辑门的输出状态取决于其_________。

答案:输入状态2. 一个D触发器的输出在时钟信号的_________沿触发。

答案:上升沿3. 一个4位二进制计数器的计数范围是从_________到_________。

答案:0000到11114. 一个逻辑电路的输出是其输入的_________。

答案:逻辑函数5. 在数字逻辑中,使用_________可以表示一个逻辑函数的真值表。

答案:卡诺图四、简答题(每题5分,共15分)1. 描述一个典型的组合逻辑电路的工作原理。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《数字逻辑》作业

一、单项选择题

1. 八进制数8)4.573(的十六进制数是 C 。

A. 16)4.17(C

B. 16)4.16(B

C. 16)8.17(B

D. 16)5.17(b 2. 用0,1两个符号对100个信息进行编码,则至少需要 B 。

A. 8位

B. 7位

C. 9位

D. 6位 3.逻辑函数B DEG B B A B A F +++=___D___

A.B F =

B.B F =

C.0=F

D. 1=F 4.逻辑函数C A ABC F Θ=)(的最小项标准式为 C 。

A. ∑=

)5,4,3,1,0(F B.C A C A F +=

C.7520m m m m F +++=

D. ∑=)7,6,1,0(F

5.已知逻辑函数∑=

)5,4,3,1,0(F ,则F 的最简反函数为 A 。

A.C B AB F +=

B.C A B F +=

C.AC B F +=

D. C B AB F += 6.在下列名组变量取值中,使函数∑=

)12,6,4,3,1,0()(ABCD F 的值为1的是 D 。

A.1 1 0 1

B.1 0 0 1

C.0 1 0 1

D. 1 1 0 0 7.逻辑函数CD D B A D C A ABD F +++=的最简或非式是 A 。

A.D A C A +++

B.D A C A +++

C.AD C A +

D. D A C A +++

8.函数⎪⎩⎪⎨

⎧=+=∑)

(0)

15,13,11,10,8,2,0(约束条件D C B BD A F 的最简与非式为 A 。

A.BD AD AB ⋅⋅ B.AD BD ⋅ C.BD AD ⋅ D. D B AD ⋅⋅

二、请根据真值表写出其最小项表达式

1.

2.

三、用与非门实现

四、用或非门实现

B

A B A B A L +=⊕=

B A B A B A L +=⊕=

五、逻辑电路如图所示,请分析出该电路的最简与或表达式,并画出其真值表。

1.

2.

六、

裁决由每一个裁判按一下自己面前的按钮来确定。

只有当两个或两个以上裁判判明成功,并且其中有一个为主裁判时,表明成功的灯才亮。

L

CA

BC AB Y ++=

七、设计一个楼上、楼下开关的控制逻辑电路来控制楼梯上的路灯,使之在上楼前,用楼下开关打开电灯,上楼后,用楼上开关关灭电灯;或者在下楼前,用楼上开关打开电灯,下楼后,用楼下开关关灭电灯。

八、①试分析下图中用何种触发器,并写出该触发器的特性方程。

②分析该时序逻辑电路的功能。

1.

有效循环的6个状态分别是0~5这6个十进制数字的格雷码,并且在时钟脉冲CP 的作用下,这6个状态是按递增规律变化的,即:000→001→011→111→110→100→000→…所以这是一个用格雷码表示的六进制同步加法计数器。

当对第6个脉冲计数时,计数器又重新从000开始计数,并产生输出Y =1。

2.

当输入X =0时,在时钟脉冲CP 的作用下,电路的4个状态按递增规律循环变化,即:00→01→10→

11→00→…当X =1时,在时钟脉冲CP 的作用下,电路的4个状态按递减规律循环变化,即:00→11→10→01→00→…可见,该电路既具有递增计数功能,又具有递减计数功能,是一个2位二进制同步可逆计数器。

3.

在时钟脉冲CP 的作用下,电路的8个状态按递减规律循环变化,即:000→111→110→101→100→011→010→001→000→…电路具有递减计数功能,是一个3位二进制异步减法计数器 4.

有效循环的6个状态分别是0~5这6个十进制数字的格雷码,并且在时钟脉冲CP的作用下,这6个状态是按递增规律变化的,即:000→001→011→111→110→100→000→…所以这是一个用格雷码表示的六进制同步加法计数器。

当对第6个脉冲计数时,计数器又重新从000开始计数,并产生输出Y=1。