一种基于FPGA的信号发生器设计实现

基于FPGA的信号发生器的设计与实现

基于FPGA的信号发生器的设计与实现作者:臧谱阳王正斌来源:《电脑知识与技术》2020年第27期摘要:该文详细介绍了一种通过DDS数字合成器技术,来实现一种频率,幅度,相位可调制的高精度信号发生器。

在FPGA中设计了串口模块和相应的解析模块向DDS发送指令,使其通过读取ROM内的波形数据存储器的数据进而实现对频率和相位的控制。

同时可以根据需要自行更换ROM内存储的波形数据,能够产生正弦波,方波,锯齿波和任意波形信号。

关键词:FPGA;DDS;信号发生器;串口;ROM中图分类号:TP311 文献标识码:A文章编号:1009-3044(2020)27-0220-02开放科学(资源服务)标识码(OSID):1 概述本系统以FPGA为核心控制器,相比于STM32系列单片机的顺序指令队列,FPGA强大的并行能力在处理模拟信号和拓展接口上效率会更高,读写速度也更快。

相比于传统C语言通过FLASH读取数组信息来获取波形数据,本系统通过读取片内ROM并结合DDS进行波形数据采集,设计方法更加简单灵活,波形的显示也会更流畅。

可以输出直流、交流等信号。

2 DDS技术原理与分析DDS(Direct Digital Synthesizer)是一种新型的频率合成技术,其主要组成部分有相位累加器,相位调制器,波形数据表和D/A转换器。

其广泛运用于通信领域,特点是波形选择范围大,可供选择带宽的范围大,可控制时间长,精度高等[1-2]。

对于信号的相位、频率、幅值均可以通过自制的波形编码生成,自由度大。

其基本结构见图1所示。

在每个时钟的上升沿时,加法器会将默认的频率控制字与同步寄存器中的相位值累加,得到的数值是由加法器和寄存器的位数决定的。

累加的值接着在第二个时钟上升沿时反馈至累加寄存器的输入端,重复与设定的频率控制字相加[3-5]。

这样,在每一个时钟周期,对设定的频率控制字不断进行线性累加,这时的累加值输出的数据就是最终处理信号的相位值,也是波形存储器的采样地址。

基于FPGA的函数信号发生器设计

第14期2018年5月No.14May ,2018王译平(上海东湖机械厂,上海200439)引言FPGA 的全称为Field Programmable Gate Array ,即现场可编程门阵列,内部主要由逻辑阵列块LAB 、嵌入式存储器块、I/O 单元和PLL 等模块组成,在各个模块之间存在着丰富的互连线和时钟网络。

通过利用超高速集成电路硬件描述语言(Very-High-Speed Integrated Circuit Hardware Description Language ,VHDL )编程,在对应的硬件综合平台上对其进行综合,把抽象的软件代码翻译成原理图,再进行相应的配置,使FPGA 实现预想的功能[1]。

直接数字式频率合成器(Direct Digital Synthesizer ,DDS )是将波形数据采样数据连续地存储在波形存储器只读存储器镜像(Read Only Memory image ,ROM )内,结合外围控制电路,将既定的波形数据在输出端口以数字信号形式发出,利用D/A 转换器转换成模拟信号,再通过低通滤波器平滑后输出精确的所需的波形。

DDS 更区别于传统的生成波形的数字方法,具有频率可快速切换、相位连续等特点[2]。

其工作流程如图1所示。

1DDS 的基本原理DDS 是一种数字化的频率合成技术,其结构主要由相位累加器、波形存储ROM 、D/A 转换器和低通滤波器等四大结构组成,如图2所示。

作者简介:王译平(1984—),男,上海人,工程师,学士;研究方向:装备维修。

江苏科技信息Jiangsu Science &Technology Information基于FPGA 的函数信号发生器设计摘要:函数信号发生器在测量、控制等领域应用十分广泛,是各种测试过程中不可缺少的工具。

文章以FPGA 为核心,使用VHDL 语言,采用DDS 技术实现函数信号发生器。

关键词:函数信号发生器;FPGA ;VHDL ;DDS 中图分类号:O1文献标识码:A图1直接数字频率合成方式的任意波形发生器图2DDS 结构原理--411.1相位累加器相位累加器是DDS模块最重要的组成部分,由一个N位的加法器和一个N位寄存器组成。

基于FPGA的DDS信号发生器设计分析

基于FPGA的DDS信号发生器设计分析摘要:随着现代电子技术的飞速发展,直接数字频率合成DDS 技术逐渐被广泛使用,DDS 是目前数据调度常用的数据分发技术,此技术能够有效结合数据服务质量要求,完成数据分发操作。

为此提出基于FPGA的DDS信号发生器设计,以提升信号发生器精度效果。

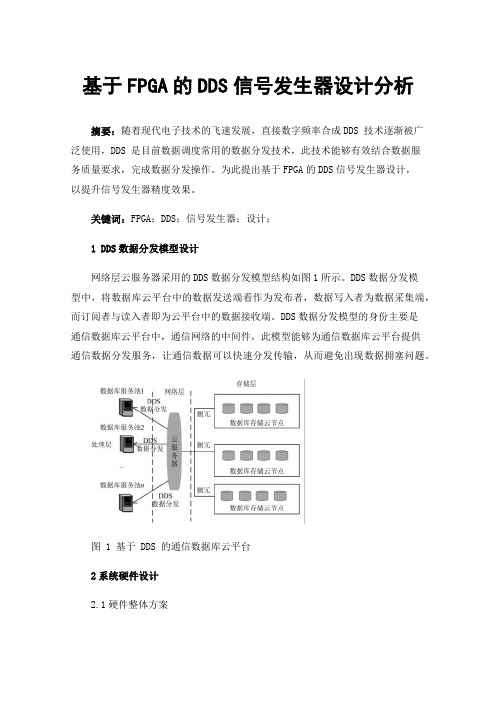

关键词:FPGA;DDS;信号发生器;设计;1 DDS数据分发模型设计网络层云服务器采用的DDS数据分发模型结构如图1所示。

DDS数据分发模型中,将数据库云平台中的数据发送端看作为发布者,数据写入者为数据采集端,而订阅者与读入者即为云平台中的数据接收端。

DDS数据分发模型的身份主要是通信数据库云平台中,通信网络的中间件,此模型能够为通信数据库云平台提供通信数据分发服务,让通信数据可以快速分发传输,从而避免出现数据拥塞问题。

图 1 基于 DDS 的通信数据库云平台2系统硬件设计2.1硬件整体方案函数信号发生器的硬件系统主要包括MCU控制电路,FPGA构成的DDS发生器、DAC转换和低通滤波电路,及一些用于输入输出的器件等。

按键输入和LCD输出显示主要由MCU负责控制,MCU然后将输入的信号运算处理后发送给FPGA,FPGA根据输入的各种参数在ROM表中寻址,同时输出对应控制的波形、频率和幅度的数字信号,最后经过DA转换为对应的模拟电压信号,在经过一个低通滤波器使得模拟电压信号变得平滑。

2.2硬件模块电路系统的硬件电路主要分为两个部分,一是系统主控电路,二是DDS信号发生器电路。

系统主控电路包括以STM32F103C8T6为主控的最小系统板、四路用户按键输入、OLED显示屏输出(SPI)、UART通信连接上位机、硬件SPI连接FPGA负责信号数据传输。

DDS信号发生器电路,其中的FPGA模块的核心芯片为LatticeLCMXO2-4000HC-4MG132,其模块上内置8路输出LED指示灯、4路按键输入、4路拨码输入和两位数码管输出灯资源。

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计随着数字信号处理(DSP)技术的发展,直接数字频率合成器(DDS)逐渐取代了传统的频率合成器,成为一种高性能的信号发生器。

DDS信号发生器通过数字信号直接产生模拟信号,具有频率精度高、可编程性强和快速调频等优点。

本文将通过FPGA实现DDS信号发生器的设计。

首先,我们需要了解DDS信号发生器的基本原理。

DDS信号发生器的核心是相位累加器、查找表和数模转换器(DAC)。

通过累加器产生相位累积,将相位累积的结果通过查找表得到对应的振幅值,并经过数模转换器输出模拟信号。

1.确定需要生成的信号的参数,包括输出频率、相位步进精度、振幅等。

根据这些参数,计算累加器的增量值,即每个时钟周期累加器需要累加的值。

2.在FPGA中设计相位累加器。

相位累加器的宽度取决于相位步进精度,一般为32位或64位。

通过在每个时钟周期加上增量值,实现相位的累加。

3.设计查找表。

查找表的大小取决于数字信号的分辨率,一般为2^N 位。

通过输入相位值查找对应的振幅值。

4.设计数模转换器(DAC)。

通过DAC将数字信号转换为模拟信号输出。

5.在FPGA中实现控制逻辑,包括控制相位累加器和查找表的读写操作,使其按照设定的参数进行相位累加和振幅输出。

6.将设计好的FPGA模块进行综合、布局和时序约束,生成比特流文件。

通过以上步骤,基于FPGA的DDS信号发生器的设计就完成了。

设计好的FPGA模块可以实现高精度、高稳定性的信号发生器,广泛应用于通信、雷达、医疗设备等领域。

需要注意的是,在设计过程中需要考虑到FPGA的资源限制,包括LUT资源的利用、频率分辨率和输出频率的限制等。

此外,还可以通过增加相位累积周期、使用多路查找表和多路DAC等方法进一步优化设计。

综上所述,基于FPGA的DDS信号发生器设计是一个较为复杂的过程,需要对DDS原理有深入的理解,并结合FPGA的特点进行设计。

通过合理的设计和优化,可以实现高性能的DDS信号发生器。

基于FPGA的实用多功能信号发生器的设计与制作

基于FPGA的实用多功能信号发生器的设计与制作基于FPGA的实用多功能信号发生器的设计与制作摘要多功能信号发生器已成为现代测试领域应用最为广泛的通用仪器之一,代表了信号源的发展方向。

直接数字频率合成(DDS)是二十世纪七十年代初提出的一种全数字的频率合成技术,其查表合成波形的方法可以满足产生任意波形的要求。

由于现场可编程门阵列(FPGA)具有高集成度、高速度、可实现大容量存储器功能的特性,能有效地实现DDS技术,极大的提高函数发生器的性能,降低生产成本。

本文首先介绍了函数信号发生器的研究背景和DDS的理论。

然后详尽地叙述了利用Verilog HDL描述DDS模块的设计过程,以及设计过程中应注意的问题。

文中详细地介绍了多种信号的发生理论、实现方法、实现过程、部分Verilog HDL代码以及利用Modelsim仿真的结果。

文中还介绍了Altera公司的DE2多媒体开发平台的部分功能及使用,并最终利用DE2平台完成了多功能信号发生器的大部分功能。

包括由LCD显示和按键输入构成的人机界面和多种信号的发生。

数字模拟转换器是BURR-BROWN 公司生产的DAC902。

该信号发生器能输出8种不同的信号,并且能对输出信号的频率、相位以及调制信号的频率进行修改设定。

关键词:信号发生器;DDS;FPGA;DE2Practical FPGA-based multi function signal generatordesign and productionAbstractMulti function signal generator has become the most widely used in modern testing field of general instrument, and has represented one of the development direction of the source. Direct digital frequency synthesis (DDS) is a totaly digital frequency synthesis technology, which been put forward in the early 1970s. Using a look-up table method to synthetic waveform, it can satisfy any requirement of waveform produce. Due to the field programmable gates array (FPGA) with high integrity, high speed, and large storage properties, it can realize the DDS technology effectively, increase signal generator’s performance and reduce production costs.Firstly, this article introduced the function signal generator of the research background and DDS theory. Then, it described how to design a DDS module by Verilog HDL, and introduced various signal occurs theory, method and the implementation process, Verilog HDL code and simulation results.This paper also introduces the function of DE2 multimedia development platform, and completed most of the functions of multi-function signal generator on DE2 platform finally. Including the occurrence of multiple signal and the man-machine interface which composed by LCD display and key input. Digital-to-analog converters is DAC902, which produced by company BURR-BROWN.This signal generator can output eight different kinds of signals, and the frequency of the output signal, phase and modulation frequency signal also can be modifyed.Key Words: Signal generator; DDS; FPGA; DE2目录论文总页数:34页1 引言 (1)1.1课题背景 (1)1.2国内外波形发生器的发展现状 (1)1.3本文研究的主要内容 (2)2 信号发生器原理 (2)2.1直接数字频率合成技术的基本原理 (2)2.2相位偏移控制 (3)2.3多种信号的发生 (3)2.3.1方波的发生 (3)2.3.2三角波发生 (4)2.2.3锯齿波发生 (4)2.3.4 PWM信号发生 (4)2.3.5 SPWM信号发生 (5)2.3.6 AM信号发生 (5)2.3.7 FM信号发生 (6)2.4DDS的特点 (7)2.4.1 DDS 的优点 (7)2.4.2 DDS 系统的缺点 (7)3 系统整体设计 (8)3.1硬件部分 (8)3.1.1 DE2实验板 (8)3.1.2 LCD模块 (9)3.1.2 DAC902 (11)3.2基于VERILOG的FPGA设计 (12)3.3软件工具 (12)3.3.1 Modelsim (12)3.3.2 Quartus (12)3.4系统设计 (13)3.4.1 系统初始化模块 (13)3.4.2按键模块和LCD模块 (13)3.4.3 RAM模块 (14)3.4.4数据转换模块 (15)3.4.5 DAC驱动模块 (15)3.4.6系统的运行 (15)4 VERILOG HDL代码实现与仿真 (15)4.1信号发生器模块 (15)4.1.1频率控制字和相位累加器 (15)4.1.2 相位偏移控制 (16)4.1.3正弦波发生模块 (17)4.1.4 方波发生模块 (17)4.1.5 三角波发生模块 (18)4.1.6 锯齿波发生模块 (18)4.1.7 PWM信号发生模块 (19)4.1.8 SPWM信号发生模块 (19)4.1.9 AM信号发生模块 (20)4.1.10 FM信号发生模块 (21)4.2按键输入模块 (22)4.3LCD显示模块 (23)4.4RAM模块 (24)4.5数据转换模块 (25)5 系统测试 (26)5.1控制及显示部分测试 (27)5.2输出频率测试 (27)5.3信号发生测试 (28)5.3.1 正弦波、方波、三角波、锯齿波测试 (28)5.3.2 PWM信号测试 (29)5.3.3 SPWM信号测试 (29)5.3.4 AM信号测试 (29)5.3.5 FM信号测试 (30)结论 (31)参考文献 (32)致谢...................................................... 错误!未定义书签。

基于FPGA的多功能信号发生器的设计

电子电路设计与方案0 前言现场可编程门阵列具有运行速度快,修改灵活方便,并自带大量的输入输出端口等优点,通过FPGA实现该信号发生器的核心部件DDS模块,可以灵活地对信号发生器的参数进行调整,另外通过单片机的配合实现对其他外设电路的控制,实现信号发生器显示、参数调节等辅助的功能,通过数模转换电路和波形处理电路实现所需信号波形的输出。

本设计的主要指标为:(1)频率范围:0~1MHz,可通过键盘任意设置频率,步进1Hz。

(2)频率精度:±1%。

(3)幅值范围:±5V,可通过键盘任意设置幅度,步进100mV。

(4)幅值精度:±5%。

(5)用液晶显示所选波形名称,频率,幅值。

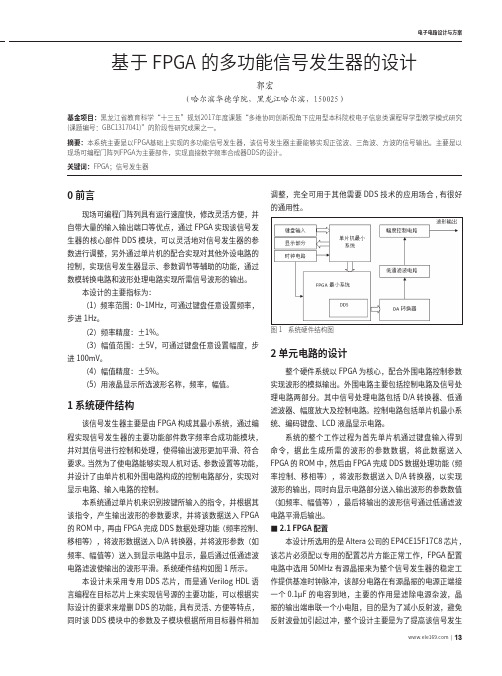

1 系统硬件结构该信号发生器主要是由FPGA构成其最小系统,通过编程实现信号发生器的主要功能部件数字频率合成功能模块,并对其信号进行控制和处理,使得输出波形更加平滑、符合要求。

当然为了使电路能够实现人机对话、参数设置等功能,并设计了由单片机和外围电路构成的控制电路部分,实现对显示电路、输入电路的控制。

本系统通过单片机来识别按键所输入的指令,并根据其该指令,产生输出波形的参数要求,并将该数据送入FPGA 的ROM中,再由FPGA完成DDS数据处理功能(频率控制、移相等),将波形数据送入D/A转换器,并将波形参数(如频率、幅值等)送入到显示电路中显示,最后通过低通滤波电路滤波使输出的波形平滑。

系统硬件结构如图1所示。

本设计未采用专用DDS芯片,而是通Verilog HDL语言编程在目标芯片上来实现信号源的主要功能,可以根据实际设计的要求来增删DDS的功能,具有灵活、方便等特点,同时该DDS模块中的参数及子模块根据所用目标器件稍加调整,完全可用于其他需要DDS技术的应用场合,有很好的通用性。

图1 系统硬件结构图2 单元电路的设计整个硬件系统以FPGA为核心,配合外围电路控制参数实现波形的模拟输出。

外围电路主要包括控制电路及信号处理电路两部分。

基于FPGA方波信号发生器的设计

基于FPGA方波信号发生器设计一.实验目的:1.进一步熟悉QuartusII及其LPM_ROM与FPGA硬件资源的使用方法。

2.加深对电路理论概念的理解3.进一步熟悉常用仪器的使用及调试4.加深计算机辅助分析及设计的概念5.了解及初步掌握对电路进行计算机辅助分析的过程6.培养学生发现问题、分析问题的创新能力7.锻炼学生搜集资料、分析综合资料的能力二.实验原理:方波波信号发生器由四部分组成:计数器或地址发生器(这里选择6位)。

方波信号数据ROM(6位地址线、8位数据线),含有64个8位数据(一个周期)。

VHDL顶层设计。

8位D/A(实验中用DAC0832代替)。

图1所示的信号发生器结构框图中,顶层文件singt.vhd在FPGA中实现,包含两个部分:ROM的地址信号发生器,由6位计数器担任;一个方波数据ROM,由LPM_ROM模块构成。

LPM_ROM底层是FPGA中的EAB、ESB或M4K等模块。

地址发生器的时钟CLK的输入频率f0与每周期的波形数据点数(在此选择64点),以及D/A输出的频率f的关系是:f = f0/64。

图1 方波信号发生器结构框图三.实验内容:1.新建一个文件夹。

利用资源管理器,新建一个文件夹,如:e : \SIN_GNT 。

注意,文件夹名不能用中文。

2.输入源程序。

打开QuartusII,选择菜单“File” “New”,在New 窗中的“Device Design Files”中选择编译文件的语言类型,这里选“VHDL Files”。

然后在VHDL 文本编译窗中键入VHDL 程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity square isport(clk,clr:in std_logic;q:out integer range 0 to 255);end entity;architecture behav of square issignal a:bit;beginprocess(clk,clr) --计数分频variable cnt:integer range 0 to 32; beginif(clr='0') thena<='0';elsif clk'event and clk='1' thenif cnt<31 then --进行32分频cnt:=cnt+1;elsecnt:=0;a<=not a;end if;end if;end process;process(clk,a) --信号输出beginif clk'event and clk='1' thenif a='1' thenq<=255;elseq<=0;end if;end if;end process;end behav;3. 建立.mif格式文件首先选择ROM 数据文件编辑窗,即在File 菜单中选择“New”,并在New 窗中选择“Other files”项,并“Memory Initialization File”(图3-11),点击OK 后产生ROM 数据文件大小选择窗。

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计随着现代科技的不断发展,数字信号发生器(DDS)已成为各种电子设备中常用的一种功能模块。

使用DDS技术可以生成高质量、高稳定性的各种频率和波形的信号。

而FPGA(Field Programmable Gate Array)作为一种可编程逻辑器件,具有高集成度、高速度和灵活性等优势,逐渐成为了实现DDS信号发生器的主要选择之一一、DDS技术概述DDS(Direct Digital Synthesis)技术是一种基于数字直接合成的方法,通过计算机算法精确地合成期望的波形。

它的工作原理是将时钟信号分频得到一系列的离散相位值,再通过查表和插值的方法得到对应的幅值,最后通过一个DAC(Digital to Analog Converter)将数字信号转换为模拟信号输出。

二、基于FPGA的DDS信号发生器设计步骤1.系统架构设计根据DDS信号发生器的要求,确定所需的系统架构。

一般包括时钟模块、相位累加器、查找表、插值器、DAC和控制逻辑等模块。

2.时钟模块使用FPGA内部的资源或外部时钟源生成所需的系统时钟信号。

可以通过时钟分频和PLL(Phase-Locked Loop)锁相环技术来实现对系统时钟的精确控制。

3.相位累加器利用FPGA的寄存器或分频模块实现相位累加功能。

通过周期性地累加相位增量,可以得到DDS信号的相位。

4.查找表利用FPGA内部的RAM(Random Access Memory)存储相位对应的幅值。

根据相位的大小来查找对应的幅值,存储在RAM中。

5.插值器可以通过线性插值或差值的方法对相位查找表的输出进行插值,以提高输出信号的精度和稳定性。

6.DAC将插值器输出的数字信号转换为模拟信号,通过FPGA的IO端口或专用的DAC芯片输出到外部电路。

7.控制逻辑设计合适的控制逻辑,可以通过外部接口或FPGA内部的控制模块来控制DDS信号发生器的频率、幅值、相位偏移等参数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第24卷第6期 武汉纺织大学学报 V ol.24 No.6 2011年12月J O U R N A L O F W U H A N T E X T I L E U N I V E R S I T Y D e c.2011 一种基于FPGA的信号发生器设计实现郑 琴,鲁 琴,宋承志(武汉纺织大学 数学与计算机学院,湖北 武汉 430073)摘 要:应用VHDL语言及QuartusII软件提供的原理图输入设计功能,结合电子线路的设计加以完成一个可应用于数字系统开发或实验时做输入脉冲信号或基准脉冲信号用的信号发生器,它具有结构紧凑,性能稳定,设计结构灵活,方便进行多功能组合的特点,经济实用,成本低廉。

关键词:信号发生器;FPGA;QuartusII;VHDL语言中图分类号:TP302 文献标识码:A文章编号:1009-5160(2011)06-0061-041 引言随着我国的经济日益增长,社会对电子产品的需求量也就越来越大,目前,我国的电子产品市场正在迅速的壮大,市场前景广阔。

FPGA(Field Programmable Gate Array,现场可编程门阵列)在现代数字电路设计中发挥着越来越重要的作用。

FPGA所具有的静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改,这样就极大地提高了电子系统设计的灵活性和通用性,缩短了产品的上市时间并降低可电子系统的开发成本。

信号发生器是数字设备运行工作中必不可少的一部分,在传统的信号发生器中,大都使用分立元件,而且体积庞大携带不便,且大部分只能输出一种脉冲信号波形,而使用专用的数字电路设计的信号发生器,设备成本高、使用复杂。

基于以上考虑,在中小型数字电路的设计和测试中,迫切需要设计一种小型易用成本低廉的信号发生器。

2 设计方案利用VHDL编程,依据基本数字电路模块原理进行整合。

系统各部分所需工作时钟信号由输入系统时钟信号经分频得到,系统时钟输入端应满足输入脉冲信号的要求。

组合波形信号经显示模块输出。

具备幅度和频率可调功能,幅度可通过电位器调整,频率控制模块则是一个简易的计数器,控制步径为100HZ的可调频率,最终送至脉冲发生模块输出脉冲信号,达到设计课题所要求的输出波形频率可调及幅度可调功能。

幅度可调功能由于比较简单,可以在FPGA外部利用硬件电路实现[2,3,8,9]。

总体设计框图如下图1所示:图1 总体设计框架图武汉纺织大学学报 2011年62 采用VHDL 语言来编程,然后下载文件到FPGA 来实现。

VHDL 语言是电子设计领域的主流硬件描述语言,具有很强的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,从而大大降低了硬件设计任务,提高了设计效率和可靠性,要比模拟电路快得多。

该方案是利用FPGA 具有的静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改,极大地提高了电子系统设计的灵活性和通用性,而且大大缩短了系统的开发周期。

3 软件设计3.1 波形产生模块本设计用VHDL 语言根据傅立叶函数采集点进行扫描,分别产生正弦波、三角波和矩形波。

以下介绍各种常用周期信号的傅立叶函数展开式[1,4,5,8,10,11]。

3.1.1 正弦波正弦波发生分为两个步骤,即正弦波幅值采样存储和正弦波波形的还原输出。

幅值采样是将一个周期正弦波进行64等分,如图2所示,将64个采样点进行量化处理,量化值=255*sin360/64(V),将64点量化值存入存储器。

正弦波形的产生是通过循环反复将存储器中的64点采样值通过DAC0832进行还原输出,得到幅值正比于64点采样值的正弦波。

3.1.2 矩形波矩形波的实现较之正弦波发生简单,由于矩形波是两个电平值间的交替变换,因此波形采样值的预存只要有两个不同的数值就行了,为了使矩形波发生的频率灵活可调,采用60个采样值扫描输出来实现,每半个矩形波周期采用三十个采样值,循环反复将存储器中的60点采样值通过DAC0832进行还原输出,得到幅值正比于点采样值的矩形波。

采样图如图3所示。

3.1.3 三角波由于三角波是线性的,比较简单就可以产生,如果最低电压设为15V,最高是255V,那么根据它的公式255/15=17,每个点的电压只要依次加17就可以得到,一个波形所以采用简单的加减算法就可实现,如图4所示三角波的采样图。

3.1.4 基波通过VHDL编程产生的正弦波、方波、三角波三种周期性波形即为基波。

图5 频率控制模块流程图图6 选择波形电路设计流程图 图2 正弦波采样图 图3 方波采样图 图4 三角波采样图第6期 郑琴,等:一种基于FPGA 的信号发生器设计实现 633.1.5 谐波的产生采用与基波产生的同样原理,编程产生三种波形的谐波,所不同的是一个波形的周期采样的点数不同,如果基波采样点为63个,谐波采样点数则为21个,其每点的电压值为255*(sin360/60+sin360/20)(V),在对其进行循环扫描即可实现基波与谐波的线性叠加。

3.2 频率控制模块系统要求频率控制是在100HZ-1KHZ,步进为100HZ。

在本题设计中只需借助FPGA 便可完成。

根据用户需要的频率[5,6,9],通过编程把频率控制数值传送给各个模块,从而实现频率的控制。

如图5所示。

3.3 选择波形模块这一部分主要是通过一个按键对波形进行循环选择,按下确认按钮后进行波形的调用。

设计流程图如图6所示。

4 硬件电路设计此次系统设计硬件部分通过FPGA/CPLD实验箱完成。

为了避免干扰信号影响系统正常工作,未分配功能的FPGA 引脚必须接地,在FPGA 器件的电源端必须并连一0.01uF 的退耦电容,在所有的输入引脚上串联100欧姆左右电阻减弱干扰信号影响,如有必要还应在输入端设置上拉或下拉电阻。

4.1 滤波电路设计如图7所示,设计D/A 输出后,通过滤波电路、输出缓冲电路,使信号平滑且具有负载能力。

为保证稳幅输出,选用AD817,这是一种低功耗、高速、宽带运算放大器 , 具有很强的大电流驱动能力。

实际电路测量结果表明:当负载100Ω、输出电压峰-峰值10V 时,带宽大于500kHz,幅度变化小于土1%。

4.2 幅度控制电路设计幅度控制电路采用一个电位器来控制波形的输出幅度,电位器的型号为10K 欧。

5 系统调试FPGA 系统的软硬件设计是紧密相连的,将软件编译综合并且通过下载对FPGA 进行适配,运行中的FPGA 是由其内部的硬件结构控制读出数据,从而产生波形。

系统仿真波形如图8所示:RI:RAM 的读数控制端;SELIN:波形选择输入端(0:正弦波;1:三角波;2:方波;3:任意波地址;4:三角波和正弦波的叠加;5:方波和正弦波的叠加;6:方波和三角波的叠加;7:三种波形的叠加)ADDIN:地址输入端;SININ:正弦波输入端;TRIIN:三角波输入端; SQUIN:方波输入端;图7 滤波电路的设计图8系统仿真波形64武汉纺织大学学报 2011年QADD:地址输出端;Q:波形选择输出端;6 结论系统以FPGA10K10器件为核心部件,可利用软件编程实现了对D/A转换信号的处理。

努力做到了线路简单、高性价比的特点,充分利用了软件编程,弥补了硬件元器件的不足。

参考文献:[1]潘松,黄继业. EDA技术实用教程(第二版)[M]. 北京:北京科学出版社,2005.2.[2]李小波,等.基于CPLD和单片机的低频信号源设计[J]. 仪表技术与传感器,2005, (11):46-48.[3]包明,等.基于FPGA的高速高精度频率测量的研究[J]. 单片机与嵌入式系统应用,2003,(2):31-33.[4]王志鹏,付丽琴.可编程逻辑器件开发技术. Quartus II. 北京: 国防工业出版社,2005.3.[5]王道先. VHDL电路设计技术. 北京: 国防工业出版社,2004.1[6]候伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,2000.[7]曾繁泰.EDA工程的理论与实践[M]. 北京: 电子工业出版社,2004.5.[8]尹佳喜,尹仕.基于CPLD的三相多波形函数发生器设计[J]. 电子工程师, 2005,(8).[9]高淼.基于FPGA的自治型SPWM波形发生器的设计[J]. 世界电子元器件, 2003,(10).[10]李刚强.FPGA设计中关键问题的研究[EB/OL]. /viewarticle.php?id=27146,2005-10-15.[11]Ralf N.Hardware/Software Co_designed for Data Flow Dominated Embedded System[M]. Kluwer Academic Publishers,1998.The Design and Implementation of A Signal Generator based on FPGAZHENG Qin, LU Qin, SONG Cheng-zhi(College of Mathmatics and Computer Science, Wuhan Textile university, Wuhan Hubei 430073, China)Abstract: VHDL language and QuartusII software application of the principle diagram provided input, combined with electronic circuit design function of the design to complete a can be used in the digital system development or experiment do input pulse signal or benchmark pulse signal with the signal generator, it has compact structure, stable performance, the structure design is flexible, convenient for the characteristics of the multi-functional combination, economic and practical, low cost.Key words: FPGA; QuartusII; VHDL。