倒装芯片的底部填充工艺

倒装工艺FC和扇出工艺FOWLP第三部分

2.7 Preassembly Underfill对于预装底部填充,底部填充的应用是在基板或晶圆上,并且在倒装芯片组装之前。

G4 [137]首次提出了带有底漆的C4凸块的回流焊,被称为NUF。

如图2.16c所示,Amkor[138]首先研究了在基板上填充非导电性胶(TC-NCP)的C2凸点的高结合力TCB [138],已将其用于为三星的Galaxy智能手机组装高通公司的SNAPDRAGON应用处理器。

在图2.37中NUF和NCP底料可以旋转,用针头分配或真空辅助。

通过从玻璃上芯片技术中学习,研究了C2凸点在晶圆上具有非导电膜(NCF)填充的高结合力TCB。

例如,三洋[139],日立[140、141],东北[142、143],陶氏[144],海力士[145],KAIST/三星[146、147],Amkor / Qualcomm [148]和东丽[ 149–151]用于2.5D / 3DIC集成[7–10]。

图2.38显示了NCF在带有焊料帽凸点晶片的Cu柱上的层压。

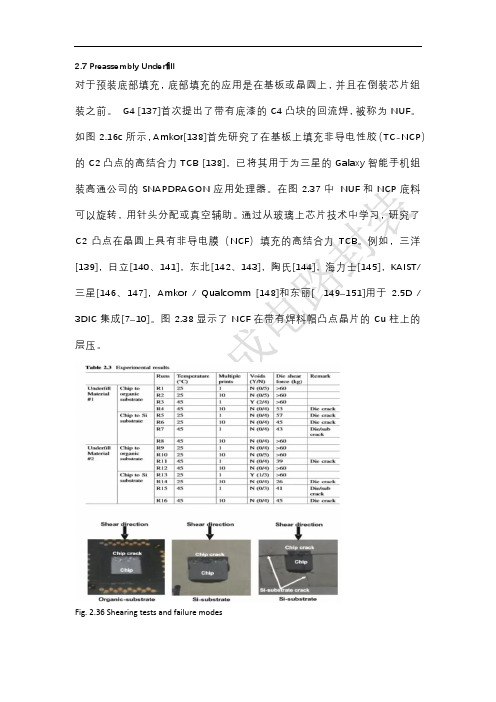

Fig. 2.36 Shearing tests and failure modes三星已经在其基于TSV的双数据速率4型动态随机存取存储器(DRAM)上生产了用于C2芯片和NCF的高键合力TCB(从叠层晶圆切割后)以进行3D IC集成,图2.38,并由Hynix在AMD图形处理器单元(GPU)代码名为Fiji的高带宽内存(HBM)上进行。

这个3D立方体由高强度TCB的C2芯片和NCF一次堆叠在一起,每个芯片需要* 10 s的时间填充胶膜,焊料熔化,胶膜固化和焊料巩固。

吞吐量是个问题!为了解决这个问题,Toray [150,151]提出了一种集体粘合方法,如图2.39所示。

可以看出,带有NCF的C2芯片是在温度= 80°C的阶段上预粘结的(粘结力= 30 N,温度= 150°C,时间<1 s)。

对于后期粘合(第一步(3 s):粘合力= 50 N,温度=220–260°C,第二步(7 s):粘合力= 70 N,温度= 280°C),初期温度= 80°C。

倒装芯片器件封装

电镀法

电镀法

• 在电镀法中,形成UBM之后,在焊盘上涂覆 光刻胶以形成凸点图案。如上图,光刻胶可打 算电镀凸点的外形和高度,因此在电镀凸点前 ,要去除光刻胶残渣。在电镀液中焊料电镀后 ,形成的凸点多为蘑菇状。与其他方法相比, 电镀凸点成分及其高度掌握比较困难,因此多 项选择用共晶钎料,如63Sn/37Pb等。电镀 后,去除光刻胶,钎料凸点在进展重熔过程, 获得球形凸点。

2.3倒装焊封装器件材料的力 学属性

2.3下填充技术

• 下填充工艺有两种,底部流淌填充和底部不流淌填充 ,应依据不同的需求选择适宜的填充工艺。底部流淌 填充工艺,是在毛细外表张力作用下,胶填充芯片和 慕板底部空隙之间,胶的流淌能够使芯片和基板之间 的气体尽量驱除出去,削减气泡的残留。芯片与基板 之间空隙足够大,可选用底部流淌填充工艺,假设芯 片面积特殊大或芯片与基板的空隙小可以选择底部不 流淌填充工艺,应依据不同的需要选择相应的填充工 艺。

• UV型的固化速度快,无温度梯度,故芯 片和基板均不需加热,因此不用考虑由 UV照射固化产生的微弱能量引起的热不 匹配问题。

超声热压倒装芯片焊接法

超声热压倒装芯片焊接法

• 该方法是使用倒装焊接机完成各种凸点 的焊接,由光学摄像对位系统、捡拾热 压超声焊头、准确定位承片台及显示屏 等组成的周密设备。

• 过程:先在基板上涂覆各向异性导电胶 〔ACA〕,将带有凸点的IC芯片与基板 上的金属焊区对位后,在芯片上加压进 展ACA固化,这样导电粒子挤压在凸点 与焊区之间,使上下接触导电。

各向异性导电胶固化法

• ACA的固化形式有热固型、热塑型和紫 外光固化型〔UV〕几种。

倒装芯片的底部填充工艺

倒装芯片的底部填充工艺随着新型基底材料的出现,倒装芯片技术面临着新的挑战,工程师们必须解决裸片和基底间热胀系数的不同引起的问题,以避免在热循环中接头边缘的破裂。

在各种先进的芯片粘接封装技术中,倒装芯片技术较适用于传呼机等小型电子产品、随着裸片尺寸的增加,以及在倒装芯片贴装中采用非陶瓷新型材料作为基底,沿用了20年的传统技术面临着新的挑战。

其中最主要的问题是裸片与基底间热膨胀系数(TCE)的不同。

在先进的倒装芯片产品中,多数底部填充材料都具有最佳流动性、最小热膨胀系数。

目前的固化时间约30分钟。

通常的底训填充材料粘度较低,以便于流入裸片的下方。

因此贮存温度最好恒定在30℃。

当机器内部温度高于30℃时,应将阀体、容器及注射器进行冷却。

底部填充材料的流动与成型不仅受其自身温度的影响,同时还受着基底材料与裸片的温度影响。

将底部填充材料涂敷于基底上时,基底表面和裸片的温度应为70℃-90℃,这样会从裸片下方和基底表面产生向上的气流。

这种表面的撩拨可减少在裸片底部产生填充气泡,避免涂料在长期使用中失效,同时可确保填充材料在裸片下方的适量填充。

温度的不同或不均会导致非线性填充,从而使空气内陷形成气泡。

因此必须采用闭环系统对基底温度进行控制,对于非接触式系统,温控精度应至少在±2℃;而对于在基底下采用加热真空夹盘的接触式系统则应高于±2℃。

在进入涂敷区前,基底应再加热以达到所要求的温度,因此还必须增加一个预热阶段。

在涂敷阶段,另外一个加热装置用于保持基板与裸片的温度。

在第三阶段(这是一个根据具体情况而选择的阶段),可用于在进入固化炉前协助填充材料正确流动或略微的凝固。

接触式与非接触式加热系统的选择十分简单,只需通过选择灵活的加工方式或专用的加工方式即可。

对于薄膜基底,只能选择接触式加热装置,该装置采用真空加热夹盘,在预热、保持和回流三个阶段在对薄膜基底进行加热。

而在采用AUER拖板或其它专用传输工具以及引线框的场合,接触式加热系统是最好的方法。

倒装芯片技术-PPT

对 UBM的要求-02

➢ 要有焊料扩散阻挡层:必须在焊料与焊盘焊区金属之 间提供一个扩散阻挡层

➢ 要有一个可以润湿焊料的表面:最后一层要直接与凸 点接触,必须润湿凸点焊料。

对 UBM的要求-03

可靠性

与一般的焊点连接一样,热压倒装芯片连接的可靠性也要 受到基板与芯片的热膨胀系数(CTE)失配的影响,此外焊点的高度 、焊点之间的最大间距亦会对可靠性造成影响。连接区的裂纹多 是在从连接温度冷却下来的过程中产生的。

由于金的熔点温度高,因此它对疲劳损伤的敏感程度远小于 焊料。因此,如果在热循环中应力没有超过凸点与焊盘之间的连 接强度,那么可靠性不会存在太大问题。

芯片与基底之间的底部填充材料使连接抵抗热疲劳的 性能显著提高,如果没有底部填充,则热疲劳将是倒装芯 片主要的可靠性问题。

生产问题

倒装芯片的连接头应该能够产生300°C 的连接温 度, 要有较高的平行对准精度,为了防止半导体材料 发生损伤,施加压力时应该保持一定的梯度。在热压倒 装芯片连接中,凸点发生变形是不可避免的,这也是形 成良好连接所必需的。另外,连接压力和温度应该尽可 能低,以免芯片和基板损坏。

点是:

• 简单,无需使用焊剂 • 工艺温度低

• 可以实现细间距连接

若干问题

对于直径为80mm的凸点, 热压压力可以达到1N。由 于压力较大,温度也较高,这种工艺仅适用于刚性基底, 如氧化铝或硅。另外,基板必须保证较高的平整度,热压 头也要有较高的平行对准精度。为了避免半导体材料受到 不必要的损害,施加压力时应该有一定的梯度。

由此模型可知:

要提高可靠性必须要求:

微电子技术之倒装芯片技术-

微电子技术之倒装芯片技术倒装芯片是一种无引脚结构,一般含有电路单元。

设计用于通过适当数量的位于其面上的锡球(导电性粘合剂所覆盖,在电气上和机械上连接于电路。

在微电子领域中起着重要的作用,是微电子大家庭中不可缺少的一员。

倒装芯片英文名为Flip chip。

其起源于60年代,由IBM率先研发出,具体原理是在I/Opad 上沉积锡铅球,然后将芯片翻转加热利用熔融的锡铅球与陶瓷板相结合,此技术已替换常规的打线接合,逐渐成为未来封装潮流。

Flip Chip既是一种芯片互连技术,又是一种理想的芯片粘接技术.早在30年前IBM公司已研发使用了这项技术。

但直到近几年来,Flip-Chip 已成为高端器件及高密度封装领域中经常采用的封装形式。

今天,Flip-Chip封装技术的应用范围日益广泛,封装形式更趋多样化,对Flip-Chip封装技术的要求也随之提高。

同时, Flip-Chip也向制造者提出了一系列新的严峻挑战,为这项复杂的技术提供封装,组装及测试的可靠支持。

以往的一级封闭技术都是将芯片的有源区面朝上,背对基板和贴后键合,如引线健合和载带自动健全(TAB。

FC则将芯片有源区面对基板,通过芯片上呈阵列排列的焊料凸点实现芯片与衬底的互连.硅片直接以倒扣方式安装到PCB从硅片向四周引出I/O,互联的长度大大缩短,减小了RC延迟,有效地提高了电性能.显然,这种芯片互连方式能提供更高的I/O密度.倒装占有面积几乎与芯片大小一致.在所有表面安装技术中,倒装芯片可以达到最小、最薄的封装。

其次倒装芯片技术是芯片以凸点阵列结构与基板直接安装互连的一种方法。

不仅如此倒装芯片是在在I/O pad上沉积锡铅球,然后将芯片翻转加热利用熔融的锡铅球与陶瓷机板相结合此技术替换常规打线接合,逐渐成为未来的封装主流,当前主要应用于高时脉的CPU、GPU(GraphicProcessor Unit及Chipset 等产品为主。

与COB 相比,该封装形式的芯片结构和I/O端(锡球方向朝下,由于I/O引出端分布于整个芯片表面,故在封装密度和处理速度上Flip chip已达到顶峰,特别是它可以采用类似SMT技术的手段来加工,因此是芯片封装技术及高密度安装的最终方向。

倒装芯片底部填充工艺

倒装芯片底部填充工艺梁凤梅(太原理工大学,山西 太原 030024)摘 要:从热疲劳故障的角度论述了倒装芯片底部填充的必要性,介绍了倒装芯片底部填充的参数控制。

通过正确的底部填充,可提高倒装芯片组装的成品率和可靠性。

关键词:倒装片;可靠性;生产辅料中图分类号:TN 4 文献标识码:A 文章编号:1001-3474(2000)06-0252-03Flip Chip Underfill TechnologyLIANG Feng -mei(Taiyuan University of Technology,Taiyuan 030024,China)Abstract:Discuss the necessary of flip chip underfill to thermal fatigue failures.Put forward controlling parameter for flip chip underfill.Then show that correct underfill can dramatically increase thermal reliability.key words:Flip chip;Reliability;Manufacture subsidiaryDocument Code:A Article ID:1001-3474(2000)06-0252-03尽管有一些成熟的工艺适用于PCB 的芯片贴装,但倒装片(FC)技术是最独特的。

倒装片是一种直接芯片贴装(DC A)技术。

先在芯片底部制作出很小的焊接用凸起阵列,然后将芯片倒转装在基板上。

随着芯片尺寸的增加,以及在倒装片贴装中采用非陶瓷新型材料作为基底,沿用了20年的传统技术面临着新的挑战。

倒装片工艺的关键问题之一是由于热膨胀系数(TCE)不同而引起的芯片与基板之间的应力,为了消除这一应力,下填充工艺被应用于基板与芯片之间。

LED芯片倒装工艺原理以及应用简介

LED芯片倒装工艺原理以及应用简介倒装晶片所需具备的条件:①基材材是硅;②电气面及焊凸在元件下表面;③组装在基板后需要做底部填充。

倒装晶片的定义:其实倒装晶片之所以被称为“倒装”是相对于传统的金属线键合连接方式(Wire Bonding)与植球后的工艺而言的。

传统的通过金属线键合与基板连接的晶片电气面朝上,而倒装晶片的电气面朝下,相当于将前者翻转过来,故称其为“倒装晶片”。

倒装芯片的实质是在传统工艺的基础上,将芯片的发光区与电极区不设计在同一个平面这时则由电极区面朝向灯杯底部进行贴装,可以省掉焊线这一工序,但是对固晶这段工艺的精度要求较高,一般很难达到较高的良率。

倒装芯片与与传统工艺相比所具备的优势:通过MOCVD技术在兰宝石衬底上生长GaN基LED结构层,由P/N结髮光区发出的光透过上面的P型区射出。

由于P型GaN传导性能不佳,为获得良好的电流扩展,需要通过蒸镀技术在P区表面形成一层Ni-Au组成的金属电极层。

P区引线通过该层金属薄膜引出。

为获得好的电流扩展,Ni-Au金属电极层就不能太薄。

为此,器件的发光效率就会受到很大影响,通常要同时兼顾电流扩展与出光效率二个因素。

但无论在什麼情况下,金属薄膜的存在,总会使透光性能变差。

此外,引线焊点的存在也使器件的出光效率受到影响。

采用GaN LED倒装芯片的结构可以从根本上消除上面的问题。

倒装LED芯片技术行业应用分析:近年,世界各国如欧洲各国、美国、日本、韩国和中国等皆有LED照明相关项目推行。

其中,以我国所推广的“十城万盏”计划最为瞩目。

路灯是城市照明不可缺少的一部分,传统路灯通常采用高压钠灯或金卤灯,这两种光源最大的特点是发光的电弧管尺寸小,可以产生很大的光输出,并且具有很高的光效。

但这类光源应用在道路灯具中,只有约40%的光直接通过玻璃罩到达路面,60%的光通过灯具反射器反射后再从灯具中射出。

因此目前传统灯具基本存在两个不足,一是灯具直接照射的方向上照度很高,在次干道可达到50Lx以上,这一区域属明显的过度照明,而两个灯具的光照交叉处的照度仅为灯下中心位置的照度的20%-40%,光分布均匀度低;二是此类灯具的反射器效率一般仅为50%-60%,因此在反射过程中有大量的光损失,所以传统高压钠灯或金卤灯路灯总体效率在70-80%,均匀度低,且有照度的过度浪费。

倒装芯片技术分析

倒装芯片技术分析摘要倒装芯片封装技术(fc)是由ibm公司在上个世纪60年代开发的,即将芯片正面朝下向基板进行封装。

本文论述了倒装芯片技术的优点,并对其凸点形成技术、测试技术、压焊技术和下填充技术进行了分析,为倒装芯片技术的发展提供借鉴。

关键词倒装芯片技术;优点;凸点技术;测试技术;压焊技术;下填充技术中图分类号tn43 文献标识码a 文章编号1674-6708(2010)25-0169-020 引言倒装芯片封装技术(fc)是由ibm公司在上个世纪60年代开发的,即将芯片正面朝下向基板进行封装。

15年前,几乎所有封装采用的都是引线键合,如今倒装芯片技术正在逐步取代引线键合的位置,这种封装方式无需引线键合,因此可以形成最短电路,从而降低电阻;并且采用金属球进行连接可以缩小封装尺寸,改善电性表现,从而解决了bga为增加引脚数而需扩大体积的困扰。

采用倒装芯片封装技术可以降低生产成本,提高速度及组件的可靠性。

1 倒装芯片技术的优点1.1 完整性、可靠性强倒装芯片相当于一个完全封装的芯片,它是由锡球下的冶金与芯片钝化层密封的,并提供下一级封装的内连接结构。

将一个构造合理的倒装芯片安装在适当载体上用于内连接,即使没有其他灌封,该载体也可以满足所有可靠性要求。

1.2 自我对准能力强在锡球回流时,焊锡受表面张力的作用,可以自动纠正芯片微小的对准偏差,从而提供了装配制造的合格率。

同时倒装芯片技术也提供低电感,在高频应用中起到至关重要的作用。

1.3 将电源带入芯片的每个象限倒装芯片技术可以将电源带入芯片的每个象限,即在整个芯片面积上,其电流是均匀分布的。

1.4 成本低廉倒装芯片技术消除了封装并减小了芯片的尺寸,因此节省了硅的使用量,降低了制作成本。

2 倒装芯片技术分析2.1 形成凸点技术凸点形成技术可以分为淀积金属、机械焊接、基于聚合物的胶粘剂等几个类型。

1)金属电镀技术一般是在电镀槽里,把基片当作阴极,利用静态电流或者脉冲电流来完成焊料的电镀。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

倒装芯片的底部填充工艺

随着新型基底材料的出现,倒装芯片技术面临着新的挑战,工程师们必须解决裸片和基底间热胀系数的不同引起的问题,以避免在热循环中接头边缘的破裂。

在各种先进的芯片粘接封装技术中,倒装芯片技术较适用于传呼机等小型电子产品、随着裸片尺寸的增加,以及在倒装芯片贴装中采用非陶瓷新型材料作为基底,沿用了20年的传统技术面临着新的挑战。

其中最主要的问题是裸片与基底间热膨胀系数(TCE)的不同。

在先进的倒装芯片产品中,多数底部填充材料都具有最佳流动性、最小热膨胀系数。

目前的固化时间约30分钟。

通常的底训填充材料粘度较低,以便于流入裸片的下方。

因此贮存温度最好恒定在30℃。

当机器内部温度高于30℃时,应将阀体、容器及注射器进行冷却。

底部填充材料的流动与成型不仅受其自身温度的影响,同时还受着基底材料与裸片的温度影响。

将底部填充材料涂敷于基底上时,基底表面和裸片的温度应为70℃-90℃,这样会从裸片下方和基底表面产生向上的气流。

这种表面的撩拨可减少在裸片底部产生填充气泡,避免涂料在长期使用中失效,同时可确保填充材料在裸片下方的适量填充。

温度的不同或不均会导致非线性填充,从而使空气内陷形成气泡。

因此必须采用闭环系统对基底温度进行控制,对于非接触式系统,温控精度应至少在±2℃;而对于在基底下采用加热真空夹盘的接触式系统则应高于±2℃。

在进入涂敷区前,基底应再加热以达到所要求的温度,因此还必须增加一个预热阶段。

在涂敷阶段,另外一个加热装置用于保持基板与裸片的温度。

在第三阶段(这是一个根据具体情况而选择的阶段),可用于在进入固化炉前协助填充材料正确流动或略微的凝固。

接触式与非接触式加热系统的选择十分简单,只需通过选择灵活的加工方式或专用的加工方式即可。

对于薄膜基底,只能选择接触式加热装置,该装置采用真空加热夹盘,在预热、保持和回流三个阶段在对薄膜基底进行加热。

而在采用AUER拖板或其它专用传输工具以及引线框的场合,接触式加热系统是最好的方法。

接触式加热温度分布比较均匀。

例如:倒装芯片可能有多种尺寸,从3mm2至12mm2甚至20mm2。

如果采用专用工具,用一套工具即可对各种元件进行处理。

接触加热的唯一个缺点是生产灵活性差,但由于其升温速度快、温度均匀,因此用10分钟来变换生产工具也就微不足道了。

在用标准的FR4 PCB作为基底时,例如用于承包式封装的倒装芯片底部填充,在这种封装中板子尺寸会变化很大。

此时,使用非接触式加热较好。

尽管此时温度上升速度与温度均匀性不可兼顾,然而,基底尺寸可随要求变化而不会导致生产的停止,这一点对转包商来说又是明显的优点。

随着倒装芯片技术在主流电子工业中应用越来越广泛,制造商应该能提供灵活的非接触式加热系统。

旋转阀技术

旋转正向位移阀可进行精确度高、重复性好的底部填充。

例如。

Speedline CAMALOT公司的680系列阀可进行低粘度底部填充材料的涂敷,同时其正向材料关闭阀可封闭针头,

防止拖滴。

该阀带有由软件驱动的闭环电机控制器,即使填充材料的比重不稳定也可监视并自动控制涂敷量。

这一体积测量系统(VMS)可选配在Speedline CAMALOT倒装芯片底部填充或封装涂敷系统上。

另外一项技术能使阀准确定位于裸片上方(定位水平轴x-y)并测量出高度(z轴)以确保阀体定位准确。

预备步骤是为了使针头尽量接近裸片边缘,防止对裸片周边造成污染。

同时还需让针头正好略低于棵片的下表面,以确保涂敷足够的粘合剂。

只要针头足够接近裸片的边缘且高度合适,沿裸片边缘所涂敷的粘合剂便会快速均匀地流入底面。

工艺控制

工艺性能,或者是CpK,已在多数用户工艺要求中成为一个重要特性,制造商也努力控制废料以提高产能和利润。

尽管底部填充是一种可控工艺流程,但是用传统的泵涂技术还达不到其精度。

不过,随着新方式的出现,Speedline CAMALOT的正向位移活塞泵涂敷系统已经能够满足甚至超过这种重复性要求,使得器件制造商对倒装芯片底部填充工艺能够进行严格的控制。

CAMALOT的这一新技术是采用一个加热的多活塞泵产生出优于±1%的重复精度而不需要再填充。

自动重量校正系统可以设置预定重量,并进行精度高、重复性好的底部填充。

表面张力和加热温度是底部填充产生毛细现象的二个主要因素。

底部。

填充工艺的工作原理是在表面张力的协助下,用低于30℃的常规底部填充材料置换裸片下方的热介质。

由于热力及表面张力的驱动,低部填充材料在被称为“毛细现象”的作用下“爬入”裸片下的空间。

对于较大的裸片,可能需要多条填充路径,不同情况下,采用不同的涂敷模式。

针头沿边缘移动的方式与顺序均会影响气泡的产生。

对小于3mm2的裸片,一条填充路径即可。

而对大于3mm2、小于6mm2,的芯片,可进行双面涂敷并采用“L”形路径。

“L”形路径可用两种不同的方法得到。

另一个屡经争议的问题是:是否需要沿裸片的另外三侧进行涂敷?目前为止,人们还认为另外三侧的涂敷只起纯粹的装饰作用,是对材料与时间的浪费。

但是,最近的研究表明,如果不进行这三侧的徐敷,原涂敷面会形成大量的堆积,固化时裸片会受到

不均匀应力的作用,在一定情况下会将裸片掀起甚至破坏连接。

倒装芯片中实现成功的底部填充的关键因素包括基底和材料温度的精确控制、涂敷阀和涂敷平台的可重复性、体积控制、涂敷模式。

随着器件尺寸的小型化和产量的增加,这些因素的精确控制将变得更为重要,并且更符合客户要求。