第三章组合逻辑电路 ppt课件

合集下载

03A第三章-组合逻辑电路PPT课件

.

15

例1:试用与非门和反相器设计一个优先排队电路。火车有特快、直快和慢车。

它们进出站的优先次序是:特快、直快、慢车,同一时刻只能有一列车 进出。

解:1)由题意进行逻辑抽象。 输入变量及逻辑状态定义:

有无特快正准备进出站定义为变量A。A=1表示有特快正准备进出站, 反之A=0

同理,将有无直快和慢车正准备进出站分别定义为变量B、C

2. 列出真值表

3. 确定逻辑功能: 奇校验电路

ABC 000 001 010 011 100 101 110 111

.

ZAB L(ABC)

0

0

0

1

1

1

1

0

1

1

1

0

0

0

0

1

5

例3 已知电路如图所示,试分析该电路的逻辑功能。

&

P2

A B

&

P1

P3

F

Байду номын сангаас

C

&

>=1

P4

&

.

6

解:1.根据逻辑电路图写出逻辑表达式

(1)若组合电路已经给定,一般要求对其进行分析

(2)若组合电路只给出功能要求,一般要对其进行设计

.

2

3.1 组合逻辑电路的分析

分析目的: 说明给定电路的逻辑功能

分析步骤: (1) 由逻辑电路图写出逻辑表达式;

(2) 化简和变换各逻辑表达式;

(3) 列出真值表;

(4) 据真值表和表达式对逻辑电路进行分析,

组合电路分类:

按逻辑功能特点,可分为:加法器、比 较器、编码器、译码器、数据选择器、 数据分配器、只读存储器等等

数字电路与逻辑设计PPT课件

Cn+1 Dn

0

0

1

1

1

1

1

0

0

1

0

0

0

0

1

1

第3章 组合逻辑电路

AnBn

AnBn

An Bn

全 减

Dn

Cn 0

00 0

01 1

11 0

10 0

Cn 00 01 11 10 00 1 0 1

Cn

器

Cn+1 1 1

1

1

0

11 0 1 0

(a)

(b)

(c)

全减器框图及K图 (a) 框图; (b) Cn+1; (c) Dn

0 0 0

带编码器的MCU应用电路

3.3.2 译码器

第3章 组合逻辑电路

将二进制代码转换成不同的输出 信号的过程称为译码。常用的MSI译码器 为74HC138(3-8Line Decoder)。

② 根据输出函数表达式列出真值表。

③ 确定电路的逻辑功能。

第3章 组合逻辑电路

【例3-1】分析图所示电路,指出该电路 的逻辑功能。

Ai

=1

=1

Bi

Si

Ci

& ≥1

Ai Bi

∑

Si

1

Ci+1 Ci

Ci+1

(a)

(b)

解: ① 写出函数表达式。

第3章 组合逻辑电路

Si Ai Bi Ci Ci1 ( Ai Bi )Ci Ai Bi

第3章 组合逻辑电路

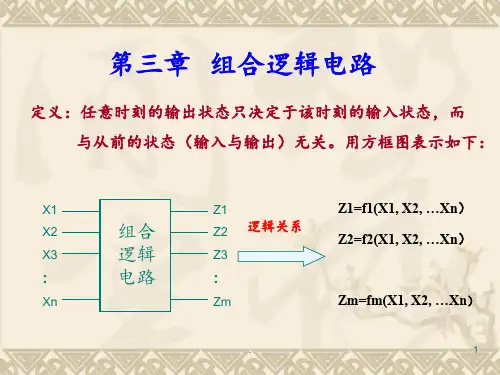

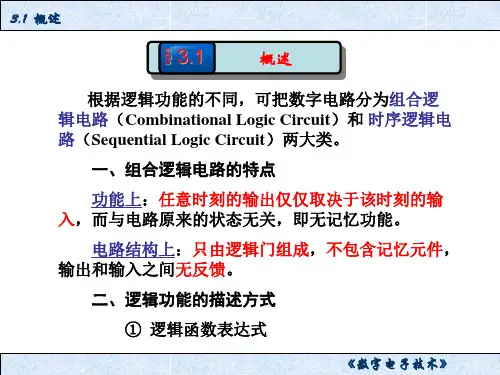

组合逻辑电路:任何时候的输 出仅仅取决于该时刻的输入,而与电路原 来的状态没有任何关系。输出状态随着输 入信号的改变而改变。

第三章 组合逻辑电路PPT课件

或非门同样可组成实现各种逻辑功能的逻辑电 路。所以,或非门也是一种通用门。

10

3 、 “与或非” 门

"与或非"门也是一种通用门。

仅当每一个“与项”均为0时,才能使F为1, 否则F为0。

11

4、" 异或 " 门

“ 异或 ” 运算是一种特殊的逻辑运算 , 用符号 表示.

变量A、B取值相同,F为0;变量A、B取值相异,F为1。

24

25

3.3组合逻辑电路的分析

分析的任务:根据给定的组合电路,写出逻辑函数表 达式,并以此来描述它的逻辑功能,确定输入与输出 的关系,必要时对其设计的合理性进行评定。

分析的一般步骤: 第一步: 写出给定组合电路的逻辑函数表达式 第二步: 化简逻辑函数表达式 第三步: 根据化简的结果列出真值表 第四步: 功能评述

“ 同或 ” 运算用符号 表示, 逻辑表达式为:

变量A、B取值相同,F为1;变量A、B取值相异,F为0。

由于同或实际上是异或之非,所以实际应用中通常 用异或门加非门实现同或运算。

12

3.2逻辑函数的实现

函数的表现形式和实际的逻辑电路之间有着对 应的关系,而实际逻辑电路大量使用 “ 与 非 ” 门、 “ 或非 ” 门、 “ 与或非 ” 门 等。

1、“ 与非 ” 门

使用 “ 与非 ” 门可以实现 “ 与 ” 、 “ 或 ” 、 “ 非 ”3 种基本运算 , 并可构 成任何逻辑电路 , 故称为通用逻辑门。

只要变量有一个为0,则函数F为1;仅当变 量全部为1时,函数F为0。

9

2、 “ 或非 ” 门

只要变量中有一个为1,则函数F为0;仅当变 量全部为0时,函数F为1。

闭合 不闭合

闭合 闭合

10

3 、 “与或非” 门

"与或非"门也是一种通用门。

仅当每一个“与项”均为0时,才能使F为1, 否则F为0。

11

4、" 异或 " 门

“ 异或 ” 运算是一种特殊的逻辑运算 , 用符号 表示.

变量A、B取值相同,F为0;变量A、B取值相异,F为1。

24

25

3.3组合逻辑电路的分析

分析的任务:根据给定的组合电路,写出逻辑函数表 达式,并以此来描述它的逻辑功能,确定输入与输出 的关系,必要时对其设计的合理性进行评定。

分析的一般步骤: 第一步: 写出给定组合电路的逻辑函数表达式 第二步: 化简逻辑函数表达式 第三步: 根据化简的结果列出真值表 第四步: 功能评述

“ 同或 ” 运算用符号 表示, 逻辑表达式为:

变量A、B取值相同,F为1;变量A、B取值相异,F为0。

由于同或实际上是异或之非,所以实际应用中通常 用异或门加非门实现同或运算。

12

3.2逻辑函数的实现

函数的表现形式和实际的逻辑电路之间有着对 应的关系,而实际逻辑电路大量使用 “ 与 非 ” 门、 “ 或非 ” 门、 “ 与或非 ” 门 等。

1、“ 与非 ” 门

使用 “ 与非 ” 门可以实现 “ 与 ” 、 “ 或 ” 、 “ 非 ”3 种基本运算 , 并可构 成任何逻辑电路 , 故称为通用逻辑门。

只要变量有一个为0,则函数F为1;仅当变 量全部为1时,函数F为0。

9

2、 “ 或非 ” 门

只要变量中有一个为1,则函数F为0;仅当变 量全部为0时,函数F为1。

闭合 不闭合

闭合 闭合

《数字电子技术基础》第3章.组合逻辑电路PPT课件

3.4 典型组合逻辑电路及其应用

3.4.3 数据选择器

示意图数据选择器 (multiplexer,MUX)又 称多路选择器或多路开关, 是应用比较广泛的中规模 组合逻辑电路,尤其是电 子设计自动化技术发展成 熟的今天。

图3.4.19 数据选择器

3.4 典型组合逻辑电路及其应用

1.典型数据选择器

1)双4选1数据选择器74153

3.2.2 冒险现象的判断

1.代数法

2.卡诺图法

3.2 组合逻辑电路中的竞争冒险与消除方法

3.2.3 冒险现象的消除方法

1.增加冗余项

2.输出接滤波电容

3.增加选通信号

3.3 VHDL的顺序行为

3.3.1 进程语句

进程本身是并行行为,且存在于结构体中。进程内 部的语句要进入进程之后才能顺序执行。进入进程是靠敏 感信号发生变化的时候,称此时为“激活”进程。若敏感 信号同时激活多个进程,进程是按并行行为执行的。进程 语句的一般形式如下:

(1)第2号不能与第7号同时配用。 (2)第3号和第6号必须同时配用。 (3)同时用第4、9号时,必须配用11号。

请设计一个逻辑电路,在违反上述任何一个规定时,发出 报警指示信号。

解:(1)设置11种化学试剂为输入信号,2对应A,7对应B, 3对应C,6对应D,4对应E,9对应F和11对应G。设置F1、F2和F3 分别为违反3种规定的输出。

<进程标号> :PROCESS<敏感信号表> <进程说明区> BEGIN <语句部分> WAIT ON<敏感信号表> ; UNTIL<条件表达式> ; WAIT FOR<时间表达式> ; END PROCESS;

第三章组合逻辑电路ppt课件

图3.3.1 3位二进制普通编码器框图 《数字电子技术》

3.3 若干常用中规模组合逻辑电路 表3-3-1 3位二进制普通编码器真值表

《数字电子技术》

3.3 若干常用中规模组合逻辑电路

由于普通编码器在任何时刻 I0 ~ I7 当中仅有一个 取值为1,即只有真值表中所列的8种状态,而且它

的( 28 8 )种状态均为约束项。因此,由真值表

A

&

1

F2

C

B

&

C

图3.2.1 【例1】逻辑电路图

《数字电子技术》

3.2 组合逻辑电路的分析和设计方法

§3.2.2 组合逻辑电路的设计方法

所谓“设计”:即根据给出的实际逻辑问题,求出实 现这个逻辑功能的最简逻辑电路。

所谓“最简”:是指所用器件最少,器件种类最少, 而且器件之间的连线也最少。

一、设计步骤 (1)进行逻辑抽象

【例1】试用两片74LS148接成16线-4线优先编码器,

将-的优11先11权’最1低6个。146位个二低进A电0A制平1~5代输A码1入5 ,信其号中

编为‘0000

的A优0 先权最高,

接成的电路图如图3.3.4所示:

《数字电子技术》

3.3 若干常用中规模组合逻辑电路

图3.3.4 用两片74LS148接成的16线-4线优先编码器逻辑图

I7

)

S

Y0 (I1I2 I4 I6 I3 I4 I6 I5 I6 I7 ) S

(由功能表第一行体现)。

《数字电子技术》

3.3 若干常用中规模组合逻辑电路

(2)YS 为选通输出端,其表达式为:

YS I0 I1 I2 I3 I4 I5 I6 I7 S

此式表明:只有当所有的编码输入端均为高 电平(即没有编码输入),且S=1( S 0 )

3.3 若干常用中规模组合逻辑电路 表3-3-1 3位二进制普通编码器真值表

《数字电子技术》

3.3 若干常用中规模组合逻辑电路

由于普通编码器在任何时刻 I0 ~ I7 当中仅有一个 取值为1,即只有真值表中所列的8种状态,而且它

的( 28 8 )种状态均为约束项。因此,由真值表

A

&

1

F2

C

B

&

C

图3.2.1 【例1】逻辑电路图

《数字电子技术》

3.2 组合逻辑电路的分析和设计方法

§3.2.2 组合逻辑电路的设计方法

所谓“设计”:即根据给出的实际逻辑问题,求出实 现这个逻辑功能的最简逻辑电路。

所谓“最简”:是指所用器件最少,器件种类最少, 而且器件之间的连线也最少。

一、设计步骤 (1)进行逻辑抽象

【例1】试用两片74LS148接成16线-4线优先编码器,

将-的优11先11权’最1低6个。146位个二低进A电0A制平1~5代输A码1入5 ,信其号中

编为‘0000

的A优0 先权最高,

接成的电路图如图3.3.4所示:

《数字电子技术》

3.3 若干常用中规模组合逻辑电路

图3.3.4 用两片74LS148接成的16线-4线优先编码器逻辑图

I7

)

S

Y0 (I1I2 I4 I6 I3 I4 I6 I5 I6 I7 ) S

(由功能表第一行体现)。

《数字电子技术》

3.3 若干常用中规模组合逻辑电路

(2)YS 为选通输出端,其表达式为:

YS I0 I1 I2 I3 I4 I5 I6 I7 S

此式表明:只有当所有的编码输入端均为高 电平(即没有编码输入),且S=1( S 0 )

数字电子技术基础 第3章 组合逻辑电路1PPT课件

2. 列真值表

3. 写输出表达式并化简

ABCY

YA B C A B CAC B ABC0 0 0 0 001 0

BC AB CAC B

010 0

B C A C AB 最简与或式 最简与非-与非式

011 1 100 0 101 1

YBC AC AB

110 1 111 1

BC AC AB

4. 画逻辑图 — 用与门和或门实现 YB C A C AB — 用与非门实现 YBC AC AB

统分析。

二、分析举例 [例] 分析图中所示电路的逻辑功能

A B

&

C

[解] 表达式

真值表

& ≥1 Y A B C Y A B C Y

000 1 100 0 001 0 101 0 010 0 110 0

011 0 111 1

YAB A C AB B C AB C C AB A C BC

ABC ABC

3. 列真值表

ABCD Y 0000 0 0001 1 0010 1 0011 0 0100 1 0101 0 0110 0 0111 1

ABCD Y 1000 1 1001 0 1010 0 1011 1 1100 0 1101 1 1110 1 1111 0

4. 功能说明: 当输入四位代码中 1 的个数为奇数时输出

第三章 组合逻辑电路

电子技术 数字电路部分

第三章

组合逻辑电路

第三章 组合逻辑电路

整体概况

+ 概况1

您的内容打在这里,或者通过复制您的文本后。

概况2

+ 您的内容打在这里,或者通过复制您的文本后。

概况3

+ 您的内容打在这里,或者通过复制您的文本后。

第3章组合逻辑电路 ppt课件.ppt

判断电路的逻辑功能。

例3-1

➢试分析图3-2所示电路的逻辑功能。

A1

1

解: ⑴由图3-2写出逻 & F3 辑表达式

& F2

F0 A1 A0

A0

1

& F1 & F0

F1 A1 A0 F2 A1 A0

/3/16

东北大学信息学院

8

例3-1

F0 A1 A0 F1 A1 A0

CI

=1

S

& ≥1 1 CO

3.1组合逻辑电路特点及表示方法

➢电路结构特点:

仅由门电路组成; 电路中无记忆元件,输入输出之间无反馈。

A =1 B

CI

=1

S

& ≥1 1 CO

3.1组合逻辑电路特点及表示方法

➢组合逻辑电路的表示方法有:

函数表达式

真值表或功能表

逻辑图

卡诺图

A =1

工作波形图 B

=1

CI & ≥1

F2 A1 A0

F3 A1 A0

⑵列出真值表 表3-1 例3-1真值表

2021/3/16

A1 A0 F0 F1 F2 F3

0 0 1000

0 1 01 0 0

1 0 0010

1 1 0001

东北大学信息学院

9

例3-1

➢⑶确定逻辑功能:

表3-1 例3-1真值表

A1 A0

00 01 10 11

F0 F1 F2 F3

⑵列出真值表

⑶确定逻辑功能

A1 A0

F

00

D0

01

D1

10

D2

11

D3

202➢1/3/电16 路具有选择数东北据大学信输息学入院 功能。

例3-1

➢试分析图3-2所示电路的逻辑功能。

A1

1

解: ⑴由图3-2写出逻 & F3 辑表达式

& F2

F0 A1 A0

A0

1

& F1 & F0

F1 A1 A0 F2 A1 A0

/3/16

东北大学信息学院

8

例3-1

F0 A1 A0 F1 A1 A0

CI

=1

S

& ≥1 1 CO

3.1组合逻辑电路特点及表示方法

➢电路结构特点:

仅由门电路组成; 电路中无记忆元件,输入输出之间无反馈。

A =1 B

CI

=1

S

& ≥1 1 CO

3.1组合逻辑电路特点及表示方法

➢组合逻辑电路的表示方法有:

函数表达式

真值表或功能表

逻辑图

卡诺图

A =1

工作波形图 B

=1

CI & ≥1

F2 A1 A0

F3 A1 A0

⑵列出真值表 表3-1 例3-1真值表

2021/3/16

A1 A0 F0 F1 F2 F3

0 0 1000

0 1 01 0 0

1 0 0010

1 1 0001

东北大学信息学院

9

例3-1

➢⑶确定逻辑功能:

表3-1 例3-1真值表

A1 A0

00 01 10 11

F0 F1 F2 F3

⑵列出真值表

⑶确定逻辑功能

A1 A0

F

00

D0

01

D1

10

D2

11

D3

202➢1/3/电16 路具有选择数东北据大学信输息学入院 功能。

第三章组合逻辑电路PPT课件

第26页/共73页

共阴极半导体7段数码管BS201 a)管脚排列图 b)内部接线图

第27页/共73页

共阳极LED数码管 a)管脚排列图 b)内部接线图

第28页/共73页

各段笔划的组合能显示出十进制数0~9及某些英文字母。 半导体数码管的优点是工作电压低(1.7~1.9V),体积 小,可靠性高,寿命长(大于一万小时),响应速度快(优 于10ηs),颜色丰富等,目前已有高亮度产品,缺点是耗电 比液晶数码管大,工作电流一般为几毫安至几十毫安。

第50页/共73页

74HC138所构成的八路数据分配器的逻辑框图

第51页/共73页

五、数据比较器

在数字系统中,经常需要对两组二进制数或二—十进制数 进行比较,用来比较两组数字的电路称为数字比较器。只比 较两组数字是否相等的数字比较器称同比较器。不但比较两 组数是否相等,而且还比较两组数的大小的数字比较器称大 小比较器或称数值比较器。下面只介绍数值比较器。

液晶数字显示器的交流驱动电路

第32页/共73页

2.七段显示译码器

第33页/共73页

例如: 对于8421BCD码的0101状态,对应的十进制数为5,译码驱动器应使分段式数码

管的a、c、d、f、g各段为高电平,而b、e两段为低电平。

第34页/共73页

74HC48应用于高电平驱动的共阴极显示器。当输入信号为 0000~1001时,分别显示0~9数字信号:

或非门的等效变换 a)原逻辑图 b)等效逻辑图

第3页/共73页

三、组合逻辑电路的设计方法

组合逻辑电路的设计,就是根据逻辑功能的要求,设计出 具体的组合电路。一般设计方法分四个步骤进行:

1.首先对命题要求的逻辑功能进行分析,确定哪些是输 入变量,哪些是输出变量以及它们之间的相互关系;然后对 它们进行逻辑赋值,即确定什么情况下为逻辑1,什么情况 下为逻辑0。这一步骤是设计组合逻辑电路的关键。

共阴极半导体7段数码管BS201 a)管脚排列图 b)内部接线图

第27页/共73页

共阳极LED数码管 a)管脚排列图 b)内部接线图

第28页/共73页

各段笔划的组合能显示出十进制数0~9及某些英文字母。 半导体数码管的优点是工作电压低(1.7~1.9V),体积 小,可靠性高,寿命长(大于一万小时),响应速度快(优 于10ηs),颜色丰富等,目前已有高亮度产品,缺点是耗电 比液晶数码管大,工作电流一般为几毫安至几十毫安。

第50页/共73页

74HC138所构成的八路数据分配器的逻辑框图

第51页/共73页

五、数据比较器

在数字系统中,经常需要对两组二进制数或二—十进制数 进行比较,用来比较两组数字的电路称为数字比较器。只比 较两组数字是否相等的数字比较器称同比较器。不但比较两 组数是否相等,而且还比较两组数的大小的数字比较器称大 小比较器或称数值比较器。下面只介绍数值比较器。

液晶数字显示器的交流驱动电路

第32页/共73页

2.七段显示译码器

第33页/共73页

例如: 对于8421BCD码的0101状态,对应的十进制数为5,译码驱动器应使分段式数码

管的a、c、d、f、g各段为高电平,而b、e两段为低电平。

第34页/共73页

74HC48应用于高电平驱动的共阴极显示器。当输入信号为 0000~1001时,分别显示0~9数字信号:

或非门的等效变换 a)原逻辑图 b)等效逻辑图

第3页/共73页

三、组合逻辑电路的设计方法

组合逻辑电路的设计,就是根据逻辑功能的要求,设计出 具体的组合电路。一般设计方法分四个步骤进行:

1.首先对命题要求的逻辑功能进行分析,确定哪些是输 入变量,哪些是输出变量以及它们之间的相互关系;然后对 它们进行逻辑赋值,即确定什么情况下为逻辑1,什么情况 下为逻辑0。这一步骤是设计组合逻辑电路的关键。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

能对两个1位二进制数进行相加而求得和 及进位的逻辑电路称为半加器。

半加器真值表

本位 A i 的和 B i

=1

Si

Ai Bi Si Ci

加数

00 01 10

0 0 向高

1

0

位的 进位

10

&

Ci

半加器电路图

11

01

Ai

∑

Si

Si AiBi AiBi Ai Bi B i

CO

Ci

Ci AiBi

半加器符号

2、全加器 能对两个1位二进制数进行相加并考虑低位来的进 位,求得和及进位的逻辑电路称为全加器。

Si 的卡诺图

S i m 1 m 2 m 4 m 7 A i B i C i 1

AiBi

Ci-1

00 01 11 10

00 0 1 0

10 1 1 1

Ci 的卡诺图

Ci m3m5AiBi

(AB)C AB

全加器的逻辑图和逻辑符号

Sim 1m 2m 4m 7A iB iC i 1A iB iC i 1A iB iC i 1A iB iC i 1

≥1

C3 &

超集 前成 进二 位进 加制 法4 器位

VCC B2 A2 S2 B3 A3 S3 C3

VDDB3C3 S3 S2 S1 S0 C0-1

16 15 14 13 12 11 10 9 74LS83

12345678

16 15 14 13 12 11 10 9 4008

12345678

S1 B1 A1 S0 B0 A0 C0-1

Si

Ci

≥1

≥1

&&&&

&&&

1

1

1

Ai

Bi

C i-1

3.2.2 加法器

实现多位二进制数相加的电路称为加法器。

1、串行进位加法器

构成:把n位全加器串联起来,低位全加器的进位 输出连接到相邻的高位全加器的进位输入。

C3 S3

C2 S2

C1 S1

C0 S0

CO ∑

CI CI

CO ∑

CI CI

CO ∑

CI CI

A i B i C i-1 000 001 010 011 100 101 110 111

Si Ci 00 10 10 01 10 01 01 11

Ai、Bi:加数, Ci-1:低位

来的进位,Si:本位的和 , Ci:向高位的进位。

AiBi

Ci-1

00 01 11 10

00 1 0 1

11 0 1 0

A i(B iC i 1B iC i 1)A i(B iC i 1B iC i 1)A i(B i C i 1)A i(B i C i 1) A i B i C i 1 C i m 3 m 5 A iB i A iB iC i 1 A iB iC i 1 A iB i (A iB i A iB i)C i 1 A iB (A i B i)C i 1 A iB i

Y0 f0 (I0 , I1, , In1)

Y1

f1(I0 , I1,

, In1)

Ym1 fm1(I0 , I1, , In1)

3.1.1 组合逻辑电路的分析方法

逻辑图

A

& Y1

逐从 级输 1 写入 出到

输 出

B

& Y2

YY

&

C

Y3

&

逻辑表 达式

化 简

2

最简与或 表达式

Y1 AB Y2 BC Y3 CA

1

YY1Y2Y3ABBCAC

2

YA BB C CA

最简与或 表达式

3

真值表

4

电路的逻 辑功能

YA BB C CA

3

ABC 000 001 010 011 100 101 110 111

Y

当输入A、B

0

、C中有2个

或3个为1时,

0

输出Y为1,

0

4

否则输出Y为 0。所以这个

1

电路实际上是

0

一种3人表决

Ai

=1

Bi

Ci-1

Ai

Si

=1

Si

Bi Ci-1

FA

Ci

&

(b) 曾用符号

&

&

Ci

Ai Bi

Ci-1

∑

CI CO

Si Ci

(a) 逻辑图

(c) 国标符号

用与门和或门实现

S i A iB iC i 1 A iB iC i 1 A iB iC i 1 A iB iC i 1

C iA iB iA iC i 1B iC i 1

CO ∑

CI CI

CI

A3 B3

CI

A2 B2

CI

A1 B1

CI

A0 B0 C0-1

特点:进位信号是由低位向高位逐级传递的,速度 不高。

2、并行进位加法器(超前进位加法器)

进位生成项 Gi AiBi 进位传递条件 Pi Ai Bi

进位表达式 C i A iB i ( A i B i) C i 1 G i P iC i 1

穷 举1 法

1

设楼上开关为A,楼下开关为B,灯泡为Y。并 设A、B闭合时为1,断开时为0;灯亮时Y为1 ,灯灭时Y为0。根据逻辑要求列出真值表。

真值表

A

B

Y

0

0

0

0

1

1

1

0

1

1

1

0

2

逻辑表达式 或卡诺图

化 简

3

最简与或 表达式

4

逻辑变换

5

逻辑电路图

2

YABAB

已为最简与 或表达式

用与非

门实现 YAB AB

C3

4 位二进制加法器

C 0 -1

A3 A2 A1 A0 B3 B2 B1 B0

C

&

&

&

S3 S2 S1 S0

1

进位 输出

C3 A3

A2

4 位二进制加法器 A1 A0 B3 B2

B1

C 0 -1 B0

进位输入

被加数

加数

本节小结

能对两个1位二进制数进行相加而求得和及进位的 逻辑电路称为半加器。

能对两个1位二进制数进行相加并考虑低位来的进 位,即相当于3个1位二进制数的相加,求得和及进 位的逻辑电路称为全加器。

实现多位二进制数相加的电路称为加法器。按照 进位方式的不同,加法器分为串行进位加法器和超 前进位加法器两种。串行进位加法器电路简单、但 速度较慢,超前进位加法器速度较快、但电路复杂 。

加法器除用来实现两个二进制数相加外,还可用 来设计代码转换电路、二进制减法器和十进制加法 器等。

3.3 数值比较器

举 法

1 成功与否的灯为Y,根据逻辑要求列出真值表。

ABC Y

ABC

Y

000

0

100

0

真值表

001

0

101

1

010

0

110

1

2

011

0

111

1

2

逻辑表达式 Y m 5 m 6 m 7A B C AC B AB

3

卡诺图

化 简

4

最简与或 表达式

5

逻辑变换

6

逻辑电 路图

3

AB

C 00 01 11 10

0

二、多输出组合电路的设计

有时电路的输出不只一个,其设计思路和 单输出的基本相同,只是在设计时要将多个输 出看成一个整体,在化简时不能孤立地以使每 个输出化为最简为目标,应考虑各个输出信号 之间的关系,找出多个输出间的共同项,力求 使整体电路达到最简。

例 用“与非门”实现下列函数:

F1(AB, C , )m(1,3,74),5, F2(AB, C , )m(3,4,7)

P3 C2 G3 P3C2

G3

P3G2

P3P2G1

P3P2P1G0

P3P2P1P0C01

C 0-1

A0

P0

B0

=1

G0 &

A1

P1

ห้องสมุดไป่ตู้

B1

=1

& G1

A2

P2

B2

=1

& G2

A3

P3

B3

=1

G3 &

超前进位发生器

=1

S0

&

≥1 C0

&

C1

≥1

=1

&

S1

&

&

≥1 C2

=1 S2

&

&

=1

S3

&

&

用的组合电路

1

:只要有2票

1

或3票同意,

表决就通过。

1

例:

A B

C

逻辑图

≥1 Y1

≥1 Y3 1

Y

1

≥1

Y2

逻辑表 达式

YY12AABBCYY3Y1Y2BABCABB

Y3XYB

最简与或 表达式

Y A B C A B B A B B A B

真值表

ABC 000 001 010 011 100 101 110 111

BCD码+0011=余3码

被 加 数 /被 减 数

加 数 /减 数 加 减 控 制