嵌入式系统最小系统硬件设计

控制系统-嵌入式系统的组成

控制系统-嵌入式系统的组成嵌入式系统最核心的层次是中央处理单元部分,它包含运算器和控制器模块,在cpu 的基础上进一步配上存储器模块、电源模块、复位模块等就构成了通常所说的最小系统。

由于技术的进步,集成电路生产商通常会把许多外设做进同一个集成电路中,这样在使用上更加方便,这样一个芯片通常称之为微控制器。

在微控制器的基础上进一步扩展电源传感与检测、执行器模块以及配套软件并构成一个具有特定功能的完整单元,就称之为一个嵌入式系统或嵌入式应用。

硬件结构尽管各种具体的嵌入式系统的功能、外观界面、操作等各不相同,甚至千差万别,但是基本的硬件结构却是大同小异的,而且和通用计算机的硬件系统有着高度的相似性。

嵌入式系统的硬件部分看起来与通用计算机系统的没有什么区别,也由处理器、存储器、外部设备、I/O接口、图形控制器等部分组成。

但是嵌入式系统应用上的特点致使嵌入式系统在软硬件的组成和实现形式上与通用计算机系统有较大区别。

为满足嵌入式系统在速度、体积和功耗上的要求,操作系统、应用软件、特殊数据等需要长期保存的数据,通常不使用磁盘这类具有大容量且速度较慢的存储介质,而大多使用EPROM、E2PROM或闪存(FlashMemory)。

在嵌入式系统中,A/D或D/A模块主要用于测控方面,这在通用计算机中用得很少。

根据实际应用和规模的不同,有些嵌入式系统要采用外部总线。

随着嵌入式系统应用领域的迅速扩张,嵌入式系统越来越趋于个性化,根据自身特点采用总线的种类也越来越多。

另外,为了对嵌入式处理器内部电路进行测试,处理器芯片普遍采用了边界扫描测试技术(JTAG)。

软件体系嵌入式系统的软件体系是面向嵌入式系统特定的硬件体系和用户要求而设计的,是嵌入式系统的重要组成部分,是实现嵌入式系统功能的关键。

嵌入式系统软件体系和通用计算机软件体系类似,分成驱动层、操作系统层、中间件层和应用层等四层,各有其特点。

驱动层驱动层是直接与硬件打交道的一层,它为操作系统和应用提供硬件驱动或底层核心支持。

嵌入式系统开发

嵌入式系统开发嵌入式系统是指内嵌在其他设备或系统中,实现特定功能的计算机系统。

它通常集成了硬件和软件,通过专门的开发平台进行开发和编程。

嵌入式系统广泛应用于各个领域,如汽车、家电、医疗设备、通信设备等。

本文将围绕嵌入式系统开发展开,介绍嵌入式系统的基本原理、开发流程以及相关技术。

一、嵌入式系统的基本原理嵌入式系统的基本原理是将处理器、存储器、输入输出设备等硬件组件集成在一起,通过操作系统和应用程序实现特定的功能需求。

常见的嵌入式系统采用单片机或微处理器作为核心处理器,具有较小的体积和功耗。

嵌入式系统的设计需要考虑硬件平台的选择、外设的接口设计、系统调度和任务管理等方面。

同时,软件开发也是嵌入式系统的重要组成部分,包括操作系统的移植、设备驱动程序的编写以及应用程序的开发。

二、嵌入式系统开发流程嵌入式系统的开发流程包括需求分析、硬件设计、软件开发、集成测试和发布等环节。

下面将逐一介绍各个环节的内容。

1. 需求分析在嵌入式系统开发之前,需要明确系统的功能需求和性能要求。

通过与用户沟通和需求分析,确定硬件平台、输入输出设备和外部接口等方面的需求。

2. 硬件设计硬件设计是指基于嵌入式系统的功能需求,选择合适的处理器、存储器、外设等硬件组件,并进行相应的电路设计和PCB布局。

硬件设计需要考虑系统的稳定性、扩展性和功耗等因素。

3. 软件开发软件开发是嵌入式系统开发的关键环节。

首先,根据硬件平台的选择,进行操作系统的移植和配置。

然后,编写设备驱动程序,实现对外设的控制和数据交换。

最后,根据系统需求,开发应用程序,实现特定功能。

4. 集成测试集成测试是将硬件和软件进行整合,测试系统的功能和性能是否满足需求。

通过功能测试、性能测试和稳定性测试,发现并修复系统中的缺陷和问题。

5. 发布在集成测试通过后,将嵌入式系统制作成最终产品,进行出厂测试和质量控制。

然后,将产品发布给客户或上线市场。

三、嵌入式系统开发的相关技术嵌入式系统开发涉及到多个技术领域,下面将介绍几个重要的技术。

《嵌入式电子系统设计》课程实验指导书实验1:最小系统实验,(2014.7.11)

实验一最小系统实验一、实验目的熟悉最小系统的硬件构成,掌握复位电路、晶振电路、电源电路(尤其是滤波电容的应用),编写一个例程,并在最小系统上运行;了解嵌入式开发的基本思想和过程。

掌握最小系统的构成,在将来的项目运用中能根据不同的场合选择相应的复位电路。

二、实验原理本实验通过一个简短的 Boot 引导程序介绍 ARM 开发平台的启动过程,同时该引导程序也可其他章节程序引导的示例程序。

本程序主要为了让读者能够清晰理解启动程序的基本架构组成部分以及掌握ARM 引导程序的编写方法。

三、主要实验设备1.硬件:宿主机、ARM教学试验箱;2.软件:Windows操作系统、ADS1.2集成开发环境。

四、实验内容构建最小系统,用示波器观察一下晶振电路的波形,测一下晶振正常工作时的电压。

编写一个例程,编译并运行。

设置ARM仿真器的开发环境。

程序架构如下:1.程序头IMPORT MDCNFG ;声明 MDCNFG(读写寄存器)物理地址0x48000000IMPORT MDREFR ;声明 MDREFR(刷新寄存器)0x48000004IMPORT MDMRS ;声明 MDMRS(模式/设置寄存器 0x48000040IMPORT init_MDCNFG ; 声明 init_MDCNFG 0x02000ac9IMPORT init_MDREFR ; 声明 init_MDREFR 0x0011e018IMPORT init_MDMRS ; 声明 init_MDMRS 0x320032IMPORT StackSvc ; 声明 StackSvc 0xa0600000IMPORT StackIrq ; 声明 StackIrq 0xa0605000IMPORT StackFiq ; 声明 StackFiq 0xa060a000IMPORT StackAbt ; 声明 StackAbt 0xa060e000IMPORT StackUnd ; 声明 StackUnd 0xa0714000IMPORT StackUsr ; 声明 StackUsr 0xa0720000IMPORT mainIMPORT宏通知编译器本源码文件需要引用在其他文件中定义的变量或函数。

S3C2410及最小系统设计

AHB AHB主要用于高性能模块(如CPU、DMA等)之间的连接。

APB APB主要用于低带宽的周边外设之间的连接,例如UART等

POWER MANAGEMENT NORMAL mode, SLOW mode, IDLE mode, and Power-OFF mode.

18

19

各部件简介

——复位

时钟系统

调试测试接口

供电系统 (电源)

s3c2410

复位及其 配置系统

存储器系统

所有微控制器均有一个复位逻辑,它负责将微控制器初 始化为某个确定的状态。这个复位逻辑需要一个复位信 号才能工作。这个信号的稳定性和可靠性对微控制器的 正常工作有重大影响。

11

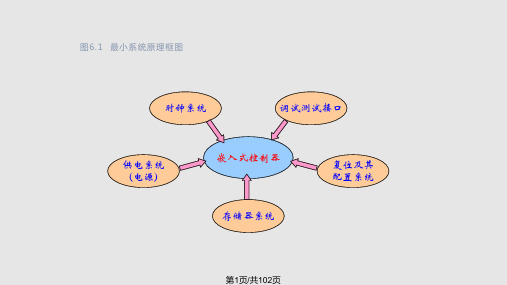

最小系统

简介 ——最小系统框图 时钟系统

调试测试接口

供电系统 (电源)

s3c2410 存储器系统

复位及其 配置系统

12

各部件简介

——电源

时钟系统

调试测试接口

供电系统

(电源)

时钟系统

s3c2410

存储器系统

复位及其

配置系统

调试测试接口

供电系统

s3c2410

复位及其

(电源)

配置系统

电源系统为整个系统提供能量,是整个系统工作的

—除 bank0 (16/32-bit) 外,所有的Bank都可以通过编程选 择总线宽度= (8/16/32-bit)

— 最后两个Bank大小可编程,且保持容量相等

— 7个Bank固定起始地址; 最后一个Bank可调整起始地址 ;

嵌入式最小系统与S3C2410开发板(完全)

• ARM 微处理器目前包括下面几个系列,以及其它厂商基 于 ARM 体系结构的处理器,除了具有 ARM 体系结构的 共同特点以外,每一个系列的 ARM 微处理器都有各自的 特点和应用领域。

– – – – – – – ARM7 系列 ARM9 系列 ARM9E 系列 ARM10E 系列 SecurCore 系列 Inter 的 Xscale Inter 的 StrongARM

– 1.工业控制领域:

• 作为32位的 RISC架构,基于ARM 核的微控制器芯片不但占据了高 端微控制器市场的大部分市场份额,同时也逐渐向低端微控制器应用 领域扩展,ARM 微控制器的低功耗、高性价比,向传统的 8 位/16 位微控制器提出了挑战。

– 2.无线通讯领域:

• 目前已有超过 85%的无线通讯设备采用了 ARM 技术, ARM 以其高 性能和低成本,在该领域的地位日益巩固。

– 4.片内外围电路的选择

• 除 ARM 微处理器核以外,几乎所有的 ARM 芯片均根据各自 不同的应用领域,扩展了相关功能模块,并集成在芯片之中, 我们称之为片内外围电路,如 USB 接口、IIS 接口、LCD 控 制器、键盘接口、RTC、ADC 和 DAC、DSP 协处理器等, 设计者应分析系统的需求,尽可能采用片内外围电路完成所需 的功能,这样既可简化系统的设计,同时提高系统的可靠性。

2.1 ARM 微处理器概述

– 2.系统的工作频率

• 系统的工作频率在很大程度上决定了 ARM 微处理 器的处理能力。ARM7 系列微处理器的典型处理速 度为 0.9MIPS/MHz,ARM9系列微处理器的典型处 理速度为 1.1MIPS/MHz,常见的 ARM9 的系统主 时钟频率为 100MHz-233MHz,ARM10 最高可以 达到 700MHz。不同芯片对时钟的处理不同,有的 芯片只需要一个主时钟频率,有的芯片内部时钟控 制器可以分别为 ARM 核和 USB、UART、DSP、 音频等功能部件提供不同频率的时钟。 • 本书所讨论的 S3C2410 时钟频率为 200MHz 以上, 若更换成 S3C2440 时钟频率最高可达到 500MHz。

嵌入式最小系统设计PPT课件

81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96

VD1/GPD1 97

VD0/GPD0 98

RXD0/GPE2 99

TXD0/GPE1 100

DATA31/nCTS0/GPC15 101

DATA30/nCTS0/GPC14 102

DATA29/RxD1/GPC13 103 DATA28/TxD1/GPC12 104

7个起始地址固定及大小可编程的地址空间。

1个起始地址及大小可变的地址空间。

所有存储器空间的访问周期都可通过编程配置。

提供外部扩展总线的等待周期。

在低功耗模式下支持DRAM/SDARM自动刷新。

支 持 地 址 对 称 或 非 地第址18页对/共称102的页 D R A M 。

3. cache和片内SRAM 4路相连统一的8KB指令/数据cache。 未作为cache使用的0/4/8KB cache存储空间可作为片内SRAM使用。 cache伪LRU(最近最少使用)的替换算法。 通过在主内存和缓冲区内容之间保持一致的方式写内存。 具有4级深度的写缓冲。 当缓冲区出错时,请求数据填充。

• SDRAM存储器作为系统运行时的主要区域,系

第3页/共102页

• JTAG接口可对芯片内部的所有部件进行访问,通 过该接口可对系统进行调试、编程等。

嵌入式系统硬件体系结构设计

嵌入式系统硬件体系结构设计一、嵌入式计算机系统体系结构体系主要组成包括:硬件层中涵盖嵌入式微处理器、存储器(sdram、rom、flash等)、通用设备USB和i/oUSB(a/d、d/a、i/o等)。

在一片嵌入式处理器基础上添加电源电路、时钟电路和存储器电路,就构成了一个嵌入式核心控制模块。

其中操作系统和应用程序都可以固化在rom中。

硬件层与软件层之间为中间层,也称作硬件抽象化层(hardwareabstractlayer,hal)或板级积极支持纸盒(boardsupportpackage,bsp),它将系统上层软件与底层硬件拆分开去,并使系统的底层驱动程序与硬件毫无关系,上层软件开发人员无须关心底层硬件的具体情况,根据bsp层提供更多的USB即可展开研发。

该层通常涵盖有关底层硬件的初始化、数据的输出/输入操作方式和硬件设备的布局功能。

3.系统软件层系统软件层由实时多任务操作系统(real-timeoperationsystem,rtos)、文件系统、图形用户USB(graphicuserinterface,gui)、网络系统及通用型组件模块共同组成。

rtos就是嵌入式应用软件的基础和研发平台。

功能层主要由实现某种或某几项任务而被开发运行于操作系统上的程序组成。

一个嵌入式系统装置通常都由嵌入式计算机系统和继续执行装置共同组成,而嵌入式计算机系统就是整个嵌入式系统的核心,由硬件层、中间层、系统软件层和应用软件层共同组成。

继续执行装置也称作被控对象,它可以拒绝接受嵌入式计算机系统收到的掌控命令,继续执行所规定的操作方式或任务。

本网关硬件环境以单片机s3c2440芯片和dm9000以太网控制芯片为主,实现rj45接口和rs232接口的数据传输。

内容包括硬件环境的初始化,数据的收发控制,封包解包设计,操作系统的移植等。

硬件框图就是直观的将每个功能模块列举,也就是一个基本的模块女团,可以简约的每个模块的功能彰显出。

soc最小系统原理

soc最小系统原理

SOC最小系统是一种集成电路系统,它包含了实现特定功能的所有硬件和软件组件,并在单一芯片上集成。

它的工作原理可以从硬件和软件两个方面来解释。

在硬件方面,SOC最小系统通过将各种硬件组件集成在单一芯片上,实现了高度的集成化。

这些硬件组件可能包括微处理器、存储器、输入输出接口、信号处理电路等。

这些组件之间的连接是通过芯片内部的电路实现的,使得它们之间的通信和数据传输速度极快,从而提高了系统的整体性能。

在软件方面,SOC最小系统通常采用嵌入式软件来控制和管理硬件组件的工作。

这些软件通常被预先加载到存储器中,并在系统启动时或根据需要自动加载和运行。

通过嵌入式软件的编程和控制,SOC最小系统可以实现各种复杂的功能,例如数据处理、信号处理、人机交互等。

总的来说,SOC最小系统的原理是通过高度集成化的硬件和嵌入式软件的有机结合,实现了系统的智能化和自动化。

这种技术具有很多优点,例如低功耗、高性能、小型化、可靠性高等,因此在许多领域都有广泛的应用前景。

嵌入式系统设计与开发

嵌入式系统设计与开发1. 引言嵌入式系统是最近几十年来较为重要的技术之一,具有广泛的应用领域。

嵌入式系统一般是指在计算机系统或其他电子设备中嵌入了专门的软件与硬件,以完成特定的任务。

它广泛应用于家用电器、汽车、医疗设备、通信设备、工业控制、航空航天等领域。

本文将从嵌入式系统的设计与开发角度来讨论该技术的基本实现原理、软件开发流程、硬件设计原则以及一些应用场景。

2. 基本实现原理嵌入式系统的设计思路与传统计算机系统不同,它通常需要一个微小的芯片来扮演整个系统的角色。

因此,嵌入式系统的设计架构非常紧凑,尽量减少硬件和软件的耗用,以实现更快的运行速度与更低的功耗。

嵌入式系统的设计与开发分为两个主要方面:软件开发和硬件设计。

3. 软件开发流程嵌入式系统的软件开发一般有以下五个步骤:1. 系统需求分析在开发嵌入式系统之前,需要对系统进行需求分析。

这可以帮助设计团队确定需要实现哪些功能,并定义硬件和软件的最小要求。

2. 软件设计在嵌入式系统的软件设计过程中,需要使用编程语言来实现所需的功能。

常用的编程语言有C、C++、Assembly等。

由于嵌入式系统通常只有很小的空间来存储程序,因此在设计时需要注意代码的体积和效率。

3. 软件开发在软件开发过程中,需要实现软件设计的方法和要求。

在这里,开发人员需要验证软件的正确性,并进行相关的测试,以确保程序的正确执行。

4. 系统集成在硬件和软件开发完成后,需要将系统硬件和软件进行集成。

在集成过程中,需要对系统进行调试和测试,以确保所有组件能够正常工作,并实现预期的任务。

5. 运行维护系统开发完成后,需要对其进行维护和管理。

在运行过程中需要进行相关检查和保养,以确保系统能够正常运行。

4. 硬件设计原则嵌入式系统的硬件设计需求取决于具体应用场景。

通常,硬件设计需要满足以下几个方面的要求:1. 可靠性和安全性嵌入式系统在很多关键应用中发挥着重要作用,因此,系统的可靠性和安全性至关重要。

嵌入式系统的软硬件设计

图2系统硬件框图

2.2

首先分析系统的功能需求,我们设计题目是基于嵌入式web服务器的远程控制系统,那么此系统需要完成以下几个功能:

1)WEB服务器的搭建

经过查阅资料我们选择BOA服务器作为本系统的WEB服务器,BOA服务器是一个小巧高效的web服务器,是一个运行于unix或linux下的,支持CGI的、适合于嵌入式系统的单任务的http服务器,源代码开放、性能高。具体的搭建流程参考网络资料。

exit(1);

}

ioctl(fd, PWM_IOCTL_SET_TCNTB, 3000);

ioctl(fd, PWM_IOCTL_SET_TCMPT, 0);

ioctl(fd, PWM_IOCTL_START);

通过读取设备文件然后通过ioctl来控制PWM的输出及启动。

4

DS18B20是常用的温度传感器,具有体积小,硬件开销低,抗干扰能力强,精度高的特点。硬件连接图如下图所示(本系统DS18B20接在GPB1上)。其操作主要通过1-wire协议完成,根据数据手册提供的操作时序及命令定义即可实现温度的获取。由于DS18B20的驱动也是采用字符设备驱动所以在设计时很多东西都是和PWM设备驱动是相同的,下面主要介绍两者不同的地方。虽然在linux驱动说明提供有关的1-wire但一直没有找到相关使用资料,所以整个DS18B20的驱动只能采用IO的控制来实现读取数据。

pwm_ioctl

static long pwm_ioctl(struct file *file, unsigned intcmd, unsigned long arg)

{

switch(cmd)

{

case PWM_IOCTL_START:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

引言嵌入式系统是以应用为中心,软件硬件可裁剪,适应应用系统对功能、可靠性、成本、体积、功耗等综合性严格要求的专用计算机系统。

本文主要研究了基于SEP3202(内嵌ARM7TDMI 处理器内核)的嵌入式最小系统,围绕其设计出相应的存储器、总线扩展槽、电源电路、复位电路、JTAG、UART等一系列电路模块。

嵌入式最小系统根据IEEE的定义,嵌入式系统是:控制、监视或者辅助装置、机器和设备运行的装置。

这主要是从应用上加以定义的,从中可以看出嵌入式系统是软件和硬件的综合体,还可以涵盖机械等附属装置。

不过上述定义并不能充分体现出嵌入式系统的精髓,目前国内一个普遍被认同的定义是:以应用为中心、以计算机技术为基础、软件硬件可裁剪、适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

嵌入式最小系统即是在尽可能减少上层应用的情况下,能够使系统运行的最小化模块配置。

以ARM内核嵌入式微处理器为中心,具有完全相配接的Flash电路、SDRAM电路、JTAG电路、电源电路、晶振电路、复位信号电路和系统总线扩展等,保证嵌入式微处理器正常运行的系统,可称为嵌入式最小系统。

对于一个典型的嵌入式最小系统,以ARM处理器为例,其构成模块及其各部分功能如图1所示,其中ARM微处理器、FLASH和SDRAM模块是嵌入式最小系统的核心部分。

•微处理器——采用了SEP3203;•电源模块——为SEP3203内核电路提供2.5V的工作电压,为部分外围芯片提供3.3V的工作电压;•时钟模块(晶振)——通常经ARM内部锁相环进行相应的倍频,以提供系统各模块运行所需的时钟频率输入。

32.768kHz给RTC和Reset模块,产生计数时钟,10MHz作为主时钟源;•Flash存储模块——存放嵌入式操作系统、用户应用程序或者其他在系统掉电后需要保存的用户数据等;•SDRAM模块——为系统运行提供动态存储空间,是系统代码运行的主要区域;•JTAG模块——对芯片内部所有部件进行访问,通过该接口对系统进行调试、编程等,实现对程序代码的下载和调试;•UART模块——用于系统与其他应用系统的短距离双向串行通信;•复位模块——实现对系统的复位;•系统总线扩展——引出地址总线、数据总线和必须的控制总线,便于用户根据自身的特定需求,扩展外围电路。

SEP3202简述SEP3203处理器内嵌由英国ARM 公司提供的ARM7TDMI 处理器内核,整个芯片可以运行在75MHz。

集成了支持黑白,灰度,彩色的LCD 控制器;多媒体加速模块,用于提供多媒体处理定点矢量乘加的计算能力;支持低成本的NAND Flash 控制器并可从其直接启动;支持多种外存类型:SRAM,NOR Flash,SDRAM;支持实时钟(RTC);支持四通道的定时器和两通道的PWM;支持用于连接触摸屏通讯的SPI 协议;支持两个UART 控制器,其中一个支持红外传输;支持USB1.1 Device 控制器用于PC 与移动终端之间的高速信息传输;支持MMC/SD 卡控制器,用户可以扩展系统的存储能力和外设功能;支持兼容AC97 协议的控制器,用于音频文件的播放和录制。

SEP3203 处理器内嵌20KByte 零等待的静态存储器(SRAM),用于多媒体处理时的核心代码与数据的存放,用户也可以将操作系统的核心代码或LCD 帧缓存存放在该处理器中,用于提供更高的性能和更低的能量消耗;6 通道DMA 控制器,为用户提供了高速的数据传输通道。

为了支持低成本的系统方案,SEP3203 支持外部32 位/16 位数据总线,结合ARM 提供的Thumb 指令集,将大大降低系统成本和功耗,考虑到Nand Flash 的成本优势,SEP3203 处理器提供专用的Nand Flash 控制器,并支持系统直接从Nand Flash 启动。

SEP3203 处理器采用LQFP176 封装形式(针对用户需求,我们还可以提供BGA 封装的版本)。

最小系统硬件的选择和单元电路的设计•电源电路电源电路的好坏,直接影响应用系统的稳定性、可靠性、功耗、成本及电池寿命和可靠性。

电源系统的总体架构如图所示:当电池电量充足时,由电池供给整个系统用电,当电池电量不足时,由5V输入电源一方面对电池充电,另一方面供给真个系统。

主要包括以下几个部分:• 3.3V~5V的DC-DC转换器,给SEP3203及其他需要3.3V电源的外围电路供电。

• 2.5V~5V的DC-DC转换器,给SEP3203芯片内核电路供电。

上电顺序为3.3V-2.5V。

其中5V-2.5V转换电路前面连接RC延迟网络,可获得比3.3V较晚些的上电时间,时间设为约10ms。

电源电路中使用了大量的去耦电容,用于滤除交流成分,使输出的直流电源更平滑。

同时,每个芯片的电源引脚和地之间都连接了这样的去耦电容,以防止电源噪声影响元件正常工作。

•晶振电路晶振电路为微处理器及其他电路提供工作时钟,是系统必须的重要电路。

本系统用两个晶振电路分别为微处理器及其他电路提供工作时钟,32.768kHz给RTC(实时时钟电路)和Reset模块,产生计数时钟,10MHz作为主时钟源。

电路图如下。

其中CD4096是非门。

•复位及唤醒电路在应用系统中,复位电路主要完成系统的上电复位和系统在运行时用户的按键复位功能。

SEP3202中的Reset方案主要是产生整个系统工作需要的Reset信号,处理wakeup信号,对外接的不规则reset、wakeup信号进行规则化,避免误触发。

外围硬件复位电路如图所示:该复位电路的工作原理如下:在系统上电时,通过电阻R5向电容C5充电,当C5两端的电压未达到高电平的门限电压时,RESET端输出为低电平,系统处于复位状态;当C5两端的电压达到高电平的门限电压时,RESET端输出为高电平,系统进入正常工作。

当用户按下按钮K1时,C5两端的电荷被释放掉,RESET端输出为低电平,系统进入复位状态,再重复以上充电过程,系统进入正常工作状态。

其中具体参数为:复位响应点电压(+2.9 ~3.00V),复位时间(140 ~560ms),有效复位条件(1V),并且支持手动复位功能。

除此之外,我们还增加了一个watchdog电路,用于监视系统状态,防止系统锁死。

使能watchdog功能以后,需要软件周期性复位,以避免该模块产生中断或者复位。

设计该模块我们用到了芯片DS1232LPS。

DS1232LP/DS1232LPS是一款低功耗的Micro Monitor芯片,用于监视微处理器控制系统的三个关键条件:电源、软件运行和外部故障。

首先,DS1232LP/DS1232LPS精确的温度补偿电路用于监视Vcc 状态。

一旦检测到主电源失效,DS1232LP/DS1232LPS将产生一个掉电中断信号,强制将处理器重置为有效状态。

当Vcc 回到电压容差范围,重置信号至少保持250ms 的有效状态,以便恢复供电和保持处理器稳定。

当软件没有对watchdog进行服务时,会产生timeout事件,通过配置中断使能寄存器中的中断位和reset请求位可以产生中断和reset请求,如果需要屏蔽也可以通过配置这两位来获得(默认情况为屏蔽)。

其电路图如下:因为SEP3203芯片有四种工作模式,即slow、normal、idle、sleep。

为了帮助系统从idle模式或sleep模式中恢复过来,建立完善的、有效的唤醒机制是必须的,这将从硬件上保证系统不会瘫痪。

•存储器存储器是计算机硬件系统中用于存放程序和数据等二进制信息的部件,是计算机的记忆部件。

CPU根据地址访问存储单元,读出或写入数据。

从一个存储单元读出或写入数据的时间称为读写时间,两次读/写操作之间的间隔称为存取周期,这两项是衡量存储器存取速度的指标。

本次试验,我们所选取的FLASH以及SDRAM的芯片如下所示:型号描述W986416EH SDRAM 64MbitTE28F160NorFlash 16M bit•FLASH存储FLASH即为闪存,有许多种种类,从结构上分主要有and、nand、nor、dinor等,其中nand 和nor是目前主流的类型,在嵌入式系统中,一般用FLASH来存放需要永久保存的程序和数据,掉电后不会丢失。

而用SDRAM来存放系统运行时的数据,掉电后则消失。

综合各方面的性能,nand flash更优,它拥有较快的擦除和写入速度(大多数的写入操作需要先进行擦除操作);在更低的成本上获得更大的容量;它的每个块最大擦写次数是100万次,远高于nor的10万次,拥有更长的使用寿命;并且nand的擦除单元(nor的擦出块单元为64~128KB,nand的擦除块单元为8~32KB)更小,相应的擦除电路更简单。

但是在nand flash中,位反转的问题更加严重,在使用nand闪存时必须同时使用EDC/ECC算法来确保其可靠性,并且nand器件中的坏块是随机分布的,如果通过可靠的方法不能进行坏块扫描,则将导致较高的故障率。

与此同时,nor闪存的连接方式类似于其他存储器,并可以直接运行代码,而不像nand器件上始终必须进行虚拟映射。

并且在nor器件上运行代码不需要任何的软件支持,在进行写入和擦除操作时,nor器件所需要的MTD(闪存技术驱动程序)相对较少,驱动程序还可用于对DiskOnChip 产品进行仿零点和闪存管理,包括纠错、坏块处理和损耗平衡。

虽然nand的性能较好,但是Nor Flash 带有SRAM接口,有足够的地址引脚,可以很容易的对存储器内部的存储单元进行直接寻址。

在实际的系统中,可以根据需要选择ARM处理器与Nor Flash的连接方式。

nor的操作最更加方便,电路也更为简易易懂,因此本次试验我们选择了nor型的闪存。

其电路图如下所示:•SDRAMSDRAM是对bank结构,例如在一个具有两个bank的SDRAM的模组中,其中一个bank在进行预充电期间,另一个bank则马上可以被读取,这样可以大大提高存储器的访问速度。

在SDRAM 芯片中一般会有实现bank选择的引脚,用于实现多个bank的选择。

目前常用的SDRAM为8bit/16bit数据宽度、工作电压一般为3.3V,主要生产厂商为Micron、HynixI、Winbond等,若同类器件具有相同的电气特性和封装形式可通用。

但在使用SDRAM时要注意ARM芯片是否具有独立的SDRAM的刷新控制逻辑,若有可直接与SDRAM接口,若无则不能直接与SDRAM连接。

实验中选用Winbond公司的64Mbit的SDRAM—W986416EH。

其读写速度都高于SEP3203芯片的典型工作时钟75MHz,从而消除了存储器访问瓶颈。

SDRAM通过对电容的充放电完成存储操作,但因电容本身有漏电问题,所以内存中的数据要持续不断地存取,存储在SDRAM中的数据必须不断地刷新以保持数据的完整性,否则数据将会丢失。