ROM实验

Logisim平台微程序控制实验-计算机组成原理

CPU的结构与功能

结构:CPU由控制器、运算器和寄存器组成

功能:控制器负责控制计算机的运行,运算器负责执行算术和逻辑运算,寄存器负责存储数据 和指令

指令集:CPU能够执行各种指令,包括算术指令、逻辑指令、控制指令等

工作原理:CPU通过读取指令、解码指令、执行指令的循环过程,实现对计算机的控制和运算。

控制器:控制计算机的运行,包括指令的 执行和程序的控制

运算器:进行算术和逻辑运算,包括加、 减、乘、除等基本运算

存储器:存储数据和程序,包括内存和外 存

输入设备:将数据或程序输入计算机,包 括键盘、鼠标等

输出设备:将计算机的处理结果输出,包 括显示器、打印机等

总线:连接计算机的各个部件,包括数据 总线、地址总线和控制总线

实验结果分析与讨论

实验目的:验证计算机组成原理的基 本概念和原理

实验方法:使用Logisim平台进行微 程序控制实验

实验结果:成功实现计算机组成原理 的基本功能

分析与讨论:实验结果与预期相符, 验证了计算机组成原理的基本概念和 原理,为后续课程学习打下基础。

06 实验总结与展望

实验总结回顾

实验目的:掌握微程序控制的基本原理和实现方法

实验内容:设计并实现一个简单的微程序控制器

实验方法:使用Logisim平台进行模拟和验证 实验结果:成功实现了微程序控制器的功能,并对计算机组成原理有了更 深入的理解

实验收获与感悟

掌握了Logisim平台的基本操作和微程序控制的原理 提高了计算机组成原理的理解和应用能力 学会了如何分析和解决实际问题 培养了团队合作和沟通能力 提高了对计算机科学的兴趣和热情

微程序控制的优势与局限性

优势:微程序控制可以实现复杂的控制功能,提高系统的灵活性和可扩展性。 优势:微程序控制可以简化硬件设计,降低硬件成本。 局限性:微程序控制需要大量的存储空间,可能导致系统资源紧张。 局限性:微程序控制可能会导致系统响应速度降低,影响系统性能。

微程序的设计与仿真实验报告

微程序的设计与仿真实验报告一、实验目的1.了解微程序原理及其设计方法。

2.掌握微程序的设计方法。

3.通过仿真实验加深对微程序的理解。

二、实验原理微程序是指一组存放在 ROM 中的程序,用于控制 CPU 的操作,并达到执行指令的目的。

微程序控制器的设计是建立在单周期 CPU 的基础上,实现了对指令执行的分段处理,每个微指令对应一个硬件操作控制信号,通过更改微程序可实现CPU 的不同功能。

三、实验设备1.计算机2.微程序分析器3.ROM4.模拟器四、实验步骤1.根据指令集设计微程序。

2.将微程序写入 ROM。

3.在微程序分析器中进行仿真,验证微程序的正确性及指令执行的正确性。

4.通过模拟器执行各类指令。

五、实验数据和结果实验中,我们以实现 add 指令为例,设计微程序,并将其写入ROM 中。

微程序如下:其中,微地址 m 的范围是 0~31;程序计数器 PC 的值在ADDR 寄存器中;指令寄存器 IR 保存当前指令;A、B、S、T、D、S1、S2 寄存器用于保存数据,根据指令需要选择是否使用;ALU 作为运算单元,根据指令选择运算方式;各控制信号用于控制微程序中的各信号。

我们将编写一个简单的测试程序,包括初始化寄存器和执行add 指令。

测试程序如下:```beginLDI R1, 1LDI R2, 2ADD R1, R2, R3end```通过微程序分析器的仿真功能,我们可以看到执行指令过程如下:可以发现,当执行 add 指令时,微程序依次执行了以下操作:1.将指令地址写入 PC,将指令加载入 IR。

2.将操作码从IR 中提取出来,并对R1、R2、R3 进行初始化。

3.将 R1 和 R2 的值送入 ALU 中,并选择加法运算。

4.将 ALU 的运算结果送入 R3 中。

LPM_ROM 和LPMM 设计

南昌航空大学实验报告2014年 5月 17日课程名称:计算机组成与原理实验名称:LPM_ROM和LPM_RAM设计班级: 120452 学生姓名:刘信学号: 12045217指导教师评定:签名:实验目的:掌握FPGA 中LPM_ROM的设置:l 作为只读存储器ROM的工作特性和配置方法;2学习将程序代码或数据以MIF格式文件加载于LPM_ROM中;掌握lpm_ram_dq 的参数设置和使用方法:l 掌握lpm_ram_dq 作为随机存储器RAM的设置;2 掌握lpm_ram_dq 的工作特性和读写方法;3--掌握lpm_ram_dq 的仿真测试方法、。

实验任务:1.LPM_ROM定制和测试LPM_ROM的参数设置;LPM_ROM中数据的写入,即初始化文件的编写;LPM_ROM的实际应用,在GW48实验台上用NO.0 电路模式测试。

2.LPM_RAM定制和测试LPM_RAM的参数设置;LPM_ROM的实际应用,在GW48实验台上用NO.0 电路模式测试。

实验指导:1 .实验原理及方案用户可编程硬件FPGA芯片设计,有许多可调用参数化库模块LPM (Library Parameterized Modules),可直接调用设置,利用嵌入式阵列块EAB(Embed Array Block )构成lpm_ROM,lpm_RAM 等各种存储器结构。

lpm_ROM有5 组信号:地址信号address[];数据信号q[];时钟信号inclock、outclock;允许信号memenable.其参数是可以设定的。

由于ROM是只读存贮器,它的数据口是单向的输出端口,数据是在对FPGA现场配置时,通过配置文件一起写入存储单元的。

lpm_ram_dq 的输入/输出信号如下:地址信号A[]; RAM_dq0 的存储单元地址;数据输入信号DATA[] RAM_dq0 的数据输入端;数据输出信号Q[]; RAM_dq0的数据输出端。

ram6116存储器芯片读写实验答案

ram6116存储器芯片读写实验答案一、实验目的:1.了解半导体静态随机读写存储器SRAM的工作原理及其使用方法2.掌握半导体存储器的字、位扩展技术3.用proteus设计、仿真基于AT89C51单片机的RAM扩展实验二、实验内容:1.用SRAM6116芯片扩展AT89C51单片机RAM存储器(2KB)选择8个连续的存储单元的地址,分别存入不同内容,做单个存储器单元的读/写操作实验。

2.用SRAM6116芯片扩展AT89C51单片机RAM存储器(8KB)必须使用译码器进行扩展;选择8个连续的存储单元的地址,分别存入不同内容,做单个存储器单元的读/写操作实验。

三、实验要求:1.根据各种控制信号的极性和时序要求,设计出实验线路图。

2.分别设计实验步骤。

3.给出字扩展实验中每片SRAM芯片的地址范围。

四、实验步骤(proteus中运行详细过程):(一)查看元件库AT89C51、74LS373、6116(二)各元器件作用:AT89C51:低电压,高性能CMOS8位单片机,片内含4k bytes的可反复擦写的只读程序存储器(PEROM)和128 bytes的随机存取数据存储器(RAM)74LS373:为三态输出八D锁存器两种线路中的一种。

6116:6116是2K*8位静态随机存储器芯片,采用CMOS工艺制造,单一+5V供电,额定功耗160mW,典型存取时间200ns,24线双列直插式封装。

(三)连接电路图(1)按老师发的电路仿真图进行连接,电路图如下:(2)选中AT89C51芯片,在Program File中添加ram.hex文件,然后点击确定。

(3)单击下面的运行按钮,再点击暂停按钮,如下:(4)查看AT89C51的内存:(5)查看存储器6116的存储内容:(6)AT89C51中的程序,程序里的数字可以修改,就是存储器中输入的数字:五、实验小结:(不少于200字)。

用状态机实现序列检测器实验报告

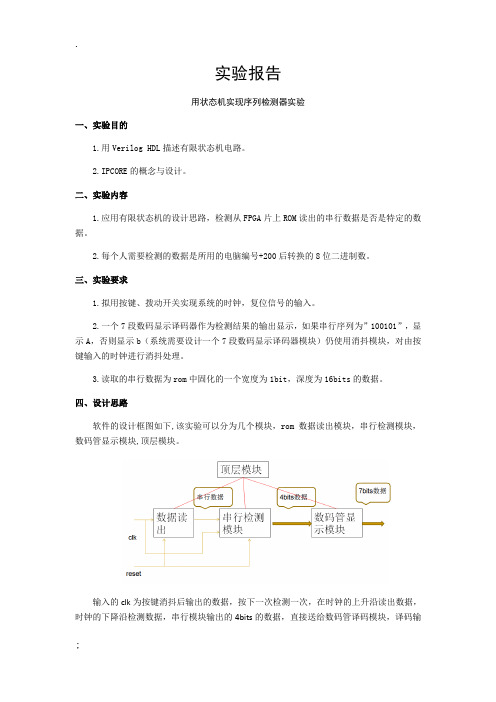

实验报告用状态机实现序列检测器实验一、实验目的1.用Verilog HDL描述有限状态机电路。

2.IPCORE的概念与设计。

二、实验内容1.应用有限状态机的设计思路,检测从FPGA片上ROM读出的串行数据是否是特定的数据。

2.每个人需要检测的数据是所用的电脑编号+200后转换的8位二进制数。

三、实验要求1.拟用按键、拨动开关实现系统的时钟,复位信号的输入。

2.一个7段数码显示译码器作为检测结果的输出显示,如果串行序列为”100101”,显示A,否则显示b(系统需要设计一个7段数码显示译码器模块)仍使用消抖模块,对由按键输入的时钟进行消抖处理。

3.读取的串行数据为rom中固化的一个宽度为1bit,深度为16bits的数据。

四、设计思路软件的设计框图如下,该实验可以分为几个模块,rom数据读出模块,串行检测模块,数码管显示模块,顶层模块。

输入的clk为按键消抖后输出的数据,按下一次检测一次,在时钟的上升沿读出数据,时钟的下降沿检测数据,串行模块输出的4bits的数据,直接送给数码管译码模块,译码输出。

五、设计原理1.ROM IP核的生成首先在ISE自己的工程中新建一个块内存,Block Memory Generator,配置深度为16,宽度为1bit,选择生成的类型为单端ROM,然后选择一个已经编写好的memory初始化文件。

Memory初始化文件,编写coe文件:这里我要写入的是226,所以二进制是11100010,写入的内容如下,:memory_initialization_radix=10;memory_initialization_vector=1 1 1 0 0 0 1 1 1 0 1 0 1 0 1 0;保存并选择载入。

2.读取rom中的数据根据时钟上升沿读取数据,所以可以写出rom读的代码,代码如下:module read_rom(clk,da,rst);input clk;input rst;output da;reg[3:0] counter;always@(posedge clk or posedge rst) beginif(rst)counter<=1'b0;else counter<=counter+1'b1;enddata_rom u1(.clka(clk), // input clka.addra(counter), // input [3 : 0] addra.douta(da) // output [0 : 0] douta);编写仿真激励文件,得到如下波形,分析可以知道,时钟上升沿数据被读取,读取的数据与我们在配置文件中写入的相同。

单片机ROM、RAM之间数据传送

单片机ROM、RAM之间数据传送数据传送实验一、实验目的1、掌握单片机的汇编指令系统及汇编语言程序设计方法。

2、掌握单片机的存储器体系结构。

3、熟悉Keil软件的功能和使用方法。

4、掌握单片机应用程序的调试方法。

二、实验内容或原理1、实现单片机内部RAM之间,外部RAM之间以及内部RAM 与外部RAM之间的数据传送。

2、利用Keil软件编辑、汇编、调试、运行实验程序并记录实验数据。

三、设计要求1、编写程序将00H~0FH 16个数据分别送到单片机内部RAM 30H~3FH单元中。

2、编写程序将片内RAM 30H~3FH的内容传送至片内RAM 40~4FH单元中。

3、编写程序将片内RAM 40H~4FH单元中的内容传送到外部RAM 4800H~480FH单元中。

4、编写程序将4800H~480FH单元内容送到外部RAM 5800H~580FH单元中。

5、编写程序将片外RAM 5800H~580FH单元内容传送回片内RAM 50H~5FH单元中。

四、实验报告要求1、实验目的和要求。

2、设计要求。

3、实验程序流程框图和程序清单。

4、实验总结。

5、思考题。

五、思考题1、说明MCS-51系列单片机对片内RAM和片外RAM存贮器各有哪些寻址方式?2、说明指令MOV A,20H和MOV C,20H中的20H含义有什么不同?传送指令中的助记符MOV,MOVX,MOVC各适用于访问哪个存储器空间?程序如下:ORG 0000HSTART: LJMP MAINORG 0030HMAIN: MOV PSW, #00HMOV R0, #20HMOV R3, #96ML: MOV @R0, #00HDJNZ R3, MLTAB: MOV DPTR, #SHUJUMOV R0, #30HMOV R4, #16TAB1: CLR AMOVC A, @A+DPTRMOV @R0, AINC R0INC DPTRDJNZ R4, TAB1LCALL FUNSHUJU: DB 00H,01H,02H,03H,04H,05H,06H,07H,08H,09H,0AH,0BH,0CH,0D H,0EH,0FHFUN: MOV R4, #16MOV R0, #30HMOV R1, #40HTAC: CLR AMOV A, @R0MOV @R1, AINC R1INC R0DJNZ R4, TACMOV R4, #16MOV R1, #40HMOV DPTR, #4800HTBD: CLR AMOV A, @R1MOVX @DPTR, AINC R1INC DPTRDJNZ R4, TBDMOV R4, #16MOV P2, #48H;((P2)(Ri))表示以(P2)为高8位地址;以(Ri)为低8位地址的片外数据存储器单元;P2为80C51单片机的P2口,其第二功能为传送地址的高8位。

计算机组成原理实验_存储器部件教学实验

实验题目存储器部件教学实验一、实验目的:1. 熟悉ROM芯片和RAM芯片在功能和使用方法等方面的相同和差异之处。

学习用编程器设备向EEPROM芯片内写入一批数据的过程和方法。

2. 理解并熟悉通过字、位扩展技术实现扩展存储器系统容量的方案。

3. 了解静态存储器系统使用的各种控制信号之间正常的时序关系。

4. 了解如何通过读、写存储顺的指令实现对58C65 ROM芯片的读、写操作。

加深理解存储器部件在计算机整机系统中的作用。

二、实验设备与器材:TEC-XP+教学实验系统和仿真终端软件PCEC。

三、实验说明和原理:1、内存储器原理内存储器是计算机中存放正在运行中的程序和相关数据的部件。

在教学计算机存储器部件设计中,出于简化和容易实现的目的,选用静态存储器芯片实现内存储器的存储体,包括唯读存储区和随读写存储区两部分,ROM存储区选用4片长度8位、容易8KB的58C65芯片实现,RAM存储区选用2片长度8位、容量2KB的6116芯片实现,每2个8位的芯片合成一组用于组成16位长度的内存字,6个芯片被分成3组,其地址空间分配关系是:0-1777h用于第一组ROM,固化监控程序,2000-2777h用于RAM,保存用户程序和用户数据,其高端的一些单元作监控程序的数据区,第二组ROM的地址范围可以由用户选择,主要用于完成扩展内存容量的教学实验。

地址总线的低13位送到ROM芯片的地址线引脚,用于选择芯片内的一个存储字。

用于实现存储字的高位字节的3个芯片的数据线引脚、实现低位字节的3个芯片的数据线引脚分别连接在一起接到数据总线的高、低位字节,是实现存储器数据读写的信息通路。

数据总线要通过一个双向三态门电路与CPU一侧的内部总线IB 相连接,已完成存储器、接口电路和CPU之间的数据通讯。

2、扩展教学机的存储空间四、实验内容:1) 要完成存储器容量扩展的教学实验,需为扩展存储器选择一个地址,并注意读写和OE等控制信号的正确状态。

9 利用BootRom下载VxWorks操作系统

实验9 利用BootRom下载VxWorks操作系统一实验原理实验3描述了如何通过uBOOT将VxWorks内核映象下载到目标板,本实验则是介绍如何利用BootRom将VxWorks内核映象下载到目标板。

二实验目标1. 将实验2创建的Bootable的工程中生成的VxWorks映象文件的二进制代码下载到目标机中运行。

三实验步骤1. 参照实验1生成BootRom并将BootRom烧写到Flash中;并重新启动实验箱。

注意,启动信息只能在串口超级终端中可以看到,在实验箱的LCD上没有任何显示。

下图为在超级终端中的显示。

2. 参照实验2编译得到VxWorks映象文件VxWorks,注意,此处可以部将VxWorks映象文件VxWorks转换成为二进制代码VxWorks.bin。

3.通过FTP将生成的目标程序映象下载到目标机中运行:运行Tornado自带的FTP服务器程序(开始->程序->Tornado 2.2->FTP Server),如下图:1) 通过菜单“security”->“users/rights”打开“User/Rights Security Dialog”对话框。

点击New User按钮添加一个用户,用户名为vxworks,登陆口令也为vxworks,在Home Directory编辑框中输入实验2产生的VxWorks映象文件的代码所在目录:“E:\ARM9资料\南京大学\实验代码\2\default”。

最后点击Done按钮确认并保存设置。

设置如下图所示。

2) 设置主机IP地址为192.168.1.180,并正确连接网线,将实验箱和主机的网线连接通。

重新启动教学系统,此时系统会自动加载并运行VxWorks,下面是加载过程:3) 加载完成后将自动运行加载的VxWorks操作系统,如下图所示:4.实验完毕,参照实验1将UBOOT重新烧写到Flash中。

四思考题BootRom是通过什么方式将VxWorks内核映象下载到目标机的?这与实验3采用的 1.方式有什么差别?五实验报告书编写要点1. 烧写BootRom到Flash中;2. 设置FTP服务器;3. 利用BootRom下载VxWorks内核映象。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第三讲 LPM_ROM配置与读出实验

一、实验目的:

1、掌握FPGA中LPM_ROM的工作特性及配置方法;初始数据MIF文件的编辑与加

载方法;

2、熟悉LPM_ROM只读存储器的组成结构、工作原理和工作流程

二、实验内容

在QuartusⅡ上对“加法计数器实验”代码进行编辑、编译、综合、适配、仿真,之后

选择模式5进行引脚锁定,再次进行编译、下载到实验箱的FPGA芯片中进行硬件测试。

三、实验要求

四、实验原理

ALTERA的FPGA中有许多可调用的LPM (Library Parameterized Modules)参数化的模

块库,可构成如lpm_rom、lpm_ram_io、lpm_fifo、lpm_ram_dq的存储器结构。CPU中的重

要部件,如RAM、ROM可直接调用他们构成,因此在FPGA中利用嵌入式阵列块EAB可

以构成各种结构的存储器,lpm_ROM是其中的一种。lpm_ROM有5组信号:地址信号

address[ ]、数据信号q[ ]、时钟信号inclock、outclock、允许信号memenable,其参数都是

可以设定的。由于ROM是只读存储器,所以它的数据口是单向的输出端口,ROM中的数

据是在对FPGA现场配置时,通过配置文件一起写入存储单元的。图3-1中的lpm_ROM有

3组信号:inclk—输入时钟脉冲;a[5..0]—lpm_ROM的6位读出地址,q[7..0]——lpm_ROM

的8位数据输出端;

图3-1 Lpm_Rom RTL电路图

五、实验步骤

1、按P118/4.2.4——P122的步骤做,务必按照图4-11调入ROM初始数据文件并选择

在系统读写功能,主要文件是“romd.mif”、“data_rom.vdh”;

2、基于Data_rom.vhd建立工程文件,按P152的实验步骤锁引脚,也可以是模式5, 模

式5更加的直观。(实验电路模式NO.0,8位地址数据输出由数码管2~1显示,6

位地址由键2、键1输入,键1负责低4位,键2负责高2位,发光管D8~D1显示

输入的6位地址,地址锁存时钟CLK由键8控制,每一次上升沿,将地址锁入);

3、检查5号地址单元的内容“EF”,19号地址单元内容“57”

4、在以上实验成功的基础上,且下载到FPGA中去了,继续做P140/4.4在系统存储器

数据读写编辑器应用;

5、时间允许的话,可以做P126/LPM_RAM的调用和结构(同P152/4-5 LPM_RAM实

验)。

图3-2 设置在系统ROM/RAM读写允许

图3-3 ROM初始化文件Romd.mif的内容

六、实验现象

键2、键1在D8~D1上敲入地址,再置键8高电平,在数码管1和数码管2上显示ROM

内存单元的值。

七、实验思考

1、怎样设计地址宽度和数据线的宽度?怎样导入LPM-ROM的设计参数文件和存储

LPM-ROM的设计参数文件?

2、如何设计8位地址宽度,24位数据宽度的Rom?