基于宽带锁相频率合成的环路滤波器设计

电荷泵锁相环四阶无源环路滤波器的设计

电荷泵锁相环四阶无源环路滤波器的设计1. 绪论1.1 研究背景1.2 研究目的与意义1.3 现有研究综述2. 无源环路滤波器原理2.1 电荷泵2.2 锁相环2.3 无源滤波器2.4 四阶环路滤波器3. 设计方案3.1 系统框图3.2 电路设计流程3.3 具体电路设计4. 实验验证4.1 实验设备与方法4.2 实验结果与分析5. 结论与展望5.1 结论总结5.2 研究展望及不足参考文献1. 绪论1.1 研究背景滤波器是电子系统中重要的信号处理器件,用于滤除噪声、干扰等非期望信号,提高系统性能和可靠性。

传统的滤波器通常包括有源滤波器和无源滤波器,有源滤波器具有较高的增益和带宽,但容易产生交叉耦合、不稳定性等问题,不适合高灵敏度和高可靠性的系统应用。

相对地,无源滤波器不需要功率放大器,具有低噪声、低失真、高工作稳定性等优点,因此受到广泛关注。

环路滤波器是一种无源滤波器,它利用环路反馈结构实现信号滤波,可以用于时钟恢复、PLL电路、模数转换器、数字信号处理等领域。

环路滤波器的特点是抑制抖动频率和高频噪声,同时保持信号相位不变,因此能够有效地减少电子系统中时钟服从误差、干扰等问题。

而四阶环路滤波器是基于二阶滤波器级联实现的,具有更高的阻带深度和抑制量,因此适用于对要求更高的滤波应用领域。

1.2 研究目的与意义目前,环路滤波器的设计研究已经相对成熟,但在实际应用中,仍然存在一些问题,如:滤波器带宽、抑制深度、相位噪声等方面的指标需要进一步优化,同时还需要提高滤波器的环路稳定性和抗噪声干扰能力。

因此,本文旨在设计一种基于电荷泵锁相环的四阶无源环路滤波器,通过优化电路设计与参数选择,提高滤波器的性能指标和工作稳定性,实现滤波效果更加优异的无源滤波器。

1.3 现有研究综述电荷泵锁相环作为一种广泛应用于频率合成和时钟恢复领域的锁相环,其具有结构简单、工作稳定、精度高等优点,目前已经在许多应用领域中得到推广应用。

同时,环路滤波器也是一种常用的滤波器结构,在信号处理、相位锁定等领域被广泛应用。

三阶锁相环环路滤波器参数设计

[8]

3

2

2

2

2

2

2 锁相环线性模型

锁相环的线性模型如图 1 所示 , 图中 K, F ( s ) ,

1 / s分别是环路总增益 、 环路滤波器 、 VCO 环节

[ 8, 9 ]

;

由图可以得到系统的开环传递函数 、 闭环传递函数 [ 8, 9 ] 和误差传递函数 。

利用伯德法则 : 当开环增益为 1 时 ,其相位余 量必须大 于 0, 闭环 才 能 稳 定 。根 据 开 环 方 程 式 ( 5 ) ,计算出增益临界频率为 τ 2 ωT = K 2 ( 7) τ 1 环路稳定的相位条件 : ωTτ 2a rc tg + 180 °> 0 2 - 270 ° 由上式可求得稳定条件 : 2 τ 1 K > 3 τ 2 令

3

摘 要 : 锁相环在通信 、 遥测 、 导航等领域有着广泛的应用 ,三阶锁相环由于其频率斜率跟踪能力 ,越 来越受到重视 ,特别是深空探测的极窄带应用 。利用系统稳定性分析方法和高阶系统分析理论 ,分 别对两种模型的二阶环路滤波器 ,即理想二阶滤波器和三参数滤波器模型 ,推导了参数设计公式 ,给 出三阶锁相环设计参数的模拟及数字环路公式 , 并与 JPL 数字锁相环 ( DPLL ) 的设计参数经验公式 进行比较 。仿真结果表明 , 3 种设计方法近似相同 ,而所推导的参数设计方法优点在于可以灵活配 置系统的零 、 极点的位置以及阻尼系数等多种参数 ,为各种变带宽和自适应算法提供理论和应用基 础。 关键词 : 深空探测 ; 数字锁相环 ; 环路滤波器 ; 稳定条件 ; 高阶系统分析 ; 参数设计 中图分类号 : TN713 文献标识码 : A

其地面锁相接收机中的应用

基于FPGA的宽频数字锁相环设计

[ l Sn0 l 入 位 字 正 0 i( 0 S0 , i 数乘法器 n I 弦值 (i 制 的 相 sn 控 复

I 复数乘法器 弦但 ( n1 和 余 弦 ) 口 ) 匀 布

I S。 c 1 值 c 不断 复 i I n 。 l ( ) 作 J o 兰=== 二 = I 数 算复 乘 器 运 ,数 法

图 3 复数相乘法器 就 会 输 出 两 路 正 交 的三角函数信 号

。

, 一

春

() 2

复数运算一次 的时间固定 , 改变 输入相 位 的正 、 弦值 , 余 就 能得到不 同频率 的输 出信 号 。然 而, 复数 相乘方 式需 要首 先计算 出输入相位控 制字 的正 、 余弦值 , 因此 , 以结 合查 可

求指数增长 。因此 , 主要缺 点是 当精度要 求较 高时 占用 内

结合使 用。

输 入输 出关 系 的 常 系数 差 分 方 程 为

(z 一 6z( 十 6 z( 1 + bx( - 2 + a ( 1 , ) D ) l 一 ) z n ) l 咒一 )

+ 口 ( 2 一 2 )

( 4 仿 真 性 能分 析 4 )

数字仿真框 图如 图 4 数控振荡 器中心频 率 4 k , , 0 Hz 频 率锁定范 围 3  ̄4 k , 入信 号是 经过 2 4 6 Hz输 4位编码 的正弦

() 3

将 上 式 化 为 标 准 滤 波 器形 式 如 下

F( 一 o - l ) b q b z

— —

1-

k zz Z b -

—

=

—

找表 和 C R C方 式实现输入信 号重建 。考虑到精度和 占 O DI 用 资源大小 的问题 , O D C算 法更 适合 与复数 相乘算 法 C R I

锁相频率合成器的设计

目录摘要 (1)1. 设计任务 (2)2. 锁相频率合成器的硬件设计 (2)2.1 锁相环基本原理 (2)2.2 频率合成器总体设计方案 (3)2.3 VCO电路设计(MAX2620) (4)2.4 集成锁相环电路设计(MB1504) (6)2.5 单片机控制电路设计 (9)3. 软件设计 (11)3.1 MB1504数据输入设计 (11)3.2 程序流程设计 (13)总结 (15)参考文献 (16)锁相频率合成器的设计摘要由锁相环构成的间接式频率合成器在无线通信领域发挥着非常重要的作用。

通常采用锁相频率合成器的输出信号来作为无线接收机中的本振信号,以使直接频率调制器、频率解调器能够从输入信号中再生载波。

本文锁相频率合成器的整个设计方案,包括压控振荡器VCO电路设计、MB1504集成锁相环电路设计、以及单片机最小硬件系统、单片机与MB1504接口电路等硬件电路设计;软件方面,以MB1504串行数据输入格式为标准,通过分析MB1504串行数据传输时序图,建立了串行通信协议。

关键词:频率合成器;锁相环;控振荡器(VCO)1. 设计任务设计一个基于锁相环的锁相频率合成器2. 锁相频率合成器的硬件设计2.1 锁相环基本原理锁相环(PLL )是一个相位跟踪系统。

图2-1显示了最基本的锁相环方框图。

它包括三个基本部件,鉴相器(PD ) 环路滤波器(LPF )和压控振荡器(VCO )图2- 1 基本的锁相环方框图设参考信号(1) 式中 ur 为参考信号的幅度ωr 为参考信号的载波角频率θr(t)为参考信号以其载波相位ωrt 为参考时的瞬时相位若参考信号是未调载波时,则θr(t)= θ1=常数。

设输出信号为(2)式中 Uo 为输出信号的振幅ωo 为压控振荡器的自由振荡角频率θo (t)为参考信号以其载波相位ωot 为参考时的瞬时相位, 在VCO 未受控制前他是常数,受控之后他是时间函数。

则两信号之间的瞬时相位差为(3) 由频率和相位之间的关系可得两信号之间的瞬时频差为(4)()sin[()]r r r r u t U t t ωθ=+()cos[()]o o o o u t U t t ωθ=+0000()()(())()()c r r r r t t t t t t θωθωθωωθθ=+-+=-+-00()()e r d t d t dt dt θθωω=--鉴相器是相位比较器,他把输出信号uo(t)和参考信号ur(t)的相位进行比较,产生对应于两信号相位差θe (t)的误差电压ud(t)。

毕业设计论文:PLL锁相环电路

摘要随着通信及电子系统的飞速发展,促使集成锁相环和数字锁相环突飞猛进。

本次毕业设计的主要任务是,采用0.18μm CMOS工艺,设计实现一个基于改进的鉴频鉴相器,压控振荡器,环路滤波器的全集成的CMOS PLL锁相环电路,设计重点为PLL锁相环电路的版图设计,设计工具为Laker。

本论文介绍了PLL锁相环电路的基本原理以及其完整的版图设计结果。

本次设计表明,采用该方案实现的锁相环电路主要功能工作正常,初步达到设计要求。

关键词:PLL锁相环电路,鉴频鉴相器,压控振荡器,环路滤波器,版图设计,0.18μm CMOS工艺AbstractWith the development of the communications and electronic systems, the technology of the integrated PLL and digital PLL develops rapidly.The main task of graduation is to design and realize a fully integrated CMOS PLL circuit which is based on an improved phase detector, VCO, loop filter using the 0.18μm CMOS technology. The design focus on the layout of the PLL circuit, and the design tools is the Laker.This paper introduces the basic principles of PLL phase locked loop circuit and its comprehensive layout results. This design shows that the program implemented by the main function of PLL circuit is working well, and it meets the design requirements.Key words:PLL phase locked loop circuits, popularly used phase detectors, discrimination, VCO loop filter, layout design, 0.18 μm CMOS process目录摘要 (1)Abstract (2)第1章绪论 (4)1.1 锁相技术的发展 (4)1.2 锁相环路的主要特性 (4)1.3 PLL锁相环的应用领域 (5)第2章基于CMOS锁相环的电路设计 (7)2.1 锁相环的基本组成 (7)2.2 锁相环工作原理 (7)2.3 鉴相器 (8)2.3.1 鉴频鉴相器(PFD) (9)2.3.2 鉴频鉴相器设计 (10)2.4 环路滤波器 (10)2.5 压控振荡器 (11)第3章关于COMS锁相环的版图设计 (12)3.1 电路设计 (12)3.2 版图设计 (12)3.2.1 版图设计规则检查 (13)3.2.2 注意事项 (13)3.3 锁相环的版图设计 (15)第4章结束语 (17)参考文献 (18)致谢 (19)第1章绪论1.1锁相技术的发展锁相技术起源于20世纪30年代,提出无线电调幅信号的锁相同步检波技术。

基于ADF4360-1的2.4G频率合成器设计

基于ADF4360-1的2.4G频率合成器设计作者:杨婧来源:《科技创新导报》 2013年第1期杨婧(中北大学信息探测与处理技术研究所山西太原 030051)摘?要:该文通过高性能、低功耗的8位ATmega8微处理器产生控制信号,利用美国ADI公司生产的锁相环芯片ADF4360-1,设计了一个稳定的2.4?GHz本振信号源电路模块,可广泛应用于电视,仪器,通信等领域。

文中详细介绍了系统中核心芯片的性能、结构以及应用方法,设计出了完整的硬件电路并对电路的各个参数进行了评估,结果基本上符合要求。

关键词:ATmega8 ADF4360-1?锁相环频率合成?本振信号源中图分类号:TN742 文献标识码:A 文章编号:1674-098X(2013)01(a)-00-01在现代无线电通信及相关领域中,为确保通信的稳定和可靠,对通信设备的频率准确度和稳定度提出了越来越高的要求。

与LC振荡电路“跑频”严重相比,晶体振荡电路具有可微调的稳定频率,但变化范围小,频率值不高。

频率合成技术是指将一个或少量的高稳定度、高准确度的标准频率作为参考频率,经过相应的信号处理过程,从而获得大量离散的具有同一稳定度和准确度的信号频率。

主要有三种合成方法:直接模拟合成、锁相环合成以及直接数字合成。

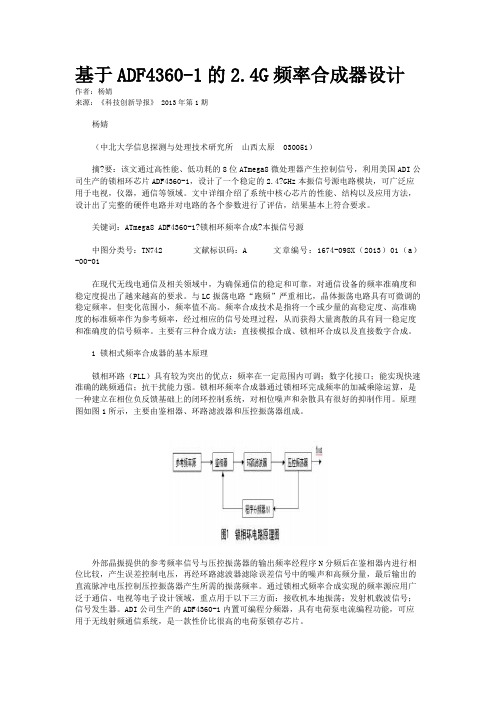

1 锁相式频率合成器的基本原理锁相环路(PLL)具有较为突出的优点:频率在一定范围内可调;数字化接口;能实现快速准确的跳频通信;抗干扰能力强。

锁相环频率合成器通过锁相环完成频率的加减乘除运算,是一种建立在相位负反馈基础上的闭环控制系统,对相位噪声和杂散具有很好的抑制作用。

原理图如图1所示,主要由鉴相器、环路滤波器和压控振荡器组成。

外部晶振提供的参考频率信号与压控振荡器的输出频率经程序N分频后在鉴相器内进行相位比较,产生误差控制电压,再经环路滤波器滤除误差信号中的噪声和高频分量,最后输出的直流脉冲电压控制压控振荡器产生所需的振荡频率。

通过锁相式频率合成实现的频率源应用广泛于通信、电视等电子设计领域,重点用于以下三方面:接收机本地振荡;发射机载波信号;信号发生器。

基本理论锁相环是一个闭环的相位负...

基于Matlab的锁相环设计摘要随着现代集成电路技术的发展,锁相环已经成为集成电路设计中非常重要的一个部分,所以对锁相环的研究具有积极的现实意义。

锁相环电路是一种输出信号在频率和相位上能够与输入参考信号同步的电路,锁相环由于其具有一系列独特的优良性能,它已经成为通信、雷达、导航、电子仪器仪表等设备中不可缺少的一部分。

所以这些年来锁相环的设计与研究工作也越来越受到人们的重视,人们开始利用人工计算或计算机软件来分析锁相环的性能。

在研究大量资料的基础之上,先对锁相系统的基本工作原理进行了分析,以传统模拟锁相环的结构为基础,分析了锁相环的数学模型,详细描述了锁相环的整体电路以及鉴相器、环路滤波器、压控振荡器等电路模块。

并以此为出发点对锁相环的锁定性能、及稳定性能、等各种性能进行了分析。

在分析和设计的同时,也采用Matlab软件对锁相环电路进行了仿真。

首先分析了一阶锁相环和二阶锁相环的锁定性能,并进行了比较。

其次分析了阻尼系数 对环路稳定性能的影响。

最后介绍了锁相环的调制作用。

从锁相环的仿真结果可知,我们的理论研究结果和实验结果相符,锁相环电路达到了设计指标要求。

关键词锁相环;Matlab;仿真Phase-Locked Loop Design Based on MatlabAbstractWith the development of modern integrated circuit technology, phase locked loop has become a significant component of integrated circuit, which makes the research of phase-locked loop valuable. Phase-locked loop is a kind of circuit that an output signal in the frequency and phase reference signal can be synchronized with the input. Because of a series of uniquely excellent performances, it is becoming an indispensable part of the equipments such as communication, radar, airmanship, electronic instrument etc. People realize the importance of the design and study of PLL , they come to use artificially calculation or software to analyze the property of PLL.After a deep study of the materials about PLL, this thesis starts with the analysis of the fundamental principles of a phase-locked system , then we build the mathematical model based on the traditional of the PLL, describes the overall PLL circuit and phase detector, loop filter, VCO circuit module, etc, and afterwards investigate some of its characters such as locking performance and stability.In the analysis and design, but also we conducted a phase locked loop circuit simulation by Matlab software. First of all, we analyzed the first-order phase lock loop and a second order phase-locked loop lock performance, and on the basis of the comparison. Secondly we analyzed the damping how to stability of the loop. Finally we introduced the modulation of the phase locked loop. From the simulation results, we know that the theory conclusions and the simulation results fit well phase-locked loop circuit to the design requirements.Keywords PLL, simulation, Matlab目录摘要 (I)Abstract (II)第1章绪论 (1)1.1 课题背景及研究意义 (1)1.2 发展历程 (2)1.3 国内外发展现状 (3)1.4 锁相环的应用 (4)1.4.1 频率合成 (5)1.4.2 时钟产生器 (5)1.4.3 时钟恢复电路 (5)1.4.4 偏移减小 (6)1.5 本文的章节安排及主要内容 (6)第2章锁相环理论 (7)2.1 基本理论 (7)2.2 基本模块 (8)2.2.1 鉴相器 (8)2.2.2 环路滤波器 (10)2.2.3 压控振荡器 (11)2.3 环路的相位模型及基本方程 (12)2.4 环路性能 (12)2.4.1 线性化相位模型和传递函数 (13)2.4.2 锁定状态下锁相环的动态特性 (14)2.5 本章小结 (16)第3章锁相环仿真 (17)3.1 Matlab软件介绍 (17)3.2 锁定性能 (18)3.2.1 一阶锁相环 (18)3.2.2 二阶锁相环 (19)3.2.3 一阶锁相环与二阶锁相环比较 (21)3.3 环路性能 (21)3.3.1 鉴相器的输出 (22)3.3.2 低通滤波器的输出 (23)3.3.3 压控振荡器的输出 (24)3.4 稳定性能 (25)3.5 调制作用 (27)3.6 本章小结 (28)结论 (29)致谢 (30)参考文献 (31)附录A (33)附录B (36)第1章绪论1.1课题背景及研究意义在现代集成电路中,锁相环(Phase Locked Loop)是一种广泛应用于模拟、数字及数模混合电路系统中的非常重要的电路模块。

基于CD4046锁相环的频率合成器设计

三、确定电路组成方案

原理框图(图1)如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N,从而就得到N倍参考频率的稳定输出。晶体振荡器输出的信号频率f1,经固定分频后(M分频)得到基准频率f2,输入锁相环的相位比较器(PC)。锁相环的VCO输出信号经可编程分频器(N分频)后输入到PC的另一端,这两个信号进行相位比较,当锁相环路锁定后得到:

图2 1——999分频器

五、锁相环参数设计

本设计中,M固定,N可变。基准频率f2定为100Hz,改变N值,使N=7001~7999,则可产生f2=700.1KHz—799.9KHz的频率范围。锁相环锁存范围:

fmax=800.00KHz

fmin=700.00KHz

则fmax/fmin=1.1

使用相位比较器PC2

(三)、N分频的设计

根据本次课程设计的要求,需设计一个N=7000-7999的分频计。通过方案的比较采用四块CD4522构成。CD4522是可预置数的二一十进制1/N减计数器。其引脚见附录。其中D1-D4是预置端,Q1—Q4是计数器输出端,其余控制端的功能如下:

PE(3)=1时,D1—D4值置进计数器EN(4)=0,且CP(6)时,计数器(Q1—Q4)减计数;CF(13)=1且计数器(Q1—Q4)减到0时,QC(12)=1 Cr(10)=1时,计数器清零。

3、拨动拨码盘,测输出频率

拨码盘

输出频率f(Hz)

输出波形

7000

700.00K

方波

7001

700.10K

方波

7051

705.10K

方波

7551

755.10K