3D集成中的晶圆键合挑战

中国晶圆片键合机市场现状及未来发展趋势

我国晶圆片键合机市场现状及未来发展趋势一、背景介绍我国晶圆片键合机市场是半导体行业的重要组成部分,晶圆片键合技术是半导体封装过程中的重要环节。

随着技术的不断进步和需求的增长,我国晶圆片键合机市场蕴含着巨大的商机和发展潜力。

本文将对我国晶圆片键合机市场的现状和未来发展趋势进行深入探讨。

二、现状分析1. 市场规模根据数据统计,我国晶圆片键合机市场规模近年来呈现出稳步增长的态势。

加上国家在半导体产业上的政策扶持和资金投入,我国半导体行业不断崛起,带动了晶圆片键合机市场的发展。

目前,我国晶圆片键合机市场规模已经位居全球前列。

2. 技术水平我国晶圆片键合机行业的技术水平在不断提高,一批技术过硬的企业不断涌现。

与国外先进技术相比,我国晶圆片键合机行业在一些方面还存在一定差距,但在国内市场的推动下,我国企业正在积极进行技术研发和创新,逐步缩小与国外差距。

3. 市场竞争我国晶圆片键合机市场存在着激烈的竞争态势。

国内外品牌企业纷纷进入我国市场,加剧了市场的竞争激烈度。

晶圆片键合技术的专利和核心技术成为企业竞争的重要制高点,技术创新成为市场竞争的关键。

三、未来发展趋势1. 技术创新未来,我国晶圆片键合机市场将持续加大技术创新力度。

随着新一代通信技术的到来,对晶圆片键合技术的要求也将更高。

企业需要不断加大研发投入,提高核心技术竞争力,以满足市场对高性能、高可靠性晶圆片键合机的需求。

2. 国际合作随着我国半导体产业进一步开放,国际合作将成为未来的发展趋势。

我国晶圆片键合机企业需要通过与国际先进企业的合作,引进国外先进技术和管理经验,提高自身竞争力。

3. 服务升级未来,我国晶圆片键合机企业将更加注重服务的升级和提升。

高品质的产品质量和良好的售后服务将成为市场竞争的新制胜点,客户需求将成为企业发展的关键导向。

四、个人观点我国晶圆片键合机市场作为半导体产业的重要组成部分,具有巨大的发展潜力。

在未来的市场中,技术创新、国际合作和服务升级将是企业持续发展的重要方向。

晶圆混合键合工艺优化研究

2 实验方案

本文研究了金属铜键合垫和氧化层相对高度对 hybrid bonding 工 艺 空 洞 的 影 响 。 应 该 看 到 ,在 bonding 前晶圆表面平坦化处理过程中,由于氧化层 的研磨速率和金属铜的研磨速率存在较大的差异, 所以在最终形成的晶圆表面上,金属铜键合垫和 SiO2 很难完全保持在同一水平面上。基此,我们通 过实验,调整了金属铜键合垫和氧化层相对高度,分 为如以下 2 种情况,研究了金属铜键合垫和氧化层 相对高度对 hybrid bonding 空洞的影响。具体表现:

http://

2021·7· (总第 266 期)65

封装

CIC 中国集成电路

China lntegrated Circult

0 引言

一是,晶圆在完成前段器件形成以及后段金属 互联工艺之后,将两片晶圆表面分别做平坦化处理,

日益增长的消费类电子产品市场不断推动着半 导体技术飞速发展,各种应用对芯片的集成度要求 不断提高,芯片尺寸不断减小,促使了各种新技术进 步都可在 CMOS 工艺中获得了应用,包括有多重光 刻图形化、新的应变增强材料和金属氧化物栅介质 等。目前集成电路工艺技术节点已经实现了 5nm 工 艺的量产,继续缩小晶体管尺寸使技术复杂度变得 越来越困难,而且继续缩小尺寸已经不能降低单位 晶体管的成本,所以越来越难以找到一种解决方案 来满足在增加器件性能的同时又能降低成本的要 求。

第一种情况。如图 3(a)所示,在,其是通过加大 对 Cu 的研磨量,使 Cu 金属键合垫的高度低于二氧 化硅氧化层;

第二种情况。如图 3(b)所示,其是通过加大对 SiO2 的研磨量,使最终晶圆上金属铜键合垫的高度 略高于二氧化硅氧化层。

图 2 键合空洞 C-SAM 图片 http://

试议3D封装到来时的机遇与挑战

试议3D封装到来时的机遇与挑战刘斌;严仕新【摘要】揭示了在摩尔定律即将失效的大背景下,电子信息产业的开发思维、生产方式将发生一系列变革;阐述了3D封装将是电子产业发展的必然趋势;反映了检测手段的提高是3D封装目前面临的主要难题.分析了我国信息电子产业在此环境下所面临的机遇和挑战.【期刊名称】《电子工业专用设备》【年(卷),期】2010(039)007【总页数】7页(P23-28,42)【关键词】摩尔定律;3D封装;微焊点自动光学显微检测(MMI)【作者】刘斌;严仕新【作者单位】苏州德天光学技术有限公司,江苏,苏州,215000;苏州德天光学技术有限公司,江苏,苏州,215000【正文语种】中文【中图分类】TN401目前,国际电子信息行业正在经历一场新的变革,摩尔定律即将失效,3D封装蓬勃兴起,如果我们能抓住这个机会,对国内相关行业及其发展环境进行大力改革整顿,顺应世界发展潮流,将大大缩小我们同国际先进水平的差距。

1 摩尔定律的失效摩尔定律是由英特尔创始人之一戈登·摩尔(GordonMoore)提出,其内容为:集成电路上可容纳的晶体管数目,约每隔18个月便会增加1倍(见图1),性能也将提升1倍。

这一定律揭示了信息技术进步的速度。

图1 摩尔定律但是,进入新世纪后,实现等比例缩减的代价变得非常高,器件尺寸已接近单个原子,而原子无法缩减。

其次,尽管目前出现了多内核处理器,但日常使用的应用软件无法利用如此强大的处理能力;而建设芯片工厂的天价成本也阻碍摩尔定律的延伸。

摩尔本人也明确表示,摩尔定律只能再延续10年,此后在技术上将会十分困难,在他看来,摩尔定律已经走到尽头。

由此将引起产业内的一系列的变革。

1.1 开发思维的变革与此同时人们逐渐发现,当今微电子产业的发展正在呈现出两个特点:一是更加符合摩尔定律(More Moore),即建立在摩尔定律基础上的CMOS技术将持续高速发展,更高集成度、更大规模的处理器和存储器件将在电子系统中扮演“大脑”的角色;而另一方面,由无源器件、传感器、通讯器件、连接技术等非数字技术的多种技术将会构成一股不容忽视的“超越摩尔定律 (More than Moore也称新摩尔定律)”的新兴封装技术(见图2),在数字化的“大脑”周围构建起电子设备中感知和沟通外部世界的部分[1]。

tek晶圆键合

tek晶圆键合1. 介绍tek晶圆键合是一种用于集成电路制造的关键工艺。

它是将两个或多个半导体材料通过压力和温度结合在一起的过程。

这种键合技术广泛应用于半导体器件的封装和组装过程中,能够实现高精度、高可靠性的电气和机械连接。

2. tek晶圆键合的原理tek晶圆键合的原理是利用金属间的冷焊或热焊来实现材料的连接。

在键合过程中,首先将两个待键合的材料表面清洁,并使其平整。

然后,通过施加压力和加热,使材料表面的金属层发生扩散,形成金属间的键合。

最后,冷却和固化键合区域,完成键合过程。

3. tek晶圆键合的应用tek晶圆键合在集成电路制造中有着广泛的应用。

以下是一些常见的应用领域:3.1 封装技术tek晶圆键合在集成电路封装过程中起到关键作用。

它能够将芯片和封装基板连接在一起,形成完整的封装结构。

通过键合技术,可以实现芯片与封装基板之间的电气连接,同时还能够提供机械支撑和热传导功能。

3.2 三维集成电路三维集成电路是一种新型的集成电路结构,通过在垂直方向上堆叠多个芯片,实现更高的集成度和性能。

tek晶圆键合是实现三维集成电路的关键技术之一。

通过键合技术,可以将不同功能的芯片堆叠在一起,并实现它们之间的电气连接。

3.3 光电子器件tek晶圆键合也广泛应用于光电子器件的制造过程中。

例如,光电二极管的制造过程中,需要将半导体芯片与光纤连接在一起。

通过键合技术,可以实现芯片与光纤之间的精确对准和稳定连接,从而提高光电子器件的性能和可靠性。

3.4 传感器制造传感器是一种能够将物理量转化为电信号的器件,广泛应用于工业控制、环境监测等领域。

tek晶圆键合在传感器制造中起到重要作用。

通过键合技术,可以实现传感器芯片与电路之间的连接,同时还能够提供良好的机械支撑和热传导性能。

4. tek晶圆键合的优势与其他键合技术相比,tek晶圆键合具有以下优势:4.1 高精度tek晶圆键合能够实现非常高的精度。

通过控制压力和温度等工艺参数,可以实现微米级的对准精度和键合精度。

mems的晶圆键合 -回复

mems的晶圆键合-回复mems的晶圆键合(mems wafer bonding)是一种用于制造微电子机械系统(micro-electromechanical systems,MEMS)的高级封装技术。

它的主要作用是将不同材料的晶圆或片层通过键合技术结合在一起,实现多层结构的制备。

本文将对mems的晶圆键合技术进行详细介绍。

第一步:mems晶圆键合的概述mems晶圆键合技术是一种先进的封装技术,用于将微小的机械和电子元件封装在一起,并实现它们之间的可靠连接。

它在MEMS器件制造中起着重要的作用,确保了器件的稳定性和可靠性。

该技术主要通过将不同材料或晶圆片层键合在一起,形成复合的功能元件,从而实现MEMS器件的制备。

第二步:mems晶圆键合的原理mems晶圆键合技术主要依靠两种主要的键合机制:金属键合和无金属键合。

金属键合主要通过金属间的互溶作用,实现键合的稳定性和可靠性。

无金属键合主要依靠压力和温度的作用,将不同材料的片层键合在一起。

第三步:mems晶圆键合的材料选择在mems晶圆键合中,材料的选择是非常重要的。

不同的材料具有不同的热膨胀系数和力学性能,因此在进行键合之前,需要仔细选择适合的材料。

常用的材料包括金属、氧化物和半导体材料。

第四步:mems晶圆键合的工艺步骤mems晶圆键合技术通常包括以下几个步骤:1. 表面处理:对键合表面进行预处理,以确保良好的键合质量。

常见的表面处理方法包括化学清洗和离子束清洗等。

2. 对接和定位:将需要键合的两个晶圆或片层对接在一起,并进行精确的定位,以确保正确的对准。

3. 压力和温度控制:在键合过程中,需要施加适当的压力和温度。

这些参数的选择通常基于材料的性质和键合的要求。

4. 键合力的应用:将键合介质(如金属膜或无机介质)放置在两个晶圆或片层之间,施加适当的键合力,实现键合。

5. 剩余应力的消除:键合完成后,可能会产生一些剩余应力。

为了消除这些应力,通常需要进行退火处理或其他应力释放技术。

临时键合技术在晶圆级封装工艺运用的研究

残留,然后重新涂胶。 溅射金属的sputtering和CVD制程对胶材的考验是最大的,目

前的临时键合胶水耐受温度都不高,低温CVD(150℃以下)可耐 受,recipe需要特殊调试,要求缓升缓降。对于更高温度要求的工 艺,极易出现“雪花纹”以及分层,如图10所示:

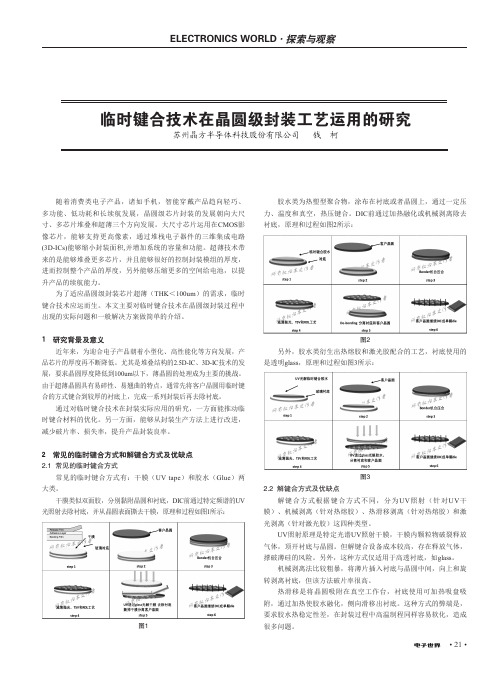

为了适应晶圆级封装芯片超薄(THK<100um)的需求,临时 键合技术应运而生。本文主要对临时键合技术在晶圆级封装过程中 出现的实际问题和一般解决方案做简单的介绍。

胶水类为热塑型聚合物,涂布在衬底或者晶圆上,通过一定压 力、温度和真空,热压键合。DIC前通过加热融化或机械剥离除去 衬底,原理和过程如图2所示:

ELECTRONICS WORLD・探索与观察

临时键合技术在晶圆级封装工艺运用的研究

苏州晶方半导体科技股份有限公司 钱 柯

随着消费类电子产品,诸如手机,智能穿戴产品趋向轻巧、 多功能、低功耗和长续航发展,晶圆级芯片封装的发展朝向大尺 寸、多芯片堆叠和超薄三个方向发展。大尺寸芯片运用在CMOS影 像芯片,能够支持更高像素,通过堆栈电子器件的三维集成电路 (3D-ICs)能够缩小封装面积,并增加系统的容量和功能。超薄技术带 来的是能够堆叠更多芯片,并且能够很好的控制封装模组的厚度, 进而控制整个产品的厚度,另外能够压缩更多的空间给电池,以提 升产品的续航能力。

1 研究背景及意义 近年来,为迎合电子产品朝着小型化、高性能化等方向发展,产

品芯片的厚度再不断降低。尤其是堆叠结构的2.5D-IC、3D-IC技术的发 展,要求晶圆厚度降低到100um以下,薄晶圆的处理成为主要的挑战。 由于超薄晶圆具有易碎性、易翘曲的特点,通常先将客户晶圆用临时键 合的方式键合到较厚的衬底上,完成一系列封装后再去除衬底。

光刻和晶圆级键合技术在D互连中的研究

光刻和晶圆级键合技术在3D互连中的研究作者:Margarete Zoberbier、Erwin Hell、Kathy Cook、Marc Hennemayer、Dr.-Ing. Barbara Neubert,SUSS MicroTec日益增长的消费类电子产品市场正在推动当今半导体技术的不断创新发展。

各种应用对增加集成度、降低功耗和减小外形因数的要求不断提高,促使众多结合了不同技术的新结构应运而生,从而又催生出诸多不同的封装方法,因此可在最小的空间内封装最多的功能。

正因如此,三维集成被认为是下一代的封装方案。

本文将探讨与三维互连技术相关的一些光刻挑战。

还将讨论三维封装使用的晶圆键合技术、所面临的各种挑战、有效的解决方案及未来发展趋势。

多种多样的三维封装技术为了适应更小引脚、更短互连和更高性能的要求,目前已开发出系统封装(SiP)、系统芯片(S oC)和封装系统(SoP)等许多不同的三维封装方案。

SiP即“单封装系统”,它是在一个IC封装中装有多个引线键合或倒装芯片的多功能系统或子系统。

无源元件、SAW/BAW滤波器、预封装IC、接头和微机械部件等其他元件都安装在母板上。

这一技术造就了一种外形因数相对较小的堆叠式芯片封装方案。

SoC可以将所有不同的功能块,如处理器、嵌入式存储器、逻辑心和模拟电路等以单片集成的方式装在一起。

在一块半导体芯片上集成系统设计需要这些功能块来实现。

通常,SoC设计与之所取代的多芯片系统相比,它的功耗更小,成本更低,可靠性更高。

而且由于系统中需要的封装更少,因而组装成本也会有所降低。

SoP采用穿透通孔和高密度布线以实现更高的小型化。

它是一种将整个系统安装在一个芯片尺寸封装上的新兴的微电子技术。

过去,“系统”往往是一些容纳了数百个元件的笨重的盒子,而S oP可以将系统的计算、通信和消费电子功能全部在一块芯片上完成,从而节约了互连时间,减少了热量的产生。

最近穿透硅通孔(TSV)得到迅速发展,已成为三维集成和晶圆级封装(WLP)的关键技术之一。

微系统封装技术-键合技术

航空航天领域

用于制造微型化航空电子设备、 卫星电路模块等。

通信领域

用于制造手机、路由器、交换 机等通信设备中的微型化电路 模块。

医疗领域

用于制造微型化医疗器械,如 植入式电子器件、医疗传感器 等。

智能制造领域

用于制造微型化工业传感器、 控制器等智能制造设备中的电 路模块。

02

键合技术的基本原理

键合技术的定义

键合技术的关键要素

键合材料的选择

总结词

选择合适的键合材料是实现高质量微系统封装的关键,需要考虑材料的物理性质、化学稳定性、热膨胀系数匹配 等因素。

详细描述

在微系统封装中,键合材料的选择至关重要。材料需要具备优良的导热性、导电性、耐腐蚀性和稳定的化学性质, 以确保键合的可靠性和长期稳定性。此外,材料的热膨胀系数也需要与基材相匹配,以减少因温度变化引起的应 力,防止键合层破裂或脱落。

超声键合技术

超声键合技术是一种利用超声波能量实现芯片 与基板连接的封装技术。

超声键合技术具有非热、非机械接触、快速和 低成本的优点,适用于各种不同类型的材料和 器件。

超声键合技术的关键在于超声波的传播和控制, 需要精确控制超声波的频率、振幅和作用时间 等参数,以确保键合的质量和可靠性。

热压键合技术

环境友好型封装技术

无铅封装

推广无铅封装技术,减少 对环境的重金属污染,满 足绿色环保要求。

可回收封装

研究开发可回收再利用的 封装材料和工艺,降低资 源消耗和环境污染。

节能封装

优化封装设计和工艺,降 低微系统封装的能耗,实 现节能减排的目标。

06

结论

微系统封装技术的重要性

提升电子设备性能

节能环保

键合质量的检测与控制

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SEMI大半导体产业网

CARRIER WAFER SOLUTION – LASER ABLADABLE GLUES

Figures courtesy of 3M

10

7/14/2010

Event, Venue information

SEMI大半导体产业网

Outline

Thin wafer handling for 3D integration: Requirements Current solutions

– – – – – – – General process flow Carrier wafers – Laser abladable glues Carrier wafers – Thermoplastic glue materials Carrier wafers – Peelable glue materials Carrier wafers – Room Temperature debondable glue materials Carrier wafers – Chemically removable glues Carrierless – Patterned support ring

SUSS XBC300 (Picture source: imec)

EVG 850DB Platform (Picture courtesy of EVG)

Equipment available from various suppliers

14

SEMI大半导体产业网

CARRIER WAFER SOLUTION – LASER ABLADABLE GLUES

Top device wafer

Adhesive layer

Top device wafer

Adhesive layer

Glass carrier

Glass carrier

Figures courtesy of 3M

Carriers recyclable

15

7/14/2010

Event, Venue information

SEMI大半导体产业网

Outline

Thin wafer handling for 3D integration: Requirements Current solutions

1

7/14/2010

Event, Venue information

SEMI大半导体产业网

Outline

Thin wafer handling for 3D integration: Requirements Current solutions Carrier-based thin wafer handling: generic learning Ideas / Questions for standardization

– – – – – – – General process flow Carrier wafers – Laser abladable glues Carrier wafers – Thermoplastic glue materials Carrier wafers – Peelable glue materials Carrier wafers – Room Temperature debondable glue materials Carrier wafers – Chemically removable glues Carrierless – Patterned support ring

SEMI大半导体产业网

wafer bonding challenges for 3-D integration

Wafer bonding challenges for 3-D integration

Anne Jourdain, Andy Miller and Bart Swinnen

Carrier-based thin wafer handling: generic learning Ideas / Questions for standardization

4

7/14/2010

Event, Venue information

SEMI大半导体产业网

8

7/14/2010

Event, Venue information

SEMI大半导体产业网

CARRIER WAFER SOLUTION – LASER ABLADABLE GLUES

Figures courtesy of 3M

9

7/14/2010

Event, Venue information

Carrier-based thin wafer handling: generic learning Ideas / Questions for standardization

12

7/14/2010

Event, Venue information

SEMI大半导体产业网

Carrier-based thin wafer handling: generic learning Ideas / Questions for standardizationnt, Venue information

SEMI大半导体产业网

Carrier based approaches: General process flow lay-out

6

7/14/2010

Event, Venue information

SEMI大半导体产业网

Outline

Thin wafer handling for 3D integration: Requirements Current solutions

– – – – – – – General process flow Carrier wafers – Laser abladable glues Carrier wafers – Thermoplastic glue materials Carrier wafers – Peelable glue materials Carrier wafers – Room Temperature debondable glue materials Carrier wafers – Chemically removable glues Carrierless – Patterned support ring

Carrier-based thin wafer handling: generic learning Ideas / Questions for standardization

3

SEMI大半导体产业网

Outline

Thin wafer handling for 3D integration: Requirements Current solutions

– – – – – – – General process flow Carrier wafers – Laser abladable glues Carrier wafers – Thermoplastic glue materials Carrier wafers – Peelable glue materials Carrier wafers – Room Temperature debondable glue materials Carrier wafers – Chemically removable glues Carrierless – Patterned support ring

Carrier-based thin wafer handling: generic learning Ideas / Questions for standardization

5

7/14/2010

Event, Venue information

SEMI大半导体产业网

CARRIER WAFER SOLUTION – LASER ABLADABLE GLUES

Key Features: CTE matched, transparent carriers Process:

– Deposition on both carrier & device wafer – Vacuum bonding + UV-cure – Low-T, light assisted release

2

7/14/2010

Event, Venue information

SEMI大半导体产业网

Thin wafer handling for 3D integration: Requirements Provide sufficient mechanical stability for backside processing Compatible with product integration flow

CARRIER WAFER SOLUTION: THERMOPLASTIC GLUE MATERIALS

Heat Thinned device Thinned device substrate

Slide

Spin rinse with solvent & spin dry Si wafer as carrier

Temperature budgets Chemical compatibility Cleanliness

Compatible with standard processing tools Reasonable COO Requirements apply to Carrier + adhesive + device system

– – – – – – – General process flow Carrier wafers – Laser abladable glues Carrier wafers – Thermoplastic glue materials Carrier wafers – Peelable glue materials Carrier wafers – Room Temperature debondable glue materials Carrier wafers – Chemically removable glues Carrierless – Patterned support ring