八位七段数码管动态显示电路设计

(完整word版)八位七段数码管动态显示电路设计

八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。

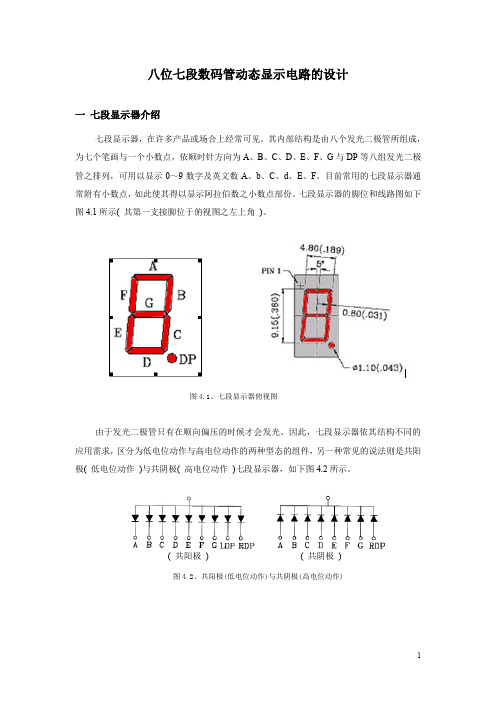

其内部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。

目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。

七段显示器的脚位和线路图如下图4.1所示( 其第一支接脚位于俯视图之左上角)。

图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时候才会发光。

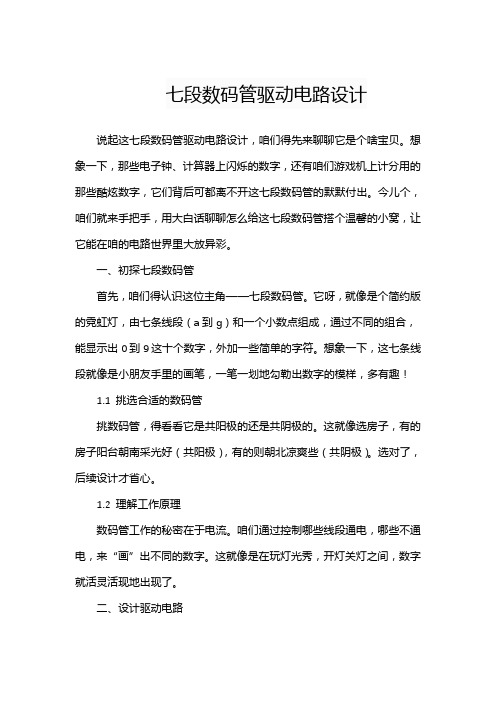

因此,七段显示器依其结构不同的应用需求,区分为低电位动作与高电位动作的两种型态的组件,另一种常见的说法则是共阳极( 低电位动作)与共阴极( 高电位动作)七段显示器,如下图4.2所示。

( 共阳极) ( 共阴极)图4.2、共阳极(低电位动作)与共阴极(高电位动作)要如何使七段显示器发光呢?对于共阴极规格的七段显示器来说,必须使用“ Sink Current ”方式,亦即是共同接脚COM为VCC,并由Cyclone II FPGA使接脚成为高电位,进而使外部电源将流经七段显示器,再流入Cyclone II FPGA的一种方式本实验平台之七段显示器模块接线图如下图4.5所示。

此平台配置了八组共阳极之七段显示器,亦即是每一组七段显示器之COM接脚,均接连至VCC电源。

而每一段发光二极管,其脚位亦均与Cyclone II FPGA接连。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

图4.5、七段显示器模块接线图七段显示器之常见应用如下可作为与数值显示相关之设计。

⏹电子时钟应用显示⏹倒数定时器⏹秒表⏹计数器、定时器⏹算数运算之数值显示器二七段显示器显示原理七段显示器可用来显示单一的十进制或十六进制的数字,它是由八个发光二极管所构成的( 每一个二极管依位置不同而赋予不同的名称,请参见图4.1 ) 。

七段数码管驱动电路设计

七段数码管驱动电路设计说起这七段数码管驱动电路设计,咱们得先来聊聊它是个啥宝贝。

想象一下,那些电子钟、计算器上闪烁的数字,还有咱们游戏机上计分用的那些酷炫数字,它们背后可都离不开这七段数码管的默默付出。

今儿个,咱们就来手把手,用大白话聊聊怎么给这七段数码管搭个温馨的小窝,让它能在咱的电路世界里大放异彩。

一、初探七段数码管首先,咱们得认识这位主角——七段数码管。

它呀,就像是个简约版的霓虹灯,由七条线段(a到g)和一个小数点组成,通过不同的组合,能显示出0到9这十个数字,外加一些简单的字符。

想象一下,这七条线段就像是小朋友手里的画笔,一笔一划地勾勒出数字的模样,多有趣!1.1 挑选合适的数码管挑数码管,得看看它是共阳极的还是共阴极的。

这就像选房子,有的房子阳台朝南采光好(共阳极),有的则朝北凉爽些(共阴极)。

选对了,后续设计才省心。

1.2 理解工作原理数码管工作的秘密在于电流。

咱们通过控制哪些线段通电,哪些不通电,来“画”出不同的数字。

这就像是在玩灯光秀,开灯关灯之间,数字就活灵活现地出现了。

二、设计驱动电路接下来,就是给数码管找个好搭档——驱动电路。

这就像是给数码管找了个司机,告诉它啥时候该亮,啥时候该暗。

2.1 选择驱动芯片市面上有好多驱动芯片,比如74HC595、TM1637等,它们就像是不同类型的汽车,有的省油(功耗低),有的跑得快(驱动能力强)。

咱们得根据实际需求,挑个最合适的。

2.2 搭建电路框架搭电路就像搭积木,把电源、驱动芯片、数码管还有必要的电阻电容按规矩摆好。

电源是心脏,驱动芯片是大脑,数码管是显示屏,电阻电容则是调节器,保证电路稳定运行。

2.3 编程控制电路搭好了,还得给它编个程序,告诉它怎么工作。

这就像是在教小朋友跳舞,一步步指导它怎么迈步、转身。

编程时,咱们得设定好每个数字对应的线段组合,让数码管能按咱们的意愿显示。

三、调试与优化电路搭完,程序编好,接下来就是见证奇迹的时刻了。

八位数码管扫描显示电路的设计

《EDA技术及应用》课程设计报告题目:八位数码管扫描显示电路的设计院(系):机电与自动化学院专业班级:电气自动化技术学生姓名:学号:指导教师:20 年6月10日至20 年6月23日华中科技大学武昌分校4、课程设计使用设备(1)EDA及SOPC综合实验平台;(2)导线若干;(3)PC机;(4)Quartus II开发工具软件。

目录摘要................................................................1.课程设计题目及要求 (1)1.1设计题目 (1)1.2L E D显示器的动态扫描驱动电路 (1)1.3设计方案论证 (1)2.L E D显示器动态扫描驱动电路各单元电路设计 (3)2.1计数器与译码器的设计 (3)2.2一位共阳极L E D动态驱动电路设计 (4)2.3七段数码管的设计 (5)3.L E D显示器动态扫描系统设计 (7)3.1整体电路图及工作原理 (7)3.2V H D L程序设计 (7)3.3电路参数计算 (10)4.Q u a r t u s运行调试 (12)4.1时序仿真 (12)4.2硬件逻辑验证 (13)4.3调试结果分析 (13)4.4调试中出现的问题及解决方法 (14)5.设计总结 (15)6.参考文献 (16)摘要本文通过一个3-8译码器电路,将输入的4位2进制数转换为与LED显示对应的8位段码,位码就是LED的显示使能端,对于共阳级的LED而言,高电平使能。

要使8个数码管动态扫描显示,就是把所有数码管的相同段并联在一起,通过选通信号分时控制各个数码管的公共端,循环点亮多个数码管,并利用人眼的视觉暂留现象,只要扫描的频率大于50Hz,将看不到闪烁现象。

使用Quartus II6.0软件设计一个VHDL程序并对设计方案进行仿真,再硬件调试经检测输出正确的设计要求结果。

关键词:动态扫描Quartus II6.0 VHDLAbstractIn this paper, through a 3-8 decoder circuit, the input of four hexadecimal number into 2 and eight LED display the corresponding section of code, a codeis the LED display can make side, for the LED with Yang level, high level canmake. To makeeight digital tube dynamic scans showed that is all the samesegment digital tube connected in parallel, through the gating signal time-sharing control public side, the digital tube loop light multiple digital tube, and use the eye of the phenomenon of persistence of vision, as long as the scanning frequency is more than 50 hz, will see the flicker phenomenon. Using Quartus II6.0 a VHDL program design and the software design simulation, and hardware debugging through testing output correct design requirementsKey words: dynamic scanning Quartus II6.0 VHDL1. 课程设计题目及要求1.1设计题目八位数码管扫描显示电路的设计设计主要内容:本课题要求掌握使用Quartus II设计数字系统的设计思路和设计方法。

《FPGA设计与应用》数码管显示实验一

《FPGA设计与应用》数码管显示实验一、实验目的和要求

1.学习动态数码管的工作原理;

2.实现对EGO1开发板四位动态数码管的控制;

二、实验内容

实现对EGO1开发板四位动态数码管的控制,使其能够正常工作;

三、实验要求

在EGO1开发板上显示想要的数字。

四、操作方法与实验步骤

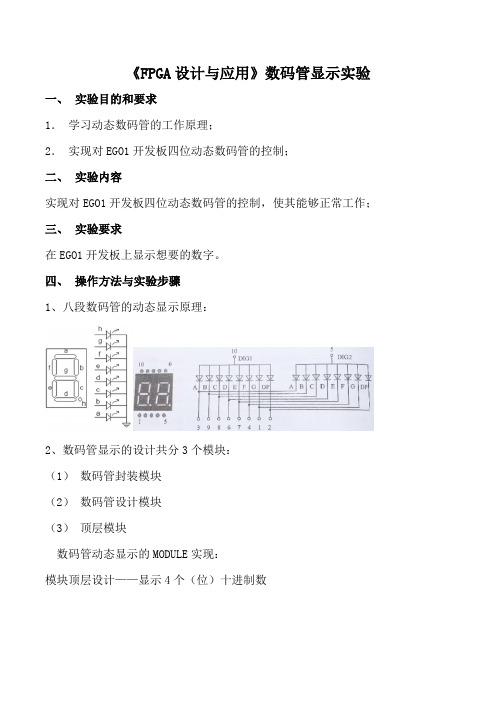

1、八段数码管的动态显示原理:

2、数码管显示的设计共分3个模块:

(1)数码管封装模块

(2)数码管设计模块

(3)顶层模块

数码管动态显示的MODULE实现:

模块顶层设计——显示4个(位)十进制数

逻辑实现:

确定当前显示的位

确定当前“位”需要显示的“数”:

将“数”翻译成相应的“段码”

仿真测试台代码编写与仿真测试定义时间标尺:

定义测试Moudle

实例化被测Moudle

定义激励信号与响应信号

构造激励信号:

五、实验数据记录和处理实验代码如下:

设计文件:(部分)

仿真文件:

约束文件:

六、实验结果与分析网表结构:

仿真图像:

实物图:

七、讨论和心得

通过这次实验,我学会了数码管的动态显示,每一个数码管共用一套电路,显示时只需控制哪一个数码管进行显示。

虽然一次只能控制单独一个数码管进行显示,但可以快速切换数码管显示,利用人眼的”视觉暂留"来“同步”进行显示。

最后我明白了我们不要遇到一点困难就退缩,就去向老师同学寻求帮助,自己是自己最好的老师,只有我们靠自己的不断修改出正确结果,才会对这个知识掌握的更加透彻。

专题七动态扫描电路设计

Q[7..0] RD 读数据控制

ARCHITECTURE a OF MEMO_RD_WR IS

SIGNAL Q0,Q1,Q2,Q3: STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL Q4,Q5,Q6,Q7: STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

扫描控制器时序图

ARCHITECTURE a OF SCAN_8 IS SIGNAL NUM: INTEGER RANGE 7 DOWNTO 0;

BEGIN PROCESS(CLK2)

BEGIN IF CLK2'EVENT AND CLK2=‘1' THEN

IF NUM<=7 THEN NUM<=NUM+1;

七段LED数码管显示电路设计(精)

实验七七段LED数码管显示电路设计一、实验目的1.学习EDA软件的基本操作2.学习使用原理图进行设计输入3.初步掌握软件输入、编译、仿真和编程的过程4.学习实验开发系统的使用方法二、实验说明本实验通过七段LED数码管显示电路的设计,初步掌握EDA 设计方法中的设计输入、编译、综合、仿真和编程的基本过程。

七段LED数码管显示电路有四个数据输入端(D0-D3),七个数据输出端(A-G。

三、实验要求1、完成七段LED数码管显示电路的原理图输入并进行编译2、对设计的电路经行仿真验证3、编程下载并在实验开发系统上验证设计结果四、实验步骤1、新建工程2、新建Verilog HDL文件3、在文本输入窗口键入代码4、保存HDL文件5、编译文件直至没有错误6、新建波形文件7、添加观察信号8、添加输入激励,保存波形文件9、功能仿真七段LED数码管显示电路真值表:输入D3D2D1D0G F E D C B A 000000111111 100010000110 200101011011 300111001111 401001100110 501011101101 601101111101 701110001111 810001111111910011101111 A10101110111 B10111111100 C11001111001 D110111011110 E11101111001 F11111110001五、电路原理图啊Verilog代码描述:module qiduan(data_in,data_out;input [3:0]data_in;output [6:0]data_out;reg [6:0]data_out;always @(data_inbegincasex(data_in4'b0000:data_out<=7'b0111111;4'b0001:data_out<=7'b0000110; 4'b0010:data_out<=7'b1011011; 4'b0011:data_out<=7'b1001111; 4'b0100:data_out<=7'b1100110; 4'b0101:data_out<=7'b1101101; 4'b0110:data_out<=7'b1111100; 4'b0111:data_out<=7'b0000111; 4'b1000:data_out<=7'b1111111; 4'b1001:data_out<=7'b1100111; 4'b1010:data_out<=7'b1110111; 4'b1011:data_out<=7'b1111100; 4'b1100:data_out<=7'b0111001; 4'b1101:data_out<=7'b1011110; 4'b1110:data_out<=7'b1111001; 4'b1111:data_out<=7'b1110001; default:data_out<=7'b0000000; endcaseendendmodule仿真波形:六、实验体会七段LED数码管显示电路是常用的数码管之一,它有四个数据输入端(D0-D3),七个数据输出端(A-G。

组合电路——7段数码管显示驱动电路设计报告

实验一、组合电路——7段数码管显示驱动电路设计一、实验目的了解EDA实验箱7位八段数码管显示模块的工作原理,设计标准扫描驱动电路模块,以备后面实验用。

二、硬件要求主芯片为Cyclone V E,型号为EP4CE22F17C8,7位八段数码管显示器,四位拨码开关。

三、实验内容用四位拨码开关产生8421BCD码,用CPLD分别产生7段数码管扫描驱动电路,然后进行仿真,观察波形,正确后编程下载实验测试。

四、实验原理1、72、动信号a,b,c,d,e,f,g。

通过调节四位拨码开关的状态,数码管应显示与之对应的字符。

五、实验连线输入:将芯片管角a0~a3分别接4个拨码开关;输出:将芯片管角led7s0~7分别接到数码管7段驱动信号a、b、c、d、e、f、g上。

六、实验源程序:decl7s.vhdlibrary ieee;use ieee.std_logic_1164.all;entity decl7s isport(a:in std_logic_vector(3 downto 0);led7s:out std_logic_vector(6 downto 0));end;architecture one of decl7s isbeginprocess(a)begincase a iswhen "0000" => led7s<="0111111"; when "0001" => led7s<="0000110"; when "0010" => led7s<="1011011"; when "0011" => led7s<="1001111"; when "0100" => led7s<="1100110"; when "0101" => led7s<="1101101"; when "0110" => led7s<="1111101"; when "0111" => led7s<="0000111"; when "1000" => led7s<="1111111"; when "1001" => led7s<="1101111"; when "1010" => led7s<="1110111"; when "1011" => led7s<="1111100"; when "1100" => led7s<="0111001"; when "1101" => led7s<="1011110"; when "1110" => led7s<="1111001"; when "1111" => led7s<="1110001"; when others => null;end case;end process;end;七、波形仿真结果。

EDA设计课程实验报告数码管动态显示实验报告

EDA设计课程实验报告实验题目:数码管动态显示实验学院名称:专业:电子信息工程班级:姓名:高胜学号小组成员:指导教师:一、实验目的学习动态扫描显示的原理;利用数码管动态扫描显示的原理编写程序,实现自己的学号的显示。

二、设计任务及要求1、在SmartSOPC实验箱上完成数码管动态显示自己学号的后八个数字。

2、放慢扫描速度演示动态显示的原理过程。

三、系统设计1、整体设计方案数码管的八个段a,b,c,d,e,f,g,h(h是小数点)都分别连接到SEG0~SEG7,8个数码管分别由八个选通信号DIG0~DIG7来选择,被选通的数码管显示数据,其余关闭。

如果希望8个数码管显示希望的数据,就必须使得8个选通信号DIG0~DIG7分别被单独选通,并在此同时,在段信号输入口SEG0~SEG7加上该对应数码管上显示的数据,于是随着选通信号的扫描就能实现动态扫描显示的目的。

虽然每次只有1个数码管显示,但只要扫描显示速率足够快,利用人眼的视觉余辉效应,我们仍会感觉所有的数码管都在同时显示。

2、功能模块电路设(1)输入输出模块框图(见图1)图1(2)模块逻辑表达(见表1)表1(数码管显示真值表)clk_1k dig seg↑01111111 C0↑10111111 F9注:数码管显示为01180121(3)算法流程图(见图2)(4)Verilog源代码module scan_led(clk_1k,d,dig,seg); //模块名scan_ledinput clk_1k; //输入时钟input[31:0] d; //输入要显示的数据output[7:0] dig; //数码管选择输出引脚output[7:0] seg; //数码管段输出引脚reg[7:0] seg_r; //定义数码管输出寄存器reg[7:0] dig_r; //定义数码管选择输出寄存器reg[3:0] disp_dat; //定义显示数据寄存器reg[2:0]count; //定义计数寄存器assign dig = dig_r; //输出数码管选择assign seg = seg_r; //输出数码管译码结果always @(posedge clk_1k) //定义上升沿触发进程begincount <= count + 1'b1;endalways @(posedge clk_1k)begincase(count) //选择扫描显示数据3'd0:disp_dat = d[31:28]; //第一个数码管3'd1:disp_dat = d[27:24]; //第二个数码管3'd2:disp_dat = d[23:20]; //第三个数码管3'd3:disp_dat = d[19:16]; //第四个数码管3'd4:disp_dat = d[15:12]; //第五个数码管3'd5:disp_dat = d[11:8]; //第六个数码管3'd6:disp_dat = d[7:4]; //第七个数码管3'd7:disp_dat = d[3:0]; //第八个数码管endcasecase(count) //选择数码管显示位3'd0:dig_r = 8'b01111111; //选择第一个数码管显示3'd1:dig_r = 8'b10111111; //选择第二个数码管显示3'd2:dig_r = 8'b11011111; //选择第三个数码管显示3'd3:dig_r = 8'b11101111; //选择第四个数码管显示3'd4:dig_r = 8'b11110111; //选择第五个数码管显示3'd5:dig_r = 8'b11111011; //选择第六个数码管显示3'd6:dig_r = 8'b11111101; //选择第七个数码管显示3'd7:dig_r = 8'b11111110; //选择第八个数码管显示endcaseendalways @(disp_dat)begincase(disp_dat) //七段译码4'h0:seg_r = 8'hc0; //显示04'h1:seg_r = 8'hf9; //显示14'h2:seg_r = 8'ha4; //显示24'h3:seg_r = 8'hb0; //显示34'h4:seg_r = 8'h99; //显示44'h5:seg_r = 8'h92; //显示54'h6:seg_r = 8'h82; //显示64'h7:seg_r = 8'hf8; //显示74'h8:seg_r = 8'h80; //显示84'h9:seg_r = 8'h90; //显示94'ha:seg_r = 8'h88; //显示a4'hb:seg_r = 8'h83; //显示b4'hc:seg_r = 8'hc6; //显示c4'hd:seg_r = 8'ha1; //显示d4'he:seg_r = 8'h86; //显示e4'hf:seg_r = 8'h8e; //显示fendcaseendendmodule四、系统调试(1)仿真代码`timescale 1ns/1nsmodule scan_ledfz;reg clk_1k;reg[31:0] d;wire[7:0] dig;wire[7:0] seg;parameter dely=100;scan_led u1(clk_1k,d,dig,seg);always #(dely/2)clk_1k=~clk_1k;initial beginclk_1k=0;d=32'h01180134;#dely ;#dely ;#dely ;#dely ;#dely ;#(dely*20);#dely $finish;endinitial $monitor($time,,,"%b,%d,%h,%h",clk_1k,d,dig,seg); endmodulemodule scan_led(clk_1k,d,dig,seg); //模块名scan_ledinput clk_1k; //输入时钟input[31:0] d; //输入要显示的数据output[7:0] dig; //数码管选择输出引脚output[7:0] seg; //数码管段输出引脚reg[7:0] seg_r; //定义数码管输出寄存器reg[7:0] dig_r; //定义数码管选择输出寄存器reg[3:0] disp_dat; //定义显示数据寄存器reg[2:0] count=3'b000; //定义计数寄存器assign dig = dig_r; //输出数码管选择assign seg = seg_r; //输出数码管译码结果always @(posedge clk_1k) //定义上升沿触发进程begincount <= count + 1'b1;endalways @(posedge clk_1k)begincase(count) //选择扫描显示数据3'd0:disp_dat = d[31:28]; //第一个数码管3'd1:disp_dat = d[27:24]; //第二个数码管3'd2:disp_dat = d[23:20]; //第三个数码管3'd3:disp_dat = d[19:16]; //第四个数码管3'd4:disp_dat = d[15:12]; //第五个数码管3'd5:disp_dat = d[11:8]; //第六个数码管3'd6:disp_dat = d[7:4]; //第七个数码管3'd7:disp_dat = d[3:0]; //第八个数码管endcasecase(count) //选择数码管显示位3'd0:dig_r = 8'b01111111; //选择第一个数码管显示3'd1:dig_r = 8'b10111111; //选择第二个数码管显示3'd2:dig_r = 8'b11011111; //选择第三个数码管显示3'd3:dig_r = 8'b11101111; //选择第四个数码管显示3'd4:dig_r = 8'b11110111; //选择第五个数码管显示3'd5:dig_r = 8'b11111011; //选择第六个数码管显示3'd6:dig_r = 8'b11111101; //选择第七个数码管显示3'd7:dig_r = 8'b11111110; //选择第八个数码管显示endcaseendalways @(disp_dat)begincase(disp_dat) //七段译码4'h0:seg_r = 8'hc0; //显示04'h1:seg_r = 8'hf9; //显示14'h2:seg_r = 8'ha4; //显示24'h3:seg_r = 8'hb0; //显示34'h4:seg_r = 8'h99; //显示44'h5:seg_r = 8'h92; //显示54'h6:seg_r = 8'h82; //显示64'h7:seg_r = 8'hf8; //显示74'h8:seg_r = 8'h80; //显示84'h9:seg_r = 8'h90; //显示94'ha:seg_r = 8'h88; //显示a4'hb:seg_r = 8'h83; //显示b4'hc:seg_r = 8'hc6; //显示c4'hd:seg_r = 8'ha1; //显示d4'he:seg_r = 8'h86; //显示e4'hf:seg_r = 8'h8e; //显示fendcaseendendmodule位码代码仿真代码`timescale 1ns/1nsmodule smg_tp; //测试模块的名字reg [2:0] c; //测试输入信号定义为reg型wire[7:0] dig; //测试输出信号定义为wire型parameter DEL Y=100; //延时100秒wei u1(c,dig); //调用测试对象initial begin //激励波形设定c=3'b0;#DEL Y c=3'b001 ;#DEL Y c=3'b010 ;#DEL Y c=3'b100 ;#DEL Y c=3'b101 ;#DEL Y c=3'b110 ;#DEL Y c=3'b111 ;#DEL Y $finish;endinitial $monitor($time,,,"dig=%d,c=%b ",dig,c); //输出格式i定义endmodulemodule wei(c,dig); //命名模块名字input[2:0] c;output[7:0] dig; //定义输入与输出reg[7:0] dig_r;reg[2:0] c_r; // 定义dig_r与c_r2个reg型数据assign dig=dig_r; //将reg型数据转化为wire型数据always @(*) //检测c_r的数据是否变化begin c_r=c;case (c_r)3'b000:dig_r=8'b11111110; //c_r的数据变化而dig_r对于的数据变化3'b001:dig_r=8'b11111101;3'b010:dig_r=8'b11111011;3'b011:dig_r=8'b11110111;3'b100:dig_r=8'b11101111;3'b101:dig_r=8'b11011111;3'b110:dig_r=8'b10111111;3'b111:dig_r=8'b01111111;default: dig_r=8'b11111111;endcase //结束case语句end //结束always语句endmodule //结束程序译码器代码仿真代码`timescale 1ns/1nsmodule duan_tp; //测试模块的名字reg[3:0] a; //测试输入信号定义为reg型wire[7:0] seg; //测试输出信号定义为wire型parameter DEL Y=100; //延时100秒duan u1(a,seg); //调用测试对象initial begin //激励波形设定a=4'b0;#DELY a=4'b0001;#DELY a=4'b0010;#DELY a=4'b0011;#DELY a=4'b0100;#DELY a=4'b0101;#DELY a=4'b0110;#DELY a=4'b0111;#DELY a=4'b1000;#DELY a=4'b1001;#DELY a=4'b1010;#DELY a=4'b1011;#DELY a=4'b1100;#DELY a=4'b1101;#DELY a=4'b1110;#DELY a=4'b1111;#DELY $finish;endinitial $monitor($time,,,"seg=%d,a=%b",seg,a); //输出格式i定义endmodulemodule duan(a,seg); //命名模块名字input[3:0] a;output[7:0] seg; //定义输入与输出reg[7:0] seg_r;reg[3:0] a_r; // 定义seg_r与a_r2个reg型数据assign seg=seg_r; //将reg型数据转化为wire型数据always @(*) //检测c_r的数据是否变化begin a_r=a;case(a_r) //七段译码4'b0000:seg_r = 8'hc0; //显示04'b0001:seg_r = 8'hf9; //显示14'b0010:seg_r = 8'ha4; //显示24'b0011:seg_r = 8'hb0; //显示34'b0100:seg_r = 8'h99; //显示44'b0101:seg_r = 8'h92; //显示54'b0110:seg_r = 8'h82; //显示64'b0111:seg_r = 8'hf8; //显示74'b1000:seg_r = 8'h80; ///显示84'b1001:seg_r = 8'h90; //显示94'b1010:seg_r = 8'h88; //显示a4'b1011:seg_r = 8'h83; //显示b4'b1100:seg_r = 8'hc6; //显示c4'b1101:seg_r = 8'ha1; //显示d4'b1110:seg_r = 8'h86; //显示e4'b1111:seg_r = 8'h8e; ///显示f endcase //结束case语句end //结束always语句endmodule //结束程序(2)仿真波形图(3)引脚图五、实验感想通过这次实验,让我学习动态扫描显示的原理;利用数码管动态扫描显示的原理编写程序,实现自己的学号的显示。

七段数码管的动态扫描显示实验

七段数码管的动态扫描显示实验七段数码管的动态扫描显示实验一、实验名称:七段数码管的动态扫描显示实验二、实验目的:(1)进一步熟悉QuartusII软件进行FPGA设计的流程(2)掌握利用宏功能模块进行常用的计数器,译码器的设计(3)学习和了解动态扫描数码管的工作原理的程序设计方法三、实验原理:实验板上常用4位联体的共阳极7段数码管,其接口电路是把所有数码管的8个笔划段a-h同名端连在一起,而每一个数码管由一个独立的公共极COM端控制。

当向数码管发送字形码时,所有数码管都接收到相同的字形码时,但究竟是那个数码管亮,取决于COM端,这一端是由I/O控制的,所以就可以自行决定何时显示哪一位。

动态扫描即采用分时方法,轮流控制各个LED轮流点亮。

在轮流点亮扫描过程中,每一位显示器的点亮时间是极为短暂的,但由于人的视觉暂留现象及发光二极管的余辉效应,尽管实际上每个显示器并非同时点亮,但只要扫描的速度足够快,给人的印象就是一组稳定的显示数据,不会有闪烁感。

四、实验要求:实现显示0000-9999的十进制计数器。

五、实验步骤1.建立工程建立名为leddisplay的工程,并建立顶层图。

2.设计技术时钟设计一分频器,对50MHz分频输出到计数器,让计数器以较慢速度递增。

打开File..New,新建一个.v文件。

输入以下程序: module int_div(clk, div_out); input clk;output reg div_out; reg [31:0] clk_div;parameter CLK_FREQ = 'D50_000_000; //系统时钟50MHz parameterDCLK_FREQ = 'D10; //输出频率10/2Hz always @(posedge clk) beginif(clk_div Set as top-level Entity。

分析该设计文件:执行工具栏处的“Start Analysis &Synthesis命令按钮,开始分析综合,此步骤在这里用于检查设计错误。

EDA8位计数显示译码电路的设计

EDA8位计数显示译码电路的设计八位计数显示译码电路是一种常见的数字电路设计,用于将二进制计数器的输出转换为对应的字符或数字显示。

本次EDA报告将介绍八位计数显示译码电路的设计原理、功能和设计过程。

1.设计原理:八位计数显示译码电路的主要原理是通过接收二进制计数器的输出信号,通过对应的译码器将其转换为七段数码管的控制信号,从而实现显示。

2.设计功能:八位计数显示译码电路的功能主要包括:-显示功能:将二进制计数器的输出显示在七段数码管上,实现数字的可视化显示。

-增量计数:根据输入的时钟信号进行增量计数,实现从0到255的循环计数。

-译码功能:将二进制计数器的输出信号转换为七段数码管的控制信号,控制数码管上对应的数码显示。

3.设计过程:八位计数显示译码电路的设计过程主要包括以下几个步骤:3.1确定输入与输出首先,我们需要确定设计的输入和输出。

输入主要包括时钟信号和复位信号,用于控制计数和复位操作;输出为控制七段数码管显示的控制信号。

3.2确定译码方式根据设计需求,我们可以选择使用常见的译码方式,如BCD译码器、十六进制译码器等。

根据实际情况选择适合的译码方式,使得设计简单有效。

3.3确定译码逻辑在确定了译码方式后,需要根据输入信号和输出信号的关系,确定译码逻辑。

根据二进制计数器的输出信号,将其映射到对应的数字或字符,为七段数码管提供正确的控制信号。

3.4组合逻辑设计根据译码逻辑,设计出控制信号的生成电路。

可以使用门电路、与非门电路或多路选择器等组合逻辑电路实现。

3.5简化逻辑电路对于逻辑电路的设计,可以使用布尔代数、卡诺图等方法进行简化和优化,使电路结构更为简洁。

3.6电路仿真与验证完成电路设计后,可以使用电路仿真工具对电路进行验证和测试,确保电路功能正确。

4.设计注意事项:在设计八位计数显示译码电路时,需要注意以下几点:4.1七段数码管的驱动电流和电压根据所选用的七段数码管的规格,需要确保驱动电流和电压符合规格要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。

其内部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。

目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。

七段显示器的脚位和线路图如下图4.1所示( 其第一支接脚位于俯视图之左上角)。

图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时候才会发光。

因此,七段显示器依其结构不同的应用需求,区分为低电位动作与高电位动作的两种型态的组件,另一种常见的说法则是共阳极( 低电位动作)与共阴极( 高电位动作)七段显示器,如下图4.2所示。

( 共阳极) ( 共阴极)图4.2、共阳极(低电位动作)与共阴极(高电位动作)要如何使七段显示器发光呢?对于共阴极规格的七段显示器来说,必须使用“ Sink Current ”方式,亦即是共同接脚COM为VCC,并由Cyclone II FPGA使接脚成为高电位,进而使外部电源将流经七段显示器,再流入Cyclone II FPGA的一种方式本实验平台之七段显示器模块接线图如下图4.5所示。

此平台配置了八组共阳极之七段显示器,亦即是每一组七段显示器之COM接脚,均接连至VCC电源。

而每一段发光二极管,其脚位亦均与Cyclone II FPGA接连。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

图4.5、七段显示器模块接线图七段显示器之常见应用如下➢可作为与数值显示相关之设计。

⏹电子时钟应用显示⏹倒数定时器⏹秒表⏹计数器、定时器⏹算数运算之数值显示器二七段显示器显示原理七段显示器可用来显示单一的十进制或十六进制的数字,它是由八个发光二极管所构成的( 每一个二极管依位置不同而赋予不同的名称,请参见图4.1 ) 。

我们可以简单的说,要产生数字,便是点亮特定数据的发光二极管。

例如要产生数字「0」,须只点亮A、B、C、D、E、F等节段的发光二极管;要产生数字「5」,则须点亮A、C、D、F、G等节段发光二极管,以此类推,参见图4.6。

因此,以共阳极七段显示器而言,要产生数字「0」,必须控制Cyclone II FPGA芯片接连至A、B、C、D、E、F 等接脚呈现“低电位”,使电路形成通路状态。

表4.1则为共阳极七段显示器显示之数字编码。

图4.6、七段显示器显示阿拉伯数字资料DP G F E D C B A16进制011000000C0111111001F9210100100A4310110000B0410011001995100100109261000001082711111000F881000000080本实验要求完成的任务是在时钟信号的作用下,通过输入的键值在数码管上显示相应的键值。

在实验中时,数字时钟选择1KHZ作为扫描时钟,用四个拨动开关做为输入,当四个拨动开关置为一个二进制数时,在数码管上显示其十六进制的值。

实验箱中的拨动开关与FPGA的接口电路,以及拨动开关FPGA的管脚连接在实验一中都做了详细说明,这里不在赘述。

数码管显示模块的电路原理如图4-2所示,图4-2 数字时钟信号模块电路原理三实验步骤(本实验用VHDL文本语言实现八位七段数码管动态显示,当然也可用Quartus的图形输入法实现八位七段数码管动态显示)1. 下面我们建立一个八位七段数码管动态显示的VHDL工程1)选择开始> 程序> Altera > QuartusII5.1,运行QUARTUSII软件。

或者双击桌面上的QUARTUSII的图标运行QUARTUSII软件,出现如图1-3所示。

图1-3 QUARTUSII软件运行界面2)选择软件中的菜单File > New Project Wizard,新建一个工程。

如图1-4所示。

图1-4 新建工程对话框3)点击图1-4中的NEXT进入工作目录,工程名的设定对话框如图1-5所示。

第一个输入框为工程目录输入框,用户可以输入如e:/eda等工作路径来设定工程的目录,设定好后,所有的生成文件将放入这个工作目录。

第二个输入框为工程名称输入框,第三个输入框为顶层实体名称输入框。

用户可以设定如EXP1,一般情况下工程名称与实体名称相同。

使用者也可以根据自已的实际情况来设定工程名和顶层文件名。

注:本处的顶层文件名必须和程序的实体名一致,否则编译会出错。

图1-5 指定工程名称及工作目录4)点击NEXT,进入下一个设定对话框,按默认选项直接点击NEXT进行器件选择对话框。

如图1-6所示。

这里我们以选用CycloneII系列芯片EP2C35F672C8为例进行介绍。

用户可以根据使用的不同芯片来进行设定。

图1-6 器件选择界面首先在对话框的左上方的Family下拉菜单中选取CycloneII,在中间右边的Speed grade下拉菜单中选取8,在左下方的Available devices框中选取EP2C35F672C8,点击NEXT完成器件的选取,进入EDA TOOL设定界面如图1-7所示。

图1-7 EDA TOOL对话框5)按默认选项,点击Next出现新建工程以前所有的设定信息,如图1-8所示,点击Finish完成新建工程的建立。

图1-8 新建工程信息2、建立VHDL设计文件1)在创建好设计工程后,选择File > NEW…菜单,出现图1-9所示的新建设计文件类型选择窗口。

这里我们以建立VHDL设计文件为例进行说明。

图1-9 新建设计文件选择窗口2)在New对话框(图1-9)中选择Device Design Files页下的VHDL File,点击OK按钮,打开图形编辑器对话框,如图1-10所示。

图中标明了常用的每个按钮的功能3)在文本编辑器中输入如下VHDL程序:--下面是引用库-------------------------------------library ieee; --库函数use ieee.std_logic_1164.all;--定义了std_logic数据类型及相应运算use ieee.std_logic_arith.all;--定义了signed和unsigned数据类型、相应运算和相关类型转换函数use ieee.std_logic_unsigned.all;--定义了一些函数,可以使std_logic_vector 类--型被当作符号数或无符号数一样进行运算----------------------------------------------------------------------下面是构造实体entity exp4 is --exp4为实体名port( clk : in std_logic; --定义动态扫描时钟信号key : in std_logic_vector(3 downto 0); --定义四位输入信号ledag : out std_logic_vector(6 downto 0); --定义七位输出信号del : out std_logic_vector(2 downto 0) --定义八位数码管位置显示信号);end exp4; --结束实体--------------------------------------------------------------------architecture whbkrc of exp4 is --whbkrc为结构体名begin --以begin为标志开始结构体的描述process(clk) --进程,clk变化时启动进程variable dount : std_logic_vector(2 downto 0); --变量,计数beginif clk'event and clk='1' then--检测时钟上升沿dount:=dount+1;--计数器dount累加end if;del<=dount; --片选信号end process;--结束进程process(key) --进程,key变化时启动进程begincase key iswhen "0000" => ledag <="0111111";--七段数码管显示0when "0001" => ledag <="0000110";--1when "0010" => ledag <="1011011";--2when "0011" => ledag <="1001111";--3when "0100" => ledag <="1100110";--4when "0101" => ledag <="1101101";--5when "0110" => ledag <="1111101";--6when "0111" => ledag <="0000111";--7when "1000" => ledag <="1111111";--8when "1001" => ledag <="1101111";--9when "1010" => ledag <="1110111";-- Rwhen "1011" => ledag <="1111100";--bwhen "1100" => ledag <="0111001";--Cwhen "1101" => ledag <="1011110";--dwhen "1110" => ledag <="1111001";--Ewhen "1111" => ledag <="1110001";--Fwhen others => null;end case;end process; --结束进程end whbkrc; --结束结构体关于VHDL,我们以上面八位七段数码管显示程序为例来解释VHDL的语法构成,以使大家对VHDL有个整体的把握。