FPGA芯片比较20100511

fpga芯片的种类

fpga芯片的种类FPGA芯片的种类FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,它具有灵活可塑性和高性能,被广泛应用于数字电路设计和嵌入式系统开发领域。

随着技术的不断发展,FPGA芯片也呈现出多样化的种类和功能,本文将介绍几种常见的FPGA芯片。

1. Xilinx Virtex系列Xilinx Virtex系列是业界最强大的FPGA产品系列之一。

它以其卓越的性能和丰富的资源而受到广泛关注。

Virtex系列采用了最新的FPGA架构,具有高达数百万个可编程逻辑单元(LUT)和丰富的高速IO接口,可满足复杂系统设计的需求。

此外,Virtex系列还提供了丰富的硬核IP(Intellectual Property),如处理器核、高速串行收发器等,使其在高性能计算和通信领域具有重要应用。

2. Altera Cyclone系列Altera Cyclone系列是一种低成本、低功耗的FPGA芯片,广泛用于嵌入式系统和消费电子产品中。

Cyclone系列采用了先进的工艺技术,具有较高的逻辑密度和丰富的资源。

该系列芯片在功耗控制上表现出色,可满足对低功耗需求较高的应用场景。

Cyclone系列还支持多种外围接口和通信协议,如CAN、SPI、I2C等,方便与其他设备进行通信和互联。

3. Lattice iCE系列Lattice iCE系列是一种超低功耗的FPGA芯片,适用于移动设备和便携式电子产品。

iCE系列采用了极小的封装和低功耗设计,能够在极端环境下提供可靠的性能。

该系列芯片具有快速启动和低功耗特性,适合应用于电池供电的场景。

iCE系列还具有较高的集成度和资源利用率,可满足对系统复杂度和成本要求较高的应用。

4. Intel Stratix系列Intel Stratix系列是一种高性能、高密度的FPGA芯片,由英特尔(Intel)公司推出。

Stratix系列采用了英特尔的最新工艺技术,具有卓越的性能和可靠性。

FPGA可编程逻辑器件芯片XQR4VSX55-10CN1140V中文规格书

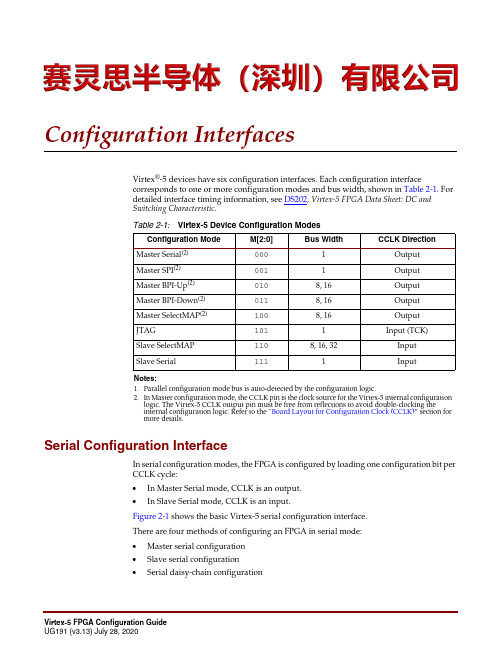

Configuration InterfacesVirtex ®-5 devices have six configuration interfaces. Each configuration interfacecorresponds to one or more configuration modes and bus width, shown in Table 2-1. For detailed interface timing information, see DS202, Virtex-5 FPGA Data Sheet: DC and Switching Characteristic .Serial Configuration InterfaceIn serial configuration modes, the FPGA is configured by loading one configuration bit per CCLK cycle:∙In Master Serial mode, CCLK is an output.∙In Slave Serial mode, CCLK is an input.Figure 2-1 shows the basic Virtex-5 serial configuration interface.There are four methods of configuring an FPGA in serial mode:∙Master serial configuration ∙Slave serial configuration ∙Serial daisy-chain configurationTable 2-1:Virtex-5 Device Configuration ModesConfiguration ModeM[2:0]Bus WidthCCLK DirectionMaster Serial (2)0001Output Master SPI (2)0011Output Master BPI-Up (2)0108, 16Output Master BPI-Down (2)0118, 16Output Master SelectMAP (2)1008, 16Output JTAG1011Input (TCK)Slave SelectMAP 1108, 16, 32Input Slave Serial1111InputNotes:1.Parallel configuration mode bus is auto-detected by the configuration logic.2.In Master configuration mode, the CCLK pin is the clock source for the Virtex-5 internal configuration logic. The Virtex-5 CCLK output pin must be free from reflections to avoid double-clocking theinternal configuration logic. Refer to the “Board Layout for Configuration Clock (CCLK)” section for more details.Chapter 2:Configuration InterfacesParallel Daisy ChainVirtex-5 FPGA configuration supports parallel daisy-chain. Figure 2-12 shows an example schematic of the leading device in BPI mode. The leading device can also be in Master or Slave SelectMAP modes. The D[15:0], CCLK, RDWR_B, PROGRAM_B, DONE, and INIT_B pins share a common connection between all of the devices. The CS_B pins are daisy chained.Notes relevant to Figure 2-12:1.The DONE pin is by default an open-drain output requiring an external pull-up resistor. In this arrangement, the active DONE driver must be disabled.2.The INIT_B pin is a bidirectional, open-drain pin. An external pull-up is required.3.The BitGen startup clock setting must be set for CCLK for SelectMAP configuration.4.The BUSY signals can be left unconnected if readback is not needed.5.The CCLK net requires Thevenin parallel termination. See “Board Layout for Configuration Clock (CCLK).”6.The FCS_B, FWE_B, FOE_B, CSO_B weak pull-up resistors should be enabled,otherwise external pull-up resistors are required for each pin. By default, all dual-mode I/Os have weak pull-downs after configuration.7.The first device in the chain can be Master SelectMAP, Slave SelectMAP, BPI-Up, or BPI-Down.8.Readback in the parallel daisy chain scheme is currently not supported.9.AES decryption is not available in x16 or x32 mode, only in x8 mode.10.Fallback is not supported in parallel daisy-chain.Figure 2-12:Parallel Daisy ChainUG191_c2_14_081910No M[2:0]=S l a ve S electMAPM[2:0]=S l a ve S electMAPSelectMAP Configuration InterfaceGanged SelectMAPIt is also possible to configure simultaneously multiple devices with the same configuration bitstream by using a ganged SelectMAP configuration. In a gangedSelectMAP arrangement, the CS_B pins of two or more devices are connected together (or tied to ground), causing all devices to recognize data presented on the D pins.All devices can be set for Slave SelectMAP mode if an external oscillator is available, or one device can be designated as the Master device, as illustrated in Figure 2-13.Notes relevant to Figure 2-13:1.The DONE pin is by default an open-drain output requiring an external pull-up resistor. In this arrangement, the active DONE driver must be disabled for both devices.2.The INIT_B pin is a bidirectional, open-drain pin. An external pull-up resistor is required.3.The BitGen startup clock setting must be set for CCLK for SelectMAP configuration.4.The BUSY signal is not used for ganged SelectMAP configuration.5.The PROM in this diagram represents one or more Xilinx PROMs. Multiple Xilinx PROMs can be cascaded to increase the overall configurations storage capacity.6.The BIT file must be reformatted into a PROM file before it can be stored on the Xilinx PROM. Refer to the “Generating PROM Files” section.Figure 2-13:Ganged x8 SelectMAP Configuration8080ΩChapter 2:Configuration InterfacesSelectMAP Configuration InterfaceReadback Abort Sequence DescriptionAn ABORT is signaled during readback as follows:1.The readback sequence begins normally.2.The user pulls the RDWR_B pin Low while the device is selected (CS_B asserted Low).3.BUSY goes High if CS_B remains asserted (Low).4.The ABORT ends when CS_B is deasserted.ABORTs during readback are not followed by a status word because the RDWR_B signal is set for write control (FPGA D[x:0] pins are inputs).ABORT Status WordDuring the configuration ABORT sequence, the device drives a status word onto the D[7:0] pins. The status bits do not bit-swap. The other data pins are always High. The key for that status word is given in Table 2-5.Figure 2-17:Configuration Abort Sequence for SelectMAP ModesDA T A[0:7]BU S YCCLKABORTu g191_c2_19_092507C S _B RDWR_BFigure 2-18:Readback Abort SequenceDATA[0:7]BUSYCCLK CS_B RDWR_B。

FPGA芯片结构、工作原理与软核、硬核、固核详解

FPGA芯片结构、工作原理与软核、硬核、固核详解一、FPGA芯片原理FPGA是在PAL、GAL、EPLD、CPLD等可编程器件的基础上进一步发展的产物。

它是作为ASIC领域中的一种半定制电路而出现的,即解决了定制电路的不足,又克服了原有可编程器件门电路有限的缺点。

由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不可能像ASIC那样通过固定的与非门来完成,而只能采用一种易于反复配置的结构。

查找表可以很好地满足这一要求,目前主流FPGA都采用了基于SRAM工艺的查找表结构,也有一些军品和宇航级FPGA采用Flash或者熔丝与反熔丝工艺的查找表结构。

通过烧写文件改变查找表内容的方法来实现对FPGA的重复配置。

根据数字电路的基本知识可以知道,对于一个n输入的逻辑运算,不管是与或非运算还是异或运算等等,最多只可能存在2n 种结果。

所以如果事先将相应的结果存放于一个存贮单元,就相当于实现了与非门电路的功能。

FPGA的原理也是如此,它通过烧写文件去配置查找表的内容,从而在相同的电路情况下实现了不同的逻辑功能。

查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。

目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的的RAM。

当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能结果,并把真值表(即结果)事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

下面给出一个4与门电路的例子来说明LUT实现逻辑功能的原理。

例1-1:给出一个使用LUT实现4输入与门电路的真值表。

表1-1:4输入与门的真值表从中可以看到,LUT具有和逻辑电路相同的功能。

实际上,LUT具有更快的执行速度和更大的规模。

由于基于LUT的FPGA具有很高的集成度,其器件密度从数万门到数千万门不等,可以完成极其复杂的时序与逻辑组合逻辑电路功能,所以适用于高速、高密度的高端数字逻辑电路设计领域。

FPGA比CPU和GPU快的原理是什么

FPGA比CPU和GPU快的原理是什么FPGA原理FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输入输出模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构。

FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。

FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

FPGA比CPU和GPU快的原理是什么CPU和GPU都属于冯·诺依曼结构,指令译码执行,共享内存。

FPGA之所以比CPU、GPU更快,本质上是因为其无指令,无共享内存的体系结构所决定的。

冯氏结构中,由于执行单元可能执行任意指令,就需要有指令存储器、译码器、各种指令的运算器、分支跳转处理逻辑。

而FPGA的每个逻辑单元的功能在重编程时就已经确定,不需要指令。

冯氏结构中使用内存有两种作用:①保存状态。

②执行单元间的通信。

FPGA芯片设计在数字电路实现方面的利与弊

FPGA芯片设计在数字电路实现方面的利与弊FPGA(Field-Programmable Gate Array)芯片是一种可重新配置的数字逻辑芯片,它通过可编程的逻辑单元和可编程的连接资源,可以根据设计者的需求定制功能。

FPGA芯片设计在数字电路实现方面具有许多优点和一些不足之处。

本文将探讨FPGA芯片设计的利与弊。

首先,FPGA芯片设计具有许多优点。

一方面,FPGA芯片设计提供了灵活性和可定制性。

与单一功能固定的ASIC(Application-Specific Integrated Circuit)相比,FPGA芯片可以根据不同的需求编程和重新配置。

这种可定制性使得FPGA芯片在快速原型开发和快速产品迭代方面具有巨大优势。

设计师可以根据需要定制功能模块,减少设计周期和成本。

其次,FPGA芯片设计能够提供高性能和高灵敏度。

FPGA芯片由大量的逻辑资源组成,并可以并行执行多个任务。

这种并行性使得FPGA芯片能够在处理大规模数据和复杂计算任务时发挥出色的性能优势。

另外,FPGA芯片设计通常具有低延迟和高速度的特点,可以满足实时性要求较高的应用。

第三,FPGA芯片设计提供了良好的可靠性和可维护性。

由于FPGA芯片是可重新配置的,当出现设计错误或功能改变时,可以轻松地进行修正或更新。

这种可维护性使得FPGA芯片在长期使用和维护方面具有优势。

而且,由于FPGA芯片是用可编程语言(如VHDL和Verilog)进行设计的,设计文档完备,易于阅读和理解,有助于后续维护工作的顺利进行。

然而,FPGA芯片设计也存在一些不足之处。

首先,相对于专用定制的硬件设计,FPGA芯片在功耗和面积上通常会有一定的损耗。

由于FPGA芯片需要包含大量的逻辑资源和可编程连接,其功耗和尺寸通常会较大。

这在某些应用场景中可能会受到限制。

其次,FPGA芯片设计的开发和调试相对复杂。

与传统的软件开发和ASIC设计相比,FPGA芯片的可编程性意味着设计过程的复杂性增加了许多。

DSP、MCU、CPLD、ARM、FPGA芯片的区别

DSP、MCU、CPLD、ARM、FPGA芯片的区别1,单片机小型电脑处理器,最小可以到8个脚,价格便宜,最便宜2块钱2,PLC可变逻辑控制器,主要用在工业控制,里面是类似一个加强的单片机。

对输入输出均有做处理(抗干扰能力、带负载能力都增强).例如抗干扰,增加带负载驱动能力3,DSP 数字信号处理芯片,这个用途可做信号处理,例如图像处理,数据采集处理,它比单片要快很多,比单片机功能要强大4,FPGA、CPLD可变逻辑控制,这个做逻辑处理控制,小型的CPLD是没有中央处理器的,大型可以嵌入系统,功能在单片机之上,适合做大型的数据处理,逻辑控制。

其价格不便宜。

但是他和单片机有本质的区别。

例如单片机有内嵌外设AD,DA转换等,CPLD则需要通过控制其他外设IC。

要想诠释清楚,也非三言两语能道明,还是多看看书本吧学习可以以单片机为先,其次是FPGA,CPLD,DSP。

PLC比较简单,学会前面后面只要了解一周一般都会了一家之言,欢迎指证:DSP:数字信号处理器,处理器采用哈弗结构,工作频率较高,能大幅度提高数字信号处理算法的执行效率。

MCU:微控制器,主要用于控制系统,工作频率一般来说比DSP低,硬件上具有多个IO端口,同时也集成了多个外设,主要是便于在控制系统中的应用。

至于ARM处理器,个人认为是MCU的高级版本,ARM本身只是一个内核,目前已经有多个版本。

CPLD:复杂可编程逻辑器件FPGA:现场可编程门阵列后两者都是可编程器件,CPLD目前一半采用FLASH技术,而FPGA采用SRAM技术,这就决定了FPGA需要采用特定的配置技术。

同时FPGA的规模要比CPLD大得多,但CPLD应用起来相对要简单的多.DSP主要用做运算,如语音,图像等信号的运算处理,但基本不用做控制.MCU,FPGA,ARM主要用做控制,MCU低价低功耗,但门限很少,结构简单,不能实现复杂控制.ARM控制能力较强,但运算能力相对较弱。

fpga与cpu的比较

fpga与cpu的比较悬赏分:0 - 解决时间:2007-10-15 19:33提问者:左岸右转117 - 四级最佳答案fpga是现场可编程门阵列,内部以LUT查找表为核心。

用户买来的fpga一般是一块空的芯片,不具备任何功能。

用户可以使用多种方法(如编程、原理图等)将fpga配置成具有特定功能的专用芯片。

而cpu指的是具有计算和控制功能的中央处理器。

显然fpga可以由用户配置成一块cpu,这一过程相对比较复杂,fpga更多用来配置成具有比较简单功能的专用芯片。

现在一些pld公司提供一些编好程序。

把程序下载到fpga中就可以实现cpu的功能,例如Altera公司的NIOS II,这就是通常所说的具有CPU功能的软核。

我来说说吧CPU是一种比较复杂的数字逻辑器件,按照厂家预先设定的方式,按顺序读取指令、执行指令。

DSP其实也可以成是CPU,不过和CPU不同,DSP内部具有多个线程,具备一定的并行能力,此外DSP通常还具有专用的运算电路, CPU需要很多时钟周期才能搞定的事情,DSP利用专门电路很快能搞定。

FPGA是一个通用可编程的逻辑器件,可以用FPGA来是实现各种数字逻辑(个别具有特意功能的FPGA具备混合信号处理能力,搭载有片上ADC),CPU和通用DSP也是数字逻辑,所以只要FPGA的片上资源够多(足够的逻辑单元、布线单元、时钟、片上内存等等),就可以用FPGA实现CPU和通用DSP。

CPLD其实和FPGA很像,历史的原因,是先有CPLD后有FPGA,一般来说FPGA具有更细致划分的逻辑单元,更多的片上资源。

ASIC是专用集成电路,是为专门目的而设计集成电路,非通用型。

所以不能泛泛描述它的功能。

通常可以认为FPGA流片后的芯片就算是ASIC了。

FPGA/CPLD能做什么呢?可以毫不夸张的讲,FPGA/CPLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用FPGA/CPLD来实现。

国产fpga芯片

国产fpga芯片FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,其核心是一个由大量可编程逻辑单元(CLB)和可编程互连设置组成的网状结构。

随着信息技术的不断发展,FPGA芯片作为一种高度灵活的芯片方案,逐渐得到了广泛应用。

在国内,由于对于自主可控的需求和对于芯片封装技术的逐渐提升,自主研发生产FPGA芯片已经成为国内芯片产业的一个重要方向。

国产FPGA芯片的研发生产具有以下几个显著特点:1. 自主可控:国内自主研发生产的FPGA芯片具有自主产权,不仅能够满足国内市场的需求,还可以提供可靠的技术支持和服务。

这对于满足国内高安全性和可靠性的应用领域是非常重要的。

2. 低功耗高性能:国产FPGA芯片在研发过程中注重了功耗控制和性能优化。

通过采用先进的工艺和优化的架构设计,国产FPGA芯片在保持较高计算性能的同时,能够在功耗方面有所降低,提高能效。

3. 丰富的外设接口:为了适应不同应用领域的需求,国产FPGA芯片在硬件设计上提供了丰富的外设接口。

这些接口可以与其他硬件设备进行通信,满足各种复杂的应用场景。

4. 丰富的软件开发支持:国产FPGA芯片提供了完善的软件开发支持,包括开发环境、开发工具和开发文档等。

这使得开发人员可以更加方便地进行FPGA应用的开发和调试。

5. 广泛的应用领域:国产FPGA芯片广泛应用于通信、计算、工业控制、军事电子等领域。

其灵活的编程能力和强大的计算能力使得FPGA芯片在这些领域中具有很大的优势。

虽然国产FPGA芯片在研发和生产方面取得了一定的成就,但与国际知名厂商相比,还存在一些差距。

这主要体现在技术水平、市场份额和品牌影响力等方面。

对于国内FPGA芯片产业的进一步发展,需要加大研发投入,提高技术创新能力,扩大市场份额,并积极参与国际市场竞争,争取更大的发展空间。

综上所述,国产FPGA芯片在技术创新和市场应用方面具有一定的优势和潜力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA芯片选型比较

Cyclone III的EP3CE10采用了60nm制造工艺,是一款功耗很低、成本很低且高性能的FPGA。

Cyclone IV的 EP4CE10也采用了60nm制造工艺,是一款新的产品。

该器件实现了低成本、高性能和低功耗,在手持式软件无线电等低功耗应用中,其功耗比以前的Cyclone产品低25%。

同样,Spartan-3E FPGA系列的XC3S500E芯片采用了90nm制造工艺技术生产。

其单位逻辑单元的成本是FPGA行业中相当低的。

它的低成本也是非常的吸引人。

现将三种产品的相关参数比较如下:

以下是Cyclone 的FAE对Cyclone IV 与Spartan 6 的比较表格,因为Spartan 6比Spartan 3高一个级别,所以这个比较有一定的参考性。

FAE也总结了Cyclone系列在技术上的的优势

1,CycloneIV/III的最高频率高于Spatarn3、Spartn6系列, 性能明显要好,(可以在QuartusII和ISE中验证比较同一程序)

2,CycloneIV/III的功耗略低于Spatarn3、Spartn6,当然,差距不是特别大

3,开发软件方面,QuartusII的编译时间明显比ISE短,界面上更加方便使用

4, CycloneIV/III市场占有率一直高于Spatarn3、Spartn6

5, Altera的CycloneIV和Xilinx的Spartan6都是新器件,很多客户都关心供货情况。

由于CycloneIV和CylconeIII可以做到兼容(只有3个管脚不同,在设计时略加处理,就可以做到兼容设计),如果CycloneIV供货有问题,可以用CylconeIII直接替代,而Xilinx Spartan6很多器件还没量产,也没有兼容型号,一旦出现供货问题,很难处理。

当然这些很多是Altera单方面的解释,他这款CycloneIV的供货问题也是存在的。

具体要等两天xilinx他们的工业级芯片报价出来再做价格比较,因为从整个FPGA市场占有率来说xilinx肯定有他们拥有很大市场占有率的道理。