DSP汇编指令学习笔记

DSP汇编指令学习笔记

Knowledge问题谁在DSP的汇编语言中加入了NOP指令?NOP指令加入的条件是什么?About DSP1.DSP是实时数字信号处理的核心和标志。

2.DSP分为专用和通用两种类型。

专用DSP一般采用定点数据结构(一般不支持小数),数据结构简单,处理速度快;通用DSP灵活性好,但是处理速度有所降低。

3.DSP采用取指、译码、执行三个阶段的流水线(Pipeline)技术,缩短了执行时间,提高了运行速率。

DSP具有8个Functional unit,如果并行处理的话,以600MHz的时钟计算,如果执行的指令是single cycle指令,则可以4800MIPS(指令每秒)。

4.DSP的8个functional Unit,具有独特的功能,对滤波、矩阵运算、FFT(傅里叶变换)具有哈弗结构把指令空间与数据空间隔离的存储方式。

这样实现是为了实现指令的连续读取,而实现pipeline流水线结构。

传统哈弗结构:两个独立的存储空间,还使用独立总线。

让取指与执行存储独立,加快执行速度。

改进型哈弗结构:指令与数据的存储空间还是独立的。

但是使用公共的总线(地址总线与数据总线)。

这样实现的原因是因为出现了CACHE,数据的存储动作大部分被内部的CACHE 总线承接了,所以总线冲突的情况会大大减少。

同时让总线的结构与控制变得简单,CACHE 存储的速度也明显快于外设存储器。

冯诺依曼结构:是指令空间与数据空间共享的存放方式。

它不能实现pipeline的执行过程。

Pipeline(流水线)技术是把指令的取指-译码和指令的执行独立开来的技术。

虽然每条指令的过程还是要经过取指-译码-执行三个阶段最少3个CPU Cycle。

但是多个指令同时并行先后进行,保证总体的指令吞吐速率理想情况下可以保证在每个指令只要一个CPU CYCLE。

Pipeline技术必须要有哈弗结构支持,即必须把指令空间与数据空间隔离存放。

流水线阻断流水线中阻断现象也十分普遍,下面就各种阻断情况下的流水线性能进行详细分析。

第五章 DSP的汇编指令..

第五章 TMS320C55x系列DSP的汇编指令

(2) 用户自定义的双指令的并行

这两条指令的并行是通过用户或C编译器定义的。两条指令 同时执行两个操作,用并行符“||”区分并行执行的两条指令。 例:

MPYM *AR1+, *CDP, AC1 ;D单元的一个MAC来完成

||XOR AR2,T1

;A单元的ALU来完成

第五章 TMS320C55x系列DSP的汇编指令

1、高速数字信号处理中常采用汇编语言编程。 2、汇编语言中的两种指令集 (1) 助记符指令集:有助于记忆的符号来表示指令。 (2) 代数指令集:类似于代数表达式,运算关系清楚明了。 注意:DSP的软件开发工具只支持单一的指令形式,不支持助记

符指令和代数指令的混合形式。 3、术语、符号和缩写见P93的表5-1 4、运算符见表5-2

令执行的条件:

TCx(测试/控制标志为1) !TCx(测试/控制标志为0)

TC1&TC2 TC1&!TC2 TC1|TC2 TC1|!TC2 TC1^TC2 TC1^!TC2

!TC1&TC2 !TC1&!TC2 !TC1|TC2 !TC1|!TC2 !TC1^TC2 !TC1^!TC2

第五章 TMS320C55x系列DSP的汇编指令

4、双16比特算术指令: [(1)语法、(2)操作数、(3)状态位] 在D单元中利用其ALU的双16比特模式,同时执行(并行)两个16

比特算术运算,包括加-减、减-加、两个加和两个减运算。

例:

说明: NO:不能并行执行 3:指令的长度为3字节 1:周期为1 X:在X(执行)流水线阶段处理

D – ALU:在D单元ALU执行。 执行结果:AC0=(*AR3)+CARRY+AC1 状态位: Affected by CARRY,C54CM,M40等

第五章 DSP的汇编指令..

令执行的条件:

TCx(测试/控制标志为1) !TCx(测试/控制标志为0)

TC1&TC2 TC1&!TC2 TC1|TC2 TC1|!TC2 TC1^TC2 TC1^!TC2

!TC1&TC2 !TC1&!TC2 !TC1|TC2 !TC1|!TC2 !TC1^TC2 !TC1^!TC2

第五章 TMS320C55x系列DSP的汇编指令

4、双16比特算术指令: [(1)语法、(2)操作数、(3)状态位] 在D单元中利用其ALU的双16比特模式,同时执行(并行)两个16

比特算术运算,包括加-减、减-加、两个加和两个减运算。

例:

▪ M40=0时,D单元按32位运算模式,因此累加器溢出、进位、符号扩

展和移位操作都以第31比特为准。

▪ M40=1时,D单元按40位运算模式,因此累加器溢出,进位,符号扩

展和移位操作都以第39比特为准。

BCLR M40 ; Clear M40

BSET M40 ; Set M40

第五章 TMS320C55x系列DSP的汇编指令

第五章 TMS320C55x系列DSP的汇编指令

一、算术运算指令 用于完成加减乘除等运算,按照功能可分成以下几类:

▪ 加法指令 ▪ 减法指令:减法,条件减法,条件加/减 ▪ 乘法指令:乘法,乘加,乘减,双乘加/减 ▪ 双16比特算术指令 ▪ 比较运算指令:比较并求极值,最大/最小值,存储单元比较,寄存器比较 ▪ 移位指令:条件移位、带符号的移位。 ▪ 寄存器修改:辅助寄存器修改、堆栈指针SP修改 ▪ 隐含的并行指令 ▪ 专用指令:绝对值、归一化、有限冲激响应滤波FIR、最小均方LMS等

✓ M40=0时: 溢出位在第31位检测

Dsp学习笔记

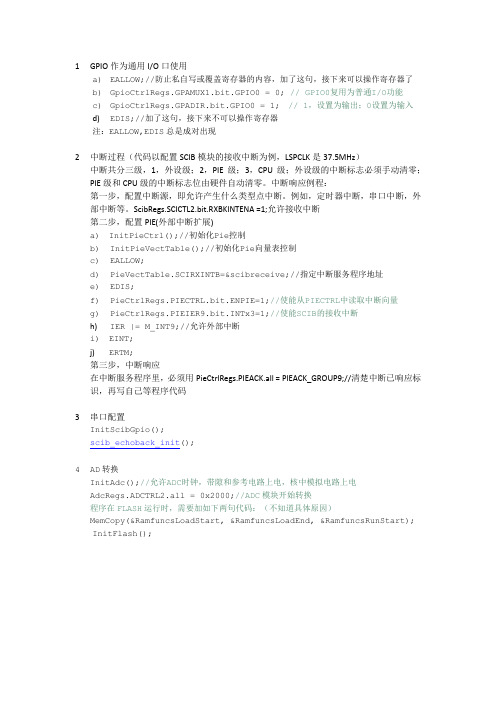

1GPIO作为通用I/O口使用a)EALLOW;//防止私自写或覆盖寄存器的内容,加了这句,接下来可以操作寄存器了b)GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 0; // GPIO0复用为普通I/O功能c)GpioCtrlRegs.GPADIR.bit.GPIO0 = 1; // 1,设置为输出;0设置为输入d)EDIS;//加了这句,接下来不可以操作寄存器注:EALLOW,EDIS总是成对出现2中断过程(代码以配置SCIB模块的接收中断为例,LSPCLK是37.5MHz)中断共分三级,1,外设级;2,PIE级;3,CPU级;外设级的中断标志必须手动清零;PIE级和CPU级的中断标志位由硬件自动清零。

中断响应例程:第一步,配置中断源,即允许产生什么类型点中断。

例如,定时器中断,串口中断,外部中断等。

ScibRegs.SCICTL2.bit.RXBKINTENA =1;允许接收中断第二步,配置PIE(外部中断扩展)a) InitPieCtrl();//初始化Pie控制b) InitPieVectTable();//初始化Pie向量表控制c) EALLOW;d) PieVectTable.SCIRXINTB=&scibreceive;//指定中断服务程序地址e) EDIS;f) PieCtrlRegs.PIECTRL.bit.ENPIE=1;//使能从PIECTRL中读取中断向量g) PieCtrlRegs.PIEIER9.bit.INTx3=1;//使能SCIB的接收中断h) IER |= M_INT9;//允许外部中断i) EINT;j) ERTM;第三步,中断响应在中断服务程序里,必须用PieCtrlRegs.PIEACK.all = PIEACK_GROUP9;//清楚中断已响应标识,再写自己等程序代码3串口配置InitScibGpio();scib_echoback_init();4AD转换InitAdc();//允许ADC时钟,带隙和参考电路上电,核中模拟电路上电AdcRegs.ADCTRL2.all = 0x2000;//ADC模块开始转换程序在FLASH运行时,需要加如下两句代码:(不知道具体原因)MemCopy(&RamfuncsLoadStart, &RamfuncsLoadEnd, &RamfuncsRunStart);InitFlash();。

DSP常用汇编语言指令简介

南航自动化学院DSP技术应用实验 室

6. I/O与存储器等指令举例

z Example1:IN 7,1000h ;(DP=6)从地址为1000H 的外部端口读入数据,盛放在地址为307h的数 据单元内。类似的指令还有:OUT。

LAR AR0, #60h

;AR0内容赋值为60h

ZAC

; 累加器ACC清零

loop: ADD *+, AR1 ;把当前工作寄存器AR0指向 的内存单元数值加到ACC,然后AR0内容加1,当前工 作寄存器指针指向AR1

BANZ loop, *-AR0 ;判断AR0是否为0,否则程序 转到loop,同时AR0的内容减1。

3. TREG(暂存单元指令),PREG(乘积单元指 令),multiply instructions (乘积指令)

4. Branch instructions (程序分支转移指令) 5. Control instructions (控制指令) 6. I/O and memory instruction(I/O和存储器指令)

室

2. 工作寄存器等指令举例

z Example1:MAR *+,AR1;把当前工作寄 存器的内容加1,然后再改变工作寄存器为 AR1。

z Example2:LAR AR4,#8123h;把AR4的 值改变为立即数。

LAR AR0,16;(DP=6)把 地址=310H的内存单元内容装入AR0。

z Example3:SAR AR0,*+;(如果当前工 作寄存器=AR1)把AR0的内容拷贝到AR1 指向的内存单元。 南航自动化学院DSP技术应用实验

DSP各种知识点总结

1 DSP芯片的特点:(1).哈佛结构(程序空间和数据空间分开)(2).多总线结构.(3)流水线结构(取指、译码、译码、寻址、读数、执行)(4)多处理单元. (5)特殊的DSP指令(6).指令周期短. (7)运算精度高.(8)硬件配置强.(9)DSP最重要的特点:特殊的内部结构、强大的信息处理能力及较高的运行速度。

2 三类TMS320:(1)TMS320C2000适用于控制领域(2)TMS320C5000应用于通信领域(3)TMS320C6000应用于图像处理3 DSP总线结构:C54x片内有8条16位主总线:4条程序/数据总线和4条对应的地址总线。

1条程序总线(PB):传送自程序储存器的指令代码和立即操作数。

3条数据总线(CB、DB、EB):CB和EB传送从数据存储器读出的操作数;EB传送写到存储器中的数据。

4条地址总线(PAB、CAB、DAB、EAB)传送相应指令所需要的代码4存储器的分类:64k字的程序存储空间、64K字的数据存储空间和64K字的I/O空间(执行4次存储器操作、1次取指、2次读操作数和一次写操作数。

5存储器空间分配片内存储器的形式有DARAM、SARAM、ROM 。

RAM安排到数据存储空间、ROM构成程序存储空间。

(1)程序空间:MP/MC=1 40000H~FFFFH 片外MP/MC=0 4000H~EDDDH 片外FF00H~FFFFH 片内OVL Y=1 0000H~007FH 保留0080H~007FH 片内OVL Y=0 0000H~3FFFH片外(2)数据空间:DROM=1 F000H~F3FFH 只读空间FF00H~FFFH保留DROM=0 F000H~FEFFH 片外6数据寻址方式(1)立即寻址(2)绝对寻址<两位>(3)累加器寻址(4)直接寻址@<包换数据存储器地址的低7位>优点:每条指令只需一个字(5)间接寻址*按照存放某个辅助寄存器中的16位地址寻址的AR0~AR7(7)储存器映像寄存器寻址(8)堆栈寻址7寻址缩写语Smem:16位单寻址操作数Xmem Ymem 16位双dmad pmad PA16位立即数(0-65535)scr源累加器dst目的累加器lk 16位长立即数8状态寄存器ST0 15~13ARP辅助寄存器指针12TC测试标志位11C进位位10累积起A 的一出标志位OV A 9OVB 8~0DP数据存储器页指针9状态寄存器ST1 CPL:直接寻址编辑方式INTM =0开放全部可屏蔽中断=1关闭C16 双16位算数运算方式10定点DSP 浮点DSP:定点DSP能直接进行浮点运算,一次完成是用硬件完成的,而浮点需要程序辅助。

DSP(知识点+思考题)

DSP复习要点第一章绪论1、数的定标:Qn表示。

例如:16进制数2000H=8192,用Q0表示16进制数2000H=0.25,用Q15表示2、‟C54x小数的表示方法:采用2的补码小数;.word 32768 *707/10003、定点算术运算:乘法:解决冗余符号位的办法是在程序中设定状态寄存器STl中的FRCT位为1,让相乘的结果自动左移1位。

第二章CPU结构和存储器设置一、思考题:1、C54x DSP的总线结构有哪些特点?答:TMS320C54x的结构是围绕8组16bit总线建立的。

(1)、一组程序总线(PB):传送从程序存储器的指令代码和立即数。

(2)、三组数据总线(CB,DB和EB):连接各种元器件,(3)、四组地址总线(PAB,CAB,DAB和EAB)传送执行指令所需要的地址。

2、C54x DSP的CPU包括哪些单元?答:'C54X 芯片的CPU包括:(1)、40bit的算术逻辑单元(2)、累加器A和B(3)、桶形移位寄存器(4)、乘法器/加法器单元(5)、比较选择和存储单元(6)、指数编码器(7)、CPU状态和控制寄存器(8)、寻址单元。

1)、累加器A和B分为三部分:保护位、高位字、地位字。

保护位保存多余高位,防止溢出。

2)、桶形移位寄存器:将输入数据进行0~31bits的左移(正值)和0~15bits的右移(负值)3)、乘法器/加法器单元:能够在一个周期内完成一次17*17bit的乘法和一次40位的加法4)、比较选择和存储单元:用维比特算法设计的进行加法/比较/选择运算。

5)、CPU状态和控制寄存器:状态寄存器ST0和ST1,由置位指令SSBX和复位指令RSBX控制、处理器模式状态寄存器PMST2-3、简述’C54x DSP的ST1,ST0,PMST的主要功能。

答:’C54x DSP的ST1,ST0,PMST的主要功能是用于设置和查看CPU的工作状态。

•ST0主要反映处理器的寻址要求和计算机的运行状态。

dsp汇编指令

dsp中的汇编伪指令伪指令分类伪指令及其表示格式具体描述段定义伪指令 .asect “段名” , 地址汇编到一以绝对地址为起始的段中.bss 符号,字数[,块标号] 在未初始化数据段bss中保留空间.data 汇编到已初始化数据段data中.sect “段名”汇编到一已命名(已初始化)的段中.text 汇编到可执行代码段text中符号 .usect “段名”,字数[,块标号] 在一已命名(未初始化)的段中保留空间常数初始化伪指令(包括数据和地址常数) .bes 位数在当前段中保留位数(标号指向所保留空间的尾部).bfloat 数值初始化一个32位,IEEE单精度的浮点常数;禁止有跨页的初始化对象。

.blong 数值1[,…,数值n] 初始化一个或多个32位整数;禁止有跨页的初始化对象。

.byte 数值1[,…,数值n] 初始化当前段中一个或多个连续字节.field 数值1[,…,数值n] 初始化一个可变长度的字段.float 数值初始化一个32位,IEEE单精度的浮点常数.int 数值1[,…,数值n] 初始化一个或多个16位整数.long 数值1[,…,数值n] 初始化一个或多个32位整数.space 位数在当前段中保留位数(标号指向所保留空间的头部).string “字符串1”[,…,“字符串n”] 初始化一个或多个文本字符串.word 数值1[,…,数值n] 初始化一个或多个16位整数对准段程序计数器的伪指令 .align 在一页的边缘对准SPC(段程序计数器).even 在一偶数的边缘对准SPC定义输出列表格式的伪指令 .drlist 使所有伪指令行都被列出(缺省方式).drnolist 禁止某些伪指令行的列出.fclist 允许列出错误的条件代码块(缺省方式).fcnolist 禁止列出错误的条件代码块.length 页的长度定义源文件列表的页长.list 从头开始源文件的列表.mlist 允许宏列表和循环块(缺省方式).mnolist 禁止宏列表和循环块定义输出列表格式的伪指令 .nolist 停止源文件列表.option{B/D/F/L/M/T/X} 选择输出列表文件的参数.page 在源文件列表中生成一页.sslist 允许扩展子程序符号列表.ssnolist 禁止扩展子程序符号列表(缺省方式).tab 大小设置表的大小.title “字符串”在列表页头显示一个标题.width 页宽设置源文件列表的页宽外部文件定位的指伪令 .copy [“]文件名[”] 包含其他文件中的源语句.def 符号1[,…,符号n] 标明一个或多个在当前模块中定义而在其他模块中要用到的符号.global 符号1[,…,符号n] 标明一个或多个全局(外部)符号.include [“]文件名[”] 包含其他文件中的源语句.mlib [“]文件名[”] 定义宏定义库.ref符号1[,…,符号n] 标明一个或多个在另一模块中定义而在当前模块中要用到的符号条件汇编伪指令.break [确切定义的表达式] 如果条件满足,就结束.loop汇编。

DSP实验报告 基本指令操作

实验二基本指令操作周二第三大节一实验目的(1)了解DSP数据表示格式(2)了解DSP汇编语言的编写格式(3)了解DSP配置文件的编写(4)了解DSP汇编与C混合编写的方法二实验内容1、css下的汇编语言实现2、css下的C语言与汇编语言混合编程三、实验过程例1 用汇编语言实现乘积累加的运算,y=∑(Ai*Xi)把data段的40个数据移动到bss段的a和x中,每个分别存放20个数据,然后分别取出a和x中位置相对应的一些数据,用块循环的方法完成数据的乘积和累加的运算。

最后结果保存在y中。

.title "asm.asm".mmregs.bss a,20.bss x,20.bss y,2STACK .usect "STACK",30.datatable: .word 1,2,3,4,5,6,7,8,9,10,11,12.word 13,14,15,16,17,18,19,20.word 1,2,3,4,5,26,27,28,29,30.word 1,2,3,4,5,6,7,8,9,10.def start.textstart: STM #a,AR1RPT #39MVPD table,*AR1+LD #0,BSTM #a,AR2STM #x,AR3STM #y,ar5STM #4,BRCRPTB done-1LD *AR2+,TMPY *AR3+,AADD A,Bdone: STH B,*ar5+STL B,*ar5end: b end.end相应的配置文件为:-e startMEMORY{PAGE 0:EPROM: org=0100H,len=1000H PAGE 1:SRAM org=02000H,len=1000H }SECTIONS{.text :> EPROM PAGE 0.data :> EPROM PAGE 0.bss :> SRAM PAGE 1.STACK :> SRAM PAGE 1}运行后,Memory下的结果例2 汇编程序和C程序混合编程的方法在一个工程中分别包含汇编源程序和C源程序,实现相互之间函数和变量的调用。

DSP笔记

R4.3 软件开发语言(1)汇编语言高效指令,代码效率高,底层控制灵活,实时性好;指令集掌握困难,程序可读性,可维护性可移植性差,流程控制困难,开发周期长;适用于运算量大、实时性要求高的场合。

(2)C语言程序可读性、可维护性、可移植性好,修改、升级方便,流程控制容易,开发周期短;某些硬件控制不便,实时性不好;适用于运算量小,实时性要求不高的场合。

(3)汇编与C混合编程。

综合利用两种语言的优越性,用C语言实现流程控制,用汇编语言实现时序或效率要求严格的核心程序。

三者各有所长,技术的发展使得DSP、通用计算机、单片机相互借鉴对方的优点,互相取长补短。

现在,PC机及部分单片机内部都有硬件乘法器;单片机内部也有了通用计算机和DSP内部才有的流水线作业(但规模小些);而DSP内部也有了一定规模的高速缓存。

吸收Intel的嵌入式系统芯片和系统软件的优点。

有的DSP内部集成了高速运行的的DSP内核及控制功能丰富的嵌入式处理器内核。

例如,内部集成有TI公司的C54xCPU内核和ARM公司的ARM7TDMIE内核的DSP,既具有高速的数据处理能力,又有各种类型的外设接口和位控能力,大大拓宽DSP在控制领域的应用。

DSP在注重高速的同时,也在发展自己的低价位控制芯片。

美国Cygnal公司的C8051F020 8位单片机,内部采用流水线结构,大部分指令的完成时间为1或2个时钟周期,峰值处理能力为25MIPS。

片上集成有8通道A/D,两路D/A,两路电压比较器,内置温度传感器、定时器、可编程数字交叉开关和64个通用I/O口、电源监测、看门狗、多种类型的串行总线(两个UART、SPI等)。

DSP工程工程是指编译dsp程序时的结构。

所有第VisualDSP++的开发都出现在工程内,工程文件(.DPJ)存储着程序的编译信息。

工程开发工程开发的步骤一个典型的工程包括模拟、评估、仿真3个阶段。

模拟:在没有真正的硬件支持的条件下也可以编译、编辑和调试DSP程序。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Knowledge问题谁在DSP的汇编语言中加入了NOP指令?NOP指令加入的条件是什么?About DSP1.DSP是实时数字信号处理的核心和标志。

2.DSP分为专用和通用两种类型。

专用DSP一般采用定点数据结构(一般不支持小数),数据结构简单,处理速度快;通用DSP灵活性好,但是处理速度有所降低。

3.DSP采用取指、译码、执行三个阶段的流水线(Pipeline)技术,缩短了执行时间,提高了运行速率。

DSP具有8个Functional unit,如果并行处理的话,以600MHz的时钟计算,如果执行的指令是single cycle指令,则可以4800MIPS(指令每秒)。

4.DSP的8个functional Unit,具有独特的功能,对滤波、矩阵运算、FFT(傅里叶变换)具有哈弗结构把指令空间与数据空间隔离的存储方式。

这样实现是为了实现指令的连续读取,而实现pipeline流水线结构。

传统哈弗结构:两个独立的存储空间,还使用独立总线。

让取指与执行存储独立,加快执行速度。

改进型哈弗结构:指令与数据的存储空间还是独立的。

但是使用公共的总线(地址总线与数据总线)。

这样实现的原因是因为出现了CACHE,数据的存储动作大部分被内部的CACHE 总线承接了,所以总线冲突的情况会大大减少。

同时让总线的结构与控制变得简单,CACHE 存储的速度也明显快于外设存储器。

冯诺依曼结构:是指令空间与数据空间共享的存放方式。

它不能实现pipeline的执行过程。

Pipeline(流水线)技术是把指令的取指-译码和指令的执行独立开来的技术。

虽然每条指令的过程还是要经过取指-译码-执行三个阶段最少3个CPU Cycle。

但是多个指令同时并行先后进行,保证总体的指令吞吐速率理想情况下可以保证在每个指令只要一个CPU CYCLE。

Pipeline技术必须要有哈弗结构支持,即必须把指令空间与数据空间隔离存放。

流水线阻断流水线中阻断现象也十分普遍,下面就各种阻断情况下的流水线性能进行详细分析。

流水线阻断总体有两种情况:1.资源冲突阻断:a)如果前一指令的某Stage与后一指令某Stage在同一个Cycle执行,但是前一指令此Stage占用了后一指此Stage的资源,则后一指令此Stage的工作会被延迟执行。

b)被延迟执行的动作会停留在前一个Stage状态,则前一个Stage的状态就不能进入新的指令的动作。

c)依次前推,则总有一个取指Stage的指令被阻断,那么其后一个指令也被阻断而不能被取指。

d)所以,每产生一个Cycle的阻断,就会让CPU的执行延迟一个Cycle。

即此指令后面的所有指令都会被延迟一个Cycle被执行。

e)解决的方法是:使用Cache让存放变得更快;变量集群使用,记录减少变量存放到memory的需要。

2.跳转阻断:a)跳转阻断有很多情况产生,比如函数调用/返回,循环的break/continue,if等条件判断,循环跳转,中断跳转的产生。

b)一旦某条指令要进行跳转时,它就会设置LR寄存器,阻止后续的指令进入执行Stage,并修改PC指针,执行跳转后的目标代码。

c)解决的方法是:减少循环、条件判断、分支结构的使用。

DSP Pipeline技术DSP具有8个独立的执行单元,所以每个CYCLE可以执行8条指令(要求其总线宽度是256bit)。

即DSP是8个pipeline并行处理的技术。

所以DSP每个阶段取8个指令,然后在译码阶段把8个指令分配到8个执行单元去处理。

所以必须保证被同时取的指令之间没有相关性(即一个指令的执行不需要其他指令的结果参与),否则会得到错误的结果。

所以,DSP引入了NOP指令,如果不能实现这一的要求,则DSP的编译器,则DSP优化器会在其编译的指令后面添加NOP指令。

表示此Cycle不能执行8条有效指令,只能擦入空指令。

则这样就会有某些执行单元在此CYCLE空闲了。

DSP Pipeline阻断DSP Pipleline的阻断处理相对比较复杂一些,因为它涉及到8独立执行单元的阻断。

1.资源冲突阻断:a)如果某个Unit因为资源冲突阻断,或者因为一个指令需要多个Cycle执行。

则此Unit会被阻断。

b)当某个Unit被阻断时,其上一个阶段的指令就不能往下传递。

一直阻断到此Unit的取值动作。

c)所以当有阻断发生是,FG并不会请求8条指令,而是请求1-7条,或者不请求(8个Unit全部阻断了)。

这样没有被阻断的Unit还是能够充分运行的。

2.跳转阻断:/p-908395009795.htmla)NOPNot dispatched instructionIt is an empty instruction in DP packet.如果一个指令标识需要Delay N个slot,则需要在这个指令后面跟N个NOP指令(对于那些自身不带NOP的指令,比如B)(但是对于BNOP则不需要的)。

通过寄存器的定位技巧1.查看NRP寄存器的值,则可以直接查看在哪个周期的指令异常了(NRP指令的前一周期就是crash的指令)(使用A10/B10……可以看到此函数的参数)2.查看B3寄存器的值,跳到此代码段查看前面一个的Jump指令。

看是jump到哪个函数了,则是在此函数中出异常了。

则可以看到是谁调用的此crash的函数。

(使用A4/B4……可以看到parent的参数)3.如果参数是二维指针,则此参数所在类存一般都是栈内的某个地址。

(可以根据栈空间的特点知道具体应该是哪个地址)CPU data path & control说明:1.Register A也是由两片寄存器组组成的,A0:A1/ … /A30:A31的pair是分布在两个组片中的2.ST path是把寄存器的值写入内存的路径3.LD path是把内存的值加载到寄存器中的路径4.DA path是读写寄存器的路径5.X path是跨组读写寄存器的路径A &B path general purpose registers1.Each A & B path has 32 32-bit register, named A0-A31, B0-B31.2.It supports 40bit & 64bit value. If value is larger than 32 bit, it needsregister-pair. The 32LSB stores in even-numbered register, such A0, and the 8 or 32 MSB stores in odd-numbered register, such A1.3.General purpose registers can be used for data, address pointers,condition registers.8 functional units1.8 functional units can be divided into 2 groups, G1: L1, S1, M1, D1for A register path, and G2: L2, S2, M2, D2 for B register path. 2.Each function units has its special function, such as +/-/*/>/<. Butsome operations can be deal in all unitsUnit pathThe C6000 CPU has 2 generous purpose register files ( A & B), 8 function units (L1/S1/D1/M1 & L2/S2/M2/D1).The 8 function units have different path to access data or data addres s:1.L Path:LD1/LD2: Access data path of A & B register filesa)从A/B中读取数据2.DA1/DA2: access data address path of A & B register filesa)把数据保存到A/B中3.ST1/ST2: write data path of A & B register filesa)把立即数或者控制寄存器保存到A/B中4.1X/2X: cross path of A & B register files, to access opposite-side.a)跨A/B读取数据5.说明:a)前面三个路径统称为T路径(LD、ST、DA)。

在具体汇编指令上,只会显示为T或者X路径,不会具体显示某一种T路径。

b)X路径是在跨A/B寄存器使用的,用或不用情况是一定的c)现在只有使用了X路径,或者LDW、STW指令会显示具体使用的路径名称。

Register File Cross Paths1.G1 units can read/write data from/into A registers. And the G2 unitscan read/write data from/into B registers. So G1 units have cross path to A registers, and G2 units have cross path to B register.2.At the same time, A registers have cross paths to opposite-B registers,such as Ax is connect to Bx. So function units of A registers can access B register.Normal registersReserved by表示谁负责保存这个寄存器中的值,如果是Parent,则是Caller;如果是Child 则是called function。

这里的Parent与child是与某此调用动作相关。

如果脱离具体的某此调用,基本所有的函数都即是parent又是child。

或者说,在某此函数调用时,哪些寄存器是在调用之前就要压栈保存(可能同时赋值的)——parent类的寄存器;哪些寄存器是在调用后如果使用到了才需要压栈保存的——child类寄存器。

寄存器中的值,始终是根据此次调用(即Crash时的调用)的参数状态。

即Parent寄存器保存的Crash function的Caller的参数;而child寄存器保存的是crash本函数的参数。