ASIC设计工具的使用

ASIC设计cadence自动布局布线工具_图文(精)

本节将使用综合工具(Design Compiler 对一个 8位全加器逻辑综合,并产生一个门级网表;利用该网表使用自动布局布线工具(Silicon Ensemble 生成一个全加器的版图。

首先输入 8位全加器 verilog 代码:module adder8(Cout,S,A,Cin;output Cout;output [7:0]S;input [7:0]A;input [7:0]B;input Cin;reg [8:0]SUM;reg [7:0]S;reg Cout;wire [7:0]A,B;always @(Aor B or CinbeginSUM [8:0]=A+B+Cin;S =SUM [7:0];Cout =SUM [8];endendmodule打开综合工具 DC (psyn_gui&File->Read..读入代码File->Setup..设置 3个相关工艺库将带红色 *号的 3个库设置如下图 Design->CompileDesign.. 编译Schematic->NewDesign Schematic View..可以看到综合后的顶层结构通过双击 C1模块还可以看到全加器的门级结构为了后面自动布局布线的需要, 这里我们要将这个综合结果保存为 adder8_nl.v 门级网表。

在 psyn_gui-xg-t>后输入如下命令下面进行自动布局布线 (一下有路径出现的地方要特别注意打开 Silicon Ensemble (sedsm&File->Import->LEF… 导入库的转换格式注意此文件的路径!File->Import->Verilog… 导入工艺库(此库为 verilog 描述的标准单元,包含各种延时信息这里去掉后面的!继续 File->Import->Verilog… 导入网表 adder8_nl.v(此处要先删掉第一个工艺库这里要加上顶层模块名 adder8Floorplan->InitializeFloorplan…准备工作完成开始布局布线点击 Variables 将里面的 PLAN.LOWERLEFT.ORIGIN 由 FALSE 改为 TUREEdit ->Add ->Row… Area 的区域可以直接点击 Area 并在图上拖拽,并使其大小与芯片核一致File->Saveas… 保存为 fplanRoute->PlanPower… 设置电源环在 Plan Power 窗口中点击 AddRings…Place->Ios…放置输入输出Place->Cells…放置单元Place->FillerCells->AddCells…Route->RoutePower->FollowPins… 添加管脚(金属线宽设为 1.8 Route->Wroute…布线View->DisplayOptions… 检查管脚名设置 Pin 为 ONFile->Export->DEF… 命名为adder8_wrouted.def打开 icfb &再导入 DEF文件之前要确保你有如下图中的一些库文件File->Import->DEF…Enter “ tutorial ” for Library Name, “ adder8” for Cell Name, and “ autoRouted ”for View Name.打开 View 中的autoRoutedDesign->Save..Tool->Layout..将提取图转换为版图,这里需要改变几个参数 Edit->Search..点击Add Criteria然后做如下图的几个改动Apply Replace AllDesign->SaveAs..现在就可以打开 layout 了DRC… 熟悉吧! !。

可编程ASIC设计实训报告

可编程ASIC设计实训报告1.引言1.1 概述概述:可编程ASIC(Application-Specific Integrated Circuit)设计是一种针对特定应用领域进行定制优化的集成电路设计方法。

与传统的ASIC 设计相比,可编程ASIC设计可以在不改变硬件的情况下,通过重新编程实现不同的功能和逻辑。

在本报告中,我们将介绍可编程ASIC设计的基本概念和原理,以及在实训中搭建设计环境和进行设计实例分析的具体过程和方法。

通过本报告的学习,读者可以深入了解可编程ASIC设计的实践应用,以及进一步掌握ASIC设计的相关技术和方法。

文章结构部分的内容可以包括对整篇文章的组织架构和每个部分的内容概述。

可以介绍文章的逻辑顺序以及每个部分的重点内容和目的。

同时,文章结构部分也可以包括对整篇文章的写作目的和读者对象的介绍。

": , "3.2 成果展示": ,"3.3 展望":请编写文章1.2 文章结构部分的内容1.3 目的目的部分:通过本报告的撰写和实训内容的呈现,旨在让读者了解可编程ASIC设计的基本概念和原理,掌握实训环境搭建的方法和技巧,以及通过设计实例分析进行实际操作,从而提升对可编程ASIC设计的理解和应用能力。

同时,通过总结和成果展示,展示实训成果,激发更多人对可编程ASIC设计领域的兴趣,为未来的发展展望提供参考。

2.正文2.1 可编程ASIC设计简介可编程ASIC(Application Specific Integrated Circuit)是一种专门定制的集成电路,与传统的ASIC相比,可编程ASIC具有更高的灵活性和可编程性。

可编程ASIC设计允许工程师在硅片上实现特定的电路功能,同时又可以根据需求进行修改和重新配置,从而实现多种功能的实现。

可编程ASIC设计的主要特点包括灵活性、可编程性和高性能。

通过使用可编程ASIC,设计人员可以快速构建复杂的数字电路,同时减少电路设计的时间和成本。

ASIC基本流程以及工具介绍

ASIC流程与工具(1)ASIC流程(En)Some notes:1. Defini tionof front-end2. Lack of FPGA protot ype(3)简化流程(4)流程所对应的工具黑体字是实验室用的工具Questi ons:Before tape-out,whichroutin e checkshould be perfor med for your layout databa se in 0.18 um proces s?a.drcb.lvsc.drc&antenn ad.simula tion(Answer:post-simula tion)What is the purpos e and genera l flow of design verifi catio n? What techni quesin your knowle dge are used in design verfic ation?验证技术:V era, SystemV erilogDC里lin k library, target library, symbol library:1.目标库(targe_libra ry):是DC在ma pping时将设计映射到特定工艺所使用的库,就是使用目标库中的元件综合成设计的门级网表2.连接库(link_l ibrar y):是提供门级网表实例化的基本单元,也就是门级网表实例化的元件或单元都来自该库。

连接库定义为标准单元的db格式的库文件加上pad db格式的库文件,加上ROM,RAM等宏单元库文件”3.符号库(symbol librar y):指定的库用来将库中的器件用图形表示出来。

whichone is worse-case in 0.18um proces s?1.1.8v,25c2.1.98v,125c3.1.62v,-40c4.1.62v,125c5.1.98v,-40c增加最大工作频率?a.lowertemper ature;b.loweroperat ing voltag e;c.lowersubstr ate doping;d.none of the above.。

数字逻辑电路asic设计

数字逻辑电路asic设计数字逻辑电路ASIC设计是一个复杂的过程,涉及多个阶段。

以下是设计的基本步骤:1. 功能指标:明确设计的目的和功能需求,这通常涉及到详细的功能描述和接口定义。

2. 系统级设计:使用高级语言(如Matlab、C等)对各个模块进行描述,并进行方案的可行性验证。

3. 前端流程:RTL寄存器传输级设计:使用硬件描述语言(如Verilog)对电路进行描述,重点是寄存器之间的传输。

功能验证(动态验证):对设计的功能进行仿真验证,需要激励驱动,是动态仿真。

常用的仿真验证工具包括Mentor公司的Modelsim、Synopsys的VCS和Cadence的NC-Verilog。

逻辑综合(Design Compile):指定特定的综合库,添加约束文件。

逻辑综合得到门级网表(Netlist)。

4. 后端流程:物理设计(Layout):基于逻辑综合后的网表进行物理设计,包括布局、布线和时钟树综合等。

DRC/LVS 检查:进行设计规则检查和布局与电路图一致性检查,确保设计的正确性和工艺的可行性。

5. 形式验证(静态验证):对综合后的网表进行功能上的验证。

6. 版图生成:根据设计要求和工艺参数,生成用于制造的版图。

7. 投片制造:将生成的版图送至半导体制造工厂进行制造。

8. 测试与验证:制造完成后,对芯片进行测试和验证,确保其功能和性能满足设计要求。

9. 封装与上市:如果芯片通过所有测试和验证,则进行封装,并推向市场。

在进行ASIC设计时,需要权衡多个因素,如速度、面积、功耗和上市时间等。

另外,ASIC设计是一项复杂且技术性很强的工作,通常需要由经验丰富的工程师团队来完成。

asic实验报告

asic实验报告ASIC实验报告引言ASIC(Application-Specific Integrated Circuit)是一种专用集成电路,它被广泛应用于各种领域,包括通信、计算机、医疗、汽车等。

本实验报告旨在介绍ASIC的基本原理、设计流程以及应用案例,以便更好地理解和应用这一技术。

一、ASIC的基本原理ASIC是根据特定应用需求而设计的集成电路,相比通用集成电路(如微处理器),ASIC具有更高的性能和更低的功耗。

ASIC的设计基于硬件描述语言(HDL),如Verilog或VHDL,通过对电路逻辑的描述来实现特定功能。

ASIC的设计流程包括电路设计、逻辑综合、布局布线和验证等步骤,最终生成可用于生产的掩模。

二、ASIC的设计流程1. 电路设计:在这一阶段,根据应用需求和功能规格书,设计师使用HDL语言描述电路的逻辑功能。

这包括组合逻辑和时序逻辑的设计,并考虑到时钟频率、功耗和面积等方面的优化。

2. 逻辑综合:逻辑综合将HDL描述的电路转化为门级电路的表示形式。

在这一过程中,综合工具会根据约束条件(如时钟频率)进行优化,并生成电路的结构和时序信息。

3. 布局布线:布局布线是将逻辑综合结果映射到物理层面的过程。

此阶段包括将逻辑电路映射到物理单元(如逻辑门、寄存器)和进行连线布局,以满足时序和电气约束。

4. 验证:验证是ASIC设计流程中至关重要的一步。

通过仿真和验证工具,设计师可以验证电路的功能和时序,并进行调试和优化。

三、ASIC的应用案例1. 通信领域:ASIC在通信领域中扮演着重要的角色。

例如,ASIC可以用于实现高性能的调制解调器,以提供更快速和可靠的数据传输。

此外,ASIC还可以用于实现各种通信协议的编解码器,如以太网、USB和HDMI等。

2. 计算机领域:ASIC在计算机领域中也有广泛的应用。

例如,ASIC可以用于实现高性能的图形处理器(GPU),以提供更好的图形渲染和计算性能。

一般ASIC设计流程

制版、流片 芯片测试

传统电子 设计技术

1、借助于计算机进行软件设计 2、现成的器件与硬件电路连接

EDA技术

借助于计算机进行硬件模块和系 统设计、仿真、硬件系统测试

1.5 基于VHDL的自顶向下设计方法

一般ASIC设计流程

系统划分 将系统分割成各个功能子模块,给出子模块

之间信号连接关系。验证各个功能块的行为 模型,确定系统的关键时序

一般ASIC设计流程

逻辑设计与综合 将划分的各个子模块用文本(网表或硬件描

述语言)、原理图等进行具体逻辑描述。 硬件描述语言:综合 电路网表文件 原理图:简单编译 逻辑网表结构

自顶向下设计流程

2.1 FPGA/CPLD设计流程

应用于FPGA/CPLD的EDA开发流程:

图2-4 一般ASIC设计流程

一般ASIC设计流程

综合后仿真 从上一步得到网表文件,在这一步进行仿真

验证

一般ASIC设计流程

版图设计 将逻辑设计中每一个逻辑元件、电阻、电容

等以及它们之间的连线转换成集成电路制造 所需要的版图信息

一般ASIC设计流程

版图验证 版图原理图对比、设计Fra bibliotek则检查、电气规则

检查

一般ASIC设计流程

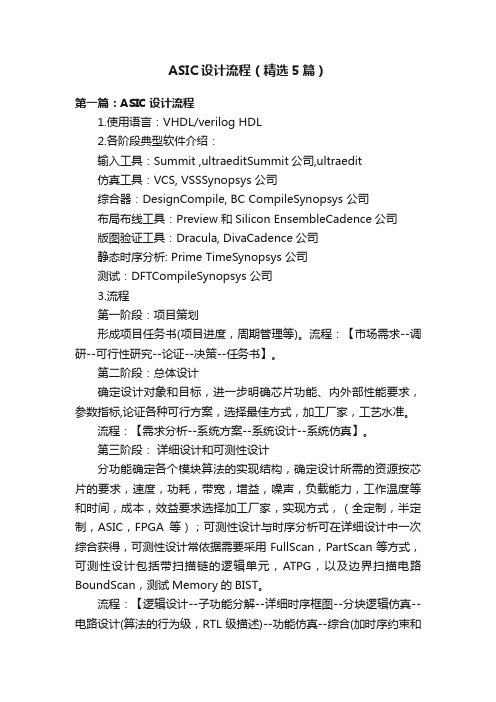

ASIC设计流程(精选5篇)

ASIC设计流程(精选5篇)第一篇:ASIC设计流程1.使用语言:VHDL/verilog HDL2.各阶段典型软件介绍:输入工具:Summit ,ultraeditSummit公司,ultraedit仿真工具:VCS, VSSSynopsys 公司综合器:DesignCompile, BC CompileSynopsys 公司布局布线工具:Preview 和Silicon EnsembleCadence公司版图验证工具:Dracula, DivaCadence公司静态时序分析: Prime TimeSynopsys 公司测试:DFTCompileSynopsys 公司3.流程第一阶段:项目策划形成项目任务书(项目进度,周期管理等)。

流程:【市场需求--调研--可行性研究--论证--决策--任务书】。

第二阶段:总体设计确定设计对象和目标,进一步明确芯片功能、内外部性能要求,参数指标,论证各种可行方案,选择最佳方式,加工厂家,工艺水准。

流程:【需求分析--系统方案--系统设计--系统仿真】。

第三阶段:详细设计和可测性设计分功能确定各个模块算法的实现结构,确定设计所需的资源按芯片的要求,速度,功耗,带宽,增益,噪声,负载能力,工作温度等和时间,成本,效益要求选择加工厂家,实现方式,(全定制,半定制,ASIC,FPGA等);可测性设计与时序分析可在详细设计中一次综合获得,可测性设计常依据需要采用FullScan,PartScan等方式,可测性设计包括带扫描链的逻辑单元,ATPG,以及边界扫描电路BoundScan,测试Memory的BIST。

流程:【逻辑设计--子功能分解--详细时序框图--分块逻辑仿真--电路设计(算法的行为级,RTL级描述)--功能仿真--综合(加时序约束和设计库)--电路网表--网表仿真】。

第四阶段:时序验证与版图设计静态时序分析从整个电路中提取出所有时序路径,然后通过计算信号沿在路径上的延迟传播,找出违背时序约束的错误(主要是SetupTime 和HoldTime),与激励无关。

数字设计之ASIC流程(1)

数字设计流程第一步、前端功能代码设计:良好的代码风格可以在满足功能和性能目标的前提下,增强代码的可读性、可移植性,首要的工作是在项目开发之前为整个设计团队建立一个命名约定和缩略语清单,以文档的形式记录下来,并要求每位设计人员在代码编写过程中都要严格遵守。

所以,在设计之前要按照顶层模块的输入INPUT、输出OUTPUT以及顶层模块内部所调用到的线网wire、reg 进行说明,同时要画出顶层模块的内部结构图,便于定义顶层模块所调用到的单元之间的连接端口关系。

良好代码编写风格的通则概括如下:(1)对所有的信号名、变量名和端口名都用小写,这样做是为了和业界的习惯保持一致;对常量名和用户定义的类型用大写;(2)使用有意义的信号名、端口名、函数名和参数名;(3)信号名长度不要太长;(4)对于时钟信号使用clk 作为信号名,如果设计中存在多个时钟,使用clk作为时钟信号的前缀;(5)对来自同一驱动源的信号在不同的子模块中采用相同的名字,这要求在芯片总体设计时就定义好顶层子模块间连线的名字,端口和连接端口的信号尽可能采用相同的名字;(6)对于低电平有效的信号,应该以一个下划线跟一个小写字母b 或n 表示。

注意在同一个设计中要使用同一个小写字母表示低电平有效;我习惯使用n来表示。

(7)对于复位信号使用rst 作为信号名,如果复位信号是低电平有效,建议使用rst_n;注意做异步复位的同步化;一般在使用的时候为了避免异步复位的毛刺对芯片的工作产生影响,都把异步复位用在上电启动的复位过程中,在芯片上电后就不再使用异步复位而改用同步复位,牺牲一个周期的复位等待时间来得到不会受到复位毛刺影响的电路性能;(8)当描述多比特总线时,使用一致的定义顺序,对于verilog 建议采用bus_signal[x:0]的表示;(9)尽量遵循业界已经习惯的一些约定。

如*_r 表示寄存器输出,*_a 表示异步信号,*_pn 表示多周期路径第n 个周期使用的信号,*_nxt 表示锁存前的信号,*_z 表示三态信号等;(10)在源文件、批处理文件的开始应该包含一个文件头、文件头一般包含的内容如下例所示:文件名,作者,模块的实现功能概述和关键特性描述,文件创建和修改的记录,包括修改时间,修改的内容等;(11)使用适当的注释来解释所有的always 进程、函数、端口定义、信号含义、变量含义或信号组、变量组的意义等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

四、综合前仿真

1、用WaveFormer Lite产生激励信号 导入信号信息 画波形 输出测试基准文件

2、选择激励文件(右击文件名)

3、运行综合前仿真

4、打开并编译源文件

第十章 ASIC设计工具的使用

以Actel设计工具为例

一、设计工具(Libeபைடு நூலகம்o IDE)的组成

1、设计输入工具

原理图输入:ViewDraw AE HDL编辑工具:HDL Editor

2、仿真工具

ModelSim WaveFormer Lite

3、逻辑综合工具(Synplify) 4、设计实现工具(designer) 4、编程工具(APS/Silicon Sculptor,FlashPro) 5、调试工具(Silicon Explorer II)

• 仿真及观察波形

五、用Synplify进行逻辑综合

1、启动综合工具

2、选择实现参数

4、运行 5、保存数据并退出

六、综合后仿真

• 过程与综合前仿真相同

七、用Designer进行设计实现

1、运行Designer

2、编译设计

3、编辑引脚

4、进行布局布线

5、参数Back-Annotate

二、设计流程

二、设计流程

• • • • • • • 创建新工程或打开工程 产生源文件(schematic, HDL, and ACTgen Macros) 向工程导入源文件 用Synplify逻辑综合 (non-schematic designs) 用ModelSim进行功能仿真 用Actel‘s Designer software进行逻辑实现 用ModelSim进行定时仿真 器件编程 器件调试

6、保存并退出

八、定时仿真

与功能仿真步骤相同,只是所用的仿真文 件不同。

九、产生编程文件

在Designer中产生

•原理图输入的设计流程

•HDL逻辑综合的设计流程

三、创建新工程

• VHDL工程(双击Libero IDE、FILE——》NEW project)

三、创建新工程

• 选择工具

• 添加文件

• 完成

• 添加HDL源程序(FILE--》NEW,打开 HDL Editor)

• 保存文件

• 添加原理图文件