后仿真流程

FPGA初学之前后仿真分析

FPGA初学之前后仿真分析最近在学习FPGA,感觉语⾔的学习到时很容易,但是由于缺乏电路图的硬件知识,所以看起来⽐较难懂,下⾯是对FPGA中仿真的⼀点理解,以后需要学习的地⽅还有很多啊。

⼀、使⽤ISE环境进⾏FPGA系统设计的时候,仿真是⼀个必不可少的步骤,即仿真过程是正确实现设计的关键环节,有两种:1.功能仿真(前仿真):在设计实现前对所创建的逻辑进⾏的验证其功能是否正确的过程,即布局布线以前的仿真。

2.时序仿真(后仿真):指布局布线后仿真,因为加⼊了线延迟信息,所以这⼀步的仿真和真正芯⽚的⾏为最接近,也是⽤于仿真芯⽚时序约束是否添加正确,布局布线后是否还满⾜时序等。

相同:两者仿真使⽤的仿真器是相同的,所需的流程和激励也是相同的;不同:时序仿真加载到仿真器的设计包括基于实际布局布线设计的最坏情况的布局布线延时,并且在仿真结果波形图中,时序仿真后的信号加载了时延,⽽功能仿真没有。

ISE环境中前后仿真的选项:以⼀个ALU的实现功能为例分析前后仿真的不同,其前仿真和后仿真的结果图为:前仿真图后仿真图从时序仿真图可以看出,后仿真存在着延迟。

本实验中存在的延迟也就是⼏ns,但是频率很⾼的时候,延迟可能会达到⼀个或者⼏个周期,这就要求⼯作频率不能超过最⾼⼯作频率。

那么最⾼频率怎么计算呢?⼆、计算最⼤⼯作频率⾸先需要知道FPGA中存在的延时有哪些,下⾯是常⽤的四种:1、纯组合逻辑延时(输⼊引脚到输出引脚),如图:2、输⼊引脚到同步元件之间的延时,如图delay23、同步元件到输出引脚之间的延时,如图delay34、不同时钟Clk1和Clk2之间的异步延时,如图delay4我们知道,⼏乎所有的FPGA设计平台都包含静态时序分析⼯具,利⽤这类⼯具可以获得映射或布局布线后的时序分析报告,从⽽对设计的性能做出评估。

⼯作频率的计算受到时序延时delay1、 delay2、 delay3、 delay4的影响。

在影响⼯作频率的参数中,由于针对某⼀个器件delay2 和delay3 是固定的,因此我们在设计中需要考虑的参数主要就是delay1 和delay4。

模拟IC版图DRC-LVS-后仿真

DRC中常见术语

浙大微电子

9

浙大微电子

10

浙大微电子

11

DRC工具简介

Mentor Calibre Cadence Dracula Synopsys Hercules

浙大微电子

12/61

Calibre DRC流程

1.DRC文件准备 2.启动软件 3.打开版图 4.Calibre 设置 5.Check 6.查看结果 7.修改保存再进行第5步,直到没有错误(密 度错误除外)

浙大微电子 13/61

DRC文件准备

去流片厂网站下载最新版本DRC文件 SmicDR2R_cal40_log_ll_sali_p1mx_1tm_1 21825.drc 路径 /home/smic/SMIC40nmPDK/SPDK40LL_11 25_CDS_Prev1.3.3/SPDK40LL_1125_1TM_ CDS_Prev1.3.3/smic40ll_1125_1tm_cds_1 P7M_2011_10_25_Prev1.3.3/Calibre/DRC

浙大微电子

27/61

浙大微电子

28/61

版图电路图一致性检查LVS

LVS 目的就是为了检查版图与电路图或者数 字网表一致。 有三种LVS形式: 版图对模拟电路图 版图对数字网表 版图对混合网表(既有数字网表,又有模拟 电路图)

浙大微电子

29/61

版图对模拟电路图LVS

1.准备LVS文件 2.打开电路图及版图 3.启动Calibre 4.设置 5.核对 6.查看结果 7.如果有错,修改版图并保存,返回第5步, 直到出现笑脸。

FPGA验证(介绍FPGA设计流程,STA,后仿真)

验证,顾名思义就是通过仿真、时序分析、上板调试等手段检验设计正确性的过程,在FPGA/IC 开发流程中,验证主要包括功能验证和时序验证两个部分。

为了了解验证的重要性,我们先来回顾一下FPGA开发的整个流程。

FPGA开发流程和IC的开发流程相似,主要分为以下几个部分:1)设计输入,利用HDL输入工具、原理图输入工具或状态机输入工具等把所要设计的电路描述出来;2)功能验证,也就是前仿真,利用Modelsim、VCS等仿真工具对设计进行仿真,检验设计的功能是否正确;常用的仿真工具有Model Tech公司的ModelSim,Synopsys公司的VCS,Cadence公司的NC-Verilog和NC-VHDL,Aldec公司的Active HDL VHDL/Verilog HDL等。

仿真过程能及时发现设计中的错误,加快了设计进度,提高了设计的可靠性。

3)综合,综合优化是把HDL语言翻译成最基本的与或非门的连接关系(网表),并根据要求(约束条件)优化所生成的门级逻辑连接,输出edf和edn等文件,导给CPLD/FPGA厂家的软件进行实现和布局布线。

常用的专业综合优化工具有Synplicity公司的synplify/Synplify Pro、Amplify等综合工具,Synopsys公司的FPGA Compiler II综合工具(Synopsys公司将停止发展FPGA Express软件,而转到FPGA Compiler II平台),Exemplar Logic公司出品的LeonardoSpectrum等综合工具。

另外FPGA/CPLD厂商的集成开发环境也带有一些综合工具,如Xilinx ISE中的XST等。

4)布局布线,综合的结果只是通用的门级网表,只是一些门与或非的逻辑关系,与芯片实际的配置情况还有差距。

此时应该使用FPGA/CPLD厂商提供的实现与布局布线工具,根据所选芯片的型号,进行芯片内部功能单元的实际连接与映射。

仿真操作流程范文

仿真操作流程范文一、准备工作在进行仿真操作之前,需要进行一些准备工作,确保设备和环境的正常运行。

首先,检查仿真设备是否完好,并查看是否有任何故障或损坏。

然后,确认仿真软件是否已正确安装并更新至最新版本。

最后,检查仿真环境是否安全,移除任何可能导致意外的障碍物。

二、启动设备和软件在准备工作完成后,需要启动仿真设备和软件。

按照设备说明书和软件操作指南的要求,正确启动设备并登录仿真软件。

同时,确保设备与仿真软件的连接稳定,以便正常进行操作。

三、选择场景和设定参数仿真软件通常提供多个场景供用户选择,每个场景都具有不同的操作难度和目标。

根据自己的需求和实际情况,选择合适的场景。

在选择场景之后,还需要设定一些操作参数,比如时间限制、物品数量等。

根据要求和目标,合理设定参数,以增加操作的挑战性和真实感。

四、学习和熟悉操作方法在正式进行操作之前,需要学习和熟悉操作方法。

通过阅读操作手册、观看教学视频或参加培训课程,了解设备和软件的操作步骤和技巧。

同时,还应该尽量模拟实际操作的场景和环境,以提高操作的真实性和准确性。

五、开始仿真操作当准备工作和学习阶段完成后,就可以开始进行仿真操作了。

根据设备和软件的要求,按照预定的操作步骤进行操作。

在操作过程中,应该密切注意设备显示的信息和指示,及时调整和纠正操作。

同时,还需要确保操作的准确性和安全性,以避免造成不必要的损失或危险。

六、评估和反馈在完成仿真操作之后,可以对操作过程进行评估和反馈。

通过对比仿真结果和目标要求,分析操作的准确性和效果。

同时,还可以查看系统提供的评分和评价,了解自己的操作水平和改进空间。

在评估和反馈的基础上,可以总结经验和教训,提高自己的操作技能和经验。

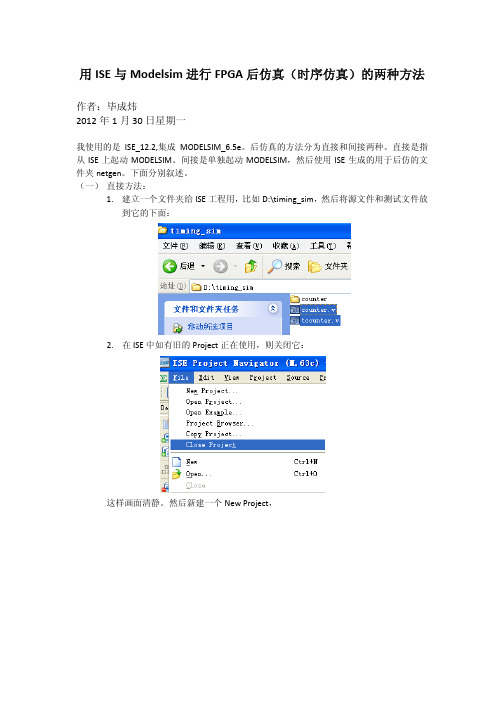

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法

用ISE与Modelsim进行FPGA后仿真(时序仿真)的两种方法作者:毕成炜2012年1月30日星期一我使用的是ISE_12.2,集成MODELSIM_6.5e。

后仿真的方法分为直接和间接两种。

直接是指从ISE上起动MODELSIM。

间接是单独起动MODELSIM,然后使用ISE生成的用于后仿的文件夹netgen。

下面分别叙述。

(一) 直接方法:1.建立一个文件夹给ISE工程用,比如D:\timing_sim,然后将源文件和测试文件放到它的下面:2.在ISE中如有旧的Project正在使用,则关闭它:这样画面清静。

然后新建一个New Project,点Next,选好器件和仿真器:点Next,点Finish.为了能够在ISE中直接唤起MODELSIM,还需要一些设置,主要是两处:双击器件:保证下图红圈处选中你要的仿真器:点OK后,在主菜单中点:保证在红圈处指定好MODELSIM执行文件所在的位置编译仿真库可以在这里双击Compile HDL Simulation Libraries,也可以在C:\Xilinx\12.2\ISE_DS\ISE\bin\nt下面找到,双击它,注意红圈处所标的是你的ISE版本所支持的MODELSIM版本,不能低于它。

否则仿真过程可能出问题。

点Next,点Next,选定你针对什么器件编译仿真库,点Next,点Next,注意,ISE可能最初不带modelsim.ini,它在此步会自动生成这个文件,并且是可写的,即它的“只读”属性是已经自动去掉的。

生成仿真库的映射关系自动写入了ISE的这个modelsim.ini,位于C:\Xilinx\12.2\ISE_DS\ISE\bin\nt,但是,它并不会自动去更新MODELSIM软件的modelsim.ini,而且MODELSIM使用的是它自己的modelsim.ini,位于C:\modeltech_6.5e。

所以需要把ISE的modelsim.ini中的映射关系再COPY到MODELSIM自己的modelsim.ini中。

simulation仿真流程

simulation仿真流程

仿真流程是指在进行仿真实验时所采取的步骤和方法。

一般而言,仿真流程包括以下几个主要步骤:

1. 确定仿真目标,首先需要明确仿真的目的和目标,包括所要研究的问题、需要模拟的系统或过程,以及希望从仿真中获得的结果。

2. 收集数据和建立模型,在进行仿真之前,需要收集相关的数据和信息,并建立相应的数学模型或计算模型,以便对系统或过程进行仿真分析。

3. 设定参数和初始条件,根据建立的模型,需要设定仿真所需的参数和初始条件,这些参数和条件将影响仿真的结果。

4. 运行仿真实验,在设定好参数和初始条件之后,开始运行仿真实验,使用计算机程序或仿真工具对模型进行数值计算或模拟,得到系统在不同时间或条件下的行为和性能。

5. 分析和验证结果,对仿真得到的结果进行分析和验证,与实

际情况进行比较,评估模型的准确性和仿真的有效性。

6. 优化和改进模型,根据分析和验证的结果,对模型进行优化和改进,以提高仿真的精度和可靠性。

7. 结果展示和报告,最后,将仿真结果进行展示和报告,向相关人员或决策者介绍仿真分析的过程和结论,为实际问题的解决提供参考依据。

总之,仿真流程是一个系统工程,需要综合运用数学、计算机科学、工程技术等多个领域的知识和方法,通过科学的步骤和严谨的分析,对复杂系统或过程进行模拟和分析,为实际问题的解决提供理论和技术支持。

仿真工作流程介绍

仿真工作流程介绍仿真工作流程是一种通过利用计算机模型、软件工具等技术手段来模拟现实世界中的复杂系统、过程或现象的方法。

它可以帮助人们理解和预测系统的行为,并在实际操作中指导决策和优化。

仿真工作流程一般包括建模、验证、分析和优化等几个主要步骤。

第一步是建模,建模是仿真工作的第一步,也是最关键的一步。

建模的目的是将现实世界的系统或过程抽象为计算机可以处理的模型。

建模可以通过使用数学方程、物理规律、统计数据等方法来描述系统的特征和行为。

建模的种类包括离散事件仿真、连续系统仿真、代理模型等。

在建模过程中,可以使用各种工具和技术,如Matlab、Simulink、AnyLogic等。

第二步是验证,验证是对建立的模型进行验证和验证的过程。

验证的目的是确保模型的准确性和正确性。

验证可以通过与现实世界的数据进行比较,分析模型的输出和实际结果的一致性来完成。

验证的方法包括参数估计、回归分析、敏感性分析等。

第三步是分析,分析是对模型进行分析和评估的过程。

分析的目的是了解系统的行为和性能,并从中提取有价值的信息。

分析可以通过观察模型的输出、生成统计数据、绘制图表等方法来完成。

分析的工具和技术包括统计分析、数据挖掘、可视化等。

第四步是优化,优化是为了改进系统的性能和效率而对模型进行的调整和改进。

优化的目标可以是最大化效益、最小化成本、最小化风险等。

优化可以通过调整模型的参数、结构或算法来实现。

优化的方法包括模拟退火、遗传算法、粒子群算法等。

在整个仿真工作流程中,还需要不断的循环迭代,根据分析和优化的结果来调整和改进模型,以逐步提高模型的准确性和可靠性。

此外,还需要对模拟的过程和结果进行文档记录和报告,以便于审查和交流。

综上所述,仿真工作流程是一个系统性的过程,包括建模、验证、分析和优化等几个主要步骤。

通过仿真,人们可以更好地理解和预测现实世界中的复杂系统和过程,并在实际应用中指导决策和优化。

仿真工作流程是一个动态的过程,需要不断地迭代和改进。

后仿----转载

后仿----转载1.后仿是否必要随着芯⽚规模的增⼤,关于IC设计流程中的后仿是否必要,有多种声⾳。

认为不必要的理由是:布局布线后的⽹表,已经可以通过STA保证时序,后仿只不过是确认⼀遍电路的时序。

⽽且随着电路规模不断增⼤,仿真⼯具的仿真速度的提升仍不明显,后仿必然是⼀个很耗时的步骤,时间代价⼤⽽收益不明显。

认为有必要的理由是,从公司以往多个项⽬的经验来看,后仿中也发现了⼀些问题。

⽽对于有些设计,STA并不能完全覆盖所有的路径。

后仿的⼯作是对后端实现最后的check。

本⽂认为,以公司现阶段的研发⼒量,后仿还是必须的。

2.前后仿的区别前仿:RTL的仿真后仿:门级仿真。

⼜分为综合后仿真和布局布线后仿真a.关注点不同;前仿:关注RTL在功能上是否正确(符合设计)后仿:关注电路在各种⼯作条件下,插⼊了延时后,功能是否依然正确。

b.仿真对象不同;前仿:仿真的对象是RTL后仿:仿真的对象是门级⽹表+sdf⽂件(可能包括⼀些IP的sdf)综合后仿真⽤的是综合后的⽹表+PreSTA产⽣的sdf(⽆net延时,cell延时不准确,时钟树不准确)布局布线后仿真⽤的是PR后的⽹表+PostSTA产⽣的sdfc.外部激励与响应检查;所⽤的激励和响应检查应⼀致后仿可能让时钟漂移以模拟极端的情况3.后仿的各种组合情况如果考虑OSC漂移以及三种Corner,可以组合以下六种情况Fast OSC + Fast SDFSlow OSC + Fast SDFFast OSC + Typ SDFSlow OSC + Typ SDFFast OSC + Slow SDFSlow OSC + Slow SDF说明:对于普通的设计,实际只需考虑3中sdf即可。

对于osc偏移可能带来的影响(如,flash编程),则后仿需要考虑更多Osc偏移带来的影响(时序不满⾜)4. 认识sdf⽂件sdf = 标准延时⽂件请参考附录1中对于sdf⽂件的注释5. Sdf反标反标:vcs将sdf⽂件中的延时信息添加到门级⽹表中对应的地⽅6.后仿违背的类型a.时序器件Setup/hold违背(posedge D -> posedge CK , negedge D -> posedge CK)Recovary/Removal违背(posedge CDN -> posedge CK ,posedge SDN -> posedge CK)Width违背(CK,CDN,SDN)b.IP时序违背IP接⼝时序不符合datasheet7.针对违背采取的措施a.同步处理第⼀级寄存器的违背i.⽅法⼀1,建⽴⽂件Sync.v,格式如下:initial beginforce Top.uXX.uYY.uZZ_reg.notifier = 1'b0;…………end2,在SimTop中的include此⽂件;解决了寄存器输出为x的情况,但仿真会报很多warningii.⽅法⼆1,建⽴⽂件Sync.v,格式如下instance {Top.uXX.uYY.uZZ_reg,……} {noTiming}2,在runsim⽂件中加⼊ +optconfigfile+./Sync.vb.其他i.时序约束是否存在问题ii.时钟树是否合理iii.电路设计是否有潜在风险iv.接⼝设计是否遵循datasheet8.后仿脚本1,+neg_tchk寄存器可能出现负的setup limit和hold limit。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

synplify,ISE,ModelSim后仿真流程我想很多人跟我一样,被ModelSim的后仿真搞的头晕脑胀。

为了这个问题,我在网上找了很多的资料,但发现这些资料往往说的不明白。

一些步骤被作者有意无意地省略掉,这常常给读者造成不必要的麻烦,所以我决定写下这一篇文章,把这3天我努力的结果拿出来,与大家分享。

首先,我把我用到的软件说明一下。

如果你发现根据我的操作,你还是解决不了ModelSim 后仿真的问题,那就可能是软件版本的问题。

1,ModelSim Se 6.1b2,Synplify Pro 7.5.13,ISE 5.2i (这个是老了点)4,WindowsXP(这个应该没有多大的关系)还有就是我使用的是verilog,我想VHDL的方法与verilog是差不多的,最多也就是在建库方面有点差别而已。

下面的这些方法,是我这3天搞出来的。

当然也参考了一些文章。

如果谁有更方便的方法,欢迎指出来。

我的邮箱是vf1983cs@。

有空大家多交流。

一,为modelsim生成3个库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。

所谓的标准库就是modelsim运行后,会自动加载的库。

不过这方面我还不是很肯定。

因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作s imprim_ver。

我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:vlog -work simprim_ver d:/Xilinx/verilog/src/simprims/*.v其中的d:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。

以下凡是要根据自己系统环境改变的内容,我都会用绿色标出,并加一个下划线。

编译完之后,你会发现你的工程文件夹下出现了一个simprim文件夹,里面又有很多个文件夹。

这些就是我们要的库了。

第四步:按照上面的方法,编译另外两个库。

所需要键入的命令分别如下:vlog -work unisim_ver d:/Xilinx/verilog/src/unisims/*.vvlog -work xilinxcorelib_ver d:/Xilinx/verilog/src/XilinxCoreLib/*.v 如果你想要编译的是VHDL的库,你需要建立的库分别是simprim,unisim和xilinxcorelib。

这三个库所需要的modelsim指令分别如下:vcom –work simprim d:Xilinx/VHDL/src/simprims/simprim_Vcomponents.vhdvcom –work simprim d:Xilinx/VHDL/src/simprims/simprim_Vpackage.vhdvcom –work simprim d:Xilinx/VHDL/src/simprims/simprim_VITAL.vhdvcom –work unisim d:Xilinx/VHDL/src/unisims/unisim_VCOMP.vhdvcom –work unisim d:Xilinx/VHDL/src/unisims/unisim_VPKG.vhdvcom –work unisim d:Xilinx/VHDL/src/unisims/unisim_VITAL.vhdvcom –work unisim d:Xilinx/VHDL/src/unisims/unisim_VCFG4K.vhdvcom –work xilinxcorelib d:Xilinx/VHDL/src/ XilinxCoreLib/*.vhd关于VHDL方面,我没有实践过,如果有误的话,改一下应该问题也不大。

第五步:把库建好后,接下来的事情就是使它成为modelsim的标准库。

这只要修改modelsim安装目录下的modelsim.ini文件就可以了。

修改后的内容如下:[Library]std = $MODEL_TECH/../stdieee = $MODEL_TECH/../ieeeverilog = $MODEL_TECH/../verilogvital2000 = $MODEL_TECH/../vital2000std_developerskit = $MODEL_TECH/../std_developerskitsynopsys = $MODEL_TECH/../synopsysmodelsim_lib = $MODEL_TECH/../modelsim_libsimprim_ver = G:/EDA/Xilinx/simprim_ver(库的路径,以下同)unisim_ver = G:/EDA/Xilinx/unisim_verxilinxcorelib_ver = G:/EDA/Xilinx/xilinxcorelib_ver注意的是,这个文件是只读属性。

修改之前要把这个属性去掉。

第六步:关掉工程,重启modelsim。

查看这3个库是否在library框里面。

如果你看到了,那么恭喜!你已经完成了第一个大步骤!!接下来,就是在ISE环境下如何用synplify对设计进行综合的方法了。

还要说明的是,这一步是一劳永逸的!有了第一次,第二次就不用了。

二,在ISE环境下,调用synplify,生成后仿真所需要的文件。

之所以要在ISE环境下调用synplify,主要是因为方便!我也尝试过在synplify环境下综合设计文件,然后在ISE里编译synplify生成的edif文件。

但是不成功。

ISE在第三方工具支持方面做的是比较好的,感觉跟用ISE直接综合一样。

不过有一个缺点是看不了RTL原理图。

你可以在synplify中打开ISE生成的synplify工程文件,解决在ISE中不方便查看synplify综合结果的问题。

现在,就要开始第二个大步骤了!第一步:创建ISE工程文件。

选择好器件。

注意Design Flow中一定要选择Synplify Pro Verilog。

第二步:综合设计文件,也就是verilog文件。

双击下图中的按钮,ISE就会自动调用synplify。

(如果没有的话,那可能是你的系统环境变量没有设置好)。

此时会弹出一个对话框,要你选择synplify的liscense。

(这步本来不用说的。

如果没有对话框弹出来的话,也不要紧)随便选择一个,就等结果了。

第三步:生成后仿真需要的文件。

如下图,我们可以看到在Implement Design中有三个大分支,这对应着三种仿真。

按你的需要按下相应的图标,生成modelsim后仿真所需要的文件,下面对生成的文件和生成这些文件的图标进行说明。

图标生成文件Generate Post-Translate Simulation Model xxx_translate.vGenerate Post-Map Simulation Model xxx_map.v,xxx_map.sdfGenerate Post-Place&Route Simulationxxx_timsim.v,xxx_timsim.sdfModel在这3种仿真中,只有第一种没有生成sdf文件。

也就是说在modelsim中,只有第一种可以不用把sdf添加到仿真器中(废话!!)。

到这时,所有为后仿真所做的准备工作就都完成了。

下面就后仿真举例。

我们要进行的是Place&Route Simulation!所以按下图标,生成为下一步的工作所需要的文件吧。

三,用modelsim进行后仿真。

在开始这一步之前,建议为你的设计新建一个文件夹。

当然你也可以不这样做,不过对于所造成的麻烦,本人不负责!后仿真总共需要3个*.v文件。

一个是你的模块的测试文件,一个是ISE生成的xxx_timsim.v(注意,我们要更改这个文件的文件名,改为xxx.v,也就是你的顶层模块名了。

这也是我要求新建文件夹的原因了,重名这件事比尔.盖茨是不答应的)。

另一个是glbl.v文件。

这个文件在Xilinx安装盘:\Xilinx\verilog\src下。

VHDL不需要第3个文件。

复制这3个文件到新建的文件夹下,开始我们的第一步工作。

第o步:为xxx_timsim.v改名!!!第一步:新建工程,把3个文件添加到这个工程里。

(大家都这么熟了,不用教了吧)第二步:在project框里按右键—》add to project –》adding simulation configuration,如下图:第三步:在弹出的对话框里,选择SDF项。

把ISE生成的SDF文件添加进出。

如下图:记住Apply to Region这一项要写好。

它对应的是你的tb文件(就是测试文件)调用的顶层模块名。

(不是顶层模块名!!)比如你的测试文件是text,例化顶层模块top为i_top,那你应该这样填:text/i_top或者/text/i_top。

如果是第一种仿真,此步可以省略。

第四步:添加library。

我们创建的那三个库终于派上用场了!我们要添加的就是这3个。

选择library项,添加这3个库。

你的库建在哪里,就去哪里找!这个也不用说了吧!如下图:第五步:选择要仿真的模块。

你先不要急,看清楚再选。

(有些朋友性子急,驾轻就熟就选了)我们要选的仿真模块可不止一个,如下图,用CTRL键实现!!选了之后点0k!!第六步:进行后仿真!完成上一步后,project框如下图所示,双击Simulation 1,modelsim就进入仿真了,是不是很方便!第七步:做你该做的!我想接下来的事情很容易了吧,就写到这!产品编号产品描述规格书JJY-P001 USB+PS2键盘JJY-P002 PS2转USB接口JJY-P003 USB汉字输入系统。