数字锁相环实验

滤波法及数字锁相环法位同步提取实验 模拟锁相环实验 载波同步帧同步实验资料

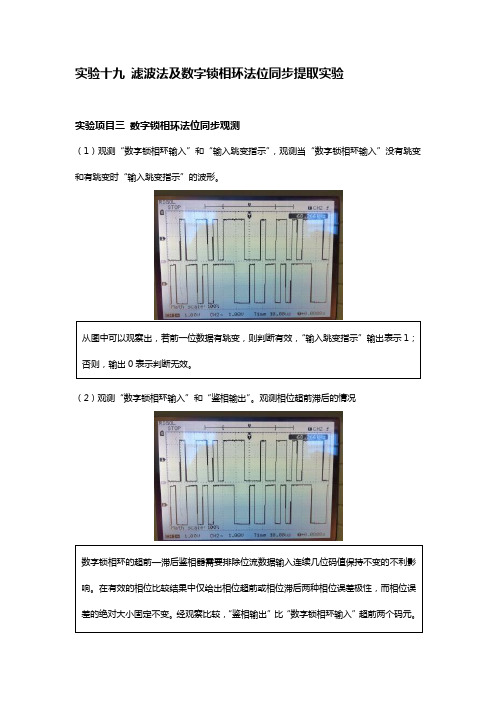

实验十九滤波法及数字锁相环法位同步提取实验实验项目三数字锁相环法位同步观测(1)观测“数字锁相环输入”和“输入跳变指示”,观测当“数字锁相环输入”没有跳变和有跳变时“输入跳变指示”的波形。

从图中可以观察出,若前一位数据有跳变,则判断有效,“输入跳变指示”输出表示1;否则,输出0表示判断无效。

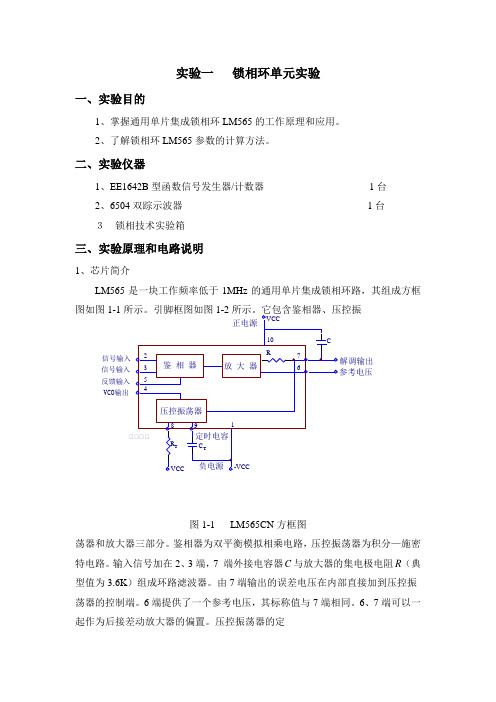

(2)观测“数字锁相环输入”和“鉴相输出”。

观测相位超前滞后的情况数字锁相环的超前—滞后鉴相器需要排除位流数据输入连续几位码值保持不变的不利影响。

在有效的相位比较结果中仅给出相位超前或相位滞后两种相位误差极性,而相位误差的绝对大小固定不变。

经观察比较,“鉴相输出”比“数字锁相环输入”超前两个码元。

(3)观测“插入指示”和“扣除指示”。

(4)以信号源模块“CLK ”为触发,观测13号模块的“BS2”。

思考题:分析波形有何特点,为什么会出现这种情况。

因为可变分频器的输出信号频率与实验所需频率接近,将其和从信号中提取的相位参考信号同时送入相位比较器,比较的结果若是载波频率高了,就通过补抹门抹掉一个输入分频器的脉冲,相当于本地振荡频率降低;相反,若示出本地频率低了时就在分频器输入端的两个输入脉冲间插入一个脉冲,相当于本地振荡频率上升,从而了达到同步的目的。

思考题:BS2恢复的时钟是否有抖动的情况,为什么?试分析BS2抖动的区间有多大?如何减小这个抖动的区间?有抖动的存在,是因为可变分频器的存在使得下一个时钟沿的到来时间不确定,从而引入了相位抖动。

而这种引入的误差是无法消除的。

减小相位抖动的方法就是将分频器的分频数提高。

实验二十 模拟锁相环实验实验项目一 VCO 自由振荡观测(1)示波器CH1接TH8,CH2接TH4输出,对比观测输入及输出波形。

实验项目二 同步带测量(1) 示波器CH1接13号模块TH8模拟锁相环输入,CH2接TH4输出BS1,观察TH4输出处于锁定状态。

将正弦波频率调小直到输出波形失锁,此时的频率大小f1为 400Hz ;将频率调大,直到TH4输出处于失锁状态,记下此时频率f2为 9.25kHz 。

基于FPGA的全数字锁相环设计与实现

基于FPGA的全数字锁相环设计与实现一、前言全数字锁相环(Digital Phase-Locked Loop,简称DPLL)是一种数字电路设计技术,可实现同步数字信号的调制和解调。

基于FPGA的全数字锁相环设计与实现,是一个极为重要的课题。

它可以有效地提高数字电路的性能,使得数字系统具有更优越的特性,并可广泛应用于数字电路的设计、数字信号的处理等领域。

二、DPLL 的体系结构DPLL是由相频检测器、滤波器、数字控制振荡器和时钟输出等多个部分组成的。

其中,相频检测器、滤波器和数字控制振荡器通常被集成到FPGA的内部,而时钟输出则需要通过FPGA的普通I/O口与市场上常见的外部输出设备相结合。

三、数字锁相环的工作原理数字锁相环的工作原理基于一个反馈循环系统,其中参考振荡器的频率与输入信号会被比较,然后通过差错检测网络来确定缺陷。

如果这些信号频率不匹配,则通过调整数字控制振荡器的频率来达到匹配。

然后,系统会根据输出信号和参考信号的相位差异来调整数字控制振荡器的频率,并通过PLL的反馈路径传输至输入端,进而得到和参考信号相同频率的输出信号。

四、数字锁相环的应用数字锁相环在通信领域有着广泛的应用,如数据码隆、数字调制、同步检测等;在数字领域,数字锁相环主要应用于数字信号处理、频谱分析、信噪比提高等方面;在电子仪器领域,数字锁相环可以被应用于测量领域、噪声分析、频率合成等方面。

五、基于FPGA的数字锁相环的设计数字锁相环的设计是一项非常复杂的工作,其中需要解决的问题主要有相频检测、低通滤波、数字控制振荡器的设计和时钟输出等方面。

在基于FPGA的数字锁相环设计过程中,可以采用很多不同的方法和技术来解决这些问题。

在数字锁相环的设计中,相频检测器是极其关键的部分,其主要功能是检测输入信号与数字控制振荡器的频率是否匹配。

其中,相频检测器常用的方式有两种:一是通过比较输入信号和数字控制振荡器的频率来实现;二是通过测量输入信号和数字控制振荡器的相位差来实现。

滤波法及数字锁相环法位同步提取实验和帧同步提取实验教学文案

滤波法及数字锁相环法位同步提取实验和帧同步提取实验滤波法及数字锁相环法位同步提取实验和帧同步提取实验一、实验目的1、掌握滤波法提取位同步信号的原理及其对信息码的要求;2、掌握用数字锁相环提取位同步信号的原理及其对信息代码的要求;3、掌握位同步器的同步建立时间、同步保持时间、位同步信号同步抖动等概念;4、掌握巴克码识别原理;5、掌握同步保护原理;6、掌握假同步、漏同步、捕捉态、维持态的概念。

二、实验内容1、熟悉实验箱2、滤波法位同步带通滤波器幅频特性测量;3、滤波法位同步恢复观测;4、数字锁相环位同步观测;5、帧同步提取实验。

三、实验条件/器材滤波法及数字锁相环法位同步提取实验:1、主控&信号源、8号(基带传输编译码)、13号(载波同步及位同步)模块2、双踪示波器(模拟/数字)3、连接线若干帧同步提取实验:1、主控&信号源、7号模块2、双踪示波器(模拟/数字)3、连接线若干四、实验原理滤波法及数字锁相环法位同步提取实验原理见通信原理综合实验指导书P129-P134;帧同步提取实验原理见通信原理综合实验指导书P141。

五、实验过程及结果分析(一)熟悉实验箱(二)滤波法位同步带通滤波器幅频特性测量1、连线及相关设置(1)关电,连线。

(2)开电,设置主控,选择【信号源】→【输出波形】。

设置输出波形为正弦波,调节相应旋钮,使其输出频率为200Khz,峰峰值3V。

(3)此时系统初始状态为:输入信号为频率200KHz、幅度为3V的正弦波。

2、实验操作及波形观测分别观测13号模块的“滤波法位同步输入”和“BPF-Out”,改变信号源的频率,测量“BPF-Out”的幅度填入下表,并绘制幅频特性曲线。

(三)滤波法位同步恢复观测1、连线及相关设置(1)关电,连线。

(2)开电,设置主控菜单,选择【主菜单】→【通信原理】→【滤波法及数字锁相环位同步法提取】。

将13号模块S2拨上。

将S4拨为1000.(3)此时系统初始状态为:输入PN为256K。

锁相实验指导内容

实验一 锁相环单元实验一、实验目的1、掌握通用单片集成锁相环LM565的工作原理和应用。

2、了解锁相环LM565参数的计算方法。

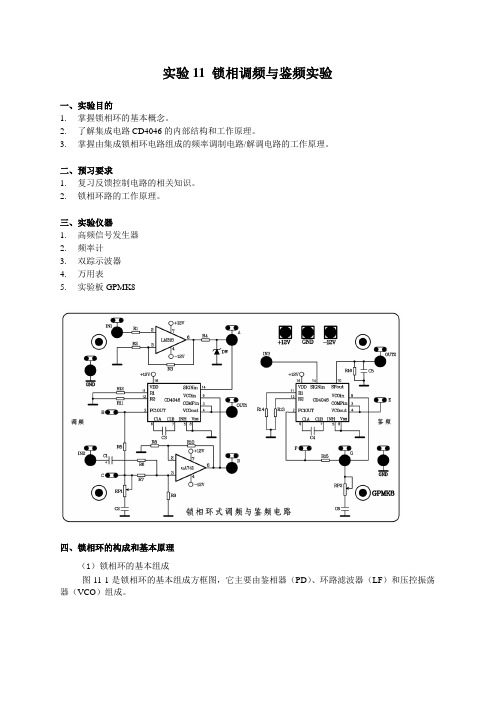

二、实验仪器1、EE1642B 型函数信号发生器/计数器 1台2、6504双踪示波器 1台 3 锁相技术实验箱三、实验原理和电路说明1、芯片简介LM565是一块工作频率低于1MHz 的通用单片集成锁相环路,其组成方框图如图1-1图1-1 LM565CN 方框图荡器和放大器三部分。

鉴相器为双平衡模拟相乘电路,压控振荡器为积分—施密特电路。

输入信号加在2、3端,7 端外接电容器C 与放大器的集电极电阻R (典型值为3.6K )组成环路滤波器。

由7端输出的误差电压在内部直接加到压控振荡器的控制端。

6端提供了一个参考电压,其标称值与7端相同。

6、7端可以一起作为后接差动放大器的偏置。

压控振荡器的定¸¸¸¸¸¸¸¸VCO¸¸¸·¸¸¸¸¸¸¸¸¸÷¸¸图1-2 LM565CN 引脚图时电阻T R 接在8端,定时电容T C 接在9端,振荡信号从4端输出。

压控振荡器的输出端4与鉴相器反馈输入端5是断开的,允许插入分频器来做频率合成器。

对LM565而言,压控振荡器振荡频率可近似表示为:TT C R f 42.1≈压控灵敏度为 :C E f K 500=式中C E 是电源电压(双向馈电时则为总电压)。

鉴相灵敏度为:π4.1=d K放大器增益为 :4.1=ALM565工作频率范围为0.001Hz~500KHz ,电源电压为±6~±12V ,鉴频失真低于0.2%,最大锁定范围为±60%f ,输入电阻为10K ,典型工作电流为8mA 。

锁相环调频和解调实验,频率合成器实验

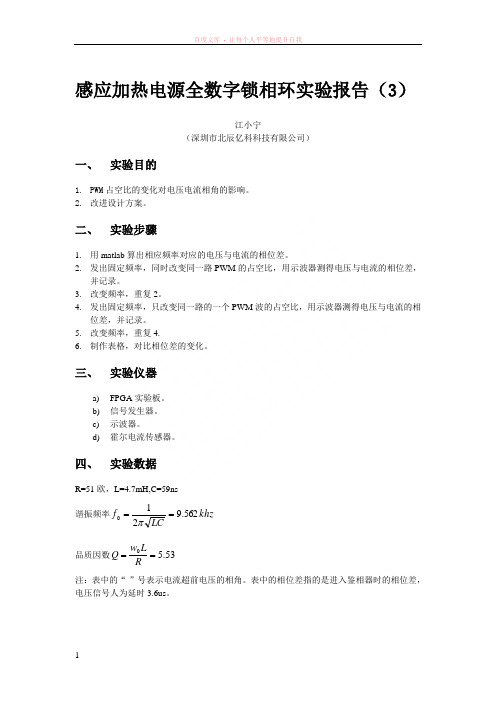

实验11 锁相调频与鉴频实验一、实验目的1.掌握锁相环的基本概念。

2.了解集成电路CD4046的内部结构和工作原理。

3.掌握由集成锁相环电路组成的频率调制电路/解调电路的工作原理。

二、预习要求1.复习反馈控制电路的相关知识。

2.锁相环路的工作原理。

三、实验仪器1.高频信号发生器2.频率计3.双踪示波器4.万用表5.实验板GPMK8四、锁相环的构成和基本原理(1)锁相环的基本组成图11-1是锁相环的基本组成方框图,它主要由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)组成。

图11-1 锁相环的基本组成① 压控振荡器(VCO )VCO 是本控制系统的控制对象,被控参数通常是其振荡频率,控制信号为加在VCO 上的电压。

所谓压控振荡器就是振荡频率受输入电压控制的振荡器。

② 鉴相器(PD )PD 是一个相位比较器,用来检测输出信号0V (t )与输入信号i V (t )之间的相位差θ (t),并把θ(t)转化为电压)(t V d 输出,)(t V d 称为误差电压,通常)(t V d 作为一直流分量或一低频交流量。

③ 环路滤波器(LF )LF 作为一低通滤波电路,其作用是滤除因PD 的非线性而在)(t V d 中产生的无用组合频率分量及干扰,产生一个只反映θ(t)大小的控制信号)(t V C 。

4046锁相环芯片包含鉴相器(相位比较器)和压控振荡器两部分,而环路滤波器由外接阻容元件构成。

(2)锁相环锁相原理锁相环是一种以消除频率误差为目的反馈控制电路,它的基本原理是利用相位误差电压去消除频率误差。

按照反馈控制原理,如果由于某种原因使VCO 的频率发生变化使得与输入频率不相等,这必将使)(t V O 与)(t V i 的相位差θ(t)发生变化,该相位差经过PD 转换成误差电压)(t V d 。

此误差电压经过LF 滤波后得到)(t V c ,由)(t V c 去改变VCO 的振荡频率,使其趋近于输入信号的频率,最后达到相等。

锁相环调频及锁相环调频发射与接收实验实验报告

锁相环调频及锁相环调频发射与接收实验实验报告沈凯捷101180101锁相环调频实验一. 实验目的1.加深对锁相环基本工作原理的理解。

2.掌握锁相环同步带、捕捉带的测试方法,增加对锁相环捕捉、跟踪和锁定等概念的理解。

3.掌握集成锁相环芯片NE564的使用方法和典型外部电路设计。

1.理解用锁相环实现调频的基本原理。

2.掌握NE564构成调频电路的原理和调试,测试方法。

二、实验使用仪器1.NE564锁相和调频实验板2.100MHz泰克双踪示波器3. FLUKE万用表4. 高频信号源5. 低频信号源三、实验内容1. 压控振荡器的测试。

2 . 同步带和捕捉带的测量。

3. 调频信号的产生和测量。

四、实验步骤1. 压控振荡器的测试(1)在实验箱主板上插上锁相环调频与测试电路实验模块。

接通实验箱上电源开关,电源指标灯点亮。

(2)把跳线S1,S2,S5,S6,S7断开,S3,S4合上。

单独测试压控振荡器的自由振荡频率。

将双排开关S8的4端合上,此时8200pF 的固定电容接入12,13脚之间,用示波器观察TP2处的波形(压控振荡器的输出端),并测量此时的振荡频率。

调节滑动变阻器W1的值,观察振荡频率是否有变化,并思考原因。

然后调节可变电容CW ,观察振荡频率的变化范围,并记录。

将双排开关S8的3端合上,此时820pF 的固定电容接入12,13脚之间,用示波器观察TP2处的波形(压控振荡器的输出端),并测量此时的振荡频率。

调节滑动变阻器W1的值,观察振荡频率是否有变化,并思考原因。

然后调节可变电容CW ,观察振荡频率的变化范围,并记录。

将双排开关S8的2端合上,此时82pF 的固定电容接入12,13脚之间,用示波器观察TP2处的波形(压控振荡器的输出端),并测量此时的振荡频率。

调节滑动变阻器W1的值,观察振荡频率是否有变化,并思考原因。

然后调节可变电容CW ,观察振荡频率的变化范围,并记录。

将双排开关S8的1端合上,此时22pF 的固定电容接入12,13脚之间,用示波器观察TP2处的波形(压控振荡器的输出端),并测量此时的振荡频率。

感应加热电源全数字锁相环实验报告

感应加热电源全数字锁相环实验报告(3)江小宁(深圳市北辰亿科科技有限公司)一、 实验目的1. PWM 占空比的变化对电压电流相角的影响。

2. 改进设计方案。

二、 实验步骤1. 用matlab 算出相应频率对应的电压与电流的相位差。

2. 发出固定频率,同时改变同一路PWM 的占空比,用示波器测得电压与电流的相位差,并记录。

3. 改变频率,重复2。

4. 发出固定频率,只改变同一路的一个PWM 波的占空比,用示波器测得电压与电流的相位差,并记录。

5. 改变频率,重复4.6. 制作表格,对比相位差的变化。

三、 实验仪器a) FPGA 实验板。

b) 信号发生器。

c) 示波器。

d)霍尔电流传感器。

四、 实验数据R=51欧,L=4.7mH,C=59ns 谐振频率khz LCf 562.9210==π品质因数53.50==RLw Q 注:表中的“-”号表示电流超前电压的相角。

表中的相位差指的是进入鉴相器时的相位差,电压信号人为延时3.6us 。

表1 同时改变同一路的占空比时,相位差的变化表2 只改变同一路的其中一个pwm 的占空比时,相位差的变化五、 实验数据分析从表1和表2中可以看出随着占空比的减小,用示波器测得的电压与电流的相位差也随之减小,甚至出现电流超前电压,与理论相位差相差越来越大。

表1与表2对比可得,只改变一个pwm 波的占空比会比同时改变两个pwm 波的占空比对相位差产生的影响小一点,但还是有影响。

远离谐振频率的相角影响要比近谐振的小。

可能原因是IGBT 开通的时间过短,影响了电流的振荡,以及二极管续流。

六、 实验结论由于占空比改变,而频率不变频率 电压信号占空比电压与电流的相位差理论相位差 9.7khz46.1% 13.27° 9.3°38.3%-10.13° 11khz 45.6% 41.58° 57.35° 36.8%9.9°频率 电压信号占空比 电压与电流的相位差理论相位差 9.7khz 46.1% 38.3% 2.1° 9.3° 46.1% 34.4% -3.8° 11khz45.6% 36.8% 27.32° 57.35° 45.6%32.4%20.2°。

锁相环实验报告

锁相环实验报告锁相环实验报告一、实验目的本次实验的目的是了解锁相环(PLL)的原理和应用,掌握PLL电路的设计和调试方法,以及了解PLL在通信系统中的应用。

二、实验原理1. PLL原理锁相环是一种基于反馈控制的电路,由比例积分环节、相位检测器、低通滤波器和振荡器等组成。

其基本原理是将输入信号与参考信号进行比较,并通过反馈调整振荡频率,使得输入信号与参考信号同步。

2. PLL应用PLL广泛应用于通信系统中,如频率合成器、时钟恢复器、数字调制解调器等。

三、实验设备和材料1. 实验仪器:示波器、函数发生器等。

2. 实验元件:电阻、电容等。

四、实验步骤1. 搭建PLL电路并连接到示波器上。

2. 调节函数发生器输出正弦波作为参考信号,并将其输入到PLL电路中。

同时,在函数发生器上设置另一个正弦波作为输入信号,并将其连接到PLL电路中。

3. 调节PLL参数,包括比例积分系数和低通滤波器截止频率等,使得输入信号与参考信号同步。

4. 观察示波器上的输出波形,记录下PLL参数的取值。

五、实验结果与分析1. 实验结果通过调节PLL参数,成功实现了输入信号与参考信号的同步,并在示波器上观察到了稳定的输出波形。

记录下了PLL参数的取值,如比例积分系数和低通滤波器截止频率等。

2. 实验分析通过本次实验,我们深入了解了锁相环的原理和应用,并掌握了PLL电路的设计和调试方法。

同时,我们也了解到PLL在通信系统中的重要作用,如时钟恢复、数字调制解调等。

六、实验结论本次实验成功地实现了输入信号与参考信号的同步,并掌握了PLL电路的设计和调试方法。

同时也加深对于PLL在通信系统中应用的认识。

七、实验注意事项1. 在搭建电路时应注意接线正确性。

2. 在调节PLL参数时应注意逐步调整,避免过度调整导致系统失控。

3. 在观察示波器输出波形时应注意放大倍数和时间基准设置。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验二 数字锁相环实验

一、实验原理和电路说明

在电信网中,同步是一个十分重要的概念。

同步的种类很多,有时钟同步、比特同步等等,其最终目的使本地终端时钟源锁定在另一个参考时钟源上,如果所有的终端均采用这种方式,则所有终端将以统一步调进行工作。

同步的技术基础是锁相,因而锁相技术是通信中最重要的技术之一。

锁相环分为模拟锁相环与数字锁相环,本实验将对数字锁相环进行实验。

B

C

A

H

G

F E

D

本地时钟14336KHz 外部测试64KHz

倍频

÷63 ÷64

÷65

÷28

÷4

延时10ns 采样1

采样2

UM01:FPGA

TPMZ03

TPMZ05

图2.2.1 数字锁相环的结构

TPMZ04

TPMZ02

÷8

TPMZ01

数字锁相环的结构如图2.2.1所示,其主要由四大部分组成:参考时钟、多模分频器(一般为三种模式:超前分频、正常分频、滞后分频)、相位比较(双路相位比较)、高倍时钟振荡器(一般为参考时钟的整数倍,此倍数大于20)等。

数字锁相环均在FPGA 内部实现,其工作过程如图2.2.2所示。

A :14336KHz

B :448KHz

C :64KHz E :16KHz F :16KHz 000111011/631/641/651/64

D :16KHz (G, H)

可变分频器分频数

T1时刻

T2时刻

T3时刻

T4时刻

图2.2.2 数字锁相环的基本锁相过程与数字锁相环的基本特征

在图2.2.1,采样器1、2构成一个数字鉴相器,时钟信号E 、F 对D 信号进行采样,如果采样值为01,则数字锁相环不进行调整(÷64);如果采样值为00,则下一个分频系数为(1/63);如果采样值为11,则下一分频系数为(÷65)。

数字锁相环调整的最终结果使本地分频时钟锁在输入的信道时钟上。

在图2.2.2中也给出了数字锁相环的基本锁相过程与数字锁相环的基本特征。

在锁相环开始工作之前的T1时该,图2.2.2中D 点的时钟与输入参考时钟C 没有确定的相关系,鉴相输出为00,则下一时刻分频器为÷63模式,这样使D 点信号前沿提前。

在T2时刻,鉴相输出为01,则下一时刻分频器为÷64模式。

由于振荡器为惯性方式,因而在T3时刻,鉴相输出为11,则下一时刻分频器为÷65模式,这样使D 点信号前沿滞后。

这样,可变分频器不断在三种模式之间进行切换,其最终目的使D 点时钟信号的时钟沿在E 、F 时钟上升沿之间,从而使D 点信号与外部参考信号达到同步。

在该模块中,各测试点定义如下:

1、 TPMZ01:本地经数字锁相环之后输出时钟(56KHz )

2、 TPMZ02:本地经数字锁相环之后输出时钟(16KHz )

3、 TPMZ03:外部输入时钟÷4分频后信号(16KHz )

4、 TPMZ04:外部输入时钟÷4分频后延时信号(16KHz )

5、 TPMZ05:数字锁相环调整信号

注:以上测试点通过JM05测试头引出,测量时请在测试引出板上进行。

JM05的排列如下图所示:

TPMZ01□□TPMZ02

TPMZ03□□TPMZ04

TPMZ05□□TPMZ06

TPMZ07□□

地□□

二、实验仪器

1、Z H5001通信原理综合实验系统一台

2、20MHz双踪示波器一台

3、函数信号发生器一台

三、实验目的

1、了解数字锁相环的基本概念

2、熟悉数字锁相环与模拟锁相环的指标

3、掌握全数字锁相环的设计

四、实验内容

准备工作:将调制方式设在BPSK方式,用函数信号发生器产生一个64KHz的TTL方波信号送入数字数字信号测试端口J007(实验箱左端)。

1.锁定状态测量

用示波器同时测量TPMZ03、TPMZ02的相位关系,测量时用TPMZ03同步;在理论上,环路锁定时该两信号应为上升沿对齐。

2.数字锁相环的相位抖动特性测量

数字锁相环在锁定时,输出信号存在相位抖动是数字锁相环的固有特征。

测量时,以TPMZ03为示波器的同步信号,用示波器测量TPMZ02,仔细调整示波器时基,使示波器刚好容纳TPMZ02的一个半周期,观察其上升沿。

可以观察到其上升较粗(抖动),其宽度与TPMZ02周期的比值的一半即为数字锁相环的时钟抖动。

3.锁定频率测量和分频比计算

将函数信号发生器设置在记数状态(频率计)。

参见数字锁相环的结构如图2.2.1数字锁相环的结构,测量各点频率。

记录测量结果,计算分频比。

4.锁定过程观测

(1)用示波器同时观测TPMZ03、TPMZ02的相位关系,测量时用TPMZ03同步;复位通信原理综合实验系统,则FPGA进行初始化,数字锁相环进行重锁状态。

此

时,观察它们的变化过程(锁相过程)。

(2)用示波器测量TPMZ05波形,复位通信原理综合实验系统,观察调整的变化过程。

5.同步带测量

(1)用函数信号发生器产生一个64KHz的TTL信号送入数字信号测试端口J007。

用示波器同时测量TPMZ03、TPMZ02的相位关系,测量时用TPMZ03同步;正常

时环路锁定,该两信号应为上升沿对齐。

(2)缓慢增加函数信号发生器输出频率,直至TPMZ03、TPMZ02两点波形失步,记录下失步前的频率。

(3)调整函数信号发生器频率,使环路锁定。

缓慢降低函数信号发生器输出频率,直至TPMZ03、TPMZ02两点波形失步,记录下失步前的频率。

(4)计算同步带。

6.捕捉带测量

(1)用函数信号发生器产生一个64KHz的TTL信号送入数字信号测试端口J0007。

用示波器同时测量TPMZ03、TPMZ02的相位关系,测量时用TPMZ03同步;在理

论上,环路锁定时该两信号应为上升沿对齐。

(2)增加函数信号发生器输出频率,使TPMZ03、TPMZ02两点波形失步;然后缓慢降低函数信号发生器输出频率,直至TPMZ03、TPMZ02两点波形同步。

记录下

同步一刻的频率。

(3)降低函数信号发生器输出频率,使TPMZ03、TPMZ02两点波形失步;然后缓慢增加函数信号发生器输出频率,直至TPMZ03、TPMZ02两点波形同步。

记录下

同步一刻的频率。

(4)计算捕捉带。

7.调整信号脉冲观测

(1)用函数信号发生器产生一个64KHz的TTL信号送入数字数字信号测试端口J0007。

用示波器观测数字锁相环调整信号TPMZ05处波形。

(2)增加或降低函数信号发生器输出频率,观测TPMZ05处波形的变化规律。

五、实验报告

1、画出数字锁相环的锁定过程。

2、画出各测量点的波形。

3、分析总结数字锁相环与模拟锁相环同步带和捕捉带的大致关系。