数字锁相环研究

位同步数字锁相环的原理与应用

位同步数字锁相环的原理与应用数字锁相环(Digital Phase-Locked Loop,DPLL)是一种用于同步信号的控制系统。

位同步数字锁相环(Bit Synchronous Digital Phase-Locked Loop)是一种特殊类型的数字锁相环,它主要用于数据通信领域中的时钟恢复和数据恢复。

在数字通信中,时钟信号的同步非常重要。

传输过程中,由于信号经过传输介质会受到噪声、衰减等因素的影响,导致时钟信号的相位和频率发生偏移。

为了恢复信号的正确时钟,就需要使用位同步数字锁相环。

位同步数字锁相环的原理基于相位比较器和数字控制环路。

首先,接收到的信号经过采样,然后由相位比较器将采样的信号与本地时钟信号进行相位比较。

相位比较器输出的误差信号经过数字控制环路进行滤波和调整,最后控制本地时钟信号的相位和频率,使其与接收到的信号保持同步。

位同步数字锁相环广泛应用于数字通信领域中的解调器和调制器设计。

在解调器中,位同步数字锁相环用于恢复接收信号的时钟,确保数据的正确接收。

在调制器中,位同步数字锁相环用于生成发送信号的时钟,确保数据的正确发送。

位同步数字锁相环的应用不仅限于数字通信领域。

它还被广泛应用于数字音频设备、数字视频设备以及其他需要对时钟信号进行同步的领域。

在数字音频设备中,位同步数字锁相环用于恢复音频信号的时钟,确保音频数据的正确传输。

在数字视频设备中,位同步数字锁相环用于恢复视频信号的时钟,确保视频数据的正确显示。

位同步数字锁相环的优点在于精度高、稳定性好、抗干扰能力强。

相对于传统的模拟锁相环,位同步数字锁相环具有更高的抗噪声和抗干扰能力。

同时,由于数字控制环路的设计和实现较为灵活,位同步数字锁相环的性能可以根据具体应用需求进行优化。

位同步数字锁相环是一种用于同步信号的控制系统,广泛应用于数字通信、数字音频、数字视频等领域。

它的原理基于相位比较器和数字控制环路,通过比较相位误差来控制本地时钟的相位和频率,使其与接收到的信号保持同步。

全数字锁相环设计研究

一、引言数字锁相环(DPLL)是一种相位反馈控制系统。

DPLL通常有三个组成模块:数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)。

本文采用超前-滞后型数字锁相环(LL-DPLL)的设计方案,在LL-DPLL中,DLF用双向计数逻辑和比较逻辑实现,DCO采用加扣脉冲式数控振荡器。

这样设计出来的DPLL 具有结构简洁明快,参数调节方便,工作稳定可靠的优点。

二、数字锁相环的分类1.过零型数字锁相环路这种数字锁相环路采用过零采样数字鉴相器,即本地估算信号在输入信号的过零点上采样后进行A/D变换,得到数字相位误差信号输出。

2.触发器型数字锁相环路这类全数字锁相环路使用的数字鉴相器是触发器型数字鉴相器。

其特点是利用输入信号和本地估算信号的正向过零点对触发器进行触发,在触发器的置“ 0”和置“ 1” 的时间间隔内,得到相位误差信号。

置“ 0”和置“ 1”的时间间隔宽度就表征了输入信号和本地估算信号之间的相位误差大小。

3.超前-滞后型数字锁相环路这种数字锁相环路采用的鉴相器是超前-滞后型数字鉴相器。

超前-滞后型数字鉴相器在每一个周期内得到输入信号的相位比本地估算信号相位超前或滞后的信息。

因此,这种鉴相器的相位误差输出只有超前或滞后两种状态。

然后将误差相位的超前或滞后信息送到序列滤波器,产生对DCO的“ 加” 或“ 扣” 脉冲控制指令去改变DCO的时钟周期,使本地估算信号的相位输入信号相位靠拢。

4.奈奎斯特速率采样型数字锁相环路在这种数字锁相环路中,对输入信号的采样按照奈奎斯特速率进行。

也就是说,对输入信号进行A/D变换的采样频率必须按照奈奎斯特速率进行,以使输入信号能够依据奈奎斯特取样定理再现。

A/D变换后的输入信号与本地估算信号进行数字相乘,得到需要的相位误差数字信号,以完成鉴相功能。

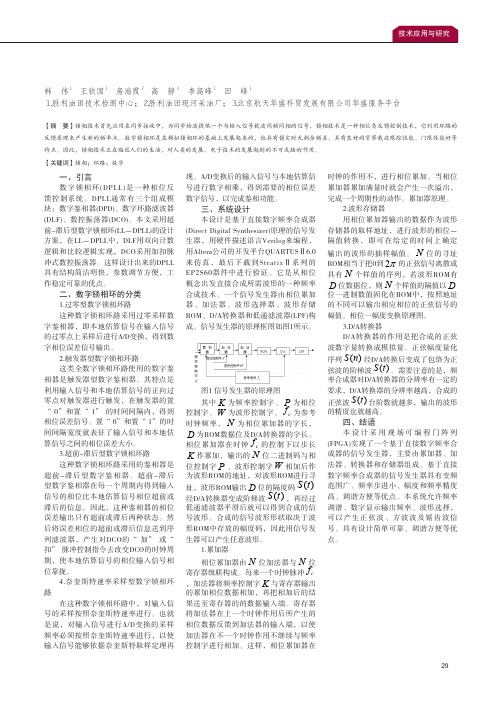

三、系统设计本设计是基于直接数字频率合成器(Direct Digital Synthesizer)原理的信号发生器,用硬件描述语言Verilog来编程,用Altera公司的开发平台QUARTUSⅡ6.0来仿真,最后下载到StratixⅡ系列的EP2S60器件中进行验证。

基于全数字锁相环的时间数字转换器的研究的开题报告

基于全数字锁相环的时间数字转换器的研究的开题报告一、研究背景及意义时间数字转换器是指将时间信号转换为数字信号的电子设备。

在许多应用场合中,需要对时间信号进行高精度的测量和处理,例如雷达、GPS、通信等领域。

时间数字转换器是这些应用的关键组件之一。

传统的时间数字转换器通常采用基于脉冲计数器的方式实现,但其精度和速度都较低。

因此,研究一种新型的高性能时间数字转换器是十分必要的。

本研究拟采用基于全数字锁相环技术的时间数字转换器,该技术是一种先进的数字信号处理技术,可以实现高精度、高速度的时间数字转换,具有很强的应用价值。

同时,该技术在数字时钟、数字信号处理等领域也有广泛的应用,因此其研究对于提高国内技术水平和推动相关领域的发展具有重要意义。

二、研究目标及内容本研究的主要目标是设计一种基于全数字锁相环的高精度时间数字转换器,并进行实现和验证。

具体而言,研究内容包括:1. 建立全数字锁相环的数学模型和仿真模型,并进行性能分析和优化。

2. 设计和实现基于全数字锁相环的时间数字转换器系统,并对其进行可靠性测试和性能评估。

3. 对实现的时间数字转换器进行误差分析和校准,评估其精度和稳定性。

4. 探索时间数字转换器的应用场景,并对其在雷达、GPS、通信等领域的性能进行测试。

三、研究方法本研究主要采用仿真和实验相结合的方法进行,具体包括:1. 利用MATLAB等工具建立基于全数字锁相环的数学模型和仿真模型,并进行性能评估和优化。

2. 设计和实现基于FPGA(Field Programmable Gate Array)的时间数字转换器原型系统,并进行可靠性测试和性能评估。

3. 对实现的时间数字转换器进行误差分析和校准,评估其精度和稳定性。

4. 在实验室中搭建测试平台,对时间数字转换器在雷达、GPS、通信等领域的性能进行测试和验证。

四、研究成果及预期本研究的最终成果为基于全数字锁相环的高精度时间数字转换器,预期达到以下技术水平:1. 时间分辨率达到纳秒级别,误差小于10 ps。

基于F2812的改进型数字锁相环研究

Re s e a r c h a n d De s i g n o f a n I mp r o v e d DP LL Ba s e d o n F2 8 1 2

Ku sh n n a 21 5 3 0 0, J i a n g s u , hi C n a :3 . T a i z h o u El e c t r i c P o we r S u p p l y

C o m p ny a P o w e r D p tc a h i n g C e n t e r , T a i z h o u 2 2 5 3 0 0 , J / ng a s u , C h i n a )

2 . 三 一重机 有 限公 司大型挖 掘机 研 究所 , 江苏 昆山 2 1 5 3 0 0 ; 3 . 泰 州供 电公 司 电力调度 中心 , 江苏 泰 州 2 2 5 3 0 0 )

摘要 : 目前 锁 相 环 方 法 有 过 零 点 检测 法 , 低 通 滤波 器 开 环 锁 相 法 , 幽 变 换 闭环 锁 相 法 和增 强 型锁 相 ( E P L L )

BA I Xu e . f e i , YU C h a n g — mi a o , Z HI Mi n g

f 1 . S c h o o l o fE l e c t r i c a n d E n g i n e e n n g , Y a n c h e n g I n s t i t u t e o f T e c h n o l o g y , Y a n c h e n g 2 2 4 0 0 0 , J i ng a s u , C h i n a : 2 . L a r g e E x c a v a t o r R e s e rc a h I n s t i t u t e o fS nyHe a a v yMa c h i n e r y C o . , L t d . ,

《应用于LVDS的锁相环电路研究》

《应用于LVDS的锁相环电路研究》一、引言随着电子技术的快速发展,高速数据传输在各个领域得到了广泛应用。

作为高速数据传输的重要技术之一,低压差分信号传输(LVDS)以其低功耗、高速度和低噪声的特性,在通信、计算机、医疗和工业控制等领域得到了广泛应用。

锁相环(PLL)电路作为LVDS系统中的关键部分,其性能的优劣直接影响到整个系统的性能。

因此,对应用于LVDS的锁相环电路进行研究具有重要的现实意义。

二、锁相环电路的基本原理锁相环电路是一种利用反馈原理实现相位自动跟踪的电路。

它主要由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成。

鉴相器用于检测输入信号与反馈信号之间的相位差;环路滤波器用于滤除鉴相器输出中的高频噪声和干扰,使控制电压稳定;压控振荡器根据控制电压调整输出信号的频率和相位,以达到锁定相位的目的。

三、应用于LVDS的锁相环电路设计在LVDS系统中,锁相环电路的设计需要考虑到传输速率、功耗、噪声等因素。

因此,设计一款适用于LVDS的锁相环电路,需要从以下几个方面进行考虑:1. 鉴相器的设计:鉴相器是锁相环的核心部分,其性能直接影响到整个系统的性能。

在LVDS系统中,常用的鉴相器有零交鉴相器和边沿鉴相器等。

其中,边沿鉴相器具有较好的抗干扰能力和较高的灵敏度,适用于LVDS系统的高速传输。

2. 环路滤波器的设计:环路滤波器的作用是滤除鉴相器输出中的高频噪声和干扰,使控制电压稳定。

在LVDS系统中,常用的环路滤波器有RC滤波器和数字滤波器等。

其中,数字滤波器具有更高的稳定性和更小的误差,适用于高精度要求的LVDS系统。

3. 压控振荡器的设计:压控振荡器是锁相环的输出部分,其性能直接影响到系统的跟踪性能和锁定时间。

在LVDS系统中,压控振荡器的设计需要考虑到其输出频率的稳定性和相位噪声等因素。

四、锁相环电路的性能分析对于应用于LVDS的锁相环电路,其性能分析主要包括锁定时间、相位噪声、抖动等方面。

通信电子中的数字PLL技术

通信电子中的数字PLL技术数字PLL技术,即数字锁相环技术,是现代通信电子领域中的一种重要技术。

数字PLL技术通过数字信号处理与锁相环技术相结合,可以实现高效、快速的信号同步与频率稳定控制。

今天,我们将探讨数字PLL技术在通信电子领域中的应用与发展。

一、数字PLL技术的基本原理数字PLL技术利用数字信号处理的方法代替了传统锁相环中的模拟部分结构,使得信号同步与频率控制的过程更为精确和稳定。

数字PLL主要包含三个部分:比较器、数字滤波器和数字控制器。

1、比较器比较器是数字PLL中最基本的核心单元,它将输入信号与参考信号进行比较,产生一个相位误差信号。

比较器的工作原理类似于模拟锁相环中的相频检测器,但是其精度更高,稳定性更强。

2、数字滤波器数字滤波器的作用是对比较器输出的数字误差信号进行滤波和放大,从而产生PLL控制电压。

数字滤波器和模拟滤波器一样,可以是低通滤波器、带通滤波器或高通滤波器。

3、数字控制器数字控制器的作用是根据控制算法(如PI控制算法)对滤波器输出进行数值处理,产生相位频率控制电压。

数字控制器可以使用通用数字信号处理器(DSP)或现场可编程门阵列(FPGA)实现。

二、数字PLL技术在通信电子领域中的应用1、数字PLL在移动通信中的应用数字PLL技术在移动通信系统中的应用非常广泛,例如在LTE (Long Term Evolution)无线通信系统中,数字PLL常用于频率同步和时序同步。

LTE系统中,使用不同的数字PLL技术(如多分频数字PLL、分数阶数字PLL等)可以实现不同的同步精度以及响应速度。

2、数字PLL在卫星导航中的应用数字PLL技术在卫星导航系统中的应用也非常广泛,例如GPS (Global Positioning System)系统中使用的数字PLL可以实现卫星信号的同步和频率稳定控制。

此外,数字PLL技术也常用于卫星通信系统中的频率同步和多路访问控制。

3、数字PLL在光通信中的应用数字PLL技术在光通信中的应用也非常重要,例如在光纤通信系统中,数字PLL常用于众多红外端用、透明传输和数字滤波技术中。

全数字锁相环的设计及分析

全数字锁相环的设计及分析1 引言锁相环是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,震荡器的输出信号与系统输入信号之间相差为零,或者保持为常数。

传统的锁相环各个部件都是由模拟电路实现的,一般包括鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)三个环路基本部件。

随着数字技术的发展,全数字锁相环ADPLL(AllDigital Phase-Locked Loop)逐步发展起来。

所谓全数字锁相环,就是环路部件全部数字化,采用数字鉴相器、数字环路滤波器、数控振荡器构成锁相环路,并且系统中的信号全是数字信号。

与传统的模拟电路实现的锁相环相比,由于避免了模拟锁相环存在的温度漂移和易受电压变化影响等缺点,从而具备可靠性高、工作稳定、调节方便等优点。

全数字锁相环的环路带宽和中心频率编程可调,易于构建高阶锁相环,并且应用在数字系统中时,不需A/D及D/A转换。

在调制解调、频率合成、FM立体声解码、图像处理等各个方面得到广泛的应用。

随着电子设计自动化(EDA)技术的发展,可以采用大规模可编程逻辑器件(如CPLD或FPGA)和VHDL语言来设计专用芯片ASIC和数字系统。

本文完成了全数字锁相环的设计,而且可以把整个系统嵌入SoC,构成片内锁相环。

2全数字锁相环的体系结构和工作原理74XX297 是出现最早,应用最为广泛的一款全数字锁相环,在本文中以该芯片为参考进行设计、分析。

ADPLL基本结构如图1所示,主要由鉴相器、K变模可逆计数器、脉冲加减电路和除N计数器4部分构成。

K变模计数器和脉冲加减电路的时钟分别为Mfc和2Nfc。

这里fc是环路中心频率,一般情况下M和N都是2的整数幂。

2.1 鉴相器常用的鉴相器有两种类型:异或门(XOR)鉴相器和边沿控制鉴相器(ECPD)。

异或门鉴相器比较输入信号Fin相位和输出信号Fout相位之间的相位差θe,并输出误差信号Se作为K变模可逆计数器的计数方向信号。

数字锁相环原理

数字锁相环原理数字锁相环(Digital Phase-Locked Loop,简称数字PLL)是一种广泛应用于通信、控制系统中的数字信号处理器。

它可以实现信号的频率和相位同步,对于数字通信系统中的时钟恢复、频率合成、信号解调等功能起着至关重要的作用。

本文将介绍数字锁相环的基本原理及其在通信系统中的应用。

数字锁相环由相位比较器、数字控制振荡器(DCO)、数字滤波器和锁定检测器组成。

其中,相位比较器用于比较输入信号和反馈信号的相位差,产生一个误差信号;数字控制振荡器根据误差信号调整输出频率;数字滤波器用于滤除噪声和抖动;锁定检测器用于检测数字锁相环是否已经锁定。

数字锁相环的工作原理可以简单描述为,首先,输入信号经过频率除法器和相位频率检测器,产生一个误差信号;然后,误差信号经过数字滤波器滤除噪声,再经过数字控制振荡器产生输出信号;最后,输出信号经过反馈回到相位比较器,形成闭环控制。

在闭环控制下,数字锁相环可以实现输入信号和输出信号的频率和相位同步。

数字锁相环在通信系统中有着广泛的应用。

在数字调制解调中,数字锁相环可以实现信号的时钟恢复和频率合成,保证接收端对发送端信号的准确解调;在频率合成器中,数字锁相环可以实现高稳定性的频率合成,满足通信系统对频率精度的要求;在通信系统中,数字锁相环还可以用于时钟同步和信号重构等功能。

总之,数字锁相环作为一种重要的数字信号处理器,在通信系统中有着广泛的应用。

它通过闭环控制实现输入信号和输出信号的频率和相位同步,保证了通信系统的稳定性和可靠性。

随着通信技术的不断发展,数字锁相环的应用范围将会更加广泛,对于提高通信系统的性能起着至关重要的作用。

通过本文的介绍,相信读者对数字锁相环的原理及其在通信系统中的应用有了更深入的了解。

数字锁相环作为一种重要的数字信号处理器,其原理简单而又实用,对于提高通信系统的性能有着重要的意义。

希望本文能对读者有所帮助,谢谢阅读!。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字锁相环研究刘飞雪摘要:全数字锁相环路,所谓全数字化,就是环路部件全部数字化,采用数字鉴相器(DPD)、数字环路滤波器(DLF)和数控振荡器(DCO)构成的锁相环路。

同步是通信系统中的一个重要实际问题。

在数字通信系统中,位同步(又称码元同步)提取是更为重要的一个环节。

因为确定了每一个码元的起始时刻,便可以对数字信息做出正确判决。

利用全数字锁相环(DPLL)便可以直接从所接收的数字信号中提取位同步信号。

用来实现位时钟同步提取的主要是超前—滞后型数字锁相环(LL-DPLL)。

本文通过对全数字锁相环的种类及其相应实现功能的研究,确定了对位同步全数字锁相环路的设计方案,设计位同步全数字锁相环各个模块,本文中设计了3个模块,其中第2块包含2个小模块,第3块又包含3 个小模块,用Verilog HDL硬件描述语言对系统中的每个模块进行描述、仿真,然后将三个模块连接成反馈环路系统,使用仿真工具QuartusⅡ6.0进行编译、仿真,调试输出正确波形,最后分析电路性能。

关键词:全数字锁相环路,位同步数字锁相环路,超前-滞后型数字锁相环,数字鉴相器,数字滤波器,数控振荡器AbstractAll Digital Phase-Locked Loop is called because every module is digital. The loop contains these modules such as Digital Phase Discriminator (DPD), Digital Loop Frequency (DLF), Digital Control Oscillator (DCO).The synchronization is the key part of application in communication systems. In the field of digital communication systems, pick-up bit synchronization (also called code synchronization) is a more important part., because the definition of originate time of every code could make correct judgement. The usage of Digital Phase-Locked Loop (DPLL) could pick-up bit synchronous signal from digital signal directly. We use Lead-Lag Digital Phase-Locked Loop (LL-DPLL) to realize bit synchronous clock.This paper first introduced DPLL kinds and function. Then it designed the theory and every modules of DPLL. This paper designed three modules. In it, the second contained 2 modules and the third contained 3 modules. Using Verilog HDL to describe and simulate every module of the system, then connecting these modules to realize the system and using simulator named QuartusⅡ6.0 to compile and simulate correct wave.Key word: DPLL, bit synchronous DPLL, LL-DPLL,DPD, DLF, DCO第一章绪论1.1 全数字锁相环的背景及发展状况锁相环路已经在模拟和数字通信及无线电电子学的各个领域得到了极为广泛的应用。

伴随着大规模、超高速数字集成电路的发展及计算机的普遍应用,在传统的模拟锁相环路(APLL)应用领域中,一部分已经被数字锁相环路(DPLL)所取代。

从六十年代起,人们就开始对数字锁相环路研究。

起初,只是把模拟锁相环路中的部分部件数字化。

比如,引进数控振荡器(DCO)代替模拟锁相环路中的压控振荡器(VCO)。

这样做的优点是能在不牺牲压控振荡器频率稳定度的情况下,加大频率牵引的范围。

从而提高整个环路的工作稳定性和可靠性。

另外,用数字集成电路制作的鉴相器非常广泛的被应用在模拟锁相环路中,使环路性能大大提高。

此后,出现了全数字化锁相环。

所谓全数字化,就是环路部件全部数字化,采用数字鉴相器(DPD)、数字环路滤波器(DLF)和数控振荡器(DCO)构成的锁相环路。

目前,全数字锁相环路的研究日趋成熟,无论在理论研究还是在硬件实现方面,国内外均有大量的文献报道。

并已经制成全数字化锁相环路FSK信号解调器、PSK信号解调器、位时钟提取器以及同步载波提取器等。

国外已有单片全数字化锁相环路商品。

全数字化锁相环路的共同特点是:它们都具有一切数字系统所特有的显著优点,即电路完全数字化,使用逻辑门电路和触发器电路。

因此,系统只有“导通”、“截止”两种工作状态,受外界和电源干扰的可能性大大减小,电路容易集成,易于制成全集成的单片全数字锁相环路。

因而,系统可靠性大大提高。

除此之外,全数字化锁相环还缓和或消除了模拟锁相环路中电压控制振荡器(VCO)的非线性以及环路中由于使用运算放大器和晶体管而出现的饱和以及运算放大器和鉴相器的零漂移等对环路性能的影响。

全数字锁相环路的另一个突出优点是:它的环路部件甚至整个环路都可以直接用微处理机来模拟实现。

值得提出的是,全数字锁相环路目前还只是在频率较低的场合中应用,例如副载波解调这类低数据速率和低频的情况。

其主要原因是因为其硬件的实现受到数字集成电路逻辑速度的限制。

但我们应该意识到,这是暂时的,随着数字集成电路逻辑速度的提高,将会使全数字锁相环路的应用越来越广泛。

正因为这样,目前,数字锁相环(部分环路部件数字化)在某些场合的应用也越来越普遍。

1.2 传统锁相环介绍锁相环是一个闭环的相位控制系统,本文主要研究数字锁相环,这部分首先介绍与之有关的概念。

一个完整的锁相环包括鉴相器,滤波器,压控振荡器三部分。

通过对输入信号和本地反馈信号的比较鉴相,最终实现信号同步的一个闭环系统1.2.1鉴相器:理想的鉴相器输出一个信号,它的直流电压值正比于两个输入周期信号的相位差,如下图示:最简单的鉴相器是一个异或门,如图2-8所示,当两个输入信号相位差变化时,输出脉冲的宽度也在变,因此可以提供一个正比于相位变化的直流电压。

如图示。

1.2.2 环路滤波器环路滤波器具有低通特性,在锁相环中起低通滤波的作用,更重要的是它对整个环路系统参数调整有着决定性的作用。

现代锁相环中的环路滤波器种类很多,有RC积分滤波器、无源比例积分滤波器和有源比例积分滤波器。

为了简单起见,便于分析锁相环环路,这里先介绍简单的RC积分滤波器R积分滤波器是结构最简单的低通滤波器,电路构成如图:简单的RC滤波器RC滤波器的幅频相频特性1.2.3 压控振荡器一个理想的压控振荡器输出周期信号,这周期信号的频率与压控振荡器的控制电压vl呈线性关系。

实际中压控振荡器增益是非线性的,一般压控振荡器的振荡频率是有上下限的,当控制电压不断增加或减小时,增益就会趋向于零,如图压控振荡器的控制特性第二章全数字锁相环所谓全数字化,就是环路部件全部数字化,采用数字鉴相器(DPD)、数字环路滤波器(DLPO ),数控振荡器(DCO)构成的锁相环路。

全数字锁相环路的一个突出优点是,它的环路部件甚至整个环路都可以直接用软件来模拟实现。

在这里我们将使用QuartusⅡ6.0仿真工具,以位同步锁相环为例来进行全数字锁相环的仿真模拟。

2.1位同步锁相环的作用位同步,或称码元同步,是要在接收端确定每一个码元的起止时刻。

它是数字通信诸多同步之中的首要问题,没有位同步就无从解出传输的数字信息。

若在传送数字信号的同时,再专门传送一个位同步信号,如直接传送时钟信号或传送用作同步的伪随机序列等,这称为外同步法。

由于位同步信号与通信的数字信号是同时传送的,有相同的信道延时,因而同步是准确的。

但位同步信号要占用信道,占去一定的功率,这种方法不太经济。

虽然数字信号自身可能并不含有位速率的频谱成分,但却含有位速率的信息,因此用专门设计的电路系统可将位同步信号提取出来,这就是自同步法。

自同步法可以用特殊设计的锁相环路来直接从接收的码元序列中提取位同步信号。

位同步锁相环的基本结构如下图所示:位同步锁相环的基本结构2.2 超前滞后型鉴相器的设计导前一滞后型数字鉴相器的特点是,它输出一个表示本地估算信号导前或滞后于输入信号的量。

如果本地估算信号超前于输入信号,则输出“超前脉冲”,以便利用该“超前脉冲”控制本地估算信号的相位推后。

反之,则输出“滞后脉冲”,并使本地估算信号的相位前移。

导前一滞后型数字鉴相器可分为微分型和积分型两种。

微分型数字鉴相器结构简单,硬件实现也比较简单。

但是它的抗干扰能力比较差。

而积分型导前一滞后数字鉴相器具有优良的抗干扰性能,但结构和硬件实现比较复杂。

我们的设计采用微分型导前一滞后型数字鉴相器。

它的基本框图如图示:微分型导前滞后鉴相器原理图在本文中我们用VerilogHDL硬件描述语言进行软件设计,鉴相器部分代码如下://the following is the weifen phase detector//module wphd(lclk,inclk,xclk,up,down);//lclk为本地估算时钟,inclk为输入码流,xclk为本地高速时钟input lclk,inclk,xclk;output up,down;wire out;reg up,down;reg a,b;always@(posedge xclk)begina<=inclk;b<=a;up<=out&lclk;down<=out&(~lclk);endassign out=(a^b)&&(b==0);endmodule仿真图:由仿真图可以看出,当本地时钟相位超前于输入码流时,输出超前信号UP,滞后时输出滞后信号DOWN.2.3数字环路滤波器(DLF)在数字锁相环中,环路滤波器通常使用数字滤波器,它和模拟锁相环中的模拟滤波器相对应。