数字电子技术基础第五版第7章

阎石《数字电子技术基础》(第5版)笔记和课后习题(含考研真题)详解(7-11章)【圣才出品】

圣才电子书 十万种考研考证电子书、题库视频学习平台

存储矩阵中选出指定单元,并把其中数据送到输出缓冲器。 (3)输出缓冲器的作用是提高存储器带负载能力,实现对输出状态的三态控制,便与 系统的总线连接。

图 7-1 ROM 的电路结构框图

2.可编程只读存储器(PROM) PROM 初始时所有存储单元中都存入了 1,可通过将所需内容自行写入 PROM 而得到 要求的 ROM。PROM 的总体结构与掩模 ROM 一样,同样由存储矩阵、地址译码器和输出 电路组成。 PROM 的内容一经写入以后,就不可能修改了,所以它只能写入一次。因此,PROM 仍不能满足研制过程中经常修改存储内容的需要。

3 / 127

圣才电子书 十万种考研考证电子书、题库视频学习平台

分组成,如图 7-4 所示。 ①存储矩阵由许多存储单元排列而成,每个存储单元能存储 1 位二值数(1 或 0),既 可以写入 1 或 0,又可以将存储的数据读出; ②地址译码器一般都分成行地址译码器和列地址译码器。行地址译码器将输入地址代码 的若干位译成某一条字线的输出高、低电平信号,从存储矩阵中选中一行存储单元;列地址 译码器将输入地址代码的其余几位译成某一根输出线上的高、低电平信号,从字线选中的一 行存储单元中再选 1 位(或几位),使这些被选中的单元经读/写控制电路与输入/输出端接 通,以便对这些单元进行读、写操作;

圣才电子书 十万种考研考证电子书、题库视频学习平台

第 7 章 半导体存储器

7.1 复习笔记

一、概述 半导体存储器是一种能存储大量二值信息(或称为二值数据)的半导体器件。半导体存 储器的种类很多,从存、取功能上可以分为只读存储器(ROM)和随机存储器(RAM)。 只读存储器在正常工作状态下只能从中读取数据,不能快速地随时修改或重新写入数 据。ROM 的优点是电路结构简单,而且在断电以后数据不会丢失。它的缺点是只适用于存 储那些固定数据的场合。只读存储器中又有掩模 ROM、可编程 ROM(PROM)和可擦除 的可编程 ROM(EPROM)几种不同类型。 随机存储器与只读存储器的根本区别在于,正常工作状态下就可以随时快速地向存储器 里写入数据或从中读出数据。根据所采用的存储单元工作原理的不同,又将随机存储器分为 静态存储器(SRAM)和动态存储器(DRAM)。

(数字电子技术)第7章数模与模数转换

第7章 数/模与模/数转换

7.1 概述 7.2 数/模转换 7.3 模/数转换 7.4 本章小结 7.5 例题精选 7.6 自我检测题

第7章 数/模与模/数转换

7.1 概 述

随着以数字计算机为代表的各种数字系统的广泛普及和 应用,模拟信号和数字信号的转换已成为电子技术中不可或 缺的重要组成部分。数/模转换指的是把数字信号转换成相 应的模拟信号,简称D/A转换,同时将实现该转换的电路称 为D/A转换器,简称DAC;模/数转换指的是把模拟信号转 换为数字信号,简称A/D转换,并将实现该转换的电路称为 A/D转换器,简称ADC。

当Rf=R时

uo=

uR 2n

n-1

di zi

i= 0

由上式可以看出,此电路完成了从数字量到模拟量的转 换,并且输出模拟电压正比于数字量的输入。

第7章 数/模与模/数转换

2. 集成DAC电路AD7524 AD7524(CB7520)是采用倒T型电阻网络的8位并行D/A 转换器,功耗为20 mW,供电电压UDD为5~15 V。 AD7524典型实用电路如图7.2.5所示。

第7章 数/模与模/数转换

7.3.4 常见的ADC电路

1. 逐次逼近型ADC 逐次逼近型ADC是按串行方式工作的,即转换器输出 的各位数码是逐位形成的。图7.3.6为原理框图,该电路由电 压比较器、逻辑控制器、D/A转换器、逐次逼近寄存器等组 成。

第7章 数/模与模/数转换

图 7.3.6 பைடு நூலகம்次逼近型ADC原理图

第7章 数/模与模/数转换

(2) 四舍五入法:取最小量化单位Δ=2Um/(2n-1-1), 量化时将0~Δ/2之间的模拟电压归并到0·Δ,把Δ/2~3·Δ/2之 间的模拟电压归并到1·Δ,依此类推,最大量化误差为Δ/2。 例如,需要把0~+1 V之间的模拟电压信号转换为3位二进制 代码,这时可取Δ=(2/15)V,那么0~(1/15)V之间的电压就 归并到0·Δ,用二进制数000表示;数值在(1/15)~(3/15)V之 间的电压归并到1·Δ,用二进制数001表示,并依此类推,如 图7.3.5(b)

精品课件-数字电子技术-第7章

(D3 23 +D2

22

+D121+D0 20 )

(7.1.2)

第7章 数/模(D/A)与模/数(A/D)转换器

对于n位输入的权电阻网络D/A转换器, 当负反馈电阻取 为R/2时, 输出电压为

vO

=

VREF 2n

(Dn1 2n1 +Dn2 2n2 + …

+D121+D0 20 )

=

VREF 2n

第7章 数/模(D/A)与模/数(A/D)转换器

第7章 数/模(D/A)与模/数(A/D)转换器

7.1 D/A转换器 7.2 A/D转换器 7.3 集成D/A转换器Multisim 10仿真实验 实验与实训 本章小结 习题

第7章 数/模(D/A)与模/数(A/D)转换器

7.1 D/A 7.1.1 权电阻网络D/A

第7章 数/模(D/A)与模/数(A/D)转换器

由图7.1.2所示电路还可以看出, 由于工作在线性反相 输入状态的运算放大电器的反相输入端相当于接地(虚地), 所以无论模拟开关Si合于何种位置, 与Si相连的倒T型2R电阻 支路从效果上看总是接“地”的, 即流经每条倒T型2R电阻 支路的电流与模拟开关Si的状态无关; 从R—2R倒T型电阻网 络的A、 D、 C、 D每个节点向左看, 每个二端网络的等效 电阻均为R, 故从基准电压UREF输出的电流恒为I=UREF/R, 而流经倒T型2R电阻支路的电流从高位到低位按2的负整数幂 递减, 从右到左分别为I3=I/2, I2=I/4, I1=I/8 , I0=I/16。

第7章 数/模(D/A)与模/数(A/D)转换器

由图7.1.2所示电路, 有

iΣ =I3 +I2 +I1+I0

电子教案《数字电子技术(第5版_杨志忠)》教学资源第7章练习题参考答案

C1

已知 R3 = 3 、 kΩ R2 = 3 6 、 kΩ C1 = 0 1 μF, 将 这 些 参 数 代 入 上 式 进 行 计 算, 并 求 出

tw2 = 0 7R2 C = 0 7 × 24 × 103 × 0 1 × 10 - 6 s = 1 68 ms

所以

( ) f =

1 2 73 + 1 68

× 10 - 3 Hz≈226 75 Hz

(2) 画 uC 和 uO 的波形,见图[题 7 8]。

(3) RD端加停振信号。当在置 0 端RD加上低电平时,多谐振荡器被强迫停止振荡。

(2) 对应画出 uI、uC 和 uO 的电压波形。 [解] (1) 求输出电压 uO 的脉冲宽度 tw

tw = 1 1RC = 1 1 × 33 × 103 × 0 1 × 10 - 6 s = 3 63 ms

(2) 对应画出 uI、uC 和 uO 的电压波形,如图[题 7 7]所示。

波形。试求:

(1 (2

) )

计 画

算 出

输

uI

出脉 、ud

冲的 和u

宽O 的度波tw形。。

第 7 章 脉冲信号的产生与整形 145

图 P7 3

(3) 输入脉冲的下限幅度为多大? [解] (1) 求输出脉冲宽度 tw

tw = 1 1RC = 1 1 × 27 × 103 × 0 01 × 10 - 6 s≈297μs

R min

=

tw(min) = 0 7C 0

7

10 × 10 - 6 × 0 01 × 10

- 6 Ω≈1428

57Ω

(2) 求最大值电阻 Rmax

R max

=

tw(max) = 0 7C

数字电子技术及应用教程第7章 数模与模数转换电路

内容提要:

本章系统地讲述了数字量转换模拟量和模拟量 转换数字量的基本原理以及几种常用典型电路。在 数字模拟转换器中,主要讲解权电阻网络数模转换 与倒 T 形数模转换电路。在模数转换器中,对模数 转换的步骤、取样定理进行详细的说明,然后又介 绍了并行比较型、逐次渐近型和双积分型三种各具 特色的模数转换电路。

7.2.5 集成DAC及其应用举例

常 用 的 集 成 DAC 有 AD7520 、 DAC0832 、 DAC0808 、 DAC1230 、 MC1408 等 , 这 里 仅 对 AD公司生产的AD7520作简要介绍。 如图 7.2.7 所示的电路为 AD7520 组成的锯齿波 发生器,其原理为10位二进制加法计数器从全0加 到全 1 ,电路的模拟输出电压 uo 由 0V 逐渐增加到 最大值。如果计数脉冲不断,则可在电路的输出 端得到周期性的锯齿波。

图7.3.7 积分型ADC的电路原理图

2.工作原理

转换开始前,先将计数器清零,接通S2使电容 C完全放电。转换开始时,断开S2。整个转换过程 分为两个阶段进行。其工作波形如图7.3.8所示。

图7.3.8 双积分型A/D转换器各点工作波形

7.3.5 ADC的转换精度和转换速度 1.ADC的转换精度

如图7.3.5为3位并行比较型A/D转换原理电路, 它由电压比较器、寄存器和优先编码器三部分组成。

图7.3.5 3位并行比较型A/D转换原理电路

7.3.3 逐次渐近型ADC 逐次渐近型A/D转换器属于直接型A/D转换器, 它能把输入的模拟电压直接转换为输出的数字代码。 逐次渐近型A/D转换器框图如图7.3.5所示,它 由控制逻辑电路、寄存器、电压比较器及D/A转换 器组成。

图7.3.10 ADC0809引脚图

《数字电子技术基础》课后习题答案

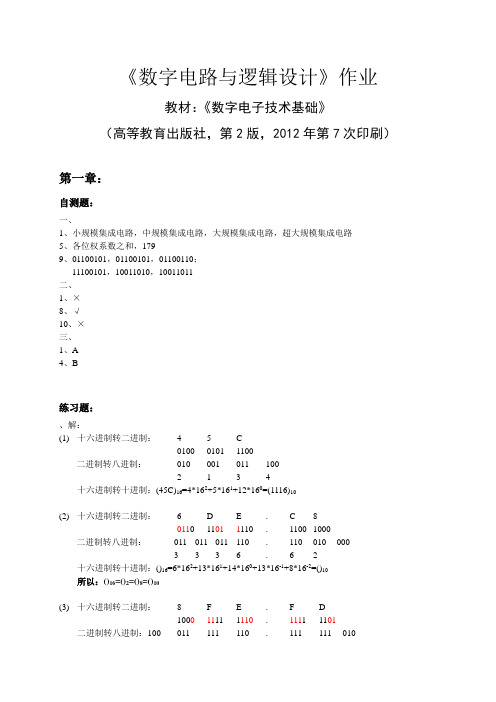

《数字电路与逻辑设计》作业教材:《数字电子技术基础》(高等教育出版社,第2版,2012年第7次印刷)第一章:自测题:一、1、小规模集成电路,中规模集成电路,大规模集成电路,超大规模集成电路5、各位权系数之和,1799、01100101,01100101,01100110;11100101,10011010,10011011二、1、×8、√10、×三、1、A4、B练习题:、解:(1) 十六进制转二进制: 4 5 C0100 0101 1100二进制转八进制:010 001 011 1002 13 4十六进制转十进制:(45C)16=4*162+5*161+12*160=(1116)10(2) 十六进制转二进制: 6 D E . C 80110 1101 1110 . 1100 1000 二进制转八进制:011 011 011 110 . 110 010 0003 3 3 6 . 6 2十六进制转十进制:()16=6*162+13*161+14*160+13*16-1+8*16-2=()10所以:()16=()2=()8=()10(3) 十六进制转二进制:8 F E . F D1000 1111 1110. 1111 1101二进制转八进制:100 011 111 110 . 111 111 0104 3 7 6 . 7 7 2十六进制转十进制:(8FE.FD)16=8*162+15*161+14*160+15*16-1+13*16-2=(2302.98828125)10 (4) 十六进制转二进制:7 9 E . F D0111 1001 1110 . 1111 1101二进制转八进制:011 110 011 110 . 111 111 0103 6 3 6 . 7 7 2十六进制转十进制:(79E.FD)16=7*162+9*161+14*160+15*16-1+13*16-2=(1950. 98828125)10 所以:()16.11111101)2=(363)8=(1950.98828125)10、解:(74)10 =(0111 0100)8421BCD=(1010 0111)余3BCD(45.36)10 =(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001 )余3BCD(136.45)10 =(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000 )余3BCD (374.51)10 =(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD、解(1)(+35)=(0 100011)原= (0 100011)补(2)(+56 )=(0 111000)原= (0 111000)补(3)(-26)=(1 11010)原= (1 11101)补(4)(-67)=(1 1000011)原= (1 1000110)补第二章:自测题:一、1、与运算、或运算、非运算3、代入规则、反演规则、对偶规则二、2、×4、×三、1、B3、D5、C练习题:2.2:(4)解:(8)解:2.3:(2)证明:左边=右式所以等式成立(4)证明:左边=右边=左边=右边,所以等式成立(1)(3)2.6:(1)2.7:(1)卡诺图如下:BCA00 01 11 100 1 11 1 1 1所以,2.8:(2)画卡诺图如下:BC A 0001 11 100 1 1 0 11 1 1 1 12.9:如下:CDAB00 01 11 1000 1 1 1 101 1 111 ×××10 1 ××2.10:(3)解:化简最小项式:最大项式:2.13:(3)技能题:2.16 解:设三种不同火灾探测器分别为A、B、C,有信号时值为1,无信号时为0,根据题意,画卡诺图如下:BC00 01 11 10A0 0 0 1 01 0 1 1 1第三章:自测题:一、1、饱和,截止7、接高电平,和有用输入端并接,悬空;二、1、√8、√;三、1、A4、D练习题:、解:(a)Ω,开门电阻3kΩ,R>R on,相当于接入高电平1,所以(e) 因为接地电阻510ΩkΩ,R<R off,相当于接入高电平0,所以、、解:(a)(c)(f)、解: (a)、解:输出高电平时,带负载的个数2020400===IH OH OH I I N G 可带20个同类反相器输出低电平时,带负载的个数78.1745.08===IL OL OL I I NG反相器可带17个同类反相器EN=1时,EN=0时,根据题意,设A为具有否决权的股东,其余两位股东为B、C,画卡诺图如下,BC00 01 11 10A0 0 0 0 01 0 1 1 1则表达结果Y的表达式为:逻辑电路如下:技能题::解:根据题意,A、B、C、D变量的卡诺图如下:CD00 01 11 10AB00 0 0 0 001 0 0 0 0 11 0 1 1 1 10 0 0 0 0电路图如下:第四章:自测题:一、2、输入信号,优先级别最高的输入信号7、用以比较两组二进制数的大小或相等的电路,A>B 二、 3、√ 4、√ 三、 5、A 7、C练习题:4.1;解:(a),所以电路为与门。

数字电子技术基础习题册答案

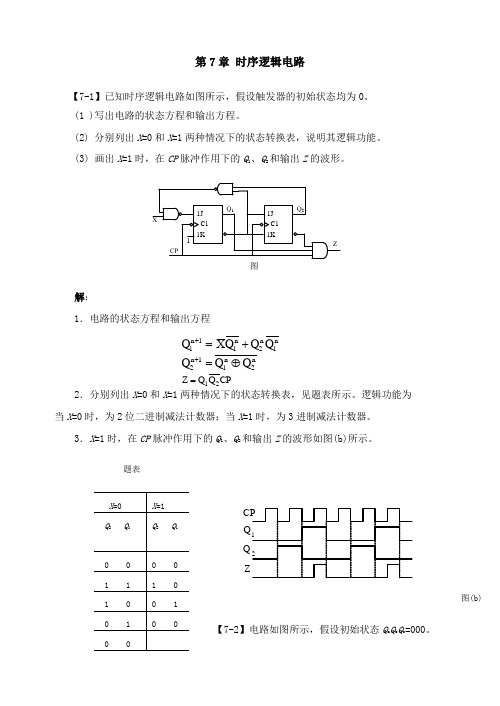

第7章 时序逻辑电路【7-1】已知时序逻辑电路如图所示,假设触发器的初始状态均为0。

(1 )写出电路的状态方程和输出方程。

(2) 分别列出X =0和X =1两种情况下的状态转换表,说明其逻辑功能。

(3) 画出X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形。

1J 1KC11J 1KC1Q 1Q 2CPXZ1图解:1.电路的状态方程和输出方程n 1n2n 11n 1Q Q Q X Q +=+n 2n 11n 2Q Q Q ⊕=+ CP Q Q Z 21=2.分别列出X =0和X =1两种情况下的状态转换表,见题表所示。

逻辑功能为 当X =0时,为2位二进制减法计数器;当X =1时,为3进制减法计数器。

3.X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形如图(b)所示。

题表Q Q Z图(b)【7-2】电路如图所示,假设初始状态Q a Q b Q c =000。

(1) 写出驱动方程、列出状态转换表、画出完整的状态转换图。

(2) 试分析该电路构成的是几进制的计数器。

Q c图解:1.写出驱动方程1a a ==K J ncn a b b Q Q K J ⋅== n b n a c Q Q J = n a c Q K = 2.写出状态方程n a 1n a Q Q =+ n a n a n a n a n c n a 1n b Q Q Q QQ Q Q +=+ nc n a n c n b n a 1n b Q Q Q Q Q Q +=+3.列出状态转换表见题表,状态转换图如图(b)所示。

图7.2(b)表7.2状态转换表CP na nbc Q Q Q 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 16 0 0 0n4.由FF a 、FF b 和FF c 构成的是六进制的计数器。

【7-3】在二进制异步计数器中,请将正确的进位端或借位端(Q 或Q )填入下表解:题表7-3下降沿触发 由 Q 端引出进位 由Q 端引出借位触发方式 加法计数器 减法计数器上升沿触发 由Q 端引出进位 由Q 端引出借位【7-4】电路如图(a)所示,假设初始状态Q 2Q 1Q 0=000。

数字电子技术基础第五版

(1000 1111 1010 1100 0110 )2

《数字电子技术基础》第五版

五、八进制数与二进制数的转换

例:将(011110.010111)2化为八进制

(011 110. 010 111 )2

(3 6 . 2 7)8

例:将(52.43)8化为二进制

(5

2 . 4

3)8

(101 010 . 100 011 )2

《数字电子技术基础》第五版

《数字电子技术基础》(第五版)教学课件

清华大学 阎石 王红

联系地址:清华大学 自动化系 邮政编码:100084 电子信箱:wang_hong@ 联系电话:(010)62792973

《数字电子技术基础》第五版

第一章

数制和码制

《数字电子技术基础》第五版

1 2 3 4 7

k n 2 n1 k n1 2 n 2 k1 2( k n 2 n 2 k n1 2 n3 k 2 ) k1

0

故 (173)10 (10101101 )2

5 6

《数字电子技术基础》第五版

二、十-二转换

1 2 m ( S ) k 2 k 2 k 2 10 1 2 m 小数部分: 左右同乘以 2

1.1 概述 数字量和模拟量

• 数字量:变化在时间上和数量上都是不连 续的。(存在一个最小数量单位△) • 模拟量:数字量以外的物理量。 • 数字电路和模拟电路:工作信号,研究的 对象,分析/设计方法以及所用的数学工具 都有显著的不同

《数字电子技术基础》第五版

数字量和模拟量

• 电流值来表示信息

《数字电子技术基础》第五版

1.4二进制数运算

1.4.2 反码、补码和补码运算

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

* 工作原理: 向G f 充电利用雪崩注入方式, D − S加正压( V),Vss 接0 6 Gc 加12V, us的正脉冲 10

G f 放电,利用隧道效应 G c = 0 , V ss 加12V ,100 ns 的正脉冲 G f 上电荷经隧道区放电

7.3 随机存储器RAM 随机存储器RAM

7.3.1 静态随机存储器(SRAM) 静态随机存储器(SRAM) 一、结构与工作原理

工作原理: G f 充电荷后 , 正常读出 GC电压 (3V )下, T截止 未充电荷时 , 正常读出 GC电压 (3V )下, T导通

充电: Wi , GC 加20V ,10 ms 的正脉冲, B j 接 0 电子隧道区 → G f

放电:GC 接0,Wi , B j 加正脉冲, G f 上电荷经隧道区放电

数据线: O0 ~ I O7 I 地址线:A0 ~ A7 读/写信号: W ′ R 片选信号:CS ′

数据线: O0 ~ I O7 I 地址线:A0 ~ A7 , A8 , A9 读/写信号: W ′ R

每一片提供 256个字,需要 256个地址 ( A0 ~ 7 : 0 ~ 0 − − − −1 ~ 1) 用A9 , A8两位代码区分四片

7.2 ROM 7.2.1 掩模ROM 掩模ROM 一、结构

二、举例

A0~An-1

D0 W0

W(2n-1)

Dm

地

A1

址

A0 D3

数

D2

据

D1 D0

0 0 1 1

0 1 0 1

0 1 0 1

1 0 1 1

0 1 0 1

1 1 0 0

两个概念: • 存储矩阵的每个交叉点是一个“存储单元”,存储单元 中有器件存入“1”,无器件存入“0” 中有器件存入“1”,无器件存入“0”

7.4 存储器容量的扩展

7.4.1 位扩展方式 适用于每片RAM,ROM字数够用而位数不够时 适用于每片RAM,ROM字数够用而位数不够时 接法:将各片的地址线、读写线、片选线并联即可

例:用八片1024 1位 例:用八片1024 x 1位→ 1024 x 8位的RAM 8位的RAM

7.4.2 字扩展方式

A1 A0

7.5 用存储器实现组合逻辑函数

一、基本原理 从ROM的数据表可见: ROM的数据表可见: 若以地址线为输入变量,则数据线即为一组关于地址变 量的逻辑函数 地 址 数 据

A1 A0 D3 D2 D1 D0

0 0 1 1

0 1 0 1

0 1 0 1

1 0 1 1

0 1 0 1

1 1 0 0

第七章

半导体存储器

本章的重点内容为: 1.存储器的基本工作原理、分类和每种类型存储器的 特点 2.扩展存储器容量的方法 3.用存储器设计组合逻辑电路的原理和方法

第七章

半导体存储器

!单元数庞大 !输入/输出引脚数目有限

7.1 概述 能存储大量二值信息的器件 一、一般结构形式

输 入 出 电 路 I/O

二、分类 1、从存/取功能分: 、从存/ ①只读存储器 (Read-Only-Memory) Read-Only-Memory)

掩模 ROM 可编程 ROM 可擦除的可编程 EPROM

②随机读/ ②随机读/写 静态RAM (Random-Access-Memory) 动态RAM Random-Access-Memory) 2、从工艺分: ①双极型 ②MOS型 MOS型

若R = 0, 则 A1截止, A 2与 A3 导通, W′ I → Q ,写操作 O

Y j = 1时,所在列被选中, 第i行 T7 , T8导通,这时 单元与缓冲器相连 第j 列

7.3.2* 动态随机存储器(DRAM) 动态随机存储器(DRAM) 动态存储单元是利用MOS管栅极电容可以存储电荷的原理 动态存储单元是利用MOS管栅极电容可以存储电荷的原理

7.2.2 可编程ROM(PROM) 可编程ROM(PROM)

总体结构与掩模ROM一样,但存储单元不同 总体结构与掩模ROM一样,但存储单元不同

写入时,要使用编程器

7.2.3 可擦除的可编程ROM(EPROM) 可擦除的可编程ROM(EPROM)

总体结构与掩模ROM一样,但存储单元不同 总体结构与掩模ROM一样,但存储单元不同 一、用紫外线擦除的PROM(UVEPROM) 一、用紫外线擦除的PROM(UVEPROM)

适用于每片RAM,ROM位数够用而字数不够时 适用于每片RAM,ROM位数够用而字数不够时 例:用四片256 8位 例:用四片256 x 8位→1024 x 8位 RAM 8位

I O0 ...................... I O7

A0 ...... A7 , A8 , A9R W ′

1024 x 8 RAM

三、快闪存储器(Flash Memory) 三、快闪存储器(Flash Memory) 为提高集成度,省去T2(选通管) 为提高集成度,省去T2(选通管) 改用叠栅MOS管(类似SIMOS管) 改用叠栅MOS管(类似SIMOS管)

G f 与衬底间SiO2更薄( ~ 15nm) 10 G f 与S区有极小的重叠区 − (隧道区)

地

A1

址

A0 D3 D2

数

据

D1 D0

0 0 1 1

0 1 0 1

0 1 0 1

1 0 1 1

0 1 0 1

1 1 0 0

二、举例

用ROM产生: Y1 = Y = 2 Y3 = Y4 = A′BC + A′B′C AB′CD′ + BCD′ + A′BCD ABCD′ + A′BC ′D′ A′B′CD′ + ABCD

A1 A0

0 0 1 1 0 1 0 1

′ ′ ′ ′ CS1 CS 2 CS3 CS 4

0 1 1 1

1 0 1 1

1 1 0 1

1 1 1 0

四片的地址分配就是: A 9 ~ A 2 00 , A 9 ~ A 2 01 , A9 ~ A 2 10 , A 9 ~ A 2 11

A2 A1 A9

二、SRAM的存储单元 二、SRAM的存储单元

六管N沟道增强型MOS管

T1 ~ T4为基本RS触发器, 作存储单元 X i = 1时,能在1行中被选中, T5 , T6 导通,Q、Q ′与B j、B′j 相通

当 C S ′ = 0时, 若 R ′ = 1, 则 A1 导通, A 2 与 A 3 截止, W Q → I ,读操作 O

SIMOS ( Stacked − gate Injuction MOS ) 叠栅注入MOS管

Gc : 控制栅 G f : 浮置栅

工作原理: 若G f 上充以负电荷,则Gc 处正常逻辑高电平下不导通 若G f 上未充负电荷,则Gc 处正常逻辑高电平下导通

“写入”:雪崩注入, D − S间加高压(20 ~ 25V) , 发生雪崩击穿 同时在Gc上加25V ,50ms宽的正脉冲, 吸引高速电子穿过SiO2到达G f , 形成注入电荷 “擦除”:通过照射产生电子 − 空穴对,提供泄放通道 紫外线照射20 ~ 30分钟(阳光下一周,荧光灯下3年)

二、电可擦除的可编程ROM( PROM) 二、电可擦除的可编程ROM(E2PROM) 总体结构与掩模ROM一样,但存储单元不同 总体结构与掩模ROM一样,但存储单元不同

为克服 UVEPROM 擦除慢,操作不便的缺 点 采用 FLOTOX ( 浮栅隧道氧化层 MOS 管)

G f 与 D之间有小的隧道区, SiO2厚度 < 2 × 10 −8 m ,电子会穿越隧道 当场强达到一定大小( 10 7 V / cm ) −−− “隧道效应”

Y1 = ∑ m( 2,3,6,7 ) Y2 = ∑ m( 6,7,10,14) Y3 = ∑ m( 4,14) Y4 = ∑ m( 2,15)

即将 A9 A8 译成 Y0′ ~ Y3′, 分别接四片的 CS ′

A9 A8

0 0 1 1 0 1 0 1

′ ′ ′ CS1′ CS 2 CS 3 CS 4

0 1 1 1

1 0 1 1

1 1 0 1

1 1 1 0

四片的地址分配就是: 00 A7 ~ A0 , 0 ~ 255 01 A7 ~ A0 , 256 ~ 511 10 A7 ~ A0 , 512 ~ 767 11 A7 ~ A0 768 ~ 1023

A0~An-1

W0

W(2n-1)

7.5 用存储器实现组合逻辑函数

一、基本原理 从ROM的数据表可见: ROM的数据表可见: 若以地址线为输入变量,则数据线即为一组关于地址变 量的逻辑函数

地

A1

址

A0 D3

数

D2

据

D1 D0

0 0 1 1

0 1 0 1

0 1 0 1

1 0 1 1

ห้องสมุดไป่ตู้

0 1 0 1

1 1 0 0

• 存储器的容量:“字数 x 位数”

掩模ROM的特点: 掩模ROM的特点: 出厂时已经固定,不能更改,适合大量生产 简单,便宜,非易失性

7.2.2 可编程ROM(PROM) 可编程ROM(PROM)

总体结构与掩模ROM一样,但存储单元不同 总体结构与掩模ROM一样,但存储单元不同

∗ 熔丝由易熔合金制成 ∗出厂时,每个结点上都 有 ∗ 编程时将不用的熔断 ! 是一次性编程,不能改 写 !