数字锁相环调频发射机电路设计与制作

锁相环电路设计

锁相环电路设计

锁相环电路是一种常见的电路设计,它可以用于信号的同步和频率的稳定。

锁相环电路的基本原理是将输入信号与参考信号进行比较,然后通过反馈控制来调整输出信号的相位和频率,使其与参考信号保持同步。

锁相环电路广泛应用于通信、雷达、测量等领域。

锁相环电路的基本组成部分包括相频检测器、环路滤波器、控制电压源和振荡器。

相频检测器用于将输入信号与参考信号进行比较,产生误差信号。

环路滤波器用于滤除误差信号中的高频成分,以保证系统的稳定性。

控制电压源根据误差信号的大小和方向来产生控制电压,用于调整振荡器的频率和相位。

振荡器则产生输出信号,其频率和相位受到控制电压的影响。

锁相环电路的设计需要考虑多个因素,如相频检测器的灵敏度、环路滤波器的带宽、控制电压源的响应速度等。

此外,还需要根据具体应用场景选择合适的振荡器类型和工作频率。

在实际应用中,锁相环电路的性能也受到环境温度、电源噪声等因素的影响,因此需要进行充分的测试和优化。

锁相环电路是一种重要的电路设计,它可以实现信号同步和频率稳定,广泛应用于通信、雷达、测量等领域。

在设计锁相环电路时,需要考虑多个因素,进行充分的测试和优化,以保证系统的性能和稳定性。

锁相环调频和解调实验,频率合成器实验

实验11 锁相调频与鉴频实验一、实验目的1.掌握锁相环的基本概念。

2.了解集成电路CD4046的内部结构和工作原理。

3.掌握由集成锁相环电路组成的频率调制电路/解调电路的工作原理。

二、预习要求1.复习反馈控制电路的相关知识。

2.锁相环路的工作原理。

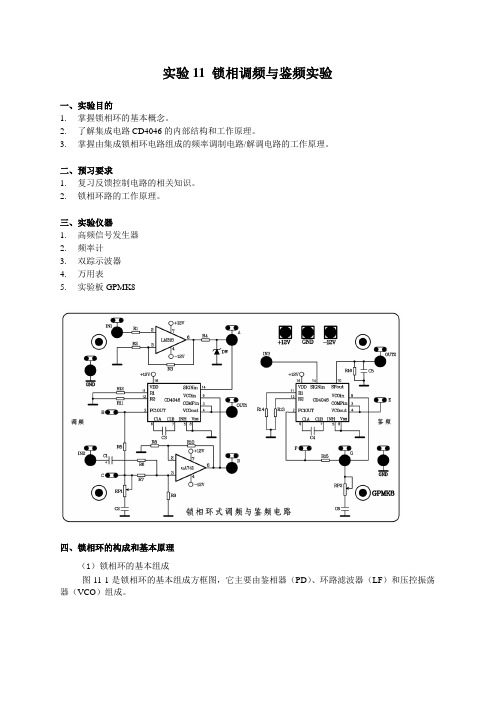

三、实验仪器1.高频信号发生器2.频率计3.双踪示波器4.万用表5.实验板GPMK8四、锁相环的构成和基本原理(1)锁相环的基本组成图11-1是锁相环的基本组成方框图,它主要由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)组成。

图11-1 锁相环的基本组成① 压控振荡器(VCO )VCO 是本控制系统的控制对象,被控参数通常是其振荡频率,控制信号为加在VCO 上的电压。

所谓压控振荡器就是振荡频率受输入电压控制的振荡器。

② 鉴相器(PD )PD 是一个相位比较器,用来检测输出信号0V (t )与输入信号i V (t )之间的相位差θ (t),并把θ(t)转化为电压)(t V d 输出,)(t V d 称为误差电压,通常)(t V d 作为一直流分量或一低频交流量。

③ 环路滤波器(LF )LF 作为一低通滤波电路,其作用是滤除因PD 的非线性而在)(t V d 中产生的无用组合频率分量及干扰,产生一个只反映θ(t)大小的控制信号)(t V C 。

4046锁相环芯片包含鉴相器(相位比较器)和压控振荡器两部分,而环路滤波器由外接阻容元件构成。

(2)锁相环锁相原理锁相环是一种以消除频率误差为目的反馈控制电路,它的基本原理是利用相位误差电压去消除频率误差。

按照反馈控制原理,如果由于某种原因使VCO 的频率发生变化使得与输入频率不相等,这必将使)(t V O 与)(t V i 的相位差θ(t)发生变化,该相位差经过PD 转换成误差电压)(t V d 。

此误差电压经过LF 滤波后得到)(t V c ,由)(t V c 去改变VCO 的振荡频率,使其趋近于输入信号的频率,最后达到相等。

锁相环电路设计

锁相环电路设计锁相环电路是一种常见的电路设计,它可以用于频率合成、时钟恢复、数字信号处理等领域。

锁相环电路的基本原理是通过比较输入信号和参考信号的相位差,控制输出信号的频率和相位,使其与参考信号同步。

本文将介绍锁相环电路的基本原理、设计流程和应用。

一、锁相环电路的基本原理锁相环电路由相位检测器、环路滤波器、控制电压源和振荡器四部分组成。

其中,相位检测器用于检测输入信号和参考信号的相位差,环路滤波器用于滤波和放大控制电压,控制电压源用于产生控制电压,振荡器用于产生输出信号。

锁相环电路的工作原理如下:首先,输入信号和参考信号经过相位检测器比较,得到相位差。

然后,相位差经过环路滤波器滤波和放大,产生控制电压。

控制电压作用于振荡器,调整其频率和相位,使其与参考信号同步。

最后,输出信号经过除频器输出所需频率。

二、锁相环电路的设计流程锁相环电路的设计流程包括以下几个步骤:1. 确定输入信号和参考信号的频率范围和精度要求。

2. 选择合适的相位检测器和环路滤波器,根据输入信号和参考信号的特性确定其参数。

3. 选择合适的振荡器,根据输出信号的频率和精度要求确定其参数。

4. 设计控制电压源,根据环路滤波器的特性确定其参数。

5. 进行仿真和实验验证,调整参数,优化电路性能。

三、锁相环电路的应用锁相环电路广泛应用于频率合成、时钟恢复、数字信号处理等领域。

以下是几个典型的应用案例:1. 频率合成器:锁相环电路可以将参考信号的频率倍频或分频,产生所需的输出频率。

2. 时钟恢复器:锁相环电路可以从输入信号中恢复时钟信号,用于数字通信系统中的时钟同步。

3. 数字信号处理:锁相环电路可以用于数字信号的相位同步和频率同步,提高信号质量和可靠性。

四、总结锁相环电路是一种常见的电路设计,其基本原理是通过比较输入信号和参考信号的相位差,控制输出信号的频率和相位,使其与参考信号同步。

锁相环电路的设计流程包括确定输入信号和参考信号的特性、选择合适的电路元件、仿真和实验验证等步骤。

调频发射机电路设计资料

调频发射机电路设计资料一、调频发射机电路设计的基本原理:晶体振荡器常用于产生高稳定性的参考频率。

频率乘法器则可以将其乘以所需的倍数,以获得所需的射频信号频率。

滤波器用于消除锯齿波形,以及对射频信号进行滤波,以保证信号质量。

二、调频发射机电路设计的步骤:1.确定射频信号频率范围:根据应用需求,确定射频信号的频率范围。

常见的FM广播频率范围是88-108MHz。

2.设计VCO电路:根据射频信号频率范围,设计合适的VCO电路。

VCO电路一般采用压控型振荡器,通过改变其电压来改变频率输出。

可以使用压控电容二极管或压控电感等元件来实现电压对频率的控制。

3.频率乘法器设计:根据需要提高射频信号输出频率,设计合适的频率乘法器电路。

常用的频率乘法器电路包括倍频器、三重频器等。

4.射频滤波器设计:为了保证射频信号质量,需要设计合适的射频滤波器。

射频滤波器可以通过使用LC电路、微带线滤波器等来实现。

滤波器的设计需要考虑频率范围和带宽等因素。

5.功率放大器设计:为了提高输出功率,可以在射频信号输出之前添加功率放大器。

功率放大器一般采用晶体管、功率放大模块等。

放大器设计需要考虑输出功率和频率响应等因素。

6.其他辅助电路设计:在调频发射机电路中,还需要包含其他辅助电路,如音频输入电路、频率稳定电路、限幅器电路、调制电路等。

三、调频发射机电路设计的应用:在广播电台中,调频发射机电路用于将音频信号转化为对应的射频信号,并发送到天线中进行传输。

在无线电对讲机中,调频发射机电路用于将话音信号转化为无线射频信号,并发送到其他对讲机中进行通信。

在无线数传系统中,调频发射机电路用于将数字信号转化为对应的射频信号,并发送到接收端进行数据传输。

总之,调频发射机电路设计是无线通信领域的重要组成部分,它的设计需要考虑频率稳定性、信号品质、功率输出、射频滤波等因素,以满足不同应用的需求。

单片机控制的自动锁相调频发射机的设计

单片机控制的自动锁相调频发射机的设计摘要本文介绍了利用基于单片机AT89C2051控制锁相环组成调频发射电台的设计实现。

设计所选用的锁相环是采用Bi-CMOS工艺,具有吞除脉冲功能的单片串行集成锁相频率合成器芯片,具有很高的频率稳定度和极低的相位抖动,配合单片机可实现灵活方便的编程和控制。

关键词:锁相环频率合成器调频稳定度单片机AT89C20510 引言无线电技术诞生以来,信息传输和信息处理始终是其主要任务。

要将无线电信号有效地发射出去,天线的尺寸必须和电信号的波长为同一数量级[1]。

为了有效地进行传输,必须将携带信息的低频电信号调制到几十MHz~几百MHz以上的高频振荡信号上,再经天线发送出去。

为减小各种因素引起的系统不稳定,增强系统的可靠性,系统必须包括自动增益控制、自动频率控制和自动相位控制(锁相环)在内的反馈控制电路。

其中锁相环电路的性能就显得尤其重要。

本文所讨论的就是一个利用锁相环组成的直接调频信号合成器、小功率发射机并由此而组成一个调频发射电台的设计。

1 系统的整体设计方案1.1 调频发射电台基本原理发射电台的原理很简单,如图1所示,携带信息的低频电信号调制到一个高频信号中,再经高频功率放大器放大后由天线发射出去。

图1 发射电台的基本原理框图图2 系统整体实现框图1.2 整体实现框图[2]本设计采用锁相环直接调频的方案,使其不仅具有很高的频率稳定度(约10-6),还具有比较高的最大频偏量。

整体系统框图如图2所示。

晶振为振荡源提供基准频率信号,振荡源采用PLL频率合成方式。

调频利用调制信号直接加到压控振荡器上来实现的。

压控振荡器由变容二极管和晶体三极管组成电容三点式振荡器。

射频功率放大器采用效率比较高的丙类功放。

整个系统由单片机实现控制和显示频率等功能。

2.各主要部分原理2.1 锁相环的工作原理[3][4]锁相环最基本的结构如图3所示,由三个基本的部件组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。

PLL(锁相环)电路原理及设计 [收藏]

![PLL(锁相环)电路原理及设计 [收藏]](https://img.taocdn.com/s3/m/ca8d027601f69e3143329497.png)

PLL(锁相环)电路原理及设计[收藏]PLL(锁相环)电路原理及设计在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。

无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。

但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。

如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。

此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。

一PLL(锁相环)电路的基本构成PLL(锁相环)电路的概要图1所示的为PLL(锁相环)电路的基本方块图。

此所使用的基准信号为稳定度很高的晶体振荡电路信号。

此一电路的中心为相位此较器。

相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器)的相位比较。

如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。

(将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。

)利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致。

PLL(锁相环)可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。

由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。

只要是基准频率的整数倍,便可以得到各种频率的输出。

从图1的PLL(锁相环)基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。

在此,假设基准振荡器的频率为fr,VCO的频率为fo。

在此一电路中,假设frgt;fo时,也即是VC0的振荡频率fo比fr低时。

此时的相位比较器的输出PD 会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。

相反地,如果frlt;fo时,会产生负脉波信号。

(此为利用脉波的边缘做二个信号的比较。

锁相环路(PLL)电路设计实例

软件实现PLL的代码示例

01

```systemverilog

02

// 定义PLL模块

03

module pll(input wire clk_in, output reg clk_out);

软件实现PLL的代码示例

01

parameter FREF = 100e3; // 参考频率

02

parameter N = 10; // 分频比

相位保持一致。

电荷泵型PLL的电路实现

电荷泵由两个开关和两个电容 组成,一个开关用于充电,另

一个用于放电。

当输入信号与VCO输出信号 的相位存在误差时,电荷泵 的开关会根据误差信号的极 性进行切换,从而在电容上

积累或释放电荷。

电容上的电荷量会转换为电压 信号,该电压信号通过低通滤 波器平滑后,用于调整VCO的

频率。

电荷泵型PLL的性能分析

01

电荷泵型PLL具有较高的带宽和较快的响应速度,因此适用于高 速数据传输和无线通信等应用。

02

由于电荷泵型PLL采用电荷传输方式,因此对电源噪声和电磁干

扰较为敏感,需要采取相应的措施进行抑制。

电荷泵型PLL的另一个优点是易于集成,因此适合于大规模生产

03

和应用。

04

软件实现PLL的代码示例

assign clk_out = div_by_n;

always @(posedge clk_in) begin phase_error <= #1 ($posedge clk_in ? 32'hFFFFFFFF : phase_error 1);

软件实现PLL的代码示例

PLL电路设计实例:模拟型 PLL

锁相环5W调频1075MHZ发射机功放设想

锁相环5W调频107.5MHZ发射机功放设计设计目的:为了得到一台调频发射机。

设计原理:本发射机为了得到较好音质,故主振级必须屏蔽,为了美观与音质兼并而又简单则直接采用闽实的MCE1417H100M模块做主振级。

故本发射机重点在高频功放上,本次设计采用3355(甲类)+3355(甲类)+2053(丙类)+1971(丙类)模式。

设计步骤:1、理论电路设计(1)末级功放(1971)设计,采用以下电路图1计算C10,L7,C11构成末级匹配网络,C1971上加的是12V电压,发射-集电极饱和压降1V,所以1971输出阻抗Rr=(12V-1V)*(12V-1V)/(2*5W)=12.1Ω。

负载为Rc=50Ω。

如图:图2C11=sqrt(Rc-Rr)/(2*Π*f*Rc*sqrtRr)=sqrt(50-12.1)/(2×3.14×107500000×50×sqrt12.1)=6.156/117500000000=52.4pFL7=sqrt(Rr(Rc-Rr))/(2*Π*f)=sqrt(12.1×(50-12.1))/2× 3.14×107500000=21.415/675000000=31.72nHC11可选用5/30P的微调电容加30P的瓷片再加个5P的瓷片并联起来用,这样电容的变化范围为40~65也能通过较大电流不会太发热,C11=52.4pF是在这个范围的。

本人手头上只有0.6MM的漆包线,故采用此线制作本设计中所有空心电感,利用空心电感计算器计算得到,如图:,图3可到到L7为5D 3T Φ0.6,电感量为49.9291nH。

有人就要问了L7应该是31.72 nH啊?怎么现在要把线饶成49.9291 nH呢?不急,大家听我慢慢道来,在图2中是不是还有个C10没计算啊?我是这样理解的:L7是空心电感调起来不是很方便,而且会弄的很不美观,我们给L7串联个C10就可以变相的来调节L7的大小了,请看下图:图4我们可以认为L7是由L7(1)和L7(2)两个电感串联而得到的,令L7(1)=31.72 nH,则L7(2)=49.9291-31.72=18.209 nH,此处我们只看L7(1)与C11即可构成12.1Ω向50Ω的匹配网络,然而L7(1)是虚拟的,谁能把个电感一绕就饶到31.72 nH,神仙恐怕也没这么厉害,我们是凡人,所以我们绕的电感实际植是49.9291 nH,则必然多出了L7(2)=18.209 nH。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字锁相环调频发射机电路设计与制作

一.数字锁相环发射机电路工作原理分析

BA1404对于一般的调频发射已经足够,但是它有一个致命的缺点:没有锁相环电路,容易跑频。

因此,对于要求高的地方就不适合了。

下面给出基于数字锁相环的调频发射机实现。

通常使用的数字锁相环调频发射机都是采用一些专用的高频锁相环电路,如MC145152等。

但是这种实现方式的一个缺点就是电路复杂,调试麻烦,因此我们注意到了BH1414-BH1417系列芯片,即相当于BA1404+PLL。

下面介绍BH1415数控调频发射机电路的设计与制作。

1.调频部分电路

图一:BH1415调频发射机电路

由于BH1415控制方式采用串行方式,因此必须要使用到单片机控制。

大家也可以采用BH1417+拔码开关的方式(适用于对单片机不熟悉的同学)。

2.控制电路

图二:单片机控制电路

控制部分:选用了89S51单片机作为控制芯片,频率显示部分采用数码管来显示(由于单片机的I/O大部分空闲,建议采用1602LCD显示方式)。

3.功率放大电路《参考BA1404调频发射机电路设计与制作》。

二.制作与调试

1.制作要点:正确的PCB设计是首要条件,高频电路讲究接地,该电路虽然外围元件少,但如果模拟、数字电路布线不合理,干扰很大,此时PCB的设计显得尤为重要,一定要保证数、模分开,一点接地。

退耦电容不可少,笔者电路中用到了8颗容量不同的电容。

电容值的选取最好不全一样,如102、103、104等。

控制板的PCB设计笔者将三极管放在四位数码管下,三极管卧放,再装上数码管,这样看起来比较简洁。

2.调试:配合正确的控制部分,本制作唯一难点在压控部分的调试。

常见问题是调不出频率,或者出了频率但不受单片机控制,该类问题主要是压控调试不对,没有锁相。

先测试变容二极管上的电压,频率越高,电压越高,调节电感匝距,使得频率设置在108MHz时,电压接近Vcc,频率设置在98MHz时,电压约3 V,频率设置在88MHz时,电压接近0V。

如果电压不变,则需要检查电路是否正确,电压变化范围不够宽,则说明变容二极管变容比不够大,这样频率调节范围不能达到满频任意调节。

变容二极管建议选用KV1471或则BB910等。

三.参考文献

[1]谢自美,电子线路设计.实验.测试(第二版) 华中科技大学出版社,2001.9

[2]何中庸(译) 高频电路设计与制作,科学出版社2005.4

[3]bh1415芯片手册(网上查找可得)。