IO端口及相关寄存器

IO映射

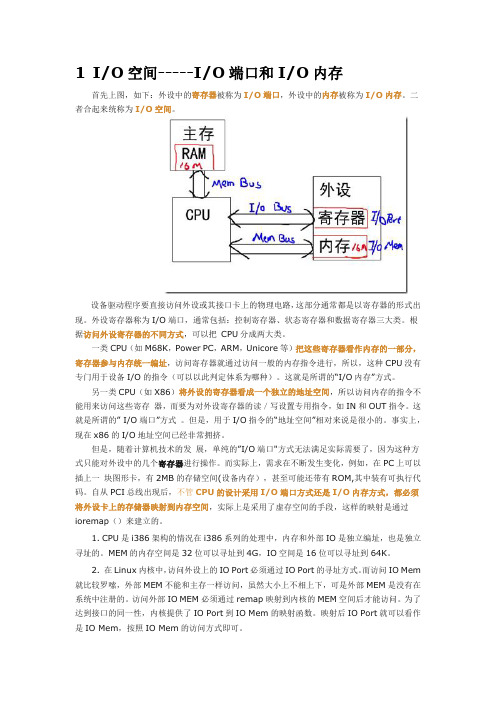

1I/O空间-----I/O端口和I/O内存首先上图,如下:外设中的寄存器被称为I/O端口,外设中的内存被称为I/O内存。

二者合起来统称为I/O空间。

设备驱动程序要直接访问外设或其接口卡上的物理电路,这部分通常都是以寄存器的形式出现。

外设寄存器称为I/O端口,通常包括:控制寄存器、状态寄存器和数据寄存器三大类。

根据访问外设寄存器的不同方式,可以把CPU分成两大类。

一类CPU(如M68K,Power PC,ARM,Unicore等)把这些寄存器看作内存的一部分,寄存器参与内存统一编址,访问寄存器就通过访问一般的内存指令进行,所以,这种CPU没有专门用于设备I/O的指令(可以以此判定体系为哪种)。

这就是所谓的“I/O内存”方式。

另一类CPU(如X86)将外设的寄存器看成一个独立的地址空间,所以访问内存的指令不能用来访问这些寄存器,而要为对外设寄存器的读/写设置专用指令,如IN和OUT指令。

这就是所谓的” I/O端口”方式。

但是,用于I/O指令的“地址空间”相对来说是很小的。

事实上,现在x86的I/O地址空间已经非常拥挤。

但是,随着计算机技术的发展,单纯的”I/O端口"方式无法满足实际需要了,因为这种方式只能对外设中的几个寄存器进行操作。

而实际上,需求在不断发生变化,例如,在PC上可以插上一块图形卡,有2MB的存储空间(设备内存),甚至可能还带有ROM,其中装有可执行代码。

自从PCI总线出现后,不管CPU的设计采用I/O端口方式还是I/O内存方式,都必须将外设卡上的存储器映射到内存空间,实际上是采用了虚存空间的手段,这样的映射是通过ioremap()来建立的。

1. CPU是i386架构的情况在i386系列的处理中,内存和外部IO是独立编址,也是独立寻址的。

MEM的内存空间是32位可以寻址到4G,IO空间是16位可以寻址到64K。

2. 在Linux内核中,访问外设上的IO Port必须通过IO Port的寻址方式。

8086对存储器和io端口的编址方式 -回复

8086对存储器和io端口的编址方式-回复8086微处理器是Intel公司于1979年推出的一款16位微处理器,广泛应用于个人电脑和工业控制系统等领域。

在8086中,存储器和I/O端口被分别编址,下面将一步一步回答关于8086对存储器和I/O端口的编址方式的问题。

一、存储器的编址方式:8086微处理器使用20位地址总线,整个寻址空间范围为1MB(2^20)。

这种编址方式称为“段:偏移”地址形式。

1. 段选择器:在8086中,用于选择段的寄存器有CS(Code Segment, 代码段)、DS (Data Segment, 数据段)、SS(Stack Segment, 栈段)和ES(Extra Segment, 附加段)。

这些寄存器的值是16位的,用于存储存储器段的起始地址,偏移地址的计算需要与这些寄存器的值相结合。

2. 偏移地址:8086通过16位的偏移地址来表示存储器中的特定字节。

偏移地址可以是由程序员指定的常数,也可以是由程序中的地址计算得出的。

3. 存储器地址计算:8086微处理器将段选择器的值左移4位(乘以16),加上偏移地址的值。

例如,当使用DS和SI寄存器来指定一个存储器地址时,计算公式为:物理地址= DS * 16 + SI二、I/O端口的编址方式:8086微处理器使用16位地址总线寻址I/O端口。

I/O端口被视为存储器中的特殊地址,可以访问外部设备。

1. I/O端口地址空间:8086将I/O端口地址空间映射到存储器地址空间的一部分,称为I/O端口地址空间。

I/O端口地址空间的范围为0x0000到0xFFFF,共有65536个端口地址。

2. IN指令:IN指令用于从指定的I/O端口读取数据。

它需要提供一个8位或16位的端口地址。

IN指令执行时,8086将相应的端口地址发送给外部设备,然后接收来自该设备的数据。

例如,以下指令从I/O端口0x01 读取数据:IN AL, 0x013. OUT指令:OUT指令用于向指定的I/O端口写入数据。

PC的IO端口地址表(IO端口地址表)

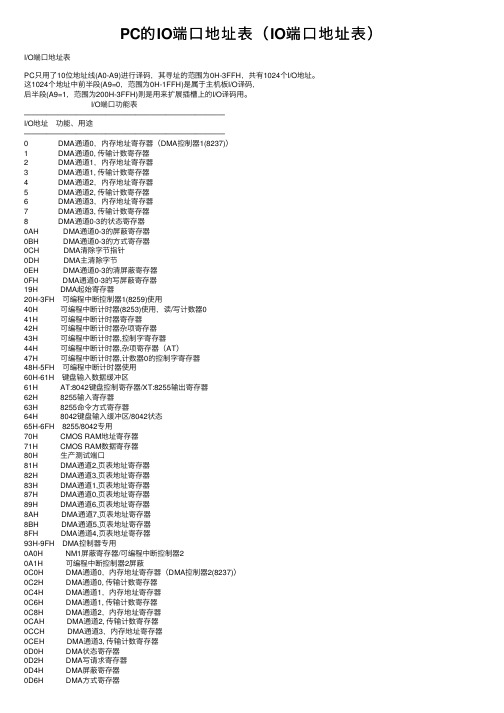

PC的IO端⼝地址表(IO端⼝地址表)I/O端⼝地址表PC只⽤了10位地址线(A0-A9)进⾏译码,其寻址的范围为0H-3FFH,共有1024个I/O地址。

这1024个地址中前半段(A9=0,范围为0H-1FFH)是属于主机板I/O译码,后半段(A9=1,范围为200H-3FFH)则是⽤来扩展插槽上的I/O译码⽤。

I/O端⼝功能表———————————————————————————I/O地址 功能、⽤途———————————————————————————0 DMA通道0,内存地址寄存器(DMA控制器1(8237))1 DMA通道0, 传输计数寄存器2 DMA通道1,内存地址寄存器3 DMA通道1, 传输计数寄存器4 DMA通道2,内存地址寄存器5 DMA通道2, 传输计数寄存器6 DMA通道3,内存地址寄存器7 DMA通道3, 传输计数寄存器8 DMA通道0-3的状态寄存器0AH DMA通道0-3的屏蔽寄存器0BH DMA通道0-3的⽅式寄存器0CH DMA清除字节指针0DH DMA主清除字节0EH DMA通道0-3的清屏蔽寄存器0FH DMA通道0-3的写屏蔽寄存器19H DMA起始寄存器20H-3FH 可编程中断控制器1(8259)使⽤40H 可编程中断计时器(8253)使⽤,读/写计数器041H 可编程中断计时器寄存器42H 可编程中断计时器杂项寄存器43H 可编程中断计时器,控制字寄存器44H 可编程中断计时器,杂项寄存器(AT)47H 可编程中断计时器,计数器0的控制字寄存器48H-5FH 可编程中断计时器使⽤60H-61H 键盘输⼊数据缓冲区61H AT:8042键盘控制寄存器/XT:8255输出寄存器62H 8255输⼊寄存器63H 8255命令⽅式寄存器64H 8042键盘输⼊缓冲区/8042状态65H-6FH 8255/8042专⽤70H CMOS RAM地址寄存器71H CMOS RAM数据寄存器80H ⽣产测试端⼝81H DMA通道2,页表地址寄存器82H DMA通道3,页表地址寄存器83H DMA通道1,页表地址寄存器87H DMA通道0,页表地址寄存器89H DMA通道6,页表地址寄存器8AH DMA通道7,页表地址寄存器8BH DMA通道5,页表地址寄存器8FH DMA通道4,页表地址寄存器93H-9FH DMA控制器专⽤0A0H NM1屏蔽寄存器/可编程中断控制器20A1H 可编程中断控制器2屏蔽0C0H DMA通道0,内存地址寄存器(DMA控制器2(8237))0C2H DMA通道0, 传输计数寄存器0C4H DMA通道1,内存地址寄存器0C6H DMA通道1, 传输计数寄存器0C8H DMA通道2,内存地址寄存器0CAH DMA通道2, 传输计数寄存器0CCH DMA通道3,内存地址寄存器0CEH DMA通道3, 传输计数寄存器0D0H DMA状态寄存器0D2H DMA写请求寄存器0D4H DMA屏蔽寄存器0D6H DMA⽅式寄存器0D8H DMA清除字节指针0DAH DMA主清0DCH DMA清屏蔽寄存器0DEH DMA写屏蔽寄存器0DFH-0EFH 保留0F0H-0FFH 协处理器使⽤100H-16FH保留170H 1号硬盘数据寄存器171H 1号硬盘错误寄存器172H 1号硬盘数据扇区计数173H 1号硬盘扇区数174H 1号硬盘柱⾯(低字节)175H 1号硬盘柱⾯(⾼字节)176H 1号硬盘驱动器/磁头寄存器177H 1号硬盘状态寄存器1F0H 0号硬盘数据寄存器1F1H 0号硬盘错误寄存器1F2H 0号硬盘数据扇区计数1F3H 0号硬盘扇区数1F4H 0号硬盘柱⾯(低字节)1F5H 0号硬盘柱⾯(⾼字节)1F6H 0号硬盘驱动器/磁头寄存器1F7H 0号硬盘状态寄存器1F9H-1FFH保留200H-20FH游戏控制端⼝210H-21FH扩展单元278H 3号并⾏⼝,数据端⼝279H 3号并⾏⼝,状态端⼝27AH 3号并⾏⼝,控制端⼝2B0H-2DFH保留2E0H EGA/VGA使⽤2E1H GPIP(0号适配器)2E2H 数据获取(0号适配器)2E3H 数据获取(1号适配器)2E4H-2F7H保留2F8H 2号串⾏⼝,发送/保持寄存器(RS232接⼝卡2) 2F9H 2号串⾏⼝,中断有效寄存器2FAH 2号串⾏⼝,中断ID寄存器2FBH 2号串⾏⼝,线控制寄存器2FCH 2号串⾏⼝,调制解调控制寄存器2FDH 2号串⾏⼝,线状态寄存器2FEH 2号串⾏⼝,调制解调状态寄存器2FFH 保留300H-31FH原形卡320H 硬盘适配器寄存器322H 硬盘适配器控制/状态寄存器324H 硬盘适配器提⽰/中断状态寄存器325H-347H保留348H-357H DCA3278366H-36FH PC⽹络372H 软盘适配器数据输出/状态寄存器375H-376H 软盘适配器数据寄存器377H 软盘适配器数据输⼊寄存器378H 2号并⾏⼝,数据端⼝379H 2号并⾏⼝,状态端⼝37AH 2号并⾏⼝,控制端⼝380H-38FH SDLC及BSC通讯390H-393H Cluster适配器03A0H-3AFH BSC通讯3B0H-3B H MDA视频寄存器3BCH 1号并⾏⼝,数据端⼝3BDH 1号并⾏⼝,状态端⼝3BEH 1号并⾏⼝,控制端⼝3C0H-3CFH EGA/VGA视频寄存器3D0H-3D7H CGA视频寄存器3F0H-3F7H 软盘控制器寄存器3F8H 1号串⾏⼝,发送/保持寄存器(RS232接⼝卡1) 3F9H 1号串⾏⼝,中断有效寄存器3FAH 1号串⾏⼝,中断ID寄存器3FBH 1号串⾏⼝,线控制寄存器3FCH 1号串⾏⼝,调制解调控制寄存器3FDH 1号串⾏⼝,线状态寄存器3FEH 1号串⾏⼝,调制解调状态寄存器3FFH 保留2.2.1 I/O端⼝和寻址2.2 I/O端⼝寻址和访问控制⽅式2.2.1 I/O端⼝和寻址CPU为了访问I/O接⼝控制器或控制卡上的数据和状态信息,需要⾸先指定它们的地址。

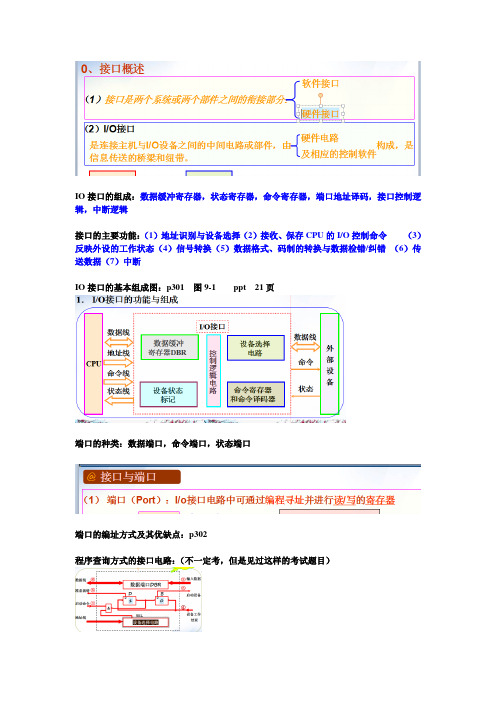

计算机组成原理IO接口的组成

IO接口的组成:数据缓冲寄存器,状态寄存器,命令寄存器,端口地址译码,接口控制逻辑,中断逻辑接口的主要功能:(1)地址识别与设备选择(2)接收、保存CPU的I/O控制命令(3)反映外设的工作状态(4)信号转换(5)数据格式、码制的转换与数据检错/纠错(6)传送数据(7)中断IO接口的基本组成图:p301 图9-1 ppt 21页端口的种类:数据端口,命令端口,状态端口端口的编址方式及其优缺点:p302程序查询方式的接口电路:(不一定考,但是见过这样的考试题目)程序查询方式的流程:中断(重中之重)中断的定义(背):计算机在执行程序的过程中,当出现异常情况或特殊请求时,计算机会停止现行程序的运行转向对这些异常情况或特殊请求进行处理,处理结束后再返回到现行程序的间断处继续执行凡是向CPU提出中断请求的各种因素,统称为中断源。

在每条指令执行结束时,CPU去执行中断服务程序外设向CPU发出中断申请的时间是随机的,在任何一个时刻只能为一个中断源的请求提供服务,实现中断的软/硬件,总称为中断系统中断的处理过程中断请求中断判优中断响应中断服务中断返回中断隐指令:在中断响应时候执行,主要功能:中断隐指令的功能:发出中断响应信号将程序断点(当前PC值)和标志位寄存器FR压入堆栈,关中断(清EINT为0),将中断处理程序的首地址送入PC。

在中断处理过程中,中断服务程序的处理流程是:保护现场、中断服务和恢复现场。

(p305)单重中断和多重中断的中断处理流程图p305 图9-4单重中断和多重中断的定义;(考试易出简答题)单:CPU执行中断服务程序时,不响应新的中断请求即不允许中断现行的中断服务程序。

多:在处理中断的过程中,有新的,优先级更高的中断请求到来,此时CPU暂停现行的中断服务,允许级别更高的中断源中断现行的中断服务程序形成中断入口地址的方法可分为:软件查询法和硬件向量法。

软件查询法:软件查询法是用一个中断管理程序,按照优先级由高到低的顺序,依次查询每一个中断源是否有中断请求。

单片机IO端口工作原理

单片机IO端口工作原理在单片机内部,每一个IO端口都对应着一个寄存器,该寄存器称为IO口寄存器,用于控制该IO端口的输入输出状态。

IO口寄存器通常是一个8位或16位的寄存器,每一位对应一个IO端口。

单片机的IO端口工作原理如下:1.输入方式:当一些端口被设置为输入模式时,它可以接收外部信号。

在输入模式下,该端口的电平状态可以被单片机读取到。

通常通过设置IO口寄存器的相应位来控制端口的输入模式。

在输入模式下,可以通过查询或中断方式读取IO端口的状态。

2.输出方式:当一些端口被设置为输出模式时,它可以向外部设备发送信号。

在输出模式下,可以通过设置IO口寄存器相应位的值来控制端口的输出电平状态。

高电平和低电平对应着不同的输出状态,可以通过操作寄存器来改变IO端口的电平状态。

3.端口模式设置:针对每一个IO端口,单片机提供了相应的寄存器来设置其工作模式。

通常包括输入模式、输出模式、上拉模式和下拉模式等。

输入模式和输出模式可以通过设置IO口寄存器的相应位来实现,上拉模式和下拉模式则需要通过设置其他寄存器或器件来实现。

4.状态改变:在一些情况下,IO端口的状态可能发生改变,如按键按下、外部信号触发等。

这时候可以通过查询或中断的方式来获取IO端口的状态变化,然后进行相应的处理。

5.外部设备连接:IO端口通常通过引脚连接到外部设备,如按键、LED灯、LCD显示屏、电机等。

通过IO端口的输出控制可以实现对外部设备的控制,通过IO端口的输入可以获取外部设备的状态。

总之,单片机IO端口通过IO口寄存器进行控制,可以实现与外部设备的信息交换和控制。

通过设置端口的输入输出模式,可以实现数据的输入和输出。

通过查询或中断的方式,可以实时获取IO端口的状态变化。

通过连接外部设备,可以实现对其控制和监测。

51单片机io口的用法

51单片机io口的用法51单片机是一种经典的单片机系列,广泛应用于各种嵌入式系统中。

其IO口是单片机最基本的输入输出功能,可以用来连接外部设备和实现与外界的交互。

本文将介绍51单片机IO口的用法,并提供相关参考内容,帮助读者更好地理解和应用。

一、51单片机IO口简介51单片机的IO口是通过P0、P1、P2、P3四个寄存器来控制的。

其中P0口为8位双向I/O口,P1、P2、P3口为8位I/O 口,可以通过配置将其设置为输入(IN)或输出(OUT)模式。

在51单片机中,IO口的状态(高电平或低电平)决定了其在电路中的功能。

二、IO口的输入模式通过将IO口设置为输入模式,可以实现对外部信号的读取。

以下是51单片机IO口输入模式的几种常见应用:1. 按键输入:通过将IO口与按键连接,读取按键的状态(按下或松开)。

2. 传感器输入:通过将IO口与传感器连接,读取传感器的输出信号,如光线强度、温度等。

3. 外部信号输入:通过将IO口与其他设备连接,读取外部设备的状态或数据。

在使用IO口作为输入时,需要设置对应端口的引脚为输入模式,并读取相应寄存器的值进行判断。

三、IO口的输出模式通过将IO口设置为输出模式,可以实现对外部设备的控制。

以下是51单片机IO口输出模式的几种常见应用:1. LED显示:通过将IO口与LED连接,控制LED的闪烁、亮灭。

2. 电机驱动:通过将IO口与电机驱动芯片连接,控制电机的转动方向、速度。

3. 继电器控制:通过将IO口与继电器连接,控制继电器的开关状态。

在使用IO口作为输出时,需要设置对应端口的引脚为输出模式,并将相应寄存器的值设置为高电平或低电平。

四、IO口的控制方法有两种常见的方式可以控制51单片机的IO口:位操作和寄存器读写。

1. 位操作:通过对相应寄存器的位进行操作来控制IO口的状态。

例如,要将P1口的第0位设置为高电平,可以使用以下代码:P1_0 = 1;要将P1口的第1位设置为低电平,可以使用以下代码:P1_1 = 0;2. 寄存器读写:通过读写相应寄存器的值来控制IO口的状态。

gpio常用寄存器解释

gpio常用寄存器解释GPIO是通用输入输出的缩写,是一种常见的硬件接口。

在嵌入式系统或单片机开发中,GPIO常用于与外部设备进行数据交互。

GPIO常用寄存器是用来控制和设置GPIO引脚的寄存器。

下面是几个常用的GPIO寄存器的解释:1. GPIO方向寄存器(GPIODIR):该寄存器用于设置GPIO引脚的输入或输出方向。

当某一位为1时,表示该引脚为输出模式;当某一位为0时,表示该引脚为输入模式。

2. GPIO数据寄存器(GPIODATA):该寄存器用于读取或设置GPIO引脚的数据。

当引脚为输出模式时,可以通过该寄存器设置引脚的输出值;当引脚为输入模式时,可以通过该寄存器读取引脚的输入值。

3. GPIO中断使能寄存器(GPIOIE):该寄存器用于启用GPIO引脚的中断功能。

当某一位为1时,表示该引脚的中断功能被启用;当某一位为0时,表示该引脚的中断功能被禁用。

4. GPIO中断状态寄存器(GPIOIS):该寄存器用于检测GPIO引脚的中断状态。

当某一位为1时,表示该引脚触发了中断;当某一位为0时,表示该引脚未触发中断。

读取该寄存器后,需清零相应引脚的中断状态。

5. GPIO上升/下降沿触发寄存器(GPIOIBE):该寄存器用于设置GPIO引脚的中断触发方式。

当某一位为1时,表示该引脚的中断触发方式为上升沿和下降沿;当某一位为0时,表示该引脚的中断触发方式为边沿触发。

通过使用这些GPIO常用寄存器,开发者可以灵活地控制和配置GPIO引脚的操作模式、数据传输和中断触发等功能。

在嵌入式系统中,GPIO的应用非常广泛,例如控制外部LED灯的亮灭、读取外部传感器的数据等。

熟悉并理解这些寄存器对于嵌入式系统的开发非常重要。

单片机IO口介绍

P0口和P2的结构 口和P2 4.1.1 P0口和P2的结构

一、P0口的结构

下图为P0口的某位P0.n(n=0~7)结构图,它由一个 输出锁存器、两个三态输入缓冲器和输出驱动电路 及控制电路组成。从图中可以看出,P0口既可以作 为I/O用,也可以作为地址/数据线用。

地址/数据 地址/ 控制 读锁存器

地址/数据 地址/ 控制 读锁存器

T1 P0.n D Q MUX

VCC

内部总线 写锁存器

T2:如果此时该端口的负载恰是一个晶体管基极,且原端 口输出值为1,那么导通了的PN结会把端口引脚高电平拉低;若 此时直接读端口引脚信号,将会把原输出的“1”电平误读为“0” 电平。现采用读输出锁存器代替读引脚,图中,上面的三态缓 冲器就为读锁存器Q端信号而设,读输出锁存器可避免上述可能 发生的错误。** 地址/数据 地址/ 控制 读锁存器

二、P3 P3第二功能(Q=1) P3 此时引脚部分输入(Q=1、W=1) ,部分输出(Q=1、W输出)

第二输出功能 第二输出功能 读锁存器 VCC

。

W

R P3.n P3口

D Q

内部总线 写锁存器

T

CLK Q

引脚

读引脚 第二输入功能 第二输入功能

P3第二功能各引脚功能定义: P3

P3.0:RXD串行口输入 P3.1:TXD串行口输出 P3.2:INT0外部中断0输入 P3.3:INT1外部中断1输入 P3.4:T0定时器0外部输入 P3.5:T1定时器1外部输入 P3.6:WR外部写控制 P3.7:RD外部读控制

地址/数据 地址/ 控制 读锁存器

T1 P0.n D Q MUX

VCC

内部总线 写锁存器

T2

P0口 P0口 引脚

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

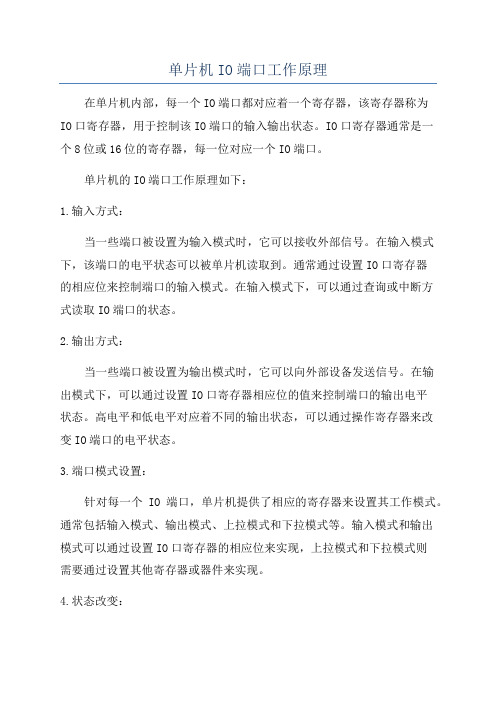

P4M0 register (不可位寻址) SFR name Address P4M0 B4H name P4M0.7 P4M0.6 P4M0.5 P4M0.4 P4M0.3 P4M0.2 P4M0.1 P4M0.0

P3 register (可位寻址) SFR name Address P3 B0H bit name B7 P3.7 B6 P3.6 B5 P3.5 B4 P3.4 B3 P3.3 B2 P3.2 B1 P3.1 B0 P3.0

P2 register (可位寻址) SFR name Address P2 A0H bit name B7 P2.7 B6 P2.6 B5 P2.5 B4 P2.4 B3 P2.3 B2 P2.2 B1 P2.1 B0 P2.0

P2M1 register (不可位寻址) SFR name Address P2M1 95H bit B7 B6 B5 B4 B3 B2 B1 B0 name P2M1.7 P2M1.6 P2M1.5 P2M1.4 P2M1.3 P2M1.2 P2M1.1 P2M1.0

P1M1 register (不可位寻址) SFR name P1M1 Address 91H bit B7 B6 B5 B4 B3 B2 B1 B0 name P1M1.7 P1M1.6 P1M1.5 P1M1.4 P1M1.3 P1M1.2 P1M1.1 P1M1.0

P1M0 register (不可位寻址) SFR name Address P1M0 92H bit B7 B6 B5 B4 B3 B2 B1 B0 name P1M0.7 P1M0.6 P1M0.5 P1M0.4 P1M0.3 P1M0.2 P1M0.1 P1M0.0

B6

B5

B4

B3

B2

B1

B0

name P0M1.7 P0M1.6 P0M1.5 P0M1.4 P0M1.3 P0M1.2 P0M1.1 P0M1.0

P0M0 register (不可位寻址) SFR name P0M0 Address 94H bit B7 B6 B5 B4 B3 B2 B1 B0 name P0M0.7 P0M0.6 P0M0.5 P0M0.4 P0M0.3 P0M0.2 P0M0.1 P0M0.0

P4M1 register (不可位寻址) SFR name Address P4M1 B3H bit B7 B6 B5 B4 B3 B2 B1 B0 name P4M1.7 P4M1.6 P4M1.5 P4M1.4 P4M1.3 P4M1.2 P4M1.1 P4M1.0 bit B7 B6 B5 B4 B3 B2 B1 B0

P2M0 register (不可位寻址) SFR name Address P2M0 96H bit B7 B6 B5 B4 B3 B2 B1 B0 name P2M0.7 P2M0.6 P2M0.5 P2M0.4 P2M0.3 P2M0.2 P2M0.1 P2M0.0

P1 register (可位寻址) SFR name P1 Address 90H bit name B7 P1.7 B6 P1.6 B5 P1.5 B4 P1.4 B3 P1.3 B2 P1.2 B1 P1.1 B0 P1.0

I/O端口及相关寄存器

P5 register (可位寻址) SFR name Address P5 C8H bit name B7 B6 B5 B4 B3 P5.3 B2 P5.2 B1 P5.1 B0 P5.0

P5M1 register (不可位寻址) SFR name Address P5M1 C9H bit name bit name B7 B7 B6 B6 B5 B5 B4 B4 B3 B2 B1 B0 P5M1.3 P5M1.2 P5M1.1 P3M1.0 B3 B2 B1 B0

P5M0 register (不可位寻址) SFR name Address P5M0 CAH P5M0.3 P5M0.2 P5M0.1 P5M0.0

P4 register (可位寻址) SFR name Address P4 C0H bit name B7 P4.7 B6 P4.6 B5 P4.5 B4 P4.4 B3 P4.3 B2 P4.2 B1 P4.1 B0 P4.0

P3M1 register (不可位寻址) SFR name Address P3M1 B1H bit B7 B6 B5 B4 B3 B2 B1 B0 name P3M1.7 P3M1.6 P3M1.5 P3M1.4 P3M1.3 P3M1.2 P3M1.1 P3M1.0

P3M0 register (不可位寻址) SFR name Address P3M0 B2H bit B7 B6 B5 B4 B3 B2 B1 B0 name P3M0.7 P3M0.6 P3M0.5 P3M0.4 P3M0.3 P3M0.2 P3M0.1 P3M0.0

P0 register (可位寻址) SFR name Address P0 80H P0M1 register SFR name P0M1 Address 93H

bit name

B7 P0.7B3 P0.3

B2 P0.2

B1 P0.1

B0 P0.0

bit

B7