哈工大计算机组成原理第九章课件唐朔飞老师

合集下载

计算机组成原理-唐朔飞(完整版)

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

2020年最新

计算机组成原理课后答案(第二版)_唐朔飞_第九章

当芯片改变后,相应参数变为: 机器周期=0.4µ s×4=1.6µs 平均指令周期=1.6µs×2.5=4µ s 平均指令执行速度=1/4µ s =0.25MIPS 若要得到平均每秒80万次的指令 执行速度,则应采用的主频为: 平均指令周期=1/0.8MIPS =1.25 ×10-6=1.25µ s 机器周期=1.25µ s÷2.5=0.5µs 时钟周期= 0.5µ s÷4=0.125µ s 主频=1/0.125µ s=8MHz 应采用主频为8MHz的CPU芯片。

LDA PC+D(IR)EAR EARBusMAR M(MAR)MDR MDRBus ACC

PCo,IRo,+,EARi EARo,MARi

R/-W=R

MDRo,ACCi

(2)“SUB D(XR)”指令周期流程图及控制信号序列:

PC Bus MAR M(MAR) MDR MDR Bus IR PC+1 PC OP=?

解:先通过主频求出时钟周期时 间,再进一步求出机器周期和平均指 令周期。 时钟周期=1/10MHz=0.1×10-6 =100ns 机器周期=100ns×4=400ns=0.4µ s 平均指令周期=1/1MIPS =1×10-6=1µ s 每个指令周期所含机器周期个数 = 1µ s/0.4µs=2.5个

4. 能不能说CPU的主频越快,计 算机的运行速度就越快?为什么? 解:不能说机器的主频越快,机 器的速度就越快。因为机器的速度不 仅与主频有关,还与数据通路结构、 时序分配方案、ALU运算能力、指令 功能强弱等多种因素有关,要看综合 效果。

5. 设机器A的CPU主频为8MHz, 机器周期含4个时钟周期,且该机的平 均指令执行速度是0.4MIPS,试求该机 的平均指令周期和机器周期,每个指 令周期中含几个机器周期?如果机器B 的CPU主频为12MHz,且机器周期也 含4个时钟周期,试问B机的平均指令 执行速度为多少MIPS? 解:先通过A机的平均指令执行速 度求出其平均指令周期,再通过主频 求出时钟周期,然后进一步求出机器 周期。B机参数的算法与A机类似。 计算如下:

计算机组成原理课后习题及答案-唐朔飞(完整版)ppt课件

控制器组成。 • PC:Program Counter,程序计数器,其功能是存放当前欲执行指令的地址,并可自动计数形成下

一条指令地址。 • IR:Instruction Register,指令寄存器,其功能是存放当前正在执行的指令。 • CU:Control Unit,控制单元(部件),为控制器的核心部件,其功能是产生微操作命令序列。 • ALU:Arithmetic Logic Unit,算术逻辑运算单元,为运算器的核心部件,其功能是进行算术、逻辑

CLK: T0: T1: T2: T3: P0: P1: P2: P3:

编辑版pppt

24

返回目录

以8位总线为例,电路设计如下: (图中,A、B、C、D四个寄存器与数据总线 的连接方法同上。)

数据总线(D7~D0)

ABUS

BBUS

CBUS

DBUS

1Q OE

374 8Q

1D A 8D

1Q 374 8Q

编辑版pppt

14

8. 为什么说半同步通信 同时保留了同步通信和异步 通信的特点?

解: 半同步通信既能像同步

通信那样由统一时钟控制, 又能像异步通信那样允许传 输时间不一致,因此工作效 率介于两者之间。

编辑版pppt

15

10. 什么是总线标准?为什么要设

置总线标准?目前流行的总线标准有哪些? 什么是即插即用?哪些总线有这一特点?

• 解:P9-10 • 主机:是计算机硬件的主体部分,由CPU和主存储器MM合成为主机。 • CPU:中央处理器,是计算机硬件的核心部件,由运算器和控制器组成;(早期的运

算器和控制器不在同一芯片上,现在的CPU内除含有运算器和控制器外还集成了 CACHE)。 • 主存:计算机中存放正在运行的程序和数据的存储器,为计算机的主要工作存储器, 可随机存取;由存储体、各种逻辑部件及控制电路组成。

一条指令地址。 • IR:Instruction Register,指令寄存器,其功能是存放当前正在执行的指令。 • CU:Control Unit,控制单元(部件),为控制器的核心部件,其功能是产生微操作命令序列。 • ALU:Arithmetic Logic Unit,算术逻辑运算单元,为运算器的核心部件,其功能是进行算术、逻辑

CLK: T0: T1: T2: T3: P0: P1: P2: P3:

编辑版pppt

24

返回目录

以8位总线为例,电路设计如下: (图中,A、B、C、D四个寄存器与数据总线 的连接方法同上。)

数据总线(D7~D0)

ABUS

BBUS

CBUS

DBUS

1Q OE

374 8Q

1D A 8D

1Q 374 8Q

编辑版pppt

14

8. 为什么说半同步通信 同时保留了同步通信和异步 通信的特点?

解: 半同步通信既能像同步

通信那样由统一时钟控制, 又能像异步通信那样允许传 输时间不一致,因此工作效 率介于两者之间。

编辑版pppt

15

10. 什么是总线标准?为什么要设

置总线标准?目前流行的总线标准有哪些? 什么是即插即用?哪些总线有这一特点?

• 解:P9-10 • 主机:是计算机硬件的主体部分,由CPU和主存储器MM合成为主机。 • CPU:中央处理器,是计算机硬件的核心部件,由运算器和控制器组成;(早期的运

算器和控制器不在同一芯片上,现在的CPU内除含有运算器和控制器外还集成了 CACHE)。 • 主存:计算机中存放正在运行的程序和数据的存储器,为计算机的主要工作存储器, 可随机存取;由存储体、各种逻辑部件及控制电路组成。

《计算机组成原理》唐朔飞 重点、难点课件

如 16 MB (227位)的存储器

寻址范围

按 字节 寻址 按 字(16位)寻址 按 字 (32位)寻址

224= 16 M 223 = 8 M 222 = 4 M

字节 寻址 字(16位)寻址

24 位 23 位

22 位

字 (32位)寻址

容量 224 × 23 = 227位 223 × 24 = 227位 222 × 25 = 227位

字块2m-1

某一主存块 j 按模 Q 映射到 缓存 的第 i 组中的 任一块

例 假设主存容量为 512 KB,Cache 容量为 4KB,每个字块为

16 个字,每个字 32 位。 (1)Cache 地址有多少位?可容纳多少块?

根据 Cache 容量为 4KB 得 Cache 地址 12 位 4KB/4B = 1K字 1K/16 = 64 块 (2)主存地址有多少位?可容纳多少块? 根据 512KB 得主存地址 19 位 512KB/4B = 128K字 128K/16 = 8192 块。 (3)在直接映射方式下,主存的第几块映射到 Cache 中的第 5 块(设起始字块为第 1 块)? 主存的第 5,64 + 5,2×64 + 5, … , 8192 – 64 + 5 块 能映射到 Cache 的第 5 块

第1章 计算机系统概论

计算机

第1篇 概论

第1章 计算机系统概论

计算机

存储器 I/O

系统总线

第2篇 计算机系统的硬件结构

CPU

第1章 计算机系统概论

计算机

存储器 I/O

第3篇 CPU

系统总线

CPU

中央处理器

ALU CU

CPU 内部互连

计算机组成原理课后答案(第二版)_唐朔飞_第九章

转间址操作

Y

间址操作 X(MDR)MAR MM读 OP=? STA MDRMAR ACMDR MM写

MDRo,MARi 1 R

MDRo,MARi ACo,MDRi 1 W 注:指令中X为形式地址

13. 设CPU内部结构如图9.4所示,此 外还设有R1~R4四个寄存器,它们各自的 输入和输出端都与内部总线相通,并分别 受控制信号控制(如R2i为寄存器R2的输入 控制;R2o为寄存器R2的输出控制)。要 求从取指令开始,写出完成下列指令所需 的全部微操作和控制信号。 (1)ADD R2,@ R4 ; ((R2)+((R4)) R2,寄存器间接寻址) (2)SUB R1,@ mem ; ((R1)-((mem)) R1,存储器间接寻址) 解:解题方法步骤同第11题。 (1) “ADD R2,@ R4”指令的流程 图和全部微操作控制信号如下:

R2o,Yi R4o,MARi 1 R MDRo,ALUi,+

Zo,R2i

(2)SUB R1,@ mem指令流程图和全部微命令如下: PCMAR MM读 PC+1 PC MDR IR I=1?

PCo,MARi

1 R +1(图中未标出, 可与前一步并行) MDRo,IRi

SUB

PCo,MARi

R/-W=R(MAR、MDR 与M直连,故不需控制) MDRo,IRi

+1(图中未标出, 可与前一步并行)

SUB XR+D(IR) EAR EARBusMAR M(MAR)MDR ACC﹣MDRLATCH LATCHBusACC

7. 某CPU的主频为10MHz,若已 知每个机器周期平均包含4个时钟周期, 该机的平均指令执行速度为1MIPS, 试求该机的平均指令周期及每个指令 周期含几个机器周期?若改用时钟周 期为0.4µ s的CPU芯片,则计算机的平 均指令执行速度为多少MIPS?若要得 到平均每秒80万次的指令执行速度, 则应采用主频为多少的CPU芯片?

Y

间址操作 X(MDR)MAR MM读 OP=? STA MDRMAR ACMDR MM写

MDRo,MARi 1 R

MDRo,MARi ACo,MDRi 1 W 注:指令中X为形式地址

13. 设CPU内部结构如图9.4所示,此 外还设有R1~R4四个寄存器,它们各自的 输入和输出端都与内部总线相通,并分别 受控制信号控制(如R2i为寄存器R2的输入 控制;R2o为寄存器R2的输出控制)。要 求从取指令开始,写出完成下列指令所需 的全部微操作和控制信号。 (1)ADD R2,@ R4 ; ((R2)+((R4)) R2,寄存器间接寻址) (2)SUB R1,@ mem ; ((R1)-((mem)) R1,存储器间接寻址) 解:解题方法步骤同第11题。 (1) “ADD R2,@ R4”指令的流程 图和全部微操作控制信号如下:

R2o,Yi R4o,MARi 1 R MDRo,ALUi,+

Zo,R2i

(2)SUB R1,@ mem指令流程图和全部微命令如下: PCMAR MM读 PC+1 PC MDR IR I=1?

PCo,MARi

1 R +1(图中未标出, 可与前一步并行) MDRo,IRi

SUB

PCo,MARi

R/-W=R(MAR、MDR 与M直连,故不需控制) MDRo,IRi

+1(图中未标出, 可与前一步并行)

SUB XR+D(IR) EAR EARBusMAR M(MAR)MDR ACC﹣MDRLATCH LATCHBusACC

7. 某CPU的主频为10MHz,若已 知每个机器周期平均包含4个时钟周期, 该机的平均指令执行速度为1MIPS, 试求该机的平均指令周期及每个指令 周期含几个机器周期?若改用时钟周 期为0.4µ s的CPU芯片,则计算机的平 均指令执行速度为多少MIPS?若要得 到平均每秒80万次的指令执行速度, 则应采用主频为多少的CPU芯片?

计算机组成原理课后答案第二版唐朔飞第九章省公共课一等奖全国赛课获奖课件

第12页

11. 设CPU内部结构如图9.4所表 示,另外还设有B、C、D、E、H、L 六个存放器,它们各自输入和输出端 都与内部总线相通,并分别受控制信 号控制(如Bi为存放器B输入控制;Bo 为存放器B输出控制)。要求从取指 令开始,写出完成以下指令所需全部 微操作和控制信号。 (1)ADD B,C;((B)+(C) B) (2)SUB A,H;((AC)-(H) AC)

第27页

14. 设单总线计算机结构如图9.5所表示,其中 M为主存,XR为变址存放器,EAR为有效地址 存放器,LATCH为锁存器。假设指令地址已存 于PC中,画出“LDA * D”和“SUB D(XR)”指 令周期信息流程图,并列出对应控制信号序列。

说明:

(1) “LDA * D”指令字中*表示相对寻址, D为相对位移量。

(AC)–(H)Z

ZAC

Ho,Yi ACo,ALUi,– Zo,ACi

第18页

12. CPU结构同上题,写出完成 以下指令所需全部微操作和控制信号 (包含取指令)。

(1)存放器间接寻址无条件转移 指令“JMP @ B”。

(2)间接寻址存数指令“STA @ X”。

解:解题方法步骤同上题。 (1) “JMP @ B”指令流程图和 全部微操作控制信号以下:

第2页

4. 能不能说CPU主频越快,计算 机运行速度就越快?为何?

解:不能说机器主频越快,机器 速度就越快。因为机器速度不但与主 频相关,还与数据通路结构、时序分 配方案、ALU运算能力、指令功效强 弱等各种原因相关,要看综合效果。

第3页

5. 设机器ACPU主频为8MHz,机 器周期含4个时钟周期,且该机平均指 令执行速度是0.4MIPS,试求该机平均 指令周期和机器周期,每个指令周期 中含几个机器周期?假如机器BCPU主 频为12MHz,且机器周期也含4个时钟 周期,试问B机平均指令执行速度为多 少MIPS?

11. 设CPU内部结构如图9.4所表 示,另外还设有B、C、D、E、H、L 六个存放器,它们各自输入和输出端 都与内部总线相通,并分别受控制信 号控制(如Bi为存放器B输入控制;Bo 为存放器B输出控制)。要求从取指 令开始,写出完成以下指令所需全部 微操作和控制信号。 (1)ADD B,C;((B)+(C) B) (2)SUB A,H;((AC)-(H) AC)

第27页

14. 设单总线计算机结构如图9.5所表示,其中 M为主存,XR为变址存放器,EAR为有效地址 存放器,LATCH为锁存器。假设指令地址已存 于PC中,画出“LDA * D”和“SUB D(XR)”指 令周期信息流程图,并列出对应控制信号序列。

说明:

(1) “LDA * D”指令字中*表示相对寻址, D为相对位移量。

(AC)–(H)Z

ZAC

Ho,Yi ACo,ALUi,– Zo,ACi

第18页

12. CPU结构同上题,写出完成 以下指令所需全部微操作和控制信号 (包含取指令)。

(1)存放器间接寻址无条件转移 指令“JMP @ B”。

(2)间接寻址存数指令“STA @ X”。

解:解题方法步骤同上题。 (1) “JMP @ B”指令流程图和 全部微操作控制信号以下:

第2页

4. 能不能说CPU主频越快,计算 机运行速度就越快?为何?

解:不能说机器主频越快,机器 速度就越快。因为机器速度不但与主 频相关,还与数据通路结构、时序分 配方案、ALU运算能力、指令功效强 弱等各种原因相关,要看综合效果。

第3页

5. 设机器ACPU主频为8MHz,机 器周期含4个时钟周期,且该机平均指 令执行速度是0.4MIPS,试求该机平均 指令周期和机器周期,每个指令周期 中含几个机器周期?假如机器BCPU主 频为12MHz,且机器周期也含4个时钟 周期,试问B机平均指令执行速度为多 少MIPS?

计算机组成原理唐朔飞完整版

取x 至运算器中 乘以a 在运算器中 加b 在运算器中 乘以x 在运算器中 加c 在运算器中

指令格式举例

1.2

操作码

地址码

取数 000001 存数 加 乘 打印 停机

α 0000001000 β γ δ

[α]

ACC

[ACC] [ACC]+[γ] [ACC]×[δ]

[ ]

β ACC

ACC 打印机

计算 ax2 + bx + c 程序清单

乘积高位

乘数 乘积低位

被除数

除法 余数

商

X 加数 减数 被乘数 除数

① 加法操作过程

1.2

ACC MQ ALU

X

运算器

指令

加

初态 ACC [M]

[ACC]+[X]

M 被加数 X ACC

② 减法操作过程

1.2

ACC MQ ALU

X

运算器

指令

减M

初态 ACC [M]

[ACC]-[X]

被减数 X ACC

1.2

指令和数据存于

指令

主存单元的地址 操作码 地址码

注释

0

000001 0000001000 取数x至ACC

1

000100 0000001001 乘a得ax,存于ACC中

2

000011 0000001010 加b得ax+b ,存于ACC中

3

000100 0000001000 乘x得(ax+b)x,存于ACC中

计算机

存储器 I/O

第3篇 CPU

系统总线

CPU

中央处理器

ALU CU

CPU 内部互连

计算机组成原理(唐朔飞)CPU结构和功能 PPT

指令1、指令3、 指令 1 与指令 指令存储器和数据存储器分开 6 冲突 指令 、指令 、指令 解决办法 4• 冲突 …… 指令 2 与指令 5 冲突

• 指令预取技术 (适用于访存周期短的情况) 适用于访存周期短的情况)

《计算机组成原理》 计算机组成原理》

2、 控制相关 程序的相近指令之间出现某种关联 、

解决办法 ?

4. 指令的六级流水

t 1

指令 1 指令 2 指令 3 指令 4 指令 5 指令 6 指令 7 指令 8 指令 9 FI

《计算机组成原理》 计算机组成原理》

取指、指令译码、算操作数地址、取操作数、执行指令、 取指、指令译码、算操作数地址、取操作数、执行指令、写操作数

2

DI FI

3

CO DI FI

IF ID EX WR

流水线速度是原来速度的 3 倍

0

1

2

3

4

5

6

7

8

9

10 11

12 13

t

3. 超长指令字

《计算机组成原理》 计算机组成原理》

并行性, 由编译程序 挖掘 出指令间 潜在 的 并行性,将 多条 一条具有 能 并行操作 的指令组合成 一条具有 多个操作码字段 的 超长指令字(可达几百位) 超长指令字(可达几百位) 多个处理部件(EX部件 部件) 采用 多个处理部件 部件

组合逻辑设计 微程序设计 硬连线逻辑

参见 第四篇

存储逻辑

参见 8.4 参见 第六章

2. 中断系统

五、ALU

《计算机组成原理》 计算机组成原理》

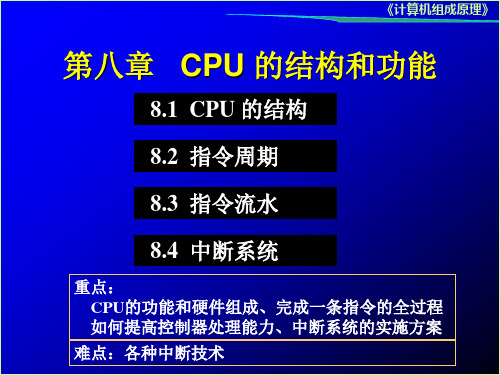

8.2 指 令 周 期

一、 指令周期的基本概念

1 . 指令周期 取出并执行一条指令所需的全部时间 指令周期:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

机器周期 机器周期

3. 多级时序系统

一个指令周期含若干个机器周期 一个机器周期包含若干个时钟周期

CLK

节拍 ) (状态)

9.2

机器周期、节拍(状态)组成多级时序系统

T0

T1

T2

T3

T0

T1

T2

T3

T0

T1

T2

T3

机器周期 (取指令)

机器周期 (取有效地址) 指令周期

机器周期 (执行指令)

节拍 ) (状态)

Yi 地址线 数据线

• 数据线

• MDR

MDRO

MAR MDR AC

MARi

MDRO ACi ACO Yi ALUi ZO

CPU 内 部 总 线

• AC

ACO

ALU

ALUi

•(AC)+(Y) •Z

ZO

Z

控制信号

… … … …

Y Y ALU Z

AC

ACi

三、多级时序系统

1. 机器周期

(1) 机器周期的概念 所有指令执行过程中的一个基准时间 (2) 确定机器周期需考虑的因素 每条指令的执行 步骤 每一步骤 所需的 时间 (3) 基准时间的确定 • 以完成 最复杂 指令功能的时间 为准 • 以 访问一次存储器 的时间 为基准 若指令字长 = 存储字长

第九章 控制单元的功能

9.1 操作命令的分析 9.2 控制单元的功能

9.1 操作命令的分析

完成一条指令分 4 个工作周期

取指周期 间址周期 执行周期 中断周期

9.1 操作命令的分析

一、取指周期

PC 1 R MDR

PC +1 IR

MAR

地址线

CPU MAR CU MDR

地 址 总 线

数 据 总 线

二、控制信号举例

1. 不采用 CPU 内部总线的方式 以 ADD @ X 为例

C2 M M D D R R

9.2

取指周期

C3 PC C0 IR 控制 信号 AC

C1

C4 CU … 控制信号 标志 … … … …

ALU

… … … …

时 钟

M A R

二、控制信号举例

1. 不采用 CPU 内部总线的方式

9.2

3. 机器周期和节拍(状态)与控制信号的关系

T1

M1 T2 T3

9.2

T3

3MHZ CLK A15~A8 AD7~AD0 ALE RD WR IO/M

T4

T1

M2 T2

T3

T1

M3 T2

PCH PCL Instr PCL

PCH byte

IO PORT IO PORT ACC

PC out

PC+1 Ins IR

9.2

控制信号 与操作码有关 (3) 标志 CU 受标志控制 (4) 外来信号 如 INTR HRQ 中断请求 总线请求

2. 输出信号

(1) CPU 内的各种控制信号

Ri Rj PC (PC) + 1

9.2

ALU +、-、与、或 ……

(2) 送至控制总线的信号

MREQ IO/M RD WR INTA HLDA 访存控制信号 访 IO/ 存储器的控制信号 读命令 写命令 中断响应信号 总线响应信号

9.2

(4) 与中断有关的信号

入 出 INTR INTA

X1 X2 Reset out SOD SID Trap RST7.5 RST6.5 RST5.5 INTR INTA AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 Vss 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21

MDR IR

IRi

• MDR

MDRO

MDRO

CPU 内 部 总 线

• OP(IR) • (PC)+ 1

CU PC

控制信号

… … …

Y ALU Z

控制信号

(2) ADD @ X 间址周期 时钟

形式地址

• MDR •1

MDRO

… CU

IRi

9.2

MAR

地址线

地址线

IR IR PC MAR MAR MDR MDR AC Y

C2 M M D D R R C5 PC IR C3 AC

9.2

ADD @ X 间址周期

C1

ALU M A R CU … 控制信号 标志 … … … …

控制 信号

… … … …

时 钟

二、控制信号举例

1. 不采用 CPU 内部总线的方式

C2 M M D D R R C5 PC IR C7 C1 ALU M A R CU … 控制信号 标志 … … … … C6 AC C8

IR(8)

指令译码 和 机器周期 编码

8 B 8) C(8) B(8 8 D 8) E(8) D(8 8 H(8) 8 L(8) SP 16 SP(16 16) PC 16 PC(16 16) IDAL 16 IDAL(16 16)

ALU

定时和控制 时钟

CLK Ready

控制

RD WR ALE

状态

IO/M

(1) 无条件转 JMP X

Ad ( IR ) PC

(2) 条件转移

BAN X

(负则转)

PC

A0 •Ad ( IR ) + A0 ( PC )

4. 三类指令的指令周期

非访存 指令周期 直接访存 指令周期 间接访存 指令周期 转移 指令周期

取指周期 执行周期

9.1

取指周期

执行周期

取指周期

间址周期

执行周期

9.2

3. 联合控制方式

同步与异步相结合

4. 人工控制方式

(1) Reset (2) 连续 和 单条 指令执行转换开关 (3) 符合停机开关

五、多级时序系统实例分析

1. 8085 的组成

INTA INTR SID SOD

9.2

中断控制

8位内部数据总线

I/O I/O控制

AC(8)

TR(8)

FR(5)

DMA

HLDA

复位

Reset

ABR(8)

A15~A8

ADBR(8)

AD7~AD0

2. 8085 的外部引脚

(1) 地址和数据信号

A15~A8 AD7~AD0 SID SOD

X1 X2 Reset out SOD SID Trap RST7.5 RST6.5 RST5.5 INTR INTA AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 Vss 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21

T0

T1

T2

T3

T0

T1

T2

机器周期 机器周期 (取指令) (执行指令) 指令周期

四、控制方式

1. 同步控制方式

9.2

产生不同微操作命令序列所用的时序控制方式 任一微操作均由 统一基准时标 的时序信号控制

CLK

T0

T1

T2

T3

T0

T1

T2

T3

T0

T1

T2

T3

机器周期 (取指令)

机器周期 (取有效地址) 指令周期

(2) 定时和控制信号

入 X1 X2 出 CLK ALE IO/M RD S0 S1 WR

(3) 存储器和 I/O 初始化

入 HOLD Ready 出 HLDA

Vcc HOLD HLDA CLK(out) Rsest in Ready IO/M S1 RD WR ALE S0 A15 A14 A13 A12 A11 A10 A9 A8

(3) 采用中央控制和局部控制相结合的方法

取指周期 执行周期

9.2

T0

T1

T2

T3

机器周期 指令周期

T0

T1

T2

T3

T0

T1

T2

T3 T* T*

局部控制节拍

T0

T1

中央控制节拍

中央控制节拍

T*

局部控制的节拍宽度与 中央控制的节拍宽度一致

2. 异步控制方式

无基准时标信号 无固定的周期节拍和严格的时钟同步 采用 应答方式

Ad(IR) 1 R MDR ACC MAR

9.1

M(MAR)

(ACC) + (MDR)

(2) 存数指令

STA X

Ad(IR) 1 ACC MDR W MDR M(MAR) MAR

(3) 取数指令

LDA X

Ad ( IR ) 1 R MDR MAR

9.1

M ( MAR ) MDR ACC

3. 转移指令

1. 非访存指令

(1) CLA 清A 0 ACC L(ACC) R(ACC) 0 G ACC ACC R(ACC), ACC0 L(ACC), ACC0

9.1

(2) COM 取反 (3) SHR 算术右移 (4) CSL 循环左移 (5) STP 停机指令

ACC0 ACCn

2. 访存指令

(1) 加法指令 ADD X

9.2

取指周期 = 机器周期

2. 时钟周期(节拍、状态)

一个机器周期内可完成若干个微操作 每个微操作需一定的时间 将一个机器周期分成若干个时间相等的 时间段(节拍、状态、时钟周期)

3. 多级时序系统

一个指令周期含若干个机器周期 一个机器周期包含若干个时钟周期

CLK

节拍 ) (状态)

9.2

机器周期、节拍(状态)组成多级时序系统

T0

T1

T2

T3

T0

T1

T2

T3

T0

T1

T2

T3

机器周期 (取指令)

机器周期 (取有效地址) 指令周期

机器周期 (执行指令)

节拍 ) (状态)

Yi 地址线 数据线

• 数据线

• MDR

MDRO

MAR MDR AC

MARi

MDRO ACi ACO Yi ALUi ZO

CPU 内 部 总 线

• AC

ACO

ALU

ALUi

•(AC)+(Y) •Z

ZO

Z

控制信号

… … … …

Y Y ALU Z

AC

ACi

三、多级时序系统

1. 机器周期

(1) 机器周期的概念 所有指令执行过程中的一个基准时间 (2) 确定机器周期需考虑的因素 每条指令的执行 步骤 每一步骤 所需的 时间 (3) 基准时间的确定 • 以完成 最复杂 指令功能的时间 为准 • 以 访问一次存储器 的时间 为基准 若指令字长 = 存储字长

第九章 控制单元的功能

9.1 操作命令的分析 9.2 控制单元的功能

9.1 操作命令的分析

完成一条指令分 4 个工作周期

取指周期 间址周期 执行周期 中断周期

9.1 操作命令的分析

一、取指周期

PC 1 R MDR

PC +1 IR

MAR

地址线

CPU MAR CU MDR

地 址 总 线

数 据 总 线

二、控制信号举例

1. 不采用 CPU 内部总线的方式 以 ADD @ X 为例

C2 M M D D R R

9.2

取指周期

C3 PC C0 IR 控制 信号 AC

C1

C4 CU … 控制信号 标志 … … … …

ALU

… … … …

时 钟

M A R

二、控制信号举例

1. 不采用 CPU 内部总线的方式

9.2

3. 机器周期和节拍(状态)与控制信号的关系

T1

M1 T2 T3

9.2

T3

3MHZ CLK A15~A8 AD7~AD0 ALE RD WR IO/M

T4

T1

M2 T2

T3

T1

M3 T2

PCH PCL Instr PCL

PCH byte

IO PORT IO PORT ACC

PC out

PC+1 Ins IR

9.2

控制信号 与操作码有关 (3) 标志 CU 受标志控制 (4) 外来信号 如 INTR HRQ 中断请求 总线请求

2. 输出信号

(1) CPU 内的各种控制信号

Ri Rj PC (PC) + 1

9.2

ALU +、-、与、或 ……

(2) 送至控制总线的信号

MREQ IO/M RD WR INTA HLDA 访存控制信号 访 IO/ 存储器的控制信号 读命令 写命令 中断响应信号 总线响应信号

9.2

(4) 与中断有关的信号

入 出 INTR INTA

X1 X2 Reset out SOD SID Trap RST7.5 RST6.5 RST5.5 INTR INTA AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 Vss 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21

MDR IR

IRi

• MDR

MDRO

MDRO

CPU 内 部 总 线

• OP(IR) • (PC)+ 1

CU PC

控制信号

… … …

Y ALU Z

控制信号

(2) ADD @ X 间址周期 时钟

形式地址

• MDR •1

MDRO

… CU

IRi

9.2

MAR

地址线

地址线

IR IR PC MAR MAR MDR MDR AC Y

C2 M M D D R R C5 PC IR C3 AC

9.2

ADD @ X 间址周期

C1

ALU M A R CU … 控制信号 标志 … … … …

控制 信号

… … … …

时 钟

二、控制信号举例

1. 不采用 CPU 内部总线的方式

C2 M M D D R R C5 PC IR C7 C1 ALU M A R CU … 控制信号 标志 … … … … C6 AC C8

IR(8)

指令译码 和 机器周期 编码

8 B 8) C(8) B(8 8 D 8) E(8) D(8 8 H(8) 8 L(8) SP 16 SP(16 16) PC 16 PC(16 16) IDAL 16 IDAL(16 16)

ALU

定时和控制 时钟

CLK Ready

控制

RD WR ALE

状态

IO/M

(1) 无条件转 JMP X

Ad ( IR ) PC

(2) 条件转移

BAN X

(负则转)

PC

A0 •Ad ( IR ) + A0 ( PC )

4. 三类指令的指令周期

非访存 指令周期 直接访存 指令周期 间接访存 指令周期 转移 指令周期

取指周期 执行周期

9.1

取指周期

执行周期

取指周期

间址周期

执行周期

9.2

3. 联合控制方式

同步与异步相结合

4. 人工控制方式

(1) Reset (2) 连续 和 单条 指令执行转换开关 (3) 符合停机开关

五、多级时序系统实例分析

1. 8085 的组成

INTA INTR SID SOD

9.2

中断控制

8位内部数据总线

I/O I/O控制

AC(8)

TR(8)

FR(5)

DMA

HLDA

复位

Reset

ABR(8)

A15~A8

ADBR(8)

AD7~AD0

2. 8085 的外部引脚

(1) 地址和数据信号

A15~A8 AD7~AD0 SID SOD

X1 X2 Reset out SOD SID Trap RST7.5 RST6.5 RST5.5 INTR INTA AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 Vss 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21

T0

T1

T2

T3

T0

T1

T2

机器周期 机器周期 (取指令) (执行指令) 指令周期

四、控制方式

1. 同步控制方式

9.2

产生不同微操作命令序列所用的时序控制方式 任一微操作均由 统一基准时标 的时序信号控制

CLK

T0

T1

T2

T3

T0

T1

T2

T3

T0

T1

T2

T3

机器周期 (取指令)

机器周期 (取有效地址) 指令周期

(2) 定时和控制信号

入 X1 X2 出 CLK ALE IO/M RD S0 S1 WR

(3) 存储器和 I/O 初始化

入 HOLD Ready 出 HLDA

Vcc HOLD HLDA CLK(out) Rsest in Ready IO/M S1 RD WR ALE S0 A15 A14 A13 A12 A11 A10 A9 A8

(3) 采用中央控制和局部控制相结合的方法

取指周期 执行周期

9.2

T0

T1

T2

T3

机器周期 指令周期

T0

T1

T2

T3

T0

T1

T2

T3 T* T*

局部控制节拍

T0

T1

中央控制节拍

中央控制节拍

T*

局部控制的节拍宽度与 中央控制的节拍宽度一致

2. 异步控制方式

无基准时标信号 无固定的周期节拍和严格的时钟同步 采用 应答方式

Ad(IR) 1 R MDR ACC MAR

9.1

M(MAR)

(ACC) + (MDR)

(2) 存数指令

STA X

Ad(IR) 1 ACC MDR W MDR M(MAR) MAR

(3) 取数指令

LDA X

Ad ( IR ) 1 R MDR MAR

9.1

M ( MAR ) MDR ACC

3. 转移指令

1. 非访存指令

(1) CLA 清A 0 ACC L(ACC) R(ACC) 0 G ACC ACC R(ACC), ACC0 L(ACC), ACC0

9.1

(2) COM 取反 (3) SHR 算术右移 (4) CSL 循环左移 (5) STP 停机指令

ACC0 ACCn

2. 访存指令

(1) 加法指令 ADD X

9.2

取指周期 = 机器周期

2. 时钟周期(节拍、状态)

一个机器周期内可完成若干个微操作 每个微操作需一定的时间 将一个机器周期分成若干个时间相等的 时间段(节拍、状态、时钟周期)