实验一半加器的设计

全加器与半加器原理及电路设计

全加器与半加器原理及电路设计全加器是一种电子逻辑电路,用于执行二进制加法。

它由三个输入端(A, B, Cin)和两个输出端(S, Cout)组成。

其中,输入端A和B是要相加的二进制位,Cin是前一位的进位,输出端S是和的结果,Cout是是否有进位。

全加器可以通过组合多个半加器来构建。

半加器是全加器的组成部分,它只有两个输入端(A, B)和两个输出端(S, Cout)。

半加器只能够完成一位二进制加法,不考虑进位情况。

其中,输入端A和B是要相加的二进制位,输出端S是和的结果,Cout是是否有进位。

半加器的电路设计相对简单,可以通过逻辑门实现。

接下来,我将详细介绍全加器和半加器的原理和电路设计。

1.半加器原理及电路设计:半加器的真值表如下:A ,B , S , Cout0,0,0,00,1,1,01,0,1,01,1,0,1可以看出,输出端S等于两个输入端A和B的异或结果,输出端Cout等于两个输入端A和B的与运算结果。

半加器的电路设计可以使用两个逻辑门实现。

一个逻辑门用于计算和的结果S,另一个逻辑门用于计算进位Cout。

S = A xor BCout = A and B逻辑门可以采用与门、或门和异或门实现。

常用的逻辑门包括与非门(NAND)和异或门(XOR)。

所以,半加器的电路设计可以使用两个与非门和一个异或门实现。

2.全加器原理及电路设计:全加器的真值表如下:A ,B , Cin , S , Cout0,0,0,0,00,0,1,1,00,1,0,1,00,1,1,0,11,0,0,1,01,0,1,0,11,1,0,0,11,1,1,1,1可以看出,输出端S等于三个输入端A、B和Cin的异或结果,输出端Cout等于输入端A、B和Cin的与运算结果和A和B的或运算结果的与运算结果。

全加器可以由两个半加器和一个或门组成。

其中,两个半加器用于计算S的低位和Cout的低位,而或门用于计算Cout的高位。

VHDL实验半加器等等指导书

实验一 半加器和全加器的设计一、 实验目的1、掌握图形的设计方式;2、掌握自建元件及调用自建元件的方法;3、熟练掌握MAXPLUS II 的使用。

二、实验内容1、熟练软件基本操作,完成半加器和全加器的设计;2、正确设置仿真激励信号,全面检测设计逻辑;3、综合下载,进行硬件电路测试。

三、实验原理1、半加器的设计半加器只考虑了两个加数本身,没有考虑由低位来的进位。

半加器逻辑表达式:B A B A B A S ⊕=+=;AB C =2.全加器的设计全加器除考虑两个加数外,还考虑了低位的进位。

全加器逻辑表达式: 1-⊕⊕=i i i i C B A S ;AB C B A C i i i i +⊕=-1)(3、利用半加器元件完成全加器的设计 (1)图形方式其中HADDER 为半加器元件。

四、实验步骤1、完成图形半加器设计。

2、完成VHDL 半加器设计与仿真(记录仿真波形)。

3、完成VHDL 全加器设计与仿真(记录仿真波形)。

4、利用半加器元件进行图形的全加器设计。

五、思考题:1、怎样自建元件?自建元件的调用要注意什么?实验二二位加法计数器的设计一、实验目的1、掌握二位加法计数器的原理;2、掌握二位加法计数器的VHDL描述。

3、深入理解VHDL中元件例化的意义。

二、实验内容1、完成带进位功能二位加法计数器的VHDL设计;2、正确设置仿真激励信号,全面检测设计逻辑;3、综合下载,进行硬件电路测试。

三、实验原理1、二位加法计数器中使用了矢量类型的数据,用来表示计数的数值。

2、元件的例化就是元件的调用,是层次化设计的基础。

具体设计程序由学生自己完成。

四、实验步骤1、了解二位加法计数器的工作原理。

2、用VHDL文本方式设计二位加法计数器。

3、进行二位加法计数器的设计仿真(记录仿真波形)。

4、进行二位加法计数器的设计下载与测试。

五、思考题1、怎样设计“减法”计数器?2、进位信号的设置应注意什么?实验三基于QUARTUSII图形输入电路的设计一、实验目的1、通过一个简单的3—8译码器的设计,掌握组合逻辑电路的设计方法。

半加器和全加器的设计

一、一、 半加器和全加器的设计半加器和全加器的设计

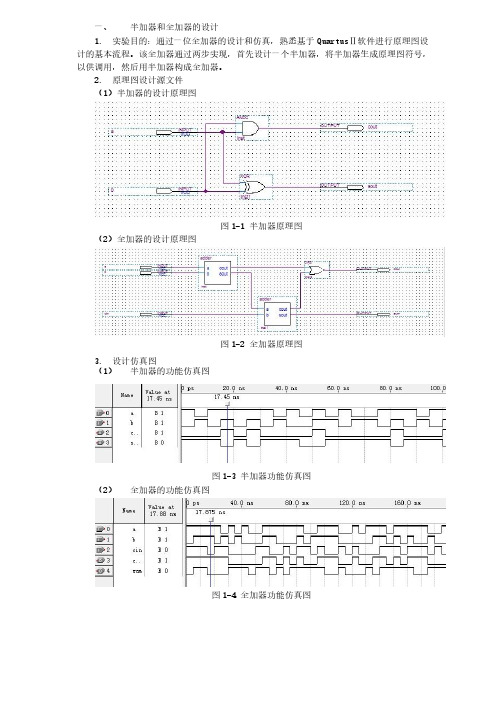

1.1. 实验目的:通过一位全加器的设计和仿真,熟悉基于Quartus QuartusⅡ软件进行原理图设Ⅱ软件进行原理图设计的基本流程。

该全加器通过两步实现,首先设计一个半加器,将半加器生成原理图符号,以供调用,然后用半加器构成全加器。

以供调用,然后用半加器构成全加器。

2.2. 原理图设计源文件原理图设计源文件

(1)半加器的设计原理图)半加器的设计原理图

图1-1 半加器原理图半加器原理图

(2)全加器的设计原理图)全加器的设计原理图

图1-2 全加器原理图全加器原理图

3.3. 设计仿真图设计仿真图

(1) 半加器的功能仿真图半加器的功能仿真图

图1-3 半加器功能仿真图半加器功能仿真图

(2) 全加器的功能仿真图全加器的功能仿真图

图1-4 全加器功能仿真图全加器功能仿真图。

半加器、全加器 实验指导书 任务书

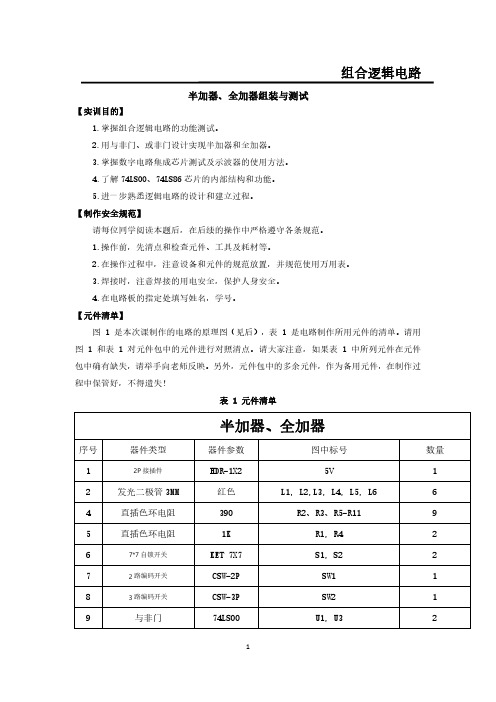

组合逻辑电路半加器、全加器组装与测试【实训目的】1.掌握组合逻辑电路的功能测试。

2.用与非门、或非门设计实现半加器和全加器。

3.掌握数字电路集成芯片测试及示波器的使用方法。

4.了解74LS00、74LS86芯片的内部结构和功能。

5.进一步熟悉逻辑电路的设计和建立过程。

【制作安全规范】请每位同学阅读本题后,在后续的操作中严格遵守各条规范。

1.操作前,先清点和检查元件、工具及耗材等。

2.在操作过程中,注意设备和元件的规范放置,并规范使用万用表。

3.焊接时,注意焊接的用电安全,保护人身安全。

4.在电路板的指定处填写姓名,学号。

【元件清单】图1是本次课制作的电路的原理图(见后),表1是电路制作所用元件的清单。

请用图1和表1对元件包中的元件进行对照清点。

请大家注意,如果表1中所列元件在元件包中确有缺失,请举手向老师反映。

另外,元件包中的多余元件,作为备用元件,在制作过程中保管好,不得遗失!表1元件清单半加器、全加器序号器件类型器件参数图中标号数量12P接插件HDR-1X25V1 2发光二极管3MM红色L1,L2,L3,L4,L5,L66 4直插色环电阻390R2、R3、R5-R119 5直插色环电阻1K R1,R42 67*7自锁开关KET7X7S1,S22 72路编码开关CSW-2P SW11 83路编码开关CSW-3P SW21 9与非门74LS00U1,U3210异或门74LS86U2,U4212座子座子DIP14U1-U4413PCB 板子PCB 板子PCB板子1【实训内容及测试】一、半加器设计1、半加器分析:半加器(一位二进制)只考虑了两个加数本身,没有考虑由低位来的进位。

输入端有2个,分别为加数与被加数;输出端有2个,分别为和与进位。

2、半加器的真值表:3、半加器的逻辑表达式:4、逻辑电路与符号二、全加器设计1、全加器分析:半加器(一位二进制)全加器除考虑两个加数外,还考虑了低位的进位。

输入端有3个,分别为加数、被加数与低位进位。

二进制数半加器设计

二进制数半加器设计一、引言二进制数半加器是一种基本的数字逻辑电路,用于将两个二进制数进行半位加法运算。

在全加器的基础上,二进制数半加器能够处理两个一位数的二进制数,不考虑进位。

本文将介绍如何设计一个二进制数半加器。

二、设计思路二进制数半加器的设计思路如下:1. 输入两个一位数的二进制数A和B;2. 将A和B进行异或运算,得到异或结果S;3. 将A和B进行与运算,得到与结果G;4. 将S和G进行或运算,得到最终的半加和S'。

三、电路设计根据上述设计思路,我们可以设计一个二进制数半加器的电路。

该电路由以下几个部分组成:1. 输入端:输入两个一位数的二进制数A和B;2. 异或门:将A和B进行异或运算,得到异或结果S;3. 与门:将A和B进行与运算,得到与结果G;4. 或门:将S和G进行或运算,得到最终的半加和S'。

四、工作原理二进制数半加器的工作原理如下:1. 当A和B的某一位相同(0或1)时,异或结果S为0,与结果G为1;2. 当A和B的某一位不同时,异或结果S为1,与结果G为0;3. 由于异或结果S和与结果G是互补的,所以最终的半加和S'为1。

五、实现方式二进制数半加器的实现方式有很多种,包括使用集成电路、使用可编程逻辑器件(如FPGA)等。

其中,使用集成电路实现方式较为简单,但成本较高;使用可编程逻辑器件实现方式较为灵活,但需要一定的编程技术。

无论哪种实现方式,都需要对电路进行适当的布局和布线,以保证电路的可靠性和稳定性。

六、总结本文介绍了如何设计一个二进制数半加器,包括设计思路、电路设计、工作原理以及实现方式等方面。

通过这个设计,我们可以更加深入地了解二进制数的基本运算原理以及数字逻辑电路的设计方法。

在实际应用中,二进制数半加器可以用于各种数字系统中,如计算机、通信设备等。

半加器&全加器

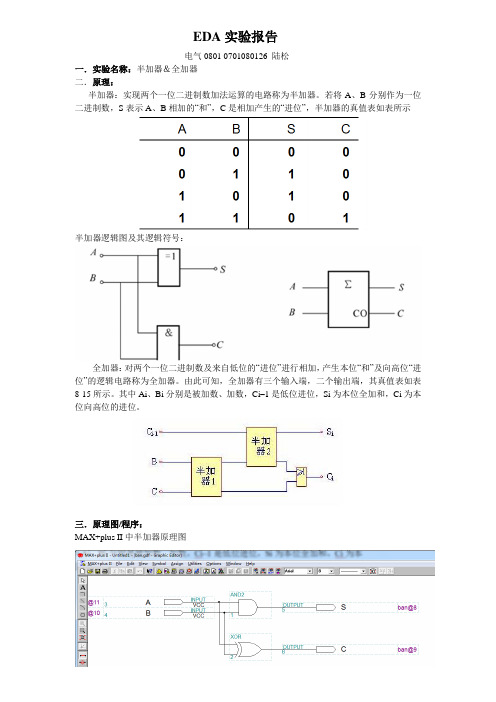

EDA实验报告电气0801 0701080126 陆松一.实验名称:半加器&全加器二.原理:半加器:实现两个一位二进制数加法运算的电路称为半加器。

若将A、B分别作为一位二进制数,S表示A、B相加的“和”,C是相加产生的“进位”,半加器的真值表如表所示半加器逻辑图及其逻辑符号:全加器:对两个一位二进制数及来自低位的“进位”进行相加,产生本位“和”及向高位“进位”的逻辑电路称为全加器。

由此可知,全加器有三个输入端,二个输出端,其真值表如表8-15所示。

其中Ai、Bi分别是被加数、加数,Ci–1是低位进位,Si为本位全加和,Ci为本位向高位的进位。

三.原理图/程序:MAX+plus II中半加器原理图VHDL程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY HALF_ADDER ISPORT(A,B:IN STD_LOGIC;S,CO:OUT STD_LOGIC);END HALF_ADDER;ARCHITECTURE HALF_ADDER OF HALF_ADDER IS COMPONENT HALF_ADDERPORT(A,B:IN STD_LOGIC;S,CO:OUT STD_LOGIC);END COMPONENT;BEGINS<='0' WHEN A='0' AND B='0' ELSE'1'WHEN A='0' AND B='1' ELSE'1' WHEN A='1' AND B='0' ELSE'0' WHEN A='1' AND B='1';CO<='0' WHEN A='0' AND B='0' ELSE'0' WHEN A='0' AND B='1' ELSE'0' WHEN A='1' AND B='0' ELSE'1' WHEN A='1' AND B='1';END HALF_ADDER;MAX+plus II中全加器原理图VHDL程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY FULL_SUBER ISPORT(A,B,CIN:IN STD_LOGIC;CO,S:OUT STD_LOGIC);END FULL_SUBER;ARCHITECTURE FULL OF FULL_SUBER IS COMPONENT HALF_SUBERPORT(A,B:IN STD_LOGIC;S,CO:OUT STD_LOGIC);END COMPONENT;SIGNAL S1,S2,S3:STD_LOGIC;BEGINU0:HALF_SUBER PORT MAP(A,B,S2,S1);U1:HALF_SUBER PORT MAP(S2,CIN,S,S3);CO<=S1 OR S3;END FULL;四.实验步骤:步骤1:为本项工程设计建立文件夹,文件夹不能为中文名。

组合逻辑电路设计之全加器、半加器

班级姓名学号实验二组合电路设计一、实验目的(1)验证组合逻辑电路的功能(2)掌握组合逻辑电路的分析方法(3)掌握用SSI小规模集成器件设计组合逻辑电路的方法(4)了解组合逻辑电路集中竞争冒险的分析和消除方法二、实验设备数字电路实验箱,数字万用表,74LS00,74LS86三、实验原理1.组合逻辑概念通常逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。

组合逻辑电路又称组合电路,组合电路的输出只决定于当时的外部输入情况,与电路的过去状态无关。

因此,组合电路的特点是无“记忆性”。

在组成上组合电路的特点是由各种门电路连接而成,而且连接中没有反馈线存在。

所以各种功能的门电路就是简单的组合逻辑电路。

组合电路的输入信号和输出信号往往不只一个,其功能描述方法通常有函数表达式、真值表,卡诺图和逻辑图等几种。

实验中用到的74LS00和74LS86的引脚图如图所示。

00 四2输入与非门Vcc4B4A4Y3B3A3Y Array 1A1B1Y2A2B2Y GND2.组合电路的分析方法。

组合逻辑电路分析的任务是:对给定的电路求其逻辑功能,即求出该电路的输出与输入之间的关系,通常是用逻辑式或真值表来描述,有时也加上必须的文字说明。

分析一般分为一下几个步骤:(1)由逻辑图写出输出端的逻辑表达式,简历输入和输出之间的关系。

(2)列出真值表。

(3)根据对真值表的分析,确定电路功能。

3.组合逻辑电路的设计方法。

组合逻辑电路设计的任务是:由给定的功能要求,设计出相应的逻辑电路。

一般设计的逻辑电路的过程如图:(1)通过对给定问题的分心,获得真值表。

在分析中要特别注意实际问题如何抽象为几个输入变量和几个输出变量直接的逻辑关系问题,其输出变量之间是否存在约束关系,从而过得真值表或简化真值表。

(2)通过卡诺图化简或逻辑代数化简得出最简与或表达式,必要时进行逻辑式的变更,最后画出逻辑图。

(3)根据最简逻辑表达式得到逻辑电路图。

四.实验内容。

1.分析,测试半加器的逻辑功能。

与非半加器实验电路图6则

与非半加器实验电路图6则以下是网友分享的关于与非半加器实验电路图的资料6篇,希望对您有所帮助,就爱阅读感谢您的支持。

实验1-2TTL与非门电路+半加器全加器(1)实验一TTL 集成与非门电路一. 实验目的1. 熟悉TTL 集成与非门外形及外部引线的排列。

2. 验证TTL 与非门的逻辑功能。

3. 试用与非门接成其它几种逻辑门的方法并熟悉它们的逻辑功能。

二. 实验仪器和芯片1. SXJ —3C 数字电路学习机2. 74LS00三. 实验内容和步骤 1. 熟悉实验设备:熟悉通用实验箱的结构和使用方法,熟悉74LS00集成块的外形和引线情况。

2. 测量与非门的逻辑功能将74LS00中的一个与非门的两个输入端分别接到实验箱中的两个电平开关上,输出端接到箱中的逻辑电平指示灯上,接通5V 电源和地,按表1—1 完成逻辑功能的测量。

并规定高电平为逻辑“1”,低电平为逻辑“0”。

3. 74LS00中的与非门分别接成与门、或门、非门、异或门画出接线图并将测试结果1-2表中,根据表分别写出它们的逻辑表达式。

表1—2四.预习内容1. 复习TTL 与非门的工作原理2. 了解74LS00集成电路的逻辑和引线排列图。

五.实验报告要求1.要求写出相应的表达式;2.画出相应的逻辑图;实验二组合逻辑电路的实验分析一. 实验目的1. 掌握组合逻辑电路的分析方法。

2. 验证半加器和全加器的逻辑功能。

3. 了解二进制数的运算规律。

二. 实验仪器设备 1. 数字电路实验箱 2. 万用表 3. 74LS00 三. 实验内容组合电路的分析是根据所给的逻辑电路,写出输入与输出之间的逻辑关系(逻辑函数表达式或真值表)。

从而评定该电路的逻辑功能。

组合电路的分析方法,一般是首先对给定的逻辑电路按逻辑门的连接方式逐一地写出相应的逻辑表达式,然后写出输出函数的表达式(如果需要列其真值表时,可由表达式通过运算求出)。

但这样写出的逻辑函数表达式可能不是最简单的,所以还应该利用逻辑代数的公式或卡诺图进行化简。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一半加器设计一、实验目的1、了解和学习Quartus II 5.1 软件设计平台。

2、了解EDA的设计过程。

3、通过实例,学习和掌握Quartus II 5.1 平台下的图形输入法4、学习和掌握半加器的工作和设计原理。

二、实验仪器PC机,操作系统为Windows2000/XP,本课程所用系统均为WindowsXp下同),Quartus II5.1 设计平台。

三、实验原理加法器是构成算术运算器的基本单元,有来自低位的进位将两个1位二进制数相力口,称为半加。

实现半加运算的电路叫做半加器。

按照二进制加法运算规则可以列出如表1-1所示的半加器真值表。

其中A、B是两个加数,S是相加的和,CO是相加高位的进位。

将S、CO和A、B的关系写成逻辑表达式如下:S 二AB AB = A: BCO 二AB四、实验步骤1、启动Quartus II 5.1 :在Windows操作系统下,单击"开始”,选择"程序”,再选择"altera ”选项下的"Quartus II 5.1 ”命令。

2、新建工程:在File菜单中选择New Project Wizard …,弹出对话框如图1-1所示图1 — 1在这个对话框中,第一行是需要你指定项目保存的路径,支持含中文字符的路径,第二行是需要你为这个项目取一个名称,第三行是需要你为这个项目的顶层实体取个名称,如实验不需要使用芯片,这三个设定好后,点击“ finish ”。

(如何使用芯片及各参数设定将在实验 3 中讲到)出现如下界面在File 菜单中选择New,出现一个对话框如图 1 — 2图1 — 2 选择 Block Diaqram/Schematic File ,然后点击"OK ”。

ft QuBEtus TK - £:7>uuiiKn!x mJ 5D <I I >3i E x/tafi/|Krii/ 3/d D » --£Bl«i£kl .MFjtils £di L £LM * frajiiri,占■■LfriaABtiaLi [lain Ukl?□ GS ®筍而訂T 旦才®曙涉C •轿峙fe ® 0IkCLTJ^dm AI .TO'i. SyriE-Hi/i Pltionti^j k /iBI-A J "Vt'-mmy 扎 CiifcdiWkniW 扎 Eiot 人行WMJ Nfrlrtfl®p 暑讣1F4t IN IK TiRii FlEH. "V |础 1■■中■ | Mb图1 — 34、 保存文件:选菜单File'Save ,在弹出的Save As 对话窗口中,指定存放文件类型、 文件夹和文件名。

这一步也可以放在图形设计完成后进行。

5、 原理图设计输入: (1 )元器件符号放置通过Edit->lnsert Symbol 插入元器件或点击图板左侧的快捷键卜' I Symbol,或双击图板3 、新建文件 \ l±图1— 4在左侧Name下输入你要找的元器件的名称图1 — 5点击“ 0K ”将元器件拖入图板,(2)元器件复制按住Ctrl选中元器件,拖动即可。

(3)元器件移动用鼠标单击并拖动元器件符号至相应地方即可。

若要同时移动多个元器件符号,可以按住鼠标左键画一个将所有要移动的符号包括在内的大矩形,然后用鼠标点中矩形内任意一点就可随意移动。

(4)元器件转动右击需转动元器件符号,可对元器件符号作水平镜像转动( Flip Horizo ntal )和垂直镜像转动(Flip Vertical ),也可按90 °、180 °、270 转动(Rotate by Degrees )。

也可点击图板左侧的快捷键(5) 元器件删除单击选中元器件符号后,用键盘上的 Delete 键删除该符号。

(6) 管脚的命名绘制完所有的元器件符号后,此时所有输入、输出管脚的默认名为 PIN_NAME 用鼠标左键双击PIN_NAME 使其变为黑底白字显示,然后可直接键入管脚名。

本实验的输入分别 是A B ;输出是S 和CO(7) 在元器件之间添加连线① 直接相连:把鼠标移到元器件引脚附近, 鼠标光标会自动由箭头变为十字形, 按住鼠标左键拖动,即可画出连线。

② 引线命名:先点击左侧菜单栏中的 A ,再点击命名的引线使其成为高亮线,然后输入 引线名即可。

相同引线名的所有引线表示连接在一起。

注意:与输入、输出管脚相连的引线名即为管脚名,不能再给输入、输出管脚的引线取其它名称,完成后的半加器如图1-6所示.』QCC :WOT'-5、保存原理图选菜单File'Save 或单击工具栏中的=按钮。

点击保存。

&编译: .......... .图1-6半加器图形设计图如果有多个文件要把这个文件设为当前顶层实体,这样软件编译时就只编译这个文件。

点击projet->Set as Top-level En tityCtrl+Shift+J接下来进行编译,点击processing->Start Compilation,见下图点击File->Open ,在文件类型中将文件后缀名设为 .bsf ,选择*.bsf 的文件,打开• :j>i HE t! U3i IT — C: -JI C x ir.J Sdl *1 aii| ■■ >(! ill/ 9/daa.a - dca« 1 Cvspil -i L ■ L >II Rep L >E 1 - Fl^v ~-JUHB _ ,J ' i□ tf u . :■皤 ~ _3|血+警曙弟 评”时令营連辱(HKIjj Aun Rnpmi Flwi Si R n- DD W< FUl I gj hLi ■&.HIWl A..W •・■■- I. •■凰忑迦Kii.l.arT!■! U l*ml :FCVriiHmaEhj.' B Film 申 DnonU^rir |母 E Ag IkLicri fvLliaf? EZ1 tQiEil T IM*+ di _J .kad.nJ'H 4 宜rndbni 】 ・§_| ?i ttar+ gF_| A EEMH-H -+“ 巴hj T IPLI^AaalnvrI s ! n-FI FWflilmiQ UBJ -HM . JZ TariJda H KFLI &C -TI丫■・Taj-LaRril £atLlgr MtaaE*MiLr ■■•. hi^ioc T*iid 】轉W dlllfti 上 Tdbl'al Hint 朗L 叫 -la-lx 阿 1 C^i^ULIbB. .MHiddMlUl 価"■■皿 lu Av 31 14 JT-27 iCWS. I hl LJ 1Tb I 口扭f/Sm5 SJ full T H ^I I UStralixt 丿 IQ.卿(< ! ■ JEriFQr+MB FanhlMJ -3^ InT?~・winins Quriuii IT iM>*H"¥Lqr窘 Ibt? C MAK J (MT Lm_u ■- -T ■ IJL_3*L>.11p_f :i 1 ■ a= i£f ■jp_£ilia=^ff d ・・ ~c田④In 氐. ¥ Jr.r I田舉lnb X* Inh.阳 Jj ]nrj 田:® Inb ln£> ^UhT t'JE IE AlC-MliLrir rhE EU£*ECtill. D 'UTiri, D «U*E^riCCP.V ^IELC Qur t^Ji II laaias A M I TUITdaMtfid (MT LuUQ LLine —<n ,LC4_MLLLici_£ili»iifr£i! dtflia ~c diaa "n LiBiSE_tfad.TBLi_!MhlfLiE<*CL tpj 'fks IdQffita )1 L Lfi L M .) iBfatL*Fi plh "S" ■< T 9VS AC4w'.ua II Tiei*E. hHLyEsr TW TiEJAmi, Q wrflri,. C R <34MT L*JE IE Full C HF -S I I L I n. m ncc^util 0 ^n-xrij D rmLi^.F 讯炉叶治1処U * □ - 1 t-w laipi 押"1 想1* CM- 口 a^AiiKBiS | Li I “ jiM ■砂枪期 引昇IA 皆mu 視 色跑tm ■谟 曲叫皿u o 耳啣:令 乐寻审牛 川汀 ■\予和《斤Lmi 曲 入呛入W-inwiij h Or*寿斤鬲口 X $>«■?": ,J M f 7、逻辑器件符号的生成:执行 File\Create/_update->Create Symbol Files for Curre nt File (us n - €::/DuuuMn!x xai Soil ■n[z/ta,fi/||l ;ll/ 3/diiw» - il ・iI djCHD. U ELC I [ill £diL £L#r frajairl, JjEiLfTMaLE Pt;«w ・・LE< in ・h [lain[Cl ”序叭 C1I-3IS GMFtlE,Lcu 富]Fn £■ rb* J 辰 Qp^fi Fl :bjd£1 CdiwwL lU^Fl/C EC Hr-ajbrt 号ur*tksjaciCL^oj! h'ljirl, £L ^4 PrnirlsnCrd«U £ ItShL-k£ A 'A r》口 .虫 1 n 口甲型 3 M,1 W□ O\、■zaiYK 悩 dfciH-.bdl"2+WClFl+J d 0 £通或0Caiw^rL J*rccr 14^134: Fal-iaCk'AbLi E[L thEi p. ral-k Eir CwTU-t ral*Cr^bLi ^jntcl J L L II tsr Ccrr^&L J L I» CmLi fe^ILI SE I RJ ^I Filai Jw CarrutrL Fila卫!*■<* 鱼:Ufrsh'L FriEur Ersnii. LmnL YiLai AiC'tnL frii^Lx1-■:r«ilL>r ¥V d«U 少 FiliU13T-II w •* Jh[p •曲T. :+. Jj Jnti ■& ThO ■fl 唇 lo£?筮InFfc- 4vv I vi TE ArnrVLTr "'llD W3*"r3. 0 ・u*zh<ii hBd«iij|JihkHiriiiriJilil!kBaririilJihhfeiriiidj|lil!hBaddiiJilii!iiidiirij|JilikairiiiiUilil!kHdririj|Ji lErriioj Luc ZE T SBIM lukkl^EurLcncn*. L UEI^U M- IUBi»M|_iM ,l -l -l hy_rilin»ffhp-_rilRnrfr ill即日JLK ■常卄軌 xlin ・tL 讯 pi a. "S-" 31 T.^lt cnIE tafcisr AiihlTEsr BAI nEtcdubil 巾 MGH **』0 rtnit<i TECB*pil hH r4rCpdri^d4-LlSd. ft 9. 0 rKThLIflJ 1. E^mPlucniaipf /i E^u-lfia /1. Inta /i.V«TW »J \ CifcstfEnni X /I D^IH*J±'五、问题讨论与提高1、 思考在该实验基础上,如何设计一个全加器?2、 如在编译过程中产生错误如何查错与解决?3、 试用VHDL 语言设计本实验中的半加器D U d!■■ .,':v勒 EtrilLi 呗Sr 宀*42 ®|<]世JfailLraSX t SjX*!l>iiTI E I・畑・ Ti ttBF■【■■■AiaeUvr■031 Tiai.a< AfikljEar■W^K:+ 料]nh A :血 Inh I Ml SJ Tnf- S P.+. AP ]r.E^ ■jj Tnr-- ■H 录 ln£>土 JfJ mtn ®TnFh-kcrriiaf 4MT L UE It ItiT-takLarC A M U J ^JMi'L'JE.U* ™ykB2_MLLlX£l_fllbE"df ,f - LC*_r HLLlB<l._1!llBE"£-fE jMd -J di*a 4v ■- Lvi TE A^k^VLvr ■*■■ iwe^^viFilD w^"ra. 0bBidriJ lihkBBdililjLlilikfiariilil hhhfeiriiiiljl lilihfiHdililJililiilBiddJJilikBBillilJLklihHiriililJiI JETWI IM ^ur i'JE £E T3kiM luthl^EHr电用hp-_rilRn4<r 』•・■+ Snfnh *;沖左# HHTK jLik "A"1 卄 ^xLiaatL^n pi a. ^S-" ai 7.9l5- mQ UT L QE IE takiij AxihljEsr i-tx ncEdubil d Hry 4 rmi t<x輒甩陋 嵋| £) d«u bdi •傭AFP-杯1rw 口冷扣価ritlH >-|助冲■ |* CtfI d<HD. badAWM).W■ |klb4^«MJrili_<dyE B|升 QuHEtua n - C :/Duuuwcnt! X wd Sall an[x/Mfi/|fl :li/ 9/I J IIM - - ilai ?| till £di L 丄L" trajHiri,JjEiL<r*«aLE 比isaLB [lain BfcLji严诃古用Ertiklifa。