硬件实验5

计算机硬件基础实验

计算机硬件基础实验实验1拆卸主机箱(一)实验目的1、理解主机箱内微机各部件。

2、对机箱内主要部件的连接有一个感性理解。

3、感知主机箱内各部件拆卸方法。

(二)实验准备1、每小组一个主机箱。

主要部件包括:主板、CPU、内存条、电源、显卡、声卡、网卡、硬盘、软驱、光驱等。

2、每小组一套工具:螺丝刀和尖嘴钳。

(三)实验时间安排1、建议本次实验安排在第1章学习之后实行本次实验。

2、实验时长为2学时。

(四)本卷须知1、拆卸和安装部件时,一定要先仔细察看,再动手拆卸,不可过度用力以防损坏部件。

2、不会拆卸的部件请求实验指导教师的协助。

(五)实验步骤1、拆开主机箱,观察机箱内部部件。

①打开主机箱,观察主机箱的结构。

②找到以下部件的安装位置,并仔细观察它们的连接方式:主板、CPU、内存条、电源、显卡、声卡、网卡、硬盘、软驱、光驱。

2、拆卸硬盘①仔细观察硬盘在主机箱内的安装方式。

②拔掉电源与硬盘相连的电源线。

③拔掉安在硬盘上的数据排线,并将数据排线的另一端从主板拔出。

④卸掉紧固硬盘的螺丝钉,取下硬盘。

3、拆卸光驱(方法同拆卸硬盘)4、拆卸软驱(方法同拆卸硬盘)5、拆卸扩展卡(包括显卡、声卡、网卡等)①用工具卸掉紧固扩展卡的一个螺丝钉。

②用双手将扩展卡从主板上拔出。

6、拆卸CPU①仔细观察CPU风扇的安装方式。

②在实验教师的指导下拆卸CPU风扇。

③仔细观察CPU的安装方式。

④在实验教师的示范下拆卸CPU。

7、拆卸内存条①用双手掰开内存条插槽两边的白色卡柄。

②取出内存条。

8、拆卸主板①观察主板与主机箱的紧固方式。

②观察信号线在主板上的插法。

③拆卸紧固主板的螺丝钉。

④拔掉安在主板上的信号线和电源线,取出主板。

⑤用尖嘴钳卸下主板与机箱间的铜柱。

9、拆卸电源①观察电源与主机箱的紧固方式。

②拆卸紧固电源的螺丝钉,取出电源。

(六)实验报告实验结束后,完成《实验报告1》实验2微机硬件市场调查(一)实验目的1、理解微机硬件市场各主要部件的市场行情。

汽车产品硬件实验报告模板

汽车产品硬件实验报告模板1. 实验目的本实验的目的是测试汽车产品的硬件性能,包括但不限于发动机、悬挂系统、制动等部件的性能指标。

通过实验评估汽车产品的安全性、稳定性和可靠性。

2. 实验装置与方法2.1 实验装置本实验所使用的实验装置包括汽车产品样车、动力测量设备、悬挂系统测试设备、制动力测试设备等。

2.2 实验方法1. 首先对汽车产品进行外观检查,确保外观无明显损坏。

2. 进行发动机动力测试,使用动力测量设备测量发动机的最大功率和最大扭矩。

3. 进行悬挂系统测试,使用悬挂系统测试设备测试汽车在不同路况下的悬挂性能。

4. 进行制动力测试,使用制动力测试设备测量汽车在不同速度下的制动性能。

5. 对实验数据进行分析和处理,评估汽车产品的硬件性能。

3. 实验过程与结果3.1 外观检查对汽车产品进行外观检查,未发现外观明显损坏,各部件安装正常。

3.2 发动机动力测试使用动力测量设备对汽车产品的发动机进行测试,得到如下结果:- 最大功率:200马力- 最大扭矩:250Nm3.3 悬挂系统测试使用悬挂系统测试设备对汽车产品的悬挂性能进行测试,得到如下结果:- 清障能力:通过2英寸高的障碍物时无明显顿挫感- 高速行驶稳定性:达到60mph时无明显抖动和不稳定感3.4 制动力测试使用制动力测试设备对汽车产品的制动性能进行测试,得到如下结果:- 制动距离:60mph时制动距离为30m- 制动力平衡性:前后制动力平衡性良好4. 实验分析与讨论根据实验结果和数据分析,可以得出以下结论:- 汽车产品的发动机动力表现良好,具备足够的马力和扭矩。

- 悬挂系统在通过障碍物和高速行驶时表现稳定,具备良好的悬挂性能。

- 制动系统在制动距离和制动力平衡性方面符合标准要求。

5. 实验结论根据实验结果和分析,可以得出如下结论:汽车产品在硬件方面的性能表现良好,符合安全、稳定和可靠的要求。

6. 参考文献[1] 实验装置使用手册[2] 汽车产品技术规格说明书以上是一份汽车产品硬件实验报告模板,根据实际情况和实验要求,具体内容可以做适当的调整和修改。

硬件试验方案(详尽版)

硬件试验方案(详尽版)1. 试验目的本次硬件试验的主要目的是对产品进行全面的性能评估,以确保其在满足设计要求的同时,也能满足用户的实际需求。

试验还将关注产品的可靠性和稳定性,以便为后续的产品优化提供有力支持。

2. 试验依据本次试验依据的相关标准和要求包括:- 国家及行业相关标准- 产品设计规范和需求文档- 用户使用环境和场景3. 试验范围与内容3.1 试验范围本次试验的范围包括:- 硬件组件的功能性能- 硬件组件的兼容性- 硬件组件的可靠性和稳定性3.2 试验内容本次试验的内容包括:- 功能性能测试- 兼容性测试- 可靠性测试- 稳定性测试4. 试验方法与步骤4.1 试验方法本次试验采用以下方法:- 实验室环境测试- 实地环境测试- 模拟场景测试4.2 试验步骤本次试验的步骤如下:1. 准备试验环境和设备2. 制定试验计划和方案3. 进行功能性能测试4. 进行兼容性测试5. 进行可靠性测试6. 进行稳定性测试7. 收集和分析试验数据8. 编制试验报告5. 试验条件与设备5.1 试验条件本次试验的条件如下:- 环境温度:10℃~35℃- 相对湿度:20%~80%- 电源:AC 220V,50Hz5.2 试验设备本次试验所需的设备如下:- 测试仪器:XXX测试仪- 计算机:XXX台- 网络设备:XXX台- 其他辅助设备:XXX台6. 试验数据收集与分析试验过程中,需要对各项测试指标进行数据收集,包括:- 功能性能指标数据- 兼容性指标数据- 可靠性指标数据- 稳定性指标数据收集到的数据将进行整理和分析,以便评估产品的性能和稳定性,并为后续的产品优化提供依据。

7. 试验结果判定试验结果的判定依据以下标准:- 功能性能测试:所有测试项目均达到设计要求即为合格- 兼容性测试:产品在各种环境下均能正常工作即为合格- 可靠性测试:产品在规定条件下无故障运行时间为规定时间即为合格- 稳定性测试:产品在长时间运行过程中性能无明显下降即为合格8. 试验安全与环保试验过程中,应严格遵守国家及行业相关安全规定,确保试验人员和设备的安全。

计算机硬件实验指导书(崔丽群))

《计算机硬件基础》课程实验指导书辽宁工程技术大学软件学院2010年2月目录实验上机操作范例实验一汇编语言程序的调试与运行实验二简单程序设计实验三循环程序设计实验四综合程序设计(一)实验五综合程序设计(二)实验六高级汇编技术实验上机操作范例【范例】完成具有如下功能的分段函数1 X>0Y = 0 X=0-1 X<0其中:X存放在内存单元中,Y为结果单元。

【问题分析】根据题意画出程序流程图,如图1所示。

图1 分段函数的程序流程图根据程序流程图编写如下程序DSEG SEGMENTX DW ?Y DW ?DSEG ENDSCSEG SEGMENTASSUME CS: CSEG, DS: DSEGSTART:MOV AX, DSEGMOV DS, AXLEA SI, XMOV AX, [SI]AND AX, AXJNS LP1MOV Y, 0FFH ; X<0JMP END1LP1: JNZ LP2MOV Y, 00HJMP END1LP2: MOV Y, 01HEND1: MOV AH, 4CHINT 21HCSEG ENDSEND START汇编语言程序的开发分为以下4个部分:编辑(生成.asm文件)—→汇编(生成.obj文件)—→连接(生成.exe文件)—→调试。

下面分别通过两种上机环境介绍汇编语言源程序从编辑到生成一个可执行文件(.exe文件)的过程。

一种方法是利用Microsoft公司提供的MASM5版本的工具包(包括edit.exe、masm.exe、link.exe、debug.exe),如图2所示;另一种是利用汇编集成编辑器来完成。

图2 D盘下的MASM5工具包下面的例子按以下几个步骤完成:(1)先编写一个fenduan.asm文件;(2)保存并通过运行masm.exe生成目标文件fenduan.obj;(3)再利用link.exe生成可执行文件fenduan.exe;(4)运行fenduan.exe文件;(5)运行debug fenduan.exe后即可对程序进行跟踪调试。

实验5-阻抗变换器

实验五:7.3阻抗变换器设计

一、设计要求

己设计一个同轴线阶梯阻抗变换器,使特性阻抗分别为Z01=50Ω、Z02=100Ω的两段轴线匹配连接。

要求:变换器N=2,工作频率:f0=5GHz。

已知同轴线的介质为:RT/Duriod5880(εr=2.16),外导体直径D0=7 mm。

按以下设计方法实现:

方法1:最平坦通带特性变换器(二项式)。

方法2:等波纹特性变换器(切比雪夫式),允许的最大波纹为0.05。

确定阻抗变换器的结构尺寸,完成电路图。

仿真分析S11与频率的关系特性,调节电路使其达到指标要求。

比较不同阻抗变换器的性能特点。

二、实验仪器

硬件:PC

软件:AWR软件

三、设计步骤

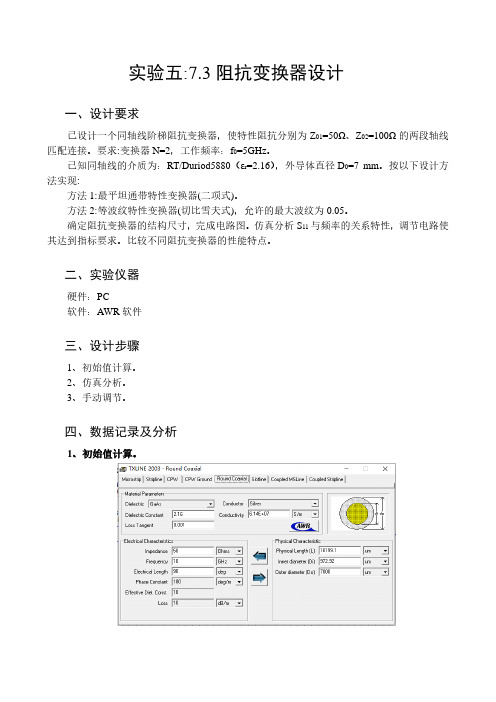

1、初始值计算。

2、仿真分析。

3、手动调节。

四、数据记录及分析

1、初始值计算。

(1)阻抗计算

参数阻值/Ω电长度/deg L/um D i/um Z0150 30 3399.72 2654.88 Z159.4603 90 10199.01 1629.57 Z284.0896 90 10199.01 890.947 Z02100 30 3399.72 603.22

2、仿真分析。

3、手动调节。

优化后的Schematic2:。

计算机硬件实验报告 (6000字)

计算机硬件技术实验报告第四次和第五次实验姓名:李新基学号:2012010630实验班号:23 机器号:39目录实验四. 中断技术 ............................................................................. . (3)一.实验目的 ............................................................................. (3)二.实验基本任务 ............................................................................. .................................. 3 1. 中断响应过程的理解 ............................................................................. (3)2. 中断程序编程练习 ............................................................................. . (6)三、已完成的选作任务。

........................................................................... (8)1. 6)(选做)去掉l4_int.c程序最后的那条无限循环语句,看看有什么现象?可以去掉吗? ........................................................................... (8)3. (选做) 采用事件标志处理中断 ............................................................................. (8)4.(选做) 按键抖动处理 ............................................................................. (10)实验五. 基本时钟和定时功能 ............................................................................. (11)一.实验目的 ............................................................................. . (11)二.实验基础任务。

计算机硬件实验报告

计算机硬件实验报告计算机硬件实验报告引言:计算机硬件是计算机系统的重要组成部分,对于计算机的性能和功能起着至关重要的作用。

在本次实验中,我们对计算机硬件进行了一系列的测试和评估,以了解其性能和稳定性。

本报告将详细介绍实验过程、测试结果和分析。

实验目的:1. 了解计算机硬件的基本构成和工作原理;2. 测试计算机硬件的性能和稳定性;3. 分析测试结果,评估计算机硬件的优劣。

实验过程:1. 硬件组装:我们首先按照指导手册,将各个硬件组件进行正确的组装。

这包括主板、CPU、内存、硬盘、显卡等部件的安装和连接。

通过仔细组装,确保硬件的稳定性和兼容性。

2. 硬件测试工具:为了测试硬件的性能和稳定性,我们使用了一系列的硬件测试工具。

例如,我们使用了CPU-Z来测试CPU的频率和核心数量,使用AIDA64来测试内存的带宽和延迟,使用CrystalDiskMark来测试硬盘的读写速度等。

3. 性能测试:我们对计算机硬件进行了一系列的性能测试。

这包括CPU的计算能力测试、内存的读写速度测试、硬盘的传输速度测试等。

通过这些测试,我们可以了解硬件在不同负载下的表现,并评估其性能优劣。

4. 稳定性测试:为了评估硬件的稳定性,我们进行了一系列的稳定性测试。

例如,我们运行了多个CPU密集型任务,以测试CPU的温度和稳定性。

我们还进行了长时间的内存测试,以检测内存是否存在错误。

通过这些测试,我们可以判断硬件在长时间运行下的稳定性和可靠性。

实验结果:1. CPU性能:经过测试,我们发现CPU的频率和核心数量与其规格相符,并且在不同负载下表现良好。

CPU的温度在正常范围内,稳定性较好。

2. 内存性能:通过测试,我们发现内存的带宽和延迟与其规格相符,并且在读写速度方面表现出色。

内存的稳定性也经过了长时间的测试。

3. 硬盘性能:经过测试,我们发现硬盘的读写速度较快,传输速度稳定。

硬盘的性能在满足我们的需求的同时,也有一定的提升空间。

分析和评估:1. 性能分析:通过测试结果,我们可以看出硬件在不同负载下的性能表现。

通信原理硬件实验报告

通信原理硬件实验报告实验二抑制载波双边带的产生一.实验目的:1.了解抑制载波双边带(SC-DSB)调制器的基本原理。

2.测试SC-DSB 调制器的特性。

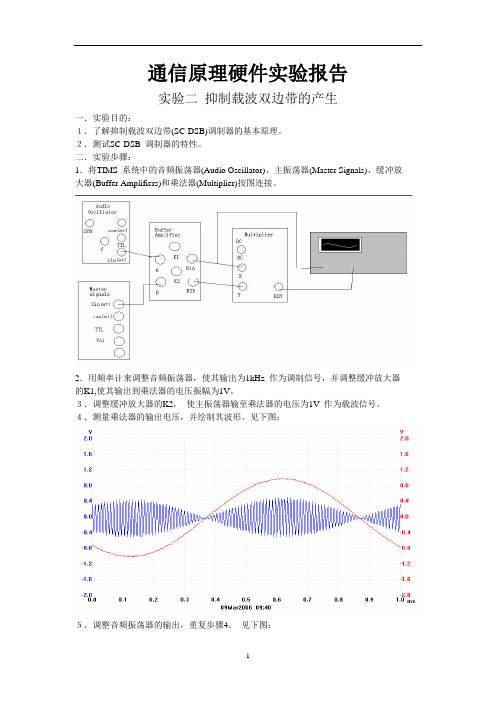

二.实验步骤:1.将TIMS 系统中的音频振荡器(Audio Oscillator)、主振荡器(Master Signals)、缓冲放大器(Buffer Amplifiers)和乘法器(Multiplier)按图连接。

2.用频率计来调整音频振荡器,使其输出为1kHz 作为调制信号,并调整缓冲放大器的K1,使其输出到乘法器的电压振幅为1V。

3.调整缓冲放大器的K2,使主振荡器输至乘法器的电压为1V 作为载波信号。

4.测量乘法器的输出电压,并绘制其波形。

见下图:5.调整音频振荡器的输出,重复步骤4。

见下图:6.将电压控制振荡器(VCO)模快和可调低通滤波器(Tuneable LPF)模块按图连接。

8.将可调低通滤波器的频率范围选择范围至“wide”状态,并将频率调整至最大,此时截至频率大约在12kHz 左右。

LPF 截止频率最大的时候输出:(频响)9.将可调低通滤波器的输出端连接至频率计,其读数除360 就为LPF 的3dB 截止频率。

10.降低可调LPF 的截止频率,使SC-DSB 信号刚好完全通过低通滤波器,记录此频率(fh=fc+F)。

11.再降低3dB 截止频率,至刚好只有单一频率的正弦波通过低通滤波器,记录频率(fl=fc-F)只通过单一频率的LPF 输出:12.变化音频振荡器输出为频率为800Hz、500Hz,重复步骤10、11。

OSC=500HZOSC=800HZ 的频响:三、思考题1、如何能使示波器上能清楚地观察到载波信号的变化?答:可以通过观察输出信号的频谱来观察载波的变化,另一方面,调制信号和载波信号的频率要相差大一些,可通过调整音频震荡器来完成。

2.用频率计直接读SC—DSB 信号,将会读出什么值。

答:围绕一个中心频率来回摆动的值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验环境的内存资与分配

主机系统有32K的RAM空间,地址为0000:0000H~ 0000:7FFFH,分配情况如下: 容量 地址范围 用途

1k 3k

28k

0~03FFH 0400H~0FFFH 1000h-1fffh 2000h-2fffh 3000h-3fffh 4000H~7FFFH

2.硬件连线:8254模块中的CS接译码模块的CS1, GATE1接键正脉冲输出,CLK1接47KHz的时钟信号, OUT1接指示灯D1。 8254芯片的端口地址分配:计数器0为300H,计数器1为 304H,计数器2为308H,控制端口为30CH。 参考程序如下。 .486 CODE SEGMENT USE16 ASSUME CS:CODE ORG 4000H START: ;向控制端口30CH写入方式控制字,初始化计数器1 MOV DX, 30CH MOV AL, 01110010B

中断向量表 系统监控程序空间 缺省分配堆栈 用户数据段 用户分配堆栈 用户代码

程序框架的示例如下。 .486 DATA SEGMENT AT 0200H USE16 ;此处定义变量 DATA ENDS SDATA SEGMENT AT 0300H USE16 STACK DB 500 DUP(?) SDATA ENDS CODE SEGMENT USE16 ASSUME CS: CODE, DS: DATA,SS:SDATA ORG 1000H BEG: MOV AX, SDATA MOV SS, AX MOV SP, 500 MOV AX, DATA MOV DS, AX ;此处添加用户代码 WT: JMP WT CODE ENDS END BEG

第五次实验内容

定时器实验 1. 计数器0工作于方式3,产生频率为1KHz 的方波。 2. 计数器1工作于方式1,观察用GATE的正 脉冲触发计数。 3. 通过计数器1、2级联产生周期为1秒的方 波,将计数器的输出与小灯相连接,观察 小灯的亮灭情况。修改计数初值,观察小 灯闪烁的变化情况。 请参考程序,提前做P14页第1题

.486 CODE SEGMENT USE16 ASSUME CS:CODE ORG 4000H START: ;向控制端口30CH写入方式控制字,初始化计数器1 MOV DX, 30CH MOV AL, 01010110B;只写低字节 OUT DX, AL ;向计数器1端口304H写入计数初值 MOV DX, 304H MOV AL, 47 OUT DX, AL ;写初值 MOV DX, 30CH MOV AL, 10110110B; OUT DX, AL ;向计数器2端口308H写入计数初值 MOV DX, 308H MOV AX, 1000 OUT DX, AL ;写初值 MOV AL,AH OUT DX,AL WT: JMP WT CODE ENDS END START

OUT DX, AL

;向计数器1端口304H写入计数初值 MOV DX, 304H MOV AX, 47000 OUT DX, AL ;写初值 MOV AL,AH OUT DX,AL WT: JMP WT CODE ENDS END START

3.硬件连线:8254模块中的CS接译码模块 的CS1,GATE1,GATE2接+5V,CLK2接 OUT1,CLK1接47KHz的时钟信号,OUT2接 指示灯D1。 8254芯片的端口地址分配:计数器0为300H, 计数器1为304H,计数器2为308H,控制端 口为30CH。 定时器1方式3,初值47,输出1K 定时器2方式3,初值1000,输出1Hz

1.硬件连线:8254模块中的CS接译码模块的CS1,GATE0接+5V, CLK0接47KHz的时钟信号,OUT0接示波器。

8254芯片的端口地址分配:计数器0为300H,计数器1为304H,计数器2为 308H,控制端口为30CH。

参考程序如下。 .486 CODE SEGMENT USE16 ASSUME CS:CODE ORG 4000H START: ;向控制端口30CH写入方式控制字,初始化计数器0 MOV DX, 30CH MOV AL, 00010110B;只写低字节 OUT DX, AL ;向计数器0端口300H写入计数初值 MOV DX, 300H MOV AL, 47 OUT DX, AL ;写初值 WT: JMP WT CODE ENDS END START