STM8L051F3

STM8L选型手册

Package SO-8 SO-8

TSSOP 20 LQFP 48 7x7x1.4 LQFP 64 10x10x1.4 UFQFPN 20 3x3x0.6 TSSOP 20,UFQFPN 20 3x3x0.6 TSSOP 20,UFQFPN 20 3x3x0.6 UFQFPN 28 4x4x0.55 UFQFPN 28 4x4x0.55 LQFP 32 7x7x1.4,UFQFPN 32 5x5x0.55 LQFP 48 7x7x1.4 LQFP 48 7x7x1.4 LQFP 48 7x7x1.4,UFQFPN 48 7x7x0.55 LQFP 48 7x7x1.4,UFQFPN 48 7x7x0.55 LQFP 48 7x7x1.4,UFQFPN 48 7x7x0.55 TSSOP 20,UFQFPN 20 3x3x0.6 TSSOP 20,UFQFPN 20 3x3x0.6 UFQFPN 28 4x4x0.55 UFQFPN 28 4x4x0.55 UFQFPN 28 4x4x0.55,WLCSP28 UFQFPN 28 4x4x0.55,WLCSP28 UFQFPN 32 5x5x0.55 UFQFPN 32 5x5x0.55 LQFP 32 7x7x1.4,UFQFPN 32 5x5x0.55 LQFP 32 7x7x1.4,UFQFPN 32 5x5x0.55 LQFP 80 14x14x1.4 LQFP 64 10x10x1.4 LQFP 64 10x10x1.4 LQFP 48 7x7x1.4,UFQFPN 48 7x7x0.55 LQFP 48 7x7x1.4,UFQFPN 48 7x7x0.55 LQFP 48 7x7x1.4,UFQFPN 48 7x7x0.55 LQFP 32 7x7x1.4,UFQFPN 32 5x5x0.55 LQFP 32 7x7x1.4,UFQFPN 32 5x5x0.55 WLCSP 32L DIE 768 LQFP 80 14x14x1.4 LQFP 64 10x10x1.4 LQFP 64 10x10x1.4 LQFP 80 14x14x1.4 LQFP 64 10x10x1.4

STM8L051低功耗模式实现说明文档

STM8L051低功耗模式测试文档STM8L051的五种低功耗模式wait ,low power run mode,low power wait mode,Ative-Halt mode,Halt mode。

1、WAIT mode在等待模式,CPU的时钟是停止的,被选择的外设继续运行。

W AIT mode 分为两种方式:WFE,WFI。

WFE是等待事件发生,才从等待模式中唤醒。

WFI是等待中断发生,才从等待模式中唤醒。

2、low power run mode在低功耗运行模式下,CPU和被选择的外设在工作,程序执行在LSI或者LSE下,从RAM 中执行程序,Flash和EEPROM都要停止运行。

电压被配置成Ultra Low Power模式。

进入此模式可以通过软件配置,退出此模式可以软件配置或者是复位。

3、low power wait mode这种模式进入是在low power run mode下,执行wfe。

在此模式下CPU时钟会被停止,其他的外设运行情况和low power run mode类似。

在此模式下可以被内部或外部事件、中断和复位唤醒。

当被事件唤醒后,系统恢复到low power run mode。

4、Active-Halt mode在此模式下,除了RTC外,CPU和其他外设的时钟被停止。

系统唤醒是通过RTC中断、外部中断或是复位。

5、Halt mode在此模式下,CPU和外设的时钟都被停止。

系统唤醒是通过外部中断或复位。

关闭内部的参考电压可以进一步降低功耗。

通过配置ULP位和FWU位,也可以6us的快速唤醒,不用等待内部的参考电压启动。

一、各个低功耗模式的代码实现1、WAIT mode等待模式分为两种:WFI和WFE。

1.1 WFI mode当执行“wfi”语句时,系统就进入WFI模式,当中断发生时,CPU被从WFI模式唤醒,执行中断服务程序和继续向下执行程序。

通过置位CFG_GCR的AL位,使主程序服务完中断服务程序后,重新返回到WFI 模式。

STM8L中文参考手册-1

简介之答禄夫天创作本参考手册的目标应用法式开发人员.它提供了完整的信息如何使用stm8l05xx,stm8l15xx和stm8l16xx微控制器的存储器和外围设备.该stm8l05xx / stm8l15xx / stm8l16xx是一个家庭的分歧存储密度的微控制器和外围设备.这些产物是专为超低功耗应用.可用的外设的完整列表,请参阅产物数据表.订购信息,引脚说明,机械和电气设备的特点,请参阅产物数据表.关于STM8 SWIM通信协议信息和调试模块,请参阅用户手册(um0470).在STM8的核心信息,请参阅STM8的CPU编程手册(pm0044).关于编程,擦除和呵护的内部快闪记忆体,请参阅STM8L闪存编程手册(pm0054).表一、类型零件号控制器价值线低密度stm8l05xx设备:stm8l051x3 8KB Flash微控制器价值线中密度stm8l05xx设备:stm8l052x6微控制器与32闪光价值线高密度stm8l05xx设备:stm8l052x8 64-KB闪存微控制器低密度stm8l15x设备:stm8l151c2 / K2 / G2/F2,stm8l151c3 / K3 / G3 / F3微控制器与4KB或8KB Flash中密度stm8l15xx设备:stm8l151c4 / K4 / G4,微控制器stm8l151c6 / K6 / G6,stm8l152c4 / K4和stm8l152c6 / K6微控制器与16-KB或32闪光培养基+密度stm8l15xx设备:stm8l151r6和stm8l152r6微控制器与闪存(32比中密度器件广泛的外设范围)高密度stm8l15xx设备:stm8l151x8和stm8l152x8随着64-KB闪存微控制器(相同的外周设置为中等+)高密度stm8l16xx设备:stm8l162x8微控制器与闪存(相同的外周设置为64-KB高密度stm8l152设备加AES硬件加速器目录1中央处置单位(CPU).30.1.2 CPU的寄存器.30.1.2.1描述CPU寄存器 (30)1.2.2STM8 CPU寄存器图 (34)1.3全球配置寄存器(cfg_gcr).34.1.3.1激活水平 (34)1.3.2游泳禁用 (35)1.3.3描述全局配置寄存器(cfg_gcr) (35)1.3.4全局配置寄存器图及复位值 (35)2 启动ROM . . .363法式存储器和数据存储器.37.3.2术语.37.3.3个主要的快闪存储器的特点.38.3.4记忆的组织.39.3.4.1低密度设备的存储器组织.393.4.2介质密度的装置记忆的组织 (40)3.4.3介质+密度装置记忆的组织 (41)3.4.4高密度存储器组织 (42)3.4.5专有代码区(译).433.4.6用户区(UBC).433.4.7数据的EEPROM(数据) (46)3.4.8主法式区.463.4.9选项字节 (46)3.5内存呵护.47.3.5.1读出呵护.473.5.2内存访问平安系统(质量).473.5.3使写访问选项字节.493.6.1同时读写(读写网) (49)2 / 573文档ID 15226转9rm0031内容3.6.2字节编程 (49)3.6.3字编程.503.6.4块编程.503.6.5选项字节编程.52Flash 3.7的低功耗模式.52.3.8例ICP和IAP.52.3.9.1闪光控制寄存器1(flash_cr1).573.9.2闪光控制寄存器2(flash_cr2).583.9.3 Flash法式存储器的解密密钥寄存器(flash_pukr).58 3.9.4数据EEPROM解除呵护关键寄存器(flash_dukr) (59)3.9.5闪光状态寄存器(flash_iapsr) (59)3.9.6 Flash寄存器图及复位值.604单线接口模块(游泳)和调试模块(DM)614.2个主要特征.61.4.3游泳模式.61.5内存和寄存器图625.1寄存器描述缩写.62.6功率控制(PWR).63.6.2上电复位(POR)/失落电复位(PDR).64.6.3失落电复位(BOR)656.4可编程电压检测器(PVD).66.6.5的内部参考电压(vrefint)676.7.1功率控制和状态寄存器1(pwr_csr1).696.7.2压水堆控制和状态寄存器2(pwr_csr2) (70)6.7.3 PWR寄存器图及复位值.707低功耗模式.71.文件编号15226启9 3 / 573内容rm00317.2周门控时钟(PCG)727.3等候模式(WFI或WFE模式).72.7.4等候中断(WFI)模式.73.7.5等候事件(WFE)模式737.5.1 WFE寄存器.747.5.2 WFE寄存器图及复位值 (79)7.6低功率运行模式.80.7.6.1进入低功率运行模式 (80)7.6.2退出低功率运行模式 (80)7.7低功率待机模式.80.7.8停止模式.81.7.8.1进入暂停模式.817.8.2退出暂停模式 (81)7.9主动停止模式.82.8复位(RST).83.8.1“复位状态”和“下复位”的界说.83.8.2外部复位(NRST引脚)838.2.1异步外部复位的描述 (83)8.2.2配置活动/ PA1引脚作为通用输出.848.3.1上电复位(POR) (84)8.3.2自力看门狗复位 (84)8.3.3窗口看门狗复位 (84)8.3.4游泳复位.848.3.5非法把持码复位.848.4个寄存器.85.8.4.1复位引脚配置寄存器(rst_cr) (85)8.4.2复位状态寄存器(rst_sr).858.4.3 RST寄存器图及复位值 (86)9控制的时钟(CLK).87.9.2 HSE时钟.88.4 / 573文档ID 15226转9rm0031内容9.4 LSE时钟.90.9.5集成电路的时钟.91.9.6系统的时钟源.91.9.6.1系统启动 (91)9.6.2系统时钟切换法式 (92)9.7周门控时钟(PCG)959.8时钟平安系统(CSS)959.8.1时钟平安系统对HSE (95)9.8.2时钟平安系统在伦敦经济学院 (96)9.8.3 CSS LSE控制和状态寄存器(csslse_csr) (97)9.8.4 CSS LSE寄存器图及复位值 (98)9.9时钟和液晶时钟.98.9.10声钟.98.9.11可配置时钟输出能力(CCO).98.9.12个自力的系统时钟的时钟源TIM2 / TIM3.99.9.14时钟寄存器.100.9.14.1系统时钟分频寄存器(clk_ckdivr) (100)9.14.2时钟RTC寄存器(clk_crtcr) (100)9.14.3内部时钟寄存器(clk_ickcr) (102)9.14.4周围门控时钟寄存器1(clk_pckenr1) (103)9.14.5周围门控时钟寄存器2(clk_pckenr2) (104)9.14.6周围门控时钟寄存器3(clk_pckenr3) (105)9.14.7可配置时钟输出寄存器(clk_ccor).1069.14.8外部时钟寄存器(clk_eckcr).1079.14.9系统时钟状态寄存器(clk_scsr) (108)9.14.10系统时钟切换寄存器(clk_swr) (109)9.14.11开关控制寄存器(clk_swcr).1099.14.12时钟平安系统寄存器(clk_cssr) (110)9.14.13时钟嘀寄存器(clk_cbeepr) (111)9.14.14 HSI校准寄存器(clk_hsicalr) (111)9.14.15 HSI时钟校准微调寄存器(clk_hsitrimr) (112)9.14.16 HSI解锁寄存器(clk_hsiunlckr) (112)9.14.17主调节器控制状态寄存器(clk_regcsr) (113)9.14.18时钟寄存器图及复位值 (114)10个通用I / O端口(GPIO).115.10.2个GPIO的主要特点.115.10.3端口的配置与使用.116.10.3.1输入模式 (117)10.3.2输出模式.11810.5未使用的I / O引脚.118.10.7.1函数输入.11810.7.2中断能力.11910.8个输出模式的详细介绍.119.10.8.1交替输出功能.11910.8.2斜率控制.11910.9个GPIO寄存器.120.10.9.1端口X输出数据寄存器(px_odr).12010.9.2端口X引脚输入寄存器(px_idr).12010.9.3 X口数据方向寄存器(px_ddr).12110.9.4端口X控制寄存器1(px_cr1) (121)10.9.5端口X控制寄存器2(px_cr2) (122)10.9.6外围函数映射.12210.9.7 GPIO寄存器图及复位值 (122)11路由接口(RI)和系统配置控制器(syscfg).123.11.2日的主要特点.123.11.2.1 RI功能描述.12511.2.2的I / O组.12511.2.3 TIM1输入捕捉路由 (127)11.2.4 TIM2和TIM3路由.12811.2.5比力器的路由 (129)11.2.6 DAC的路由 (129)11.2.7内部参考电压的路由.1316 / 573文档ID 15226转9rm0031内容11.4日寄存器.131.11.4.1按时器输入捕捉路由寄存器1(ri_icr1) (131)11.4.2按时器输入捕捉路由寄存器2(ri_icr2) (132)11.4.3 I / O输入寄存器1(ri_ioir1) (132)11.4.4 I / O输入寄存器2(ri_ioir2) (132)11.4.5 I / O输入寄存器3(ri_ioir3) (133)11.4.6 I/O控制寄存器1(ri_iocmr1) (133)11.4.7 I/O控制寄存器2(ri_iocmr2) (133)11.4.8 I/O控制寄存器3(ri_iocmr3) (134)11.4.9 I/O寄存器开关1(ri_iosr1) (134)11.4.10 I/O寄存器开关2(ri_iosr2) (136)11.4.11 I/O寄存器开关3(ri_iosr3) (137)11.4.12 IO控制寄存器(ri_iogcr) (138)11.4.13模拟开关寄存器1(ri_ascr1).14011.4.14模拟开关寄存器2(ri_ascr2).14011.4.15电阻控制寄存器(ri_rcr).14111.4.16控制寄存器(ri_cr).14211.4.17 IO屏蔽寄存器1(ri_iomr1) (143)11.4.18 IO屏蔽寄存器2(ri_iomr2) (143)11.4.19 IO屏蔽寄存器3(ri_iomr3) (144)11.4.20 IO屏蔽寄存器4(ri_iomr4) (144)11.4.21 I / O输入寄存器4(ri_ioir4) (145)11.4.22 I/O控制寄存器4(ri_iocmr4) (145)11.4.23 I/O寄存器开关4(ri_iosr4) (146)11.4.24 RI寄存器图及复位值 (147)11.5 syscfg寄存器.149.11.5.1 syscfg映射控制寄存器1(syscfg_rmpcr1) (149)11.5.2 syscfg映射控制寄存器2(syscfg_rmpcr2) (150)软件syscfg映射控制寄存器3(syscfg_rmpcr3) (151)11.5.4 syscfg寄存器图及复位值 (152)12中断控制器(ITC).153.12.2中断屏蔽和处置流程.153.12.2.1服务等候中断.15412.2.2中断源.155文件编号15226启9 7 / 573内容rm003112.4的激活水平/低功率模式控制.157.12.5.1并发中断管理模式 (157)12.5.2嵌套中断管理模式 (158)12.7中断指令.160.12.8中断映射.160.12.9国贸EXTI寄存器.161.12.9.1 CPU条件码寄存器中断位(CCR).16112.9.2软件优先级寄存器X(itc_sprx) (162)12.9.3外部中断控制寄存器1(exti_cr1) (162)12.9.4外部中断控制寄存器2(exti_cr2) (164)12.9.5外部中断控制寄存器3(exti_cr3) (165)12.9.6外部中断控制寄存器4(exti_cr4) (166)12.9.7外部中断状态寄存器1(exti_sr1).16612.9.8外部中断状态寄存器2(exti_sr2).16712.9.9外部中断端口选择寄存器(exti_conf1) (168)12.9.10外部中断端口选择寄存器(exti_conf2) (169)12.9.11 ITC和完全寄存器图及复位值 (170)13直接存储器存取控制器(DMA).171.13.1 DMA的介绍.171.辞汇 (171)13.2 DMA的主要特点.172.13.3.1 DMA交易.17313.3.2 DMA仲裁者 (174)13.3.3 DMA通道 (174)13.3.4卵白Dma1请求映射 (181)13.3.5 DMA硬件要求描述 (183)13.4 DMA低功率模式18413.5 DMA中断.185.13.6 DMA寄存器.185.13.6.1 DMA全球配置和状态寄存器(dma_gcsr) (185)13.6.2 DMA全局中断寄存器1(dma_gir1).18613.6.3 DMA通道配置寄存器(dma_cxcr) (186)8 / 573文档ID 15226转9rm0031内容13.6.4 DMA通道状态和优先级寄存器(dma_cxspr) (188)13.6.5 DMA数据传输寄存器(dma_cxndtr) (189)13.6.6 DMA地址寄存器(外周高dma_cxparh) (189)13.6.7 DMA地址寄存器(dma_cxparl)低周 (190)13.6.8 DMA通道3周地址1地址的高高的记忆寄存器(dma_c3parh_c3m1arh).19013.6.9 DMA通道3周地址低1低内存地址寄存器(dma_c3parl_c3m1arl) (191)13.6.10 DMA存储器地址寄存器(dma_cxm0arh)高0 (191)13.6.11 DMA存储器地址寄存器(dma_cxm0arl)低0 (192)13.6.12 DMA通道3个内存0扩展地址寄存器(dma_c3m0ear) (192)13.6.13 DMA寄存器图及复位值 (193)14模拟到数字转换器(ADC).195.14.1引言195 ADC14.2模数转换器的主要特点.195.14.3 ADC功能描述.196.14.3.1一般描述.19614.3.2数模拟通道 (197)14.3.3 ADC开关控制 (197)14.3.4单转换模式 (197)14.3.5连续转换模式.19914.3.6 ADC时钟.19914.3.7模拟看门狗 (199)14.3.8中断.20014.3.9信道选择(扫描模式) (200)14.3.10数据完整性.20114.3.11 DMA传输 (201)14.3.12配置分辨率.20114.3.13数据对齐 (201)14.3.14可编程采样时间.20214.3.15施密特触发器禁用.20314.3.16温度传感器 (203)14.3.17内部参考电压转换.20414.4 ADC低功耗模式.204.14.5 ADC中断.204.文件编号15226启9 9 / 573内容rm003114.6 ADC寄存器.205.14.6.1 ADC配置寄存器1(adc_cr1) (205)14.6.2 ADC配置寄存器2(adc_cr2) (206)14.6.3 ADC配置寄存器3(adc_cr3) (207)14.6.4 ADC状态寄存器(adc_sr) (208)14.6.5 ADC数据寄存器高(adc_drh) (209)14.6.6 ADC数据寄存器低(adc_drl) (209)14.6.7 ADC的高门槛高(adc_htrh)寄存器.210 14.6.8 ADC的高门槛低(adc_htrl)寄存器.210 14.6.9 ADC低阈值寄存器高(adc_ltrh).210 14.6.10 ADC低阈值寄存器低(adc_ltrl).211 14.6.11 ADC通道序列1寄存器(adc_sqr1).211 14.6.12 ADC通道序列寄存器2(adc_sqr2).212 14.6.13 ADC通道选择扫描3(adc_sqr3) (212)14.6.14 ADC通道选择扫描4(adc_sqr4) (213)14.6.15 ADC触发禁用1(adc_trigr1).21314.6.16 ADC触发禁用2(adc_trigr2).21414.6.17 ADC触发禁用3(adc_trigr3).21414.6.18 ADC触发禁用4(adc_trigr4).21414.6.19 ADC寄存器图及复位值 (215)15个数字到模拟转换器(DAC).216.15.1引言216 DAC15.2个DAC的主要特点.216.15.3的DAC功能描述.218.1. X使DAC通道 (218)15.3.2 DAC输出缓冲区启用 (218)15.3.3 DAC输出开关配置.21815.3.4数据格式.21915.3.5 DAC转换序列 (219)15.3.6 DAC输出电压.21915.3.7 DAC触发选择 (219)15.3.8 DAC的DMA请求 (220)15.3.9 DAC DMA下溢中断 (220)15.3.10噪声的发生 (220)15.3.11三角波的发生 (221)15.3.12双DAC转换 (222)10 / 573文档ID 15226转9rm0031内容15.4个DAC寄存器.226.15.4.1 DAC通道控制寄存器1(dac_chxcr1) (226)15.4.2 DAC通道控制寄存器2(dac_chxcr2) (227)15.4.3 DAC软件触发寄存器(dac_swtrigr) (228)15.4.4 DAC状态寄存器(dac_sr) (228)15.4.5 DAC通道X右对齐的数据坚持寄存器高(dac_rdhrh) (229)15.4.6 DAC通道X右对齐的数据坚持寄存器低(dac_chxrdhrl) (229)15.4.7 DAC通道X左对齐数据坚持寄存器高(dac_chxldhrh) (229)15.4.8 DAC通道X左对齐数据坚持寄存器低(dac_chxldhrl) (230)15.4.9 DAC通道×8位数据坚持寄存器(dac_chxdhr8).23015.4.10 DAC通道X双模式右对齐的数据坚持寄存器高(dac_dchxrdhrh).23115.4.11 DAC通道X双模式右对齐的数据坚持寄存器低(dac_dchxrdhrl) (231)15.4.12 DAC通道X双模式左对齐数据坚持寄存器高(dac_dchxldhrh) (232)15.4.13 DAC通道X左对齐数据坚持寄存器低(dac_dchxldhrl) (232)15.4.14 DAC通道的双模式的8位数据坚持寄存器(dac_dchxdhr8) (233)15.4.15 DAC通道数据输出寄存器高(dac_chxdorh) (233)15.4.16 DAC通道数据输出寄存器低(dac_chxdorl) (233)15.4.17 DAC寄存器映射及复位值 (234)16个比力器(COMP).237.16.1公司简介.237.16.2计算机的主要特点.239.16.3比力器1(COMP1).240.16.4比力器2(comp2).241.16.6公司的低功耗模式.243.16.8公司注册.244.文件编号15226启9 11 / 573内容rm003116.8.1比力器控制和状态寄存器1(comp_csr1) (244)16.8.2比力器控制和状态寄存器2(comp_csr2) (245)16.8.3比力器控制和状态寄存器3(comp_csr3) (246)16.8.4比力器控制和状态寄存器4(comp_csr4) (247)16.8.5比力器控制和状态寄存器5(comp_csr5) (247)16.8.6 COMP寄存器图及复位值 (248)17液晶显示控制器.249.17.1液晶显示控制器的介绍.249.17.1.1界说.24917.2液晶显示控制器的主要特点.250.17.3液晶显示功能描述.252.17.3.1一般描述.25217.3.2频率发生器 (253)17.3.3通用驱动法式.25617.3.4段驱动器.26417.3.5使一段 (265)17.3.6眨眼 (265)17.3.7复用COM [ 7:4 ]和[ 43:40赛格赛格],[ 39:36 ],或[ 31:28赛格].26517.3.8代LCD电压水平.26617.3.9 LCD缓冲区更新 (269)17.4液晶显示控制器的低功耗模式.269.17.6的LCD控制寄存器.270.17.6.1控制寄存器1(lcd_cr1) (270)19.6.2控制寄存器2(lcd_cr2) (272)17.6.3控制寄存器3(lcd_cr3) (273)17.6.4频率选择寄存器(lcd_frq) (274)17.6.5端口掩码寄存器(lcd_pm).27417.6.6控制寄存器4(lcd_cr4) (275)17.6.7 LCD显示存储器(lcd_ram) (276)17.6.8 LCD寄存器图及复位值 (278)18按时器的概述28012 / 573文档ID 15226转9rm0031内容19 16位先进控制按时器(TIM1).283.19.2 TIM1主要特点28419.3 TIM1时间单位.286.19.3.1阅读和写作的16位计数器.28719.3.2写序列的16位tim1_arr寄存器 (287)19.3.3分频器.28719.3.4了计数模式 (288)19.3.5向下计数模式 (290)19.3.6中心对齐方式(向上/向下计数) (292)19.3.7重复计数器.29419.4 TIM1时钟/触发控制器.296.19.4.1分频时钟(ck_psc) (296)19.4.2内部时钟源(fsysclk) (297)19.4.3外部时钟源模式1 (297)19.4.4外部时钟源模式2 (299)19.4.5触发同步.30019.4.6之间的同步按时器.30419.5 TIM1捕捉/比力通道.310.19.5.1写序列的16位tim1_ccri寄存器.31119.5.2输入阶段 (312)19.5.3输入捕捉模式.31319.5.4输出级.31519.5.5强制输出模式 (316)19.5.6输出比力模式 (316)19.5.7 PWM模式 (318)19.5.8利用中断功能.32519.5.9清理ociref信号对外部事件 (328)19.5.10编码器接口模式 (329)19.5.11按时器输入异或函数.33119.5.12与霍尔传感器.33119.6 TIM1中断.333.19.6.1 TIM1等事件的能力.33319.7 TIM1 DMA.333.19.7.1 DMA单模式.33319.7.2 DMA突发模式 (334)文件编号15226启9 13 / 573内容rm003119.8 TIM1寄存器33519.8.1控制寄存器1(tim1_cr1)33519.8.2控制寄存器2(tim1_cr2)33719.8.3从模式控制寄存器(tim1_smcr).338.19.8.4外部触发寄存器(tim1_etr).339.19.8.5 DMA请求使能寄存器(tim1_der)34119.8.6中断使能寄存器(tim1_ier).342.19.8.7状态寄存器1(tim1_sr1)34319.8.8状态寄存器2(tim1_sr2)34419.8.9事件生成寄存器(tim1_egr).345.19.8.10捕捉/比力寄存器模式1(tim1_ccmr1).346.19.8.11捕捉/比力寄存器模式2(tim1_ccmr2).349.19.8.12捕捉/比力寄存器模式3(tim1_ccmr3).350.19.8.13捕捉/比力寄存器模式4(tim1_ccmr4).351.19.8.14捕捉/比力使能寄存器1(tim1_ccer1)352 19.8.15捕捉/比力使能寄存器2(tim1_ccer2)35519.8.16计数器(tim1_cntrh)35519.8.17计数器的低(tim1_cntrl)35619.8.18分频器高(tim1_pscrh).356.19.8.19分频器的低(tim1_pscrl).356.19.8.20自动重载寄存器高(tim1_arrh)35719.8.21自动重载寄存器低(tim1_arrl)35719.8.22重复计数器寄存器(tim1_rcr).357.19.8.23捕捉/比力寄存器1高(tim1_ccr1h).358. 20个16位通用按时器(TIM2,TIM3,tim5)36820.2 TIMx主要特点.368.20.3 TIMx功能描述36920.3.1时间单位 (369)20.3.2时钟/触发控制器 (370)20.3.3捕捉/比力通道 (371)20.3.4按时器输入异或函数.37320.4 TIMx中断.373.20.5 TIMx寄存器.374.20.5.1控制寄存器1(timx_cr1).374.20.5.2控制寄存器2(timx_cr2).375.20.5.3从模式控制寄存器(timx_smcr).376.20.5.4外部触发寄存器(timx_etr).377.20.5.5 DMA请求使能寄存器(timx_der)37820.5.6中断使能寄存器(timx_ier).379.20.5.7状态寄存器1(timx_sr1)38020.5.8状态寄存器2(timx_sr2)38120.5.9事件生成寄存器(timx_egr).382.20.5.10捕捉/比力寄存器模式1(timx_ccmr1).383.20.5.11捕捉/比力寄存器模式2(timx_ccmr2).385.20.5.12捕捉/比力使能寄存器1(timx_ccer1)386 20.5.13计数器(timx_cntrh)38720.5.14计数器的低(timx_cntrl)38820.5.15分频寄存器(timx_pscr).388.。

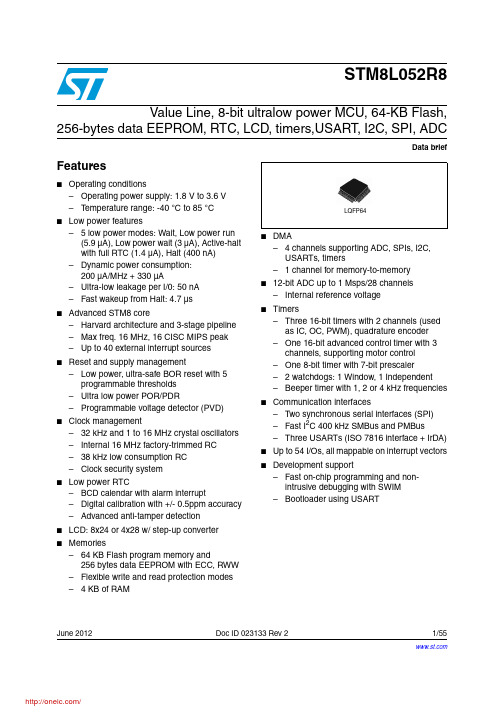

STM8L052R8T6;中文规格书,Datasheet资料

3

Functional overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.1 Low power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.1 Device overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.2 Ultra low power continuum . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

■ 12-bit ADC up to 1 Msps/28 channels – Internal reference voltage

■ Timers – Three 16-bit timers with 2 channels (used as IC, OC, PWM), quadrature encoder – One 16-bit advanced control timer with 3 channels, supporting motor control – One 8-bit timer with 7-bit prescaler – 2 watchdogs: 1 Window, 1 Independent – Beeper timer with 1, 2 or 4 kHz frequencies

STM8L系列超低功耗8位微控制器 说明书

STM8L1xx 典型应用和结构框图

医疗器械 血糖仪 胰岛素泵 糖尿病监护 血压计 胆固醇计 病人监控 心脏监护 仪表 电表/气表/水表/热表 称重 报警系统 中央处理单元 有线/无线传感器 门禁 通用移动设备 手机及配件 3D鼠标及遥控器 游戏机和玩具 GPS手表 体育设施

内部的16MHz RC振荡器 1~16MHz晶体 振荡器 内部的38kHz RC振荡器 32.768kHz晶体 振荡器 运行于16MHz的 STM8核心 嵌套的中断控制器 32个中断向量 多达40个外部中断 SWIM 调试模块 多达41个I/O端口 12位ADC 25个通道

STM8L系列

超低功耗8位微控制器

微控制 超节能

2009年9月

/mcu

STM8L超低功耗MCU系列

意法半导体公司开发出了基于8位STM8内核的超低功耗微控制器.借助一个优秀的面向未来的超低功耗平台,采 用了全新的超低漏电工艺和优化的体系结构,STM8L系列微控制器集合了高性能与超低功耗于一身.STM8L系列 现有三个子系列,可以满足对低功耗有特殊要求的多种应用.

STM8L一览

现在已有26个兼容的产品

Flash容量 (字节) STM8L152C8

64 K 32 K 16 K 8K

STM8L152R8 STM8L152M8 STM8L151R8 STM8L151M8

STM8L151C8 STM8L152K6 STM8L151G6 STM8L151K6 STM8L152K4 STM8L151G4 STM8L151K4 STM8L151F3 STM8L101F3 STM8L151G3 STM8L151K3 STM8L101G3 STM8L101K3 STM8L151G2 STM8L101G2 28引脚 QFN (4x4) 32引脚 LQFP (7x7)/ QFN (5x5) 48引脚 LQFP (7x7)/ QFN (7x7) STM8L152C6 STM8L151C6 STM8L152C4 STM8L151C4

STM8L中文参考手册-1

本参考手册的目标应用程序开发人员。

它提供了完整的信息如何使用stm8l05xx,stm8l15xx 和stm8l16xx微控制器的存储器和外围设备。

该stm8l05xx / stm8l15xx / stm8l16xx是一个家庭的不同存储密度的微控制器和外围设备。

这些产品是专为超低功耗应用。

可用的外设的完整列表,请参阅产品数据表。

订购信息,引脚说明,机械和电气设备的特点,请参阅产品数据表。

关于STM8 SWIM通信协议信息和调试模块,请参阅用户手册(um0470)。

在STM8的核心信息,请参阅STM8的CPU编程手册(pm0044)。

关于编程,擦除和保护的内部快闪记忆体,请参阅STM8L闪存编程手册(pm0054)。

1 中央处理单元(CPU)。

30。

1.1 引言301.2 CPU的寄存器。

30。

1.2.1 描述CPU寄存器。

..。

301.2.2 STM8 CPU寄存器图。

..。

341.3 全球配置寄存器(cfg_gcr)。

34。

1.3.1 激活水平。

..。

341.3.2 游泳禁用。

..。

351.3.3 描述全局配置寄存器(cfg_gcr)。

..。

35 1.3.4 全局配置寄存器图及复位值。

..。

352 启动ROM . . . 363程序存储器和数据存储器。

37。

3.1引言373.2术语。

37。

3.3个主要的快闪存储器的特点。

38。

3.4记忆的组织。

39。

3.4.1低密度设备的存储器组织。

393.4.2介质密度的装置记忆的组织。

..。

403.4.3介质+密度装置记忆的组织。

..。

413.4.4高密度存储器组织。

..。

423.4.5专有代码区(译)。

433.4.6用户区(UBC)。

433.4.7数据的EEPROM(数据)。

..。

463.4.8主程序区。

463.4.9选项字节。

..。

463.5内存保护。

47。

3.5.1读出保护。

473.5.2内存访问安全系统(质量)。

473.5.3使写访问选项字节。

493.6内存编程493.6.1同时读写(读写网)。

STM8L问答

[1问:] STM8L总线数据传输速度可达多高?[答:] CPU的时钟频率为16MHz[2问] 如何实现ARM内核的低功耗设计[答:] STM8L不是ARM内核的[3问:] STM8L的产品的工作主频能有多大?可以在待机时改变频率以节省电能吗? [答:] 最高16MHz,16MIPS,待机前可以降频[4问:] STM8加密除了在下载的时候禁止读写以外,还有什么好办法呢?[答:] 每个芯片有唯一的ID,可以在程序中做加密处理[5问:] STM8很多寄存器需要在某种状态下才允许修改的,能否详细说明一下?[答:] 这个问题能够提的具体一点吗?[6问:] 8位微控制器STM8L的外设接口是怎样设置的?[答:] 你指什么外设?[7问:] STM8L单片机和TI的msp430系列MCU有什么不同,与TI的功耗比相比有什么优势?谢谢[答:] STM8L是8位机,因此比16位机便宜。

STM8L可达16MIPS,与MSP430速度相当。

STM8L的许多工作模式,功耗比TI还低[8问:] STM8L是几级流水的?工作频率是多少?指令周期是多少?有多少单指令周期指令和双指令周期的指令?[答:] 3级16MHz Max指令集与STM8S相同STM8L的内核是CISC内核,指令周期从一个周期至最长10几个周期(除法指令)都有。

[9问:] 调试方式有几种?FLASH和RAM?可以选择吗?[答:] 可以选择Flash或RAM运行程序。

[10问:] 支持几种IDE?请简单介绍,谢谢[答:] ST推荐STVD还有Raisonance的IDE也可以。

[11问:] 目前stm8的编译器不是很好用,我想问一下是否有让iar支持stm8的计划啊?我想要是有的话,stm8的推广会更顺利一些……[答:] 再耐心等待吧,计划中的[12问:] 宣传资料上看到有关于stm芯片片内都有唯一的ID号,而且在加密时可以派上用场!请教这序列号在什么地方?我应该怎么读取?有相关例程么?[答:] 请下载最新版本的参考手册和数据手册,上面有说明[13问:] 如何设置代码在flash运行还是在sram中运行?[答:] 默认在Flash运行,但也可以选择在RAM运行。

STML中文介绍

STM8L152介绍8位超低功耗单片机,高达64 + 2字节数据的闪存EE PROM,EEPROM (Electrically Erasable Programmable Read-Only Memory),实时时钟,液晶显示器,定时器,USART,C,SPI,模数转换器,数模转换器,比较器特点:操作条件:工作电源:1.65v~ 3.6v温度范围:40 to 85, 105 or 125低功耗的特点:5个低功耗模式:等,低功率运行(5.9¦Ì一),低功耗等(3¦Ì一),active-halt全实时时钟(1.4¦Ì一),停止(400)动态功率消耗:200UA/兆赫+ 330UA,快速唤醒从停止模式(4.7us)超低漏I/ O:50nA先进的stm8核心:哈佛结构和三级流水线最大频率:16条16mhz,相关峰最多40个外部中断源复位和供应管理:低功率,超安全欠压复位5可编程阈值超低功率POR /PDR(通电复位/Protection(保护)、Detection(检测)、Response(响应))可编程电压检测器(Programmable voltage detector (PVD))时钟管理32kHz和1-16MHz晶体振荡器工厂校准的内部16MHz RC和38kHz的低功耗RC时钟安全系统低功耗RTCBCD日历,闹钟中断,数字校准+ / - 0.5ppm的准确度先进的防篡改检测DMA4个通道。

ADC,DAC的,SPIS,我2C,USART接口,定时器,1路。

存储器到存储器的LCD:8x40或4x44瓦特/升压转换器12位ADC1 Msps/28渠道温度。

传感器和内部参考。

电压记忆高达64 KB的快闪记忆体高达2KB的数据EEPROM,ECC和RWW灵活的读/写保护模式高达4 KB的RAM2x12位DAC(双模式)与输出缓冲器2个超低功耗比较器1个固定阈值和1个轨到轨唤醒功能定时器3个16位定时器,2个通道(IC,OC,PWM),正交编码器一个16位高级控制定时器,3个信道,支持电机控制1个7位预分频器的8位定时器1个窗口和1个独立的看门狗蜂鸣器定时器1,2或4kHz的频率通讯接口两个同步串行接口(SPI)快速I2C 400千赫SMBus和PMBus三个USART(ISO7816接口+红外线)最多67个I /o中断向量,所有可映射多达16个电容检测通道,免费固件快速片上编程和非侵入性调试与游泳,Bootloader的使用USART 独特的96位ID描述:1、stm8l超低功耗的8位家庭福利2、设备概述3、超低功率连续简介:本文描述的特点,因此,机械数据和订购信息:高密度stm8l15xxx装置:stm8l151x8和stm8l152x8微控制器与闪速存储器密度64字节。

STM8全系列选型手册-更新于2015年10月21日

STM8S208S6 STM8S903F3 STM8S903K3 STM8SPLNB1 STM8TL52F4 STM8TL52G4 STM8TL53C4 STM8TL53F4 STM8TL53G4

LQFP 44 10x10x1.4 SO-20; TSSOP 20; UFQFPN 20 3x3x0.6 LQFP 32 7x7x1.4; PDIP 32 .4S; UFQFPN 32 5x5x0.55 SO-20; TSSOP 20 TSSOP 20 UFQFPN 28 4x4x0.55 UFQFPN 48 7x7x0.55 TSSOP 20 UFQFPN 28 4x4x0.55

LQFP 48 7x7x1.4 LQFP 48 7x7x1.4 LQFP 64 10x10x1.4 LQFP 80 14x14x1.4 LQFP 48 7x7x1.4 LQFP 64 10x10x1.4 LQFP 80 14x14x1.4 LQFP 32 7x7x1.4 LQFP 48 7x7x1.4 LQFP 32 7x7x1.4 LQFP 48 7x7x1.4 LQFP 48 7x7x1.4 LQFP 64 10x10x1.4 LQFP 80 14x14x1.4 LQFP 48 7x7x1.4 LQFP 64 10x10x1.4 LQFP 80 14x14x1.4 TSSOP 20 LQFP 48 7x7x1.4 LQFP 64 10x10x1.4 UFQFPN 20 3x3x0.6 TSSOP 20; UFQFPN 20 3x3x0.6 TSSOP 20; UFQFPN 20 3x3x0.6 UFQFPN 28 4x4x0.55 UFQFPN 28 4x4x0.55 LQFP 32 7x7x1.4; UFQFPN 32 5x5x0.55 LQFP 48 7x7x1.4 LQFP 48 7x7x1.4 LQFP 48 7x7x1.4; UFQFPN 48 7x7x0.55 LQFP 48 7x7x1.4; UFQFPN 48 7x7x0.55 LQFP 48 7x7x1.4; UFQFPN 48 7x7x0.55 TSSOP 20; UFQFPN 20 3x3x0.6 TSSOP 20; UFQFPN 20 3x3x0.6 UFQFPN 28 4x4x0.55 UFQFPN 28 4x4x0.55 UFQFPN 28 4x4x0.55; WLCSP FAN IN UFQFPN 28 4x4x0.55; WLCSP FAN IN UFQFPN 32 5x5x0.55 UFQFPN 32 5x5x0.55 LQFP 32 7x7x1.4; UFQFPN 32 5x5x0.55 LQFP 32 7x7x1.4; UFQFPN 32 5x5x0.55 LQFP 80 14x14x1.4 LQFP 64 10x10x1.4 LQFP 64 10x10x1.4 LQFP 48 7x7x1.4; UFQFPN 48 7x7x0.55 LQFP 48 7x7x1.4; UFQFPN 48 7x7x0.55

STM8L中文参考手册-1,2,3,4(RM0031)

本参考手册的目标应用程序开发人员。

它提供了完整的信息如何使用stm8l05xx,stm8l15xx和stm8l16xx微控制器的存储器和外围设备。

该stm8l05xx / stm8l15xx / stm8l16xx是一个家庭的不同存储密度的微控制器和外围设备。

这些产品是专为超低功耗应用。

可用的外设的完整列表,请参阅产品数据表。

订购信息,引脚说明,机械和电气设备的特点,请参阅产品数据表。

关于STM8 SWIM通信协议信息和调试模块,请参阅用户手册(um0470)。

在STM8的核心信息,请参阅STM8的CPU编程手册(pm0044)。

关于编程,擦除和保护的内部快闪记忆体,请参阅STM8L闪存编程手册(pm0054)。

1 中央处理单元(CPU)。

30。

1.1 引言301.2 CPU的寄存器。

30。

1.2.1 描述CPU寄存器。

..。

301.2.2 STM8 CPU寄存器图。

..。

341.3 全球配置寄存器(cfg_gcr)。

34。

1.3.1 激活水平。

..。

341.3.2 游泳禁用。

..。

351.3.3 描述全局配置寄存器(cfg_gcr)。

..。

351.3.4 全局配置寄存器图及复位值。

..。

352 启动ROM . . . 363程序存储器和数据存储器。

37。

3.1引言373.2术语。

37。

3.3个主要的快闪存储器的特点。

38。

3.4记忆的组织。

39。

3.4.1低密度设备的存储器组织。

393.4.2介质密度的装置记忆的组织。

..。

403.4.3介质+密度装置记忆的组织。

..。

413.4.4高密度存储器组织。

..。

423.4.5专有代码区(译)。

433.4.6用户区(UBC)。

433.4.7数据的EEPROM(数据)。

..。

463.4.8主程序区。

463.4.9选项字节。

..。

463.5内存保护。

47。

3.5.1读出保护。

473.5.2内存访问安全系统(质量)。

473.5.3使写访问选项字节。

493.6内存编程493.6.1同时读写(读写网)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.11.1 Window watchdog timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.11.2 Independent watchdog timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.12 Beeper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.13 Communication interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.1 Low power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.2 Central processing unit STM8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

– Fast on-chip programming and nonintrusive debugging with SWIM

– Bootloader using USART

August 2012

This is information on a product in full production.

3.13.1 SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 3.13.2 I2C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Doc ID 023465 Rev 1

1/93

1

Contents

Contents

STM8L051F3

1

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.10 Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.10.1 16-bit general purpose timers (TIM2, TIM3) . . . . . . . . . . . . . . . . . . . . . 19

2.2 Ultra low power continuum . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3

Functional overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

■ Memories – 8 Kbytes of Flash program memory and 256 bytes of data EEPROM with ECC – Flexible write and read protection modes – 1 Kbyte of RAM

TSSOP20

3.2.1 Advanced STM8 Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.2.2 Interrupt controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

■ DMA – 4 channels supporting ADC, SPI, I2C, USART, timers – 1 channel for memory-to-memory

■ 12-bit ADC up tce voltage

■ Advanced STM8 core – Harvard architecture and 3-stage pipeline – Max freq: 16 MHz, 16 CISC MIPS peak – Up to 40 external interrupt sources

■ Reset and supply management – Low power, ultra-safe BOR reset with 5 selectable thresholds – Ultra low power POR/PDR – Programmable voltage detector (PVD)

STM8L051F3

Value Line, 8-bit ultralow power MCU, 8-KB Flash, 256-byte data EEPROM, RTC, timers, USART, I2C, SPI, ADC

Datasheet production data

Features

■ Operating conditions – Operating power supply: 1.8 V to 3.6 V Temperature range: 40 °C to 85 °C

3.3 Reset and supply management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.3.1 Power supply scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

■ Timers – Two 16-bit timers with 2 channels (used as IC, OC, PWM), quadrature encoder – One 8-bit timer with 7-bit prescaler – 2 watchdogs: 1 Window, 1 Independent – Beeper timer with 1, 2 or 4 kHz frequencies

3.4 Clock management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.5 Low power real-time clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.1 Device overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

■ Communication interfaces – Synchronous serial interface (SPI) – Fast I2C 400 kHz SMBus and PMBus – USART

■ Up to 18 I/Os, all mappable on interrupt vectors ■ Development support

■ Low power features – 5 low power modes: Wait, Low power run (5.1 µA), Low power wait (3 µA), Active-halt with RTC (1.3 µA), Halt (350 nA) – Ultra-low leakage per I/0: 50 nA – Fast wakeup from Halt: 5 µs

3.3.2 Power supply supervisor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.3.3 Voltage regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15