A1000 Presentation_'09.03.13

dell Precision Data Science Workstation 指导安装手册说明书

• 7550 mobile workstation • 7750 mobile workstation • 5820 Tower workstation • 7920 Tower workstation • 7920 Rack workstation

NVIDIA Quadro™ RT源自 graphic cardsWarranty and Support

Dell 3-year warranty, extendable to 5 years Dell enterprise support: Pro Support, and Pro Support Plus available from Dell

Canonical™ OS

• Canonical™ Ubuntu® Linux

Installation and Tuning

Dell Data Science Workstation Guided Installation Manual for a “no-surprises” guided user-install of the NVIDIA Data Science Software, powered by RAPIDS, including

• Introduction to the Dell Precision Data Science Workstation (DSW) • Some recommended DSW configurations • Instructions for the user to install the NVIDIA Data Science Software • Optimization suggestions to get the most from your DSW • Appendix containing best practices guidance for installing or reinstalling Ubuntu Linux.

Ovation I O Reference Manual

This publication adds the Eight Channel RTD module to the Ovation I/O Reference Manual. It should be placed between Sections 19 and 20.Date: 04/03IPU No.243Ovation ® Interim Publication UpdatePUBLICATION TITLEOvation I/O Reference ManualPublication No. R3-1150Revision 3, March 2003Section 19A. Eight Channel RTDModule19A-1. DescriptionThe Eight (8) channel RTD module is used to convert inputs from Resistance Temperature Detectors (RTDs) to digital data. The digitized data is transmitted to the Controller.19A-2. Module Groups19A-2.1. Electronics ModulesThere is one Electronics module group for the 8 channel RTD Module:n5X00119G01 converts inputs for all ranges and is compatible only with Personality module 5X00121G01 (not applicable for CE Mark certified systems).19A-2.2. Personality ModulesThere is one Personality module groups for the 8 channel RTD Module:n5X00121G01 converts inputs for all ranges and is compatible only with Electronics module 5x00119G01 (not applicable for CE Mark certified systems).19A-2.3. Module Block Diagram and Field Connection WiringDiagramThe Ovation 8 Channel RTD module consists of two modules an electronics module contains a logic printed circuit board (LIA) and a printed circuit board (FTD). The electronics module is used in conjunction with a personalty module, which contains a single printed circuit board (PTD). The block diagram for the 8 channel RTD moduleis shown in Figure 19A-1.Table 19A-1. 8 Channel RTD Module Subsystem ChannelsElectronic Module Personality Module85X00119G015X00121G01Figure 19A-1. 8 Channel RTD Module Block Diagram and Field Connection Wiring Diagram19A-3. SpecificationsElectronics Module (5X00119)Personality Module (5X00121)Table 19A-2. 8 Channel RTD Module SpecificationsDescription ValueNumber of channels8Sampling rate50 HZ mode: 16.67/sec. normally. In 3 wire mode, leadresistance measurement occurs once every 6.45 sec.during which the rate drops to 3/sec.60 HZ mode: 20/sec. normally. In 3 wire mode, leadresistance measurement occurs once every 6.45 sec.during which the rate drops to 2/sec.Self Calibration Mode: Occurs on demand only. The ratedrops to 1/sec. once during each self calibration cycle.RTD ranges Refer to Table 19A-3.Resolution12 bitsGuaranteed accuracy (@25°C)0.10% ±[0.045 (Rcold/Rspan)]% ± [((Rcold + Rspan)/4096 OHM)]% ± [0.5 OHM/Rspan]% ±10 m V ± 1/2LSBwhere:Rcold and Rspan are in Ohms.Temperature coefficient 10ppm/°CDielectric isolation:Channel to channel Channel to logic 200V AC/DC 1000 V AC/DCInput impedance100 M OHM50 K OHM in power downModule power 3.6 W typical; 4.2 W maximumOperating temperature range0 to 60°C (32°F to 140°F)Storage temperature range-40°C to 85°C (-40°F to 185°F)Humidity (non-condensing)0 to 95%Self Calibration On Demand by Ovation ControllerCommon Mode Rejection120 dB @ DC and nominal power line frequency+/- 1/2%Normal Mode Rejection100 dB @ DC and nominal power line frequency+/- 1/2%Table 19A-3. 8 Channel RTD RangesScale #(HEX)Wires Type Tempo FTempo CRcold(ohm)Rhot(ohm)Excitationcurrent(ma)Accuracy± ±countsAccuracy± ±% ofSPAN1310OhmPL0 to1200–18 t o6496106.3 1.090.222310OhmCU 0 to302–18 t o1508.516.5 1.0 130.32D350OhmCU 32 to2840 to1405080 1.0110.2711350OhmCU 32 to2300 to1105378 1.0120.30193100Ohm PL –4 to334–16 t o16892163.671.0110.27223100Ohm PL 32 to5200 to269100200 1.0100.25233100Ohm PL 32 to10400 to561100301 1.0100.25253120Ohm NI –12 t o464–11 t o240109360 1.0100.25263120Ohm NI 32 to1500 to70120170 1.0130.32283120Ohm NI 32 to2780 to122120225 1.0110.27804100Ohm PL 32 to5440 to290100 208 1.0100.25814100Ohm PL 356 t o446180 t o230168 186 1.0300.74824200Ohm PL 32 to6980 to370200 473 1.0120.30834200Ohm PL 514 t o648268 t o342402452 1.0290.71844100Ohm PL 32 to1240 to51100120 1.0190.47854100Ohm PL 32 to2170 to103100 140 1.0130.3286 4100Ohm PL 32 to4120 to211100 180 1.0110.27874100Ohm PL 32 to7140 to379100 240 1.0100.25884120Ohm PL 511 t o662266 t o350200230 1.0240.5919A-4. 8 Channel RTD Terminal Block Wiring Information19A-4.1. Systems Using Personality Module 5X00121G01 Each Personality module has a simplified wiring diagram label on its side, which appears above the terminal block. This diagram indicates how the wiring from the field is to beconnected to the terminal block in the base unit. The following table lists and defines the abbreviations used in this diagram.Table 19A-4. Abbreviations Used in the DiagramAbbreviation Definition+IN, -IN Positive and negative sense input connectionEarth ground terminal. Used for landing shields when the shield is to begrounded at the module.PS+, PS-Auxiliary power supply terminals.RTN Return for current source connection.SH Shield connector. used for landing shields when the shield is to begrounded at the RTD.SRC Current source connection.Note:PS+ and PS- are not used by this module.19A-5. 8 Channel RTD Module Address Locations19A-5.1. Configuration and Status RegisterWord address 13 (D in Hex) is used for both module configuration and module status. The Module Status Register has both status and diagnostic information. The bit information contained within these words is shown in Table 19A-5.Definitions for the Configuration/Module Status Register bits:Bit 0:This bit configures the module (write) or indicates the configuration state of the module (read). A “1” indicates that the module is configured. Note that until the module is configured, reading from addresses #0 through #11 (B in Hex) will produce an attention status.Bit 1:This bit (write “1”) forces the module into the error state, resulting in the error LED being lit. The read of bit “1” indicates that there is an internal module error,or the controller has forced the module into the error state. The state of this bit is always reflected by the module’s Internal Error LED. Whenever this bit is set,an attention status is returned to the controller when address #0 through #11(B in Hex) are read.Table 19A-5. 8 Channel RTD Configuration/Status Register (Address 13 0xD in Hex)Bit Data Description -Configuration Register (Write)Data Description -Status Register (Read)0Configure Module Module Configured(1 = configured; 0 = unconfigured)1Force errorInternal or forced error(1 = forced error; 0 = no forced error)250/60 Hz select (0 = 60Hz, 1 = 50Hz)50/60 Hz System (1 = 50Hz) d(read back)3SELF_CAL (Initiates Self Calibration)Warming bit (set during power up or configuration)40050060Module Not Calibrated 708CH.1 _ 3/4 Wire.CH.1 _ 3/4 Wire - Configuration (read back)9CH.2 _ 3/4 Wire.CH.2 _ 3/4 Wire - Configuration (read back)10CH.3 _ 3/4 Wire.CH.3 _ 3/4 Wire - Configuration (read back)11CH.4 _ 3/4 Wire.CH.4 _ 3/4 Wire - Configuration (read back)12CH.5 _ 3/4 Wire.CH.5 _ 3/4 Wire - Configuration (read back)13CH.6 _ 3/4 Wire.CH.6 _ 3/4 Wire - Configuration (read back)14CH.7 _ 3/4 Wire.CH.7 _ 3/4 Wire - Configuration (read back)15CH.8 _ 3/4 Wire.CH.8 _ 3/4 Wire - Configuration (read back)Bit 2:The status of this bit (read) indicates the conversion rate of the module, write to this bit configures the conversion rate of A/D converters as shown below.see Table 19A-6.Bit3:Write: This bit is used to initiate self-calibration. Read: This bit indicates that the module is in the “Warming” state. this state exists after power up and ter-minates after 8.16 seconds. the module will be in the error condition during the warm up period.Bit4 & 5:These bits are not used and read as “0” under normal operation.Bit 6:This bit (read) is the result of a checksum test of the EEPROM. A failure of this test can indicate a bad EEPROM, but it typically indicates that the module has not been calibrated. A “0” indicates that there is no error condition. If an error is present, the internal error LED is lit and attention status will be returned for all address offsets 0-11 (0x0 - 0xB). The “1” state of this bit indicates an unre-coverable error condition in the field.Bit 7:This bits is not used and read as “0” under normal operation.Bit 8 - 15:These bits are used to configure channels 1 - 8 respectively for 3 or 4 wire op-eration. A “0” indicates 3 wire and a “1” indicates 4 wire operation, see Table 19A-7 and Table 19A-8).Word address 12 (0xC) is used to configure the appropriate scales for Channels 1 - 4 (refer to Table 19A-7 and Table 19A-8).Table 19A-6. Conversion Rate Conversion Rate (1/sec.)Bit 260 (for 60Hz systems)050 (for 50Hz systems)1Table 19A-7. Data Format for the Channel Scale Configuration Register(0xC)Bit Data Description Configuration (Write)Data Description Status (Read)0 Configure Channel #1scale - Bit 0Channel #1 scale configuration (read back) - Bit 01Configure Channel #1scale - Bit 1Channel #1 scale configuration (read back) - Bit 12Configure Channel #1scale - Bit 2Channel #1 scale configuration (read back) - Bit 23Configure Channel #1scale - Bit 3Channel #1 scale configuration (read back) - Bit 34Configure Channel #2 scale - Bit 0Channel #2 scale configuration (read back) - Bit 05Configure Channel #2 scale - Bit 1Channel #2 scale configuration (read back) - Bit 16Configure Channel #2 scale - Bit 2Channel #2 scale configuration (read back) - Bit 27Configure Channel #2 scale - Bit 3Channel #2 scale configuration (read back) - Bit 38Configure Channel #3 scale - Bit 0Channel #3 scale configuration (read back) - Bit 09Configure Channel #3 scale - Bit 1Channel #3 scale configuration (read back) - Bit 1Caution:Configuring any or all channel scales while the system is running will cause all channels to return attention status for up to two seconds following the reconfiguration.Caution:Configuring any or all channel scales while the system is running will cause all channels to return attention status for up to two seconds following the reconfiguration.10Configure Channel #3 scale - Bit 2Channel #3 scale configuration (read back) - Bit 211Configure Channel #3 scale - Bit 3Channel #3 scale configuration (read back) - Bit 312Configure Channel #4 scale - Bit 0Channel #4 scale configuration (read back) - Bit 013Configure Channel #4 scale - Bit 1Channel #4 scale configuration (read back) - Bit 114Configure Channel #4 scale - Bit 2Channel #4 scale configuration (read back) - Bit 215Configure Channel #4 scale - Bit 3Channel #4 scale configuration (read back) - Bit 3Table 19A-8. Data Format for the Channel Scale Configuration Register(0xE)Bit Data Description Configuration (Write)Data Description Status (Read)0 Configure Channel #5 scale - Bit 0Channel #5 scale configuration (read back) - Bit 01Configure Channel #5 scale - Bit 1Channel #5 scale configuration (read back) - Bit 12Configure Channel #5 scale - Bit 2Channel #5 scale configuration (read back) - Bit 23Configure Channel #5 scale - Bit 3Channel #5 scale configuration (read back) - Bit 34Configure Channel #6 scale - Bit 0Channel #6 scale configuration (read back) - Bit 05Configure Channel #6 scale - Bit 1Channel #6 scale configuration (read back) - Bit 16Configure Channel #6 scale - Bit 2Channel #6 scale configuration (read back) - Bit 27Configure Channel #6 scale - Bit 3Channel #6 scale configuration (read back) - Bit 38Configure Channel #7 scale - Bit 0Channel #7 scale configuration (read back) - Bit 09Configure Channel #7 scale - Bit 1Channel #7 scale configuration (read back) - Bit 110Configure Channel #7 scale - Bit 2Channel #7 scale configuration (read back) - Bit 211Configure Channel #7 scale - Bit 3Channel #7 scale configuration (read back) - Bit 312Configure Channel #8 scale - Bit 0Channel #8 scale configuration (read back) - Bit 013Configure Channel #8 scale - Bit 1Channel #8 scale configuration (read back) - Bit 114Configure Channel #8 scale - Bit 2Channel #8 scale configuration (read back) - Bit 215Configure Channel #8 scale - Bit 3Channel #8 scale configuration (read back) - Bit 3Table 19A-7. Data Format for the Channel Scale Configuration Register(0xC)19A-6. Diagnostic LEDsTable 19A-9. 8 Channel RTD Diagnostic LEDsLED DescriptionP (Green)Power OK LED. Lit when the +5V power is OK.C (Green)Communications OK LED. Lit when the Controller is communicatingwith the module.I (Red)Internal Fault LED. Lit whenever there is any type of error with themodule except to a loss of power. Possible causes are:n - Module initialization is in progress.n - I/O Bus time-out has occurred.n - Register, static RAM, or FLASH checksum error.n - Module resetn - Module is uncalibrated.n - Forced error has been received from the Controllern - Communication between the Field and Logic boards failedCH1 - CH 8 (Red)Channel error. Lit whenever there is an error associated with a channel or channels. Possible causes are:n - Positive overrangen - Negative overrangen Communication with the channel has failed。

A1000通讯协议

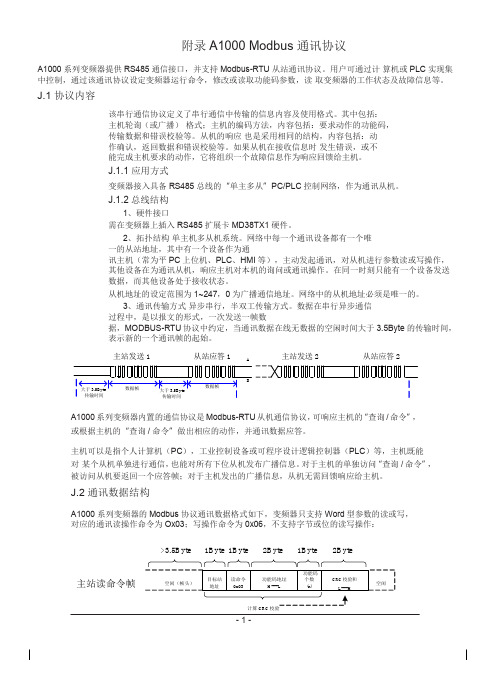

附录A1000 Modbus 通讯协议A1000系列变频器提供RS485 通信接口,并支持Modbus-RTU 从站通讯协议。

用户可通过计算机或PLC 实现集中控制,通过该通讯协议设定变频器运行命令,修改或读取功能码参数,读取变频器的工作状态及故障信息等。

J.1 协议内容该串行通信协议定义了串行通信中传输的信息内容及使用格式。

其中包括:主机轮询(或广播)格式;主机的编码方法,内容包括:要求动作的功能码,传输数据和错误校验等。

从机的响应也是采用相同的结构,内容包括:动作确认,返回数据和错误校验等。

如果从机在接收信息时发生错误,或不能完成主机要求的动作,它将组织一个故障信息作为响应回馈给主机。

J.1.1 应用方式变频器接入具备RS485 总线的“单主多从”PC/PLC 控制网络,作为通讯从机。

J.1.2 总线结构1、硬件接口需在变频器上插入RS485 扩展卡MD38TX1 硬件。

2、拓扑结构单主机多从机系统。

网络中每一个通讯设备都有一个唯一的从站地址,其中有一个设备作为通讯主机(常为平PC 上位机、PLC、HMI 等),主动发起通讯,对从机进行参数读或写操作,其他设备在为通讯从机,响应主机对本机的询问或通讯操作。

在同一时刻只能有一个设备发送数据,而其他设备处于接收状态。

从机地址的设定范围为1~247,0 为广播通信地址。

网络中的从机地址必须是唯一的。

3、通讯传输方式异步串行,半双工传输方式。

数据在串行异步通信过程中,是以报文的形式,一次发送一帧数据,MODBUS-RTU 协议中约定,当通讯数据在线无数据的空闲时间大于3.5Byte 的传输时间,表示新的一个通讯帧的起始。

主站发送1 从站应答1主站发送2 从站应答2AA1000 系列变频器内置的通信协议是Modbus-RTU 从机通信协议,可响应主机的“查询/ 命令”,或根据主机的“查询/ 命令”做出相应的动作,并通讯数据应答。

主机可以是指个人计算机(PC),工业控制设备或可程序设计逻辑控制器(PLC)等,主机既能对某个从机单独进行通信,也能对所有下位从机发布广播信息。

DDN A3I 解决方案与NVIDIA DGX A100系统的整合与优化数据平台说明书

Performance Brief Lorem ipsum dolor sit amet consecteturDDN A3I® SOLUTIONSWITH NVIDIA DGX™ A100 SYSTEMSFully-integrated and optimized data platformsfor accelerated at-scale AI, Analytics and HPCDDN A3I Solutions with NVIDIA DGX A100 Systems (2)The DDN A3I Shared Parallel Architecture (2)Get Proven Performance with the DDN AI400X Appliance (3)Deploy Rapidly with Fully-Validated Reference Architectures (4)Scale Predictably and Seamlessly with Multiple Appliances (5)Accelerate Your AI Applications with DDN Shared Parallel Architecture (9)Maximize Throughput and Efficiency with GPUDirect Storage (11)Contact DDN to Unleash the Power of Your AI (13)EXECUTIVE SUMMARYDDN A3I Solutions are proven at-scale to deliver highest data performance for AI and HPC applications running on GPUs in a DGX A100 system. DDN AI400X appliances provides up to 60X more throughput and 50X more IOPS than NFS-based data platforms, and scale predictably to ensure optimal application performance as AI requirements grow. DDN fully integrates GPUDirect Storage and demonstrates full GPU saturation, up to 162 GiB/s per DGX A100 system. The AI400X appliance enables GPU systems at all scale globally, including NVIDIA Selene, the largest SuperPOD with DGX A100 currently in operation, ranked #7 on the latest IO500 list.DDN A3I Solutions with NVIDIA DGX A100 SystemsDDN A3I solutions are architected to achieve the most from at-scale AI, Analytics and HPC applications running on DGX systems. They are designed to provide extreme amounts of performance, capacity and capability through a tight integration between DDN and NVIDIA systems. Every layer of hardware and software engaged in delivering and storing data is optimized for fast, responsive, and reliable access.DDN A3I solutions are designed, developed, and optimized in close collaboration with NVIDIA. The deep integration of DDN AI appliances with DGX systems ensures a predictable and reliable experience. DDN A3I solutions are highly configurable for flexible deployment in a wide range of environments and scale seamlessly in capacity and capability to match evolving workload needs. DDN A3I solutions are deployed globally and at all scale, from a single DGX system all the way to the largest NVIDIA DGX SuperPOD TM with DGX A100 in operation today.DDN brings the same advanced technologies used to power the world’s largest supercomputers in a fully-integrated package for DGX systems that’s easy to deploy and manage. DDN A3I solutions are proven to provide maximum benefits for at-scale AI, Analytics and HPC workloads on DGX systems.The DDN A3I Shared Parallel ArchitectureThe DDN A3I shared parallel architecture and client protocol provides superior performance, scalability, security, and reliability for DGX systems. Multiple parallel data paths extend from the drives all the way to containerized applications running on the GPUs in the DGX system. With DDN’s true end-to-end parallelism, data is delivered with high-throughput, low-latency, and massive concurrency in transactions. This ensures applications achieve the most from DGXsystems with all GPU cycles put to productive use. Optimized parallel data-delivery directly translates to increased application performance and faster completion times. The DDN A3I shared parallel architecture also contains redundancy and automatic failover capability to ensure high reliability, resiliency, and data availability in case a network connection or server becomes unavailable.The DDN A3I client's NUMA-aware capabilities enable strong optimization for DGX systems. It automatically pins threads to ensure I/O activity across the DGX system is optimally localized, reducing latencies and increasing the utilization efficiency of the whole environment. Further enhancements reduce overhead when reclaiming memory pages from page cache to accelerate buffered operations to storage. The A3I DDN shared parallel architecture provides proven enablement and acceleration for AI infrastructure and workloads on DGX systems.Get Proven Performance with the DDN AI400X ApplianceThe DDN AI400X is a turnkey appliance, fully-integrated and optimized for the most intensive AI and HPC workloads on DGX systems. The appliance is proven and well-recognized to deliver highest performance, optimal efficiency, and flexible growth for DGX deployments at all scale.A single appliance can deliver up to 48GB/s of throughput and well over 3 million IOPS to clients via a HDR100 or 100 GbE network, and can scale predictably in performance, capacity and capability. The AI400X appliance is available in all-nvme and hybrid NVME/HDD configurations for maximum efficiency and best economics.The unified namespace simplifies end-to-end deep learning workflows with integrated secure data ingest, management, and retention capabilities.The AI400X achieves the most GPU performance, streamlines workflows, eliminates data management overhead. It enables customers to scale seamlessly, limitlessly and with full-confidence as workflow requirements increase. The appliance software is feature rich and includes extensive data management capabilities, robust data protection and security frameworks, intelligent analytics and analysis engines, and integrates a modern hybrid S3 object interface. The software also includes several advanced features ideal for deployments with multiple DGX systems, notably full support for container applications and secure multi-tenancy. It iinterfaces easily with file, object and cloud-based data repositories for ingest and archive.The AI400X appliance is designed for rapid deployment, easy management and support. It’s fully-validated and deployed with hundreds of DGX client nodes. The AI400X is provides best performance for all workloads and data types. It is the most-proven data platform with maximum operational flexibility at all-scale for DGX systems.Deploy Rapidly with Fully-Validated Reference Architectures ArrayDDN proposes reference architectures for single and multi-node configurations including DGX POD and SuperPOD. They are documented in the DDN A3I Solutions Guide with NVIDIA DGX A100 Systems available from the DDN website.The DDN AI400X is a turnkey appliance for at-scale DGX deployments. DDN recommends the AI400X as the optimal data platform for DGX system deployments. The AI400X delivers maximum GPU performance for every workload and data type in a dense, power efficient 2RU chassis. The AI400X simplifies the design, deployment and management of DGX systems and provides predictable performance, capacity and scaling. The AI400X arrives fully configured, ready to deploy and installs in minutes. The appliance is designed for seamless integration with DGX systems, and enables customers to move rapidly from test to production. DDN provides complete expert design, deployment, and support services globally and ensures best customer experience. The DDN field engineering organization has already deployed hundreds of solutions for customers based on the A3I reference architectures.As general guidance, DDN recommends an AI400X for every four DGX systems in a DGX POD (Figure 1). These configurations can be adjusted and scaled easily to match specific workload requirements. For the storage network, DDN recommends HDR200 InfiniBand technology in a non-blocking topology, with redundancy to ensure data availability. DDN recommends use ofat least two HDR200 connections per DGX system to the storage network.1 Node2 Nodes 4 Nodes 8 NodesFigure 1.Rack illustrations for DDN A3I reference configurations49 GB/s READ99 GB/s READ35 GB/s WRITE72 GB/s WRITE50% MORE THROUGHPUT PER DGX SYSTEM WITH GDSAdditional testing demonstrates that the DDN A3I shared parallel architecture enables a single DGX system to achieve scaled throughput and IOPS peak performance (Figure 3). The left graph illustrates peak read throughput performance of 99 GB/s to a single mount, single DGX system from dual AI400X appliances. This is 33X more read throughput than NFS, and nearly 10X more than NFS with ROCE. The left graph demonstrates peak IOPS read performance up to 4.7 million IOPS to a single DGX system, single mount with the same configuration. This is 46X more IOPS than NFS. This testing also clearly demonstrates that the DDN AI400X delivers uncompromising performance for a wide variety of data intensive workload, using a wide variety of data types.Figure 3. Peak performance for single mount on singe DGX systemDDN A 3I solutions are currently deployed at extreme scale and power the largest NVIDIA SuperPOD with DGX A100 in operation globally. Over 280 DGX systems access the shared DDN data platform simultaneously and engage a wide variety of HPC, AI and Analytics workloads using mixed data types. The deployment for this project started with ten AI400X appliances and three additional expansions of ten AI400X, for a total of forty AI400X appliances. At every phase, the ten DDN appliances delivered additional capacity and nearly 500 GB/s of throughput. Fully deployed, the forty AI400X appliances deliver 2 TB/s of throughput to all DGX systems in the SuperPOD, from a single unified namespace. This greatly simplifies data management, and eliminates the need to copy, move or tier data between different storage locations.102030405060708090100NFS (tcp)NFS (RoCE)DDN AI400X2 x AI400X WITH DGX SYSTEM Single Client, Single Mount Peak Throughput Performance0K500K 1.0M 1.5M 2.0M 2.5M 3.0M 3.5M4.0M 4.5M5.0M NFS (tcp)NFS (RoCE)DDN AI400X2 x AI400X WITH DGX SYSTEM Single Client, Single Mount Peak IOPS Performance33XFASTER46XMORE IOPS33 GB/s 99 GB/s99 %23 %Accelerate your AI Applications with DDN Shared Parallel ArchitectureThe DDN latency and massive concurrency. This ensures that all GPU cycles are put to productive use and achieve maximum AI and HPC application performance on DGX systems with any data type. For distributed workloads, performance scales linearly and maintains full GPU saturation as multiple GPUs are engaged. This contrasts heavily with legacy network protocols like NFS which are inadequate to meet the demands of modern workloads running on GPUs.The AI400X appliance delivers faster, scalable AI application performance with DGX system. Testing with PyTorch, a very commonly used deep learning framework demonstrates 3X higher application throughput and maintains linear performance scaling with multiple GPUs (Figure 5). This contrasts heavily when using NFS, which fails to fully-engage a single GPU and cripples the performance demonstrates that efficient data delivery to GPUs with the DDN shared parallel architecture directly translates to increased AI application performance, and that this is maintained at-scale with additional GPUs and client nodes engaged.100001500020000250003000035000400004500050000A p p l i c a t i o n T h r o u g h p u t (i m a g e s p e r s e c o n d )MULTI-GPU PERFORMANCE LIMITED BY NFS BOTTLENECKDDN AI400X LINEAR SCALINGWITH MULTIPLE GPUs1 2 4 8NFS MAX1 2 4 8The benefits of the DDN shared parallel architecture for AI applications extend throughout the entire lifecycle of AI data including ingest, labeling, processing and archiving for long-term retention and reuse. Deep learning applications like PyTorch can take advantage of optimized data formats to achieve faster and more efficient runtime results.TFRecords is a highly optimized file format compatible with PyTorch that enables the conversion of discrete data and metadata asset collections into series of streamlined binary files. This process significantly reduces the amount of dataset preparation time required before running the deep learning application. To be utilized, discrete assets must be split into training, testing, and validation sets that are stored in a specific folder structure and shuffled to avoid biased data distribution. This requires tedious data handling and attention to maintain proper shuffling. TFRecords provide a consolidated dataset that is easy to maintain and distribute and that eliminates the need for file manipulation.The DDN shared parallel architecture furthers these benefits by allowing concurrent delivery of discrete data and metadata assets from source datasets to the conversion application, and rapid write of the binary file to persistent storage. In this demonstration, a dataset with 1.9 million data and metadata files spread across thousands of folders is being condensed to 1150 TFRecords binary files in a single directory, over 3X faster with DDN compared to NFS (Figure 6).Figure 6. Comparing TFRecords conversion operation duration2367TFRecords also streamlines PyTorch at runtime. Discrete assets must be opened individually, generating tremendous overhead for the data delivery and storage systems. A consolidated TFRecord binary file is more efficient as it only requires a single file open operation and allows the entire dataset to be held into a block of memory. This also enables applications to shuffle data at random places throughout the workflow and dynamically split training, testing and validation sets. This provides tremendous agility, efficiency and acceleration to Pytorch applications.Testing demonstrates that Pytorch application performs at significantly higher throughput with both optimized and discreet data sets using DDN AI400X compared to NFS (Figure 7). The graph on the left illustrates application performance using discreet data set comprised of individual JPEG files. The DDN shared parallel architecture enables 4X faster image ingest than NFS. On the right, the same application ingests the same data that has been converted to TFRecords. The application performs at much higher throughput than using a discreet dataset and the DDN shared parallel architecture further compounds the application performance benefits, with 3X faster ingest than using a legacy NFS data platform.Figure 7. PyTorch application performance on DGX system with different data set formatsThe AI400X appliance delivers faster, scalable AI application performance with DGX system, and the DDN shared parallel architecture provide clear acceleration and benefits at every stage of the end-to-end AI workflow, for every data type.50100150200250300350400450500550600650700750NFS StorageDDN AI400X PyTorch Throughput on DGX System(images/second)JPEG Images Data Set5000100001500020000250003000035000400004500050000NFS Storage DDN AI400XPyTorch Throughput on DGX System(images/second)TFRecords Optimized Data Set3XFASTER INGEST4XFASTER INGEST103 GiB/s READ 162 GiB/s READ 96 GiB/s WRITE143 GiB/s WRITE57% MORE THROUGHPUT PER DGX A100 WITH GDSHDR200 network interface cards simultaneously from a single shared data platform (Figure 9).2 GPUs3 GPUs4 GPUs5 GPUs6 GPUs7 GPUs8 GPUs100% CPU UTILIZATIONO PT IM A L I O S C A L IN G WI T H A 1G PU sContact DDN to Unleash the Power of Your AIDDN has long been a partner of choice for organizations pursuing at-scale data-driven projects.Beyond technology platforms with proven capability, DDN provides significant technicalexpertise through its global research and development and field technical organizations.A worldwide team with hundreds of engineers and technical experts can be called upon tooptimize every phase of a customer project: initial inception, solution architecture, systemsdeployment, customer support and future scaling needs.Strong customer focus coupled with technical excellence and deep field experience ensuresthat DDN delivers the best possible solution to any challenge. Taking a consultative approach,DDN experts will perform an in-depth evaluation of requirements and provide application-leveloptimization of data workflows for a project. They will then design and propose an optimized,highly reliable and easy to use solution that best enables and accelerates the customer effort.Drawing from the company’s rich history in successfully deploying large scale projects, DDNexperts will create a structured program to define and execute a testing protocol that reflectsthe customer environment and meet and exceed project objectives. DDN has equipped itslaboratories with leading GPU compute platforms to provide unique benchmarking and testingcapabilities for AI and DL applications.Contact DDN today and engage our team of experts to unleash the power of your AI projects. About DDNDataDirect Networks (DDN) is the world’s leading big data storage supplier to data-intensive, global organizations. DDN has designed, developed, deployed, and optimized systems, software, and solutions that enable enterprises, service providers, research facilities, and government agencies to generate more value and to accelerate time to insight from their data and information, on premise and in the cloud. ©DataDirect Networks. All Rights Reserved. and A³I , AI200X, AI400X, AI7990X, DDN, and the DDN logo are trademarks of DataDirect Networks. Other Names and Brands May Be Claimed as the Property of Others. V2 11/20。

非编采集P2素材详解

Panasonic AND 新奥特P2与非编如何用非编采集P2卡内的素材?非编采集P2素材详解我台使用的新奥特喜玛拉雅A1000非线性编辑系统能很好地支持松下P2存储卡的使用,只需在非编工作站上加装一只P2驱动器。

台技术人员已经在所有非编工作站上加装了内置的P2驱动器,在主机的光驱位置上,打开非编主机前面板就可见。

■ 使用前提示· 新奥特A1000非编支持P2摄像机拍摄的各种标清和高清格式素材,所有素材都可以在时间线上直接进行编辑,无需转码。

· 采集P2素材需使用非编软件中的“导入P2素材”工具。

P2素材的采集是超实时的,速度在5倍速左右,所以用“导入”来表述更贴切,以下均改称采集P2素材为“导入P2素材”。

· 根据我台当前的应用需求和防病毒需要,目前我们只开放了非编的P2素材导入功能,也就是只能从P2卡中导入素材,而不能往P2卡中回写素材。

如确有回写需要,比如需用P2卡记录高清节目与上级台交流,可求助制作机房技术支持,请技术人员帮助实现。

· 请勿试图用非编“导入P2素材”工具以外的其他途径(如资源管理器)浏览P2卡。

也不要往P2卡内写入任何其它内容,非编工作站装有安全过滤软件,P2卡一旦接入非编,卡中的任何非P2素材将自动删除。

■ P2素材的导入导入P2素材分四步:第一步插入P2卡打开非编主机前面板可看到位于光驱下方的P2卡驱动器,此为型号AJ-PCD35五卡槽驱动器,可同时插5块P2卡。

可以把P2卡插入任一卡槽中,当然也可以同时插多块卡。

卡槽内插入P2卡后,该卡槽左侧的小绿灯会亮起。

注:每个卡槽的左侧均有一个指示灯,指示灯闪烁说明该卡在读写数据,此时请勿取出此卡,以免损坏卡内数据。

第二步打开“导入P2素材”工具点击非编软件工具菜单找到“导入P2素材”工具,双击打开,跳出一个“P2设备”窗口。

第三步连接P2卡点击“P2设备”窗口左上角处的“连接”按钮。

系统会检测P2驱动器的各卡槽,如驱动器内插有P2卡,且卡内有P2素材,则会在场景列表内显示出所有检测到的素材。

________________________________________________ Session S3C MINORITY ENGINEERING PROGRAM C

________________________________________________ 1Joseph E. Urban, Arizona State University, Department of Computer Science and Engineering, P.O. Box 875406, Tempe, Arizona, 85287-5406, joseph.urban@ 2Maria A. Reyes, Arizona State University, College of Engineering and Applied Sciences, Po Box 874521, Tempe, Arizona 852189-955, maria@ 3Mary R. Anderson-Rowland, Arizona State University, College of Engineering and Applied Sciences, P.O. Box 875506, Tempe, Arizona 85287-5506, mary.Anderson@MINORITY ENGINEERING PROGRAM COMPUTER BASICS WITH AVISIONJoseph E. Urban 1, Maria A. Reyes 2, and Mary R. Anderson-Rowland 3Abstract - Basic computer skills are necessary for success in an undergraduate engineering degree program. Students who lack basic computer skills are immediately at risk when entering the university campus. This paper describes a one semester, one unit course that provided basic computer skills to minority engineering students during the Fall semester of 2001. Computer applications and software development were the primary topics covered in the course that are discussed in this paper. In addition, there is a description of the manner in which the course was conducted. The paper concludes with an evaluation of the effort and future directions.Index Terms - Minority, Freshmen, Computer SkillsI NTRODUCTIONEntering engineering freshmen are assumed to have basic computer skills. These skills include, at a minimum, word processing, sending and receiving emails, using spreadsheets, and accessing and searching the Internet. Some entering freshmen, however, have had little or no experience with computers. Their home did not have a computer and access to a computer at their school may have been very limited. Many of these students are underrepresented minority students. This situation provided the basis for the development of a unique course for minority engineering students. The pilot course described here represents a work in progress that helped enough of the students that there is a basis to continue to improve the course.It is well known that, in general, enrollment, retention, and graduation rates for underrepresented minority engineering students are lower than for others in engineering, computer science, and construction management. For this reason the Office of Minority Engineering Programs (OMEP, which includes the Minority Engineering Program (MEP) and the outreach program Mathematics, Engineering, Science Achievement (MESA)) in the College of Engineering and Applied Sciences (CEAS) at Arizona State University (ASU) was reestablished in 1993to increase the enrollment, retention, and graduation of these underrepresented minority students. Undergraduate underrepresented minority enrollment has increased from 400 students in Fall 1992 to 752 students in Fall 2001 [1]. Retention has also increased during this time, largely due to a highly successful Minority Engineering Bridge Program conducted for two weeks during the summer before matriculation to the college [2] - [4]. These Bridge students were further supported with a two-unit Academic Success class during their first semester. This class included study skills, time management, and concept building for their mathematics class [5]. The underrepresented minority students in the CEAS were also supported through student chapters of the American Indian Science and Engineering Society (AISES), the National Society of Black Engineers (NSBE), and the Society of Hispanic Professional Engineers (SHPE). The students received additional support from a model collaboration within the minority engineering student societies (CEMS) and later expanded to CEMS/SWE with the addition of the student chapter of the Society of Women Engineers (SWE) [6]. However, one problem still persisted: many of these same students found that they were lacking in the basic computer skills expected of them in the Introduction to Engineering course, as well as introductory computer science courses.Therefore, during the Fall 2001 Semester an MEP Computer Basics pilot course was offered. Nineteen underrepresented students took this one-unit course conducted weekly. Most of the students were also in the two-unit Academic Success class. The students, taught by a Computer Science professor, learned computer basics, including the sending and receiving of email, word processing, spreadsheets, sending files, algorithm development, design reviews, group communication, and web page development. The students were also given a vision of advanced computer science courses and engineering and of computing careers.An evaluation of the course was conducted through a short evaluation done by each of five teams at the end of each class, as well as the end of semester student evaluations of the course and the instructor. This paper describes theclass, the students, the course activities, and an assessment of the short-term overall success of the effort.M INORITY E NGINEERING P ROGRAMSThe OMEP works actively to recruit, to retain, and to graduate historically underrepresented students in the college. This is done through targeted programs in the K-12 system and at the university level [7], [8]. The retention aspects of the program are delivered through the Minority Engineering Program (MEP), which has a dedicated program coordinator. Although the focus of the retention initiatives is centered on the disciplines in engineering, the MEP works with retention initiatives and programs campus wide.The student’s efforts to work across disciplines and collaborate with other culturally based organizations give them the opportunity to work with their peers. At ASU the result was the creation of culturally based coalitions. Some of these coalitions include the American Indian Council, El Concilio – a coalition of Hispanic student organizations, and the Black & African Coalition. The students’ efforts are significant because they are mirrored at the program/staff level. As a result, significant collaboration of programs that serve minority students occurs bringing continuity to the students.It is through a collaboration effort that the MEP works closely with other campus programs that serve minority students such as: Math/Science Honors Program, Hispanic Mother/Daughter Program, Native American Achievement Program, Phoenix Union High School District Partnership Program, and the American Indian Institute. In particular, the MEP office had a focus on the retention and success of the Native American students in the College. This was due in large part to the outreach efforts of the OMEP, which are channeled through the MESA Program. The ASU MESA Program works very closely with constituents on the Navajo Nation and the San Carlos Apache Indian Reservation. It was through the MESA Program and working with the other campus support programs that the CEAS began investigating the success of the Native American students in the College. It was a discovery process that was not very positive. Through a cohort investigation that was initiated by the Associate Dean of Student Affairs, it was found that the retention rate of the Native American students in the CEAS was significantly lower than the rate of other minority populations within the College.In the spring of 2000, the OMEP and the CEAS Associate Dean of Student Affairs called a meeting with other Native American support programs from across the campus. In attendance were representatives from the American Indian Institute, the Native American Achievement Program, the Math/Science Honors Program, the Assistant Dean of Student Life, who works with the student coalitions, and the Counselor to the ASU President on American Indian Affairs, Peterson Zah. It was throughthis dialogue that many issues surrounding student success and retention were discussed. Although the issues andconcerns of each participant were very serious, the positiveeffect of the collaboration should be mentioned and noted. One of the many issues discussed was a general reality that ahigh number of Native American students were c oming to the university with minimal exposure to technology. Even through the efforts in the MESA program to expose studentsto technology and related careers, in most cases the schoolsin their local areas either lacked connectivity or basic hardware. In other cases, where students had availability to technology, they lacked teachers with the skills to help them in their endeavors to learn about it. Some students were entering the university with the intention to purse degrees in the Science, Technology, Engineering, and Mathematics (STEM) areas, but were ill prepared in the skills to utilize technology as a tool. This was particularly disturbing in the areas of Computer Science and Computer Systems Engineering where the basic entry-level course expected students to have a general knowledge of computers and applications. The result was evident in the cohort study. Students were failing the entry-level courses of CSE 100 (Principals of Programming with C++) or CSE 110 (Principals of Programming with Java) and CSE 200 (Concepts of Computer Science) that has the equivalent of CSE 100 or CSE 110 as a prerequisite. The students were also reporting difficulty with ECE 100, (Introduction to Engineering Design) due to a lack of assumed computer skills. During the discussion, it became evident that assistance in the area of technology skill development would be of significance to some students in CEAS.The MEP had been offering a seminar course inAcademic Success – ASE 194. This two-credit coursecovered topics in study skills, personal development, academic culture issues and professional development. The course was targeted to historically underrepresented minority students who were in the CEAS [3]. It was proposed by the MEP and the Associate Dean of Student Affairs to add a one-credit option to the ASE 194 course that would focus entirely on preparing students in the use of technology.A C OMPUTERB ASICSC OURSEThe course, ASE 194 – MEP Computer Basics, was offered during the Fall 2001 semester as a one-unit class that met on Friday afternoons from 3:40 pm to 4:30 pm. The course was originally intended for entering computer science students who had little or no background using computer applications or developing computer programs. However, enrollment was open to non-computer science students who subsequently took advantage of the opportunity. The course was offered in a computer-mediated classroom, which meantthat lectures, in- class activities, and examinations could all be administered on comp uters.During course development prior to the start of the semester, the faculty member did some analysis of existing courses at other universities that are used by students to assimilate computing technology. In addition, he did a review of the comp uter applications that were expected of the students in the courses found in most freshman engineering programs.The weekly class meetings consisted of lectures, group quizzes, accessing computer applications, and group activities. The lectures covered hardware, software, and system topics with an emphasis on software development [9]. The primary goals of the course were twofold. Firstly, the students needed to achieve a familiarity with using the computer applications that would be expected in the freshman engineering courses. Secondly, the students were to get a vision of the type of activities that would be expected during the upper division courses in computer science and computer systems engineering and later in the computer industry.Initially, there were twenty-two students in the course, which consisted of sixteen freshmen, five sophomores, and one junior. One student, a nursing freshman, withdrew early on and never attended the course. Of the remaining twenty-one students, there were seven students who had no degree program preference; of which six students now are declared in engineering degree programs and the seventh student remains undecided. The degree programs of the twenty-one students after completion of the course are ten in the computing degree programs with four in computer science and six in computer systems engineering. The remaining nine students includes one student in social work, one student is not decided, and the rest are widely distributed over the College with two students in the civil engineering program and one student each in bioengineering, electrical engineering, industrial engineering, material science & engineering, and mechanical engineering.These student degree program demographics presented a challenge to maintain interest for the non-computing degree program students when covering the software development topics. Conversely, the computer science and computer systems engineering students needed motivation when covering applications. This balance was maintained for the most part by developing an understanding that each could help the other in the long run by working together.The computer applications covered during the semester included e-mail, word processing, web searching, and spreadsheets. The original plan included the use of databases, but that was not possible due to the time limitation of one hour per week. The software development aspects included discussion of software requirements through specification, design, coding, and testing. The emphasis was on algorithm development and design review. The course grade was composed of twenty-five percent each for homework, class participation, midterm examination, and final examination. An example of a homework assignment involved searching the web in a manner that was more complex than a simple search. In order to submit the assignment, each student just had to send an email message to the faculty member with the information requested below. The email message must be sent from a student email address so that a reply can be sent by email. Included in the body of the email message was to be an answer for each item below and the URLs that were used for determining each answer: expected high temperature in Centigrade on September 6, 2001 for Lafayette, LA; conversion of one US Dollar to Peruvian Nuevo Sols and then those converted Peruvian Nuevo Sols to Polish Zlotys and then those converted Polish Zlotys to US Dollars; birth date and birth place of the current US Secretary of State; between now and Thursday, September 6, 2001 at 5:00 pm the expected and actual arrival times for any US domestic flight that is not departing or arriving to Phoenix, AZ; and your favorite web site and why the web site is your favorite. With the exception of the favorite web site, each item required either multiple sites or multiple levels to search. The identification of the favorite web site was introduced for comparison purposes later in the semester.The midterm and final examinations were composed of problems that built on the in-class and homework activities. Both examinations required the use of computers in the classroom. The submission of a completed examination was much like the homework assignments as an e-mail message with attachments. This approach of electronic submission worked well for reinforcing the use of computers for course deliverables, date / time stamping of completed activities, and a means for delivering graded results. The current technology leaves much to be desired for marking up a document in the traditional sense of hand grading an assignment or examination. However, the students and faculty member worked well with this form of response. More importantly, a major problem occurred after the completion of the final examination. One of the students, through an accident, submitted the executable part of a browser as an attachment, which brought the e-mail system to such a degraded state that grading was impossible until the problem was corrected. An ftp drop box would be simple solution in order to avoid this type of accident in the future until another solution is found for the e-mail system.In order to get students to work together on various aspects of the course, there was a group quiz and assignment component that was added about midway through the course. The group activities did not count towards the final grade, however the students were promised an award for the group that scored the highest number of points.There were two group quizzes on algorithm development and one out-of-class group assignment. The assignment was a group effort in website development. This assignment involved the development of a website that instructs. The conceptual functionality the group selected for theassignment was to be described in a one-page typed double spaced written report by November 9, 2001. During the November 30, 2001 class, each group presented to the rest of the class a prototype of what the website would look like to the end user. The reports and prototypes were subject to approval and/or refinement. Group members were expected to perform at approximately an equal amount of effort. There were five groups with four members in four groups and three members in one group that were randomly determined in class. Each group had one or more students in the computer science or computer systems engineering degree programs.The three group activities were graded on a basis of one million points. This amount of points was interesting from the standpoint of understanding relative value. There was one group elated over earning 600,000 points on the first quiz until the group found out that was the lowest score. In searching for the group award, the faculty member sought a computer circuit board in order to retrieve chips for each member of the best group. During the search, a staff member pointed out another staff member who salvages computers for the College. This second staff member obtained defective parts for each student in the class. The result was that each m ember of the highest scoring group received a motherboard, in other words, most of the internals that form a complete PC. All the other students received central processing units. Although these “awards” were defective parts, the students viewed these items as display artifacts that could be kept throughout their careers.C OURSE E VALUATIONOn a weekly basis, there were small assessments that were made about the progress of the course. One student was selected from each team to answer three questions about the activities of the day: “What was the most important topic covered today?”, “What topic covered was the ‘muddiest’?”, and “About what topic would you like to know more?”, as well as the opportunity to provide “Other comments.” Typically, the muddiest topic was the one introduced at the end of a class period and to be later elaborated on in the next class. By collecting these evaluation each class period, the instructor was able to keep a pulse on the class, to answer questions, to elaborate on areas considered “muddy” by the students, and to discuss, as time allowed, topics about which the students wished to know more.The overall course evaluation was quite good. Nineteen of the 21 students completed a course evaluation. A five-point scale w as used to evaluate aspects of the course and the instructor. An A was “very good,” a B was “good,” a C was “fair,” a D was “poor,” and an E was “not applicable.” The mean ranking was 4.35 on the course. An average ranking of 4.57, the highest for the s even criteria on the course in general, was for “Testbook/ supplementary material in support of the course.” The “Definition and application of criteria for grading” received the next highest marks in the course category with an average of 4.44. The lowest evaluation of the seven criteria for the course was a 4.17 for “Value of assigned homework in support of the course topics.”The mean student ranking of the instructor was 4.47. Of the nine criteria for the instructor, the highest ranking of 4.89 was “The instructor exhibited enthusiasm for and interest in the subject.” Given the nature and purpose of this course, this is a very meaningful measure of the success of the course. “The instructor was well prepared” was also judged high with a mean rank of 4.67. Two other important aspects of this course, “The instructor’s approach stimulated student thinking” and “The instructor related course material to its application” were ranked at 4.56 and 4.50, respectively. The lowest average rank of 4.11 was for “The instructor or assistants were available for outside assistance.” The instructor keep posted office hours, but there was not an assistant for the course.The “Overall quality of the course and instruction” received an average rank of 4.39 and “How do you rate yourself as a student in this course?” received an average rank of 4.35. Only a few of the students responded to the number of hours per week that they studies for the course. All of the students reported attending at least 70% of the time and 75% of the students said that they attended over 90% of the time. The students’ estimate seemed to be accurate.A common comment from the student evaluations was that “the professor was a fun teacher, made class fun, and explained everything well.” A common complaint was that the class was taught late (3:40 to 4:30) on a Friday. Some students judged the class to be an easy class that taught some basics about computers; other students did not think that there was enough time to cover all o f the topics. These opposite reactions make sense when we recall that the students were a broad mix of degree programs and of basic computer abilities. Similarly, some students liked that the class projects “were not overwhelming,” while other students thought that there was too little time to learn too much and too much work was required for a one credit class. Several students expressed that they wished the course could have been longer because they wanted to learn more about the general topics in the course. The instructor was judged to be a good role model by the students. This matched the pleasure that the instructor had with this class. He thoroughly enjoyed working with the students.A SSESSMENTS A ND C ONCLUSIONSNear the end of the Spring 2002 semester, a follow-up survey that consisted of three questions was sent to the students from the Fall 2001 semester computer basics course. These questions were: “Which CSE course(s) wereyou enrolled in this semester?; How did ASE 194 - Computer Basi cs help you in your coursework this semester?; and What else should be covered that we did not cover in the course?”. There were eight students who responded to the follow-up survey. Only one of these eight students had enrolled in a CSE course. There was consistency that the computer basics course helped in terms of being able to use computer applications in courses, as well as understanding concepts of computing. Many of the students asked for shortcuts in using the word processing and spreadsheet applications. A more detailed analysis of the survey results will be used for enhancements to the next offering of the computer basics course. During the Spring 2002 semester, there was another set of eight students from the Fall 2001 semester computer basi cs course who enrolled in one on the next possible computer science courses mentioned earlier, CSE 110 or CSE 200. The grade distribution among these students was one grade of A, four grades of B, two withdrawals, and one grade of D. The two withdrawals appear to be consistent with concerns in the other courses. The one grade of D was unique in that the student was enrolled in a CSE course concurrently with the computer basics course, contrary to the advice of the MEP program. Those students who were not enrolled in a computer science course during the Spring 2002 semester will be tracked through the future semesters. The results of the follow-up survey and computer science course grade analysis will provide a foundation for enhancements to the computer basics course that is planned to be offered again during the Fall 2002 semester.S UMMARY A ND F UTURE D IRECTIONSThis paper described a computer basics course. In general, the course was considered to be a success. The true evaluation of this course will be measured as we do follow-up studies of these students to determine how they fare in subsequent courses that require basic computer skills. Future offerings of the course are expected to address non-standard computing devices, such as robots as a means to inspire the students to excel in the computing field.R EFERENCES[1] Office of Institutional Analysis, Arizona State UniversityEnro llment Summary, Fall Semester , 1992-2001, Tempe,Arizona.[2] Reyes, Maria A., Gotes, Maria Amparo, McNeill, Barry,Anderson-Rowland, Mary R., “MEP Summer Bridge Program: A Model Curriculum Project,” 1999 Proceedings, American Society for Engineering Education, Charlotte, North Carolina, June 1999, CD-ROM, 8 pages.[3] Reyes, Maria A., Anderson-Rowland, Mary R., andMcCartney, Mary Ann, “Learning from our MinorityEngineering Students: Improving Retention,” 2000Proceedings, American Society for Engineering Education,St. Louis, Missouri, June 2000, Session 2470, CD-ROM, 10pages.[4] Adair, Jennifer K,, Reyes, Maria A., Anderson-Rowland,Mary R., McNeill, Barry W., “An Education/BusinessPartnership: ASU’s Minority Engineering Program and theTempe Chamber of Commerce,” 2001 Proceeding, AmericanSociety for Engineering Education, Albuquerque, NewMexico, June 2001, CD-ROM, 9 pages.[5] Adair, Jennifer K., Reyes, Maria A., Anderson-Rowland,Mary R., Kouris, Demitris A., “Workshops vs. Tutoring:How ASU’s Minority Engineering Program is Changing theWay Engineering Students Learn, “ Frontiers in Education’01 Conference Proceedings, Reno, Nevada, October 2001,CD-ROM, pp. T4G-7 – T4G-11.[6] Reyes, Maria A., Anderson-Rowland, Mary R., Fletcher,Shawna L., and McCartney, Mary Ann, “ModelCollaboration within Minority Engineering StudentSocieties,” 2000 Proceedings, American Society forEngineering Education, St. Louis, Missouri, June 2000, CD-ROM, 8 pages.[7] Anderson-Rowland, Mary R., Blaisdell, Stephanie L.,Fletcher, Shawna, Fussell, Peggy A., Jordan, Cathryne,McCartney, Mary Ann, Reyes, Maria A., and White, Mary,“A Comprehensive Programmatic Approach to Recruitmentand Retention in the College of Engineering and AppliedSciences,” Frontiers in Education ’99 ConferenceProceedings, San Juan, Puerto Rico, November 1999, CD-ROM, pp. 12a7-6 – 12a7-13.[8] Anderson-Rowland, Mary R., Blaisdell, Stephanie L.,Fletcher, Shawna L., Fussell, Peggy A., McCartney, MaryAnn, Reyes, Maria A., and White, Mary Aleta, “ACollaborative Effort to Recruit and Retain UnderrepresentedEngineering Students,” Journal of Women and Minorities inScience and Engineering, vol.5, pp. 323-349, 1999.[9] Pfleeger, S. L., Software Engineering: Theory and Practice,Prentice-Hall, Inc., Upper Saddle River, NJ, 1998.。

Cisco ASR 1000 Series Embedded Services Processors

Data Sheet Cisco ASR 1000 Series Embedded Services ProcessorsProduct OverviewThe Cisco® ASR 1000 Series Embedded Services Processors (ESPs) handle all the network data-planetraffic-processing tasks of Cisco ASR 1000 Series Aggregation Services Routers. These ESPs allow the activation of concurrent enhanced network services, such as cryptography, firewall, Network Address Translation (NAT), quality of service (QoS), NetFlow, and many others while maintaining line speeds. Figure 1 shows the Cisco ASR 1000 Series ESP 100 and ESP 200.Cisco ASR 1000 Series Routers are placed at the WAN edge of your enterprise data center or large office, as well as in service provider points of presence (POPs). The routers rely on the power of the ESPs to aggregate multiple traffic flows and network services, including encryption and traffic management, and forward them across WAN connections at line speeds. With router options that run from 2.5 to 200 Gbps, the Cisco ASR Family contains many models and licensing options to meet the speed and budget requirements of different types of organizations and various-sized locations.The Cisco ASR 1000 ESP components of these routers accelerate service delivery using parallel processing. The ESPs are based on the Cisco Flow Processor (FP) for next-generation forwarding and queuing in silicon. They operate at 20-, 40-, 100-, and 200-Gbps data-plane forwarding throughput rates. Together, the Cisco ASR 1001-X, ASR 1001-HX, ASR 1002-HX, and ASR 1002-X Routers and 100- and 200-Gbps ESPs introduce the second generation of the Cisco FP hardware and software architecture. With FP-based ESPs at their core, ASR 1000 Routers accomplish the following:●Handle all baseline packet routing operations, including MAC address classification, Layer 2 and Layer 3forwarding, QoS classification, and NetFlow packet accounting●Perform advanced services such as IP Security (IPsec) encryption, Network Address Translation (NAT),firewall, AppNav, Cisco Application Visibility and Control (AVC), Performance Routing (PfR), and Locator ID Separation Protocol (LISP); they offer diverse feature Layer 2 connectivity options such as Ethernet over MPLS (EoMPLS), Virtual Private LAN Services (VPLS), Overlay Transport Virtualization (OTV), and Virtual Extensible LAN Services (VXLAN)Platform OverviewThe following embedded services processors are supported on the Cisco ASR 1000 Series Routers:●Cisco ASR 1000 Series 20-Gbps Embedded Services Processor●Cisco ASR 1000 Series 40-Gbps Embedded Services Processor●Cisco ASR 1000 Series 100-Gbps Embedded Services Processor●Cisco ASR 1000 Series 200-Gbps Embedded Services ProcessorFigure 1. Cisco ASR 1000 Series ESP 100 and ESP 200Features and BenefitsThe main engine of the ESP is the Cisco FP, the industry’s first programmable and application-aware network processor. The Cisco FP forms the overall hardware and software architecture of the ESP. It consolidates up to 256 customized packet-processor cores (900 MHz to 1.5 GHz) into a single processor. The parallel processing capability eliminates the need for additional service blades inside the router, because all processing is performed on the FP. As a result, the ESPs enable the ASR 1000s to support the following functions and features with high performance:●Forwarding, traffic management, and services●Large-scale parallel processing with centralized shared memory to achieve low-latency packet processing●High-performance deep-packet inspection (DPI) with full visibility into the entire Layer 2 frame, includingpayload●Rapid feature development with ANSI-C software development framework●Up to 200-Gbps system throughput and up to 130 millions of packets per second (mpps) to address WANaggregation needs●Hardware-assisted cryptographic performance to yield up to 78 Gbps of throughput to enable secure WANaccess and compliance●Line-speed zone-based firewall that provides up to 200 Gbps of throughput and 6-mpps firewall sessions●DPI, Cisco IOS® Software Zone-Based Firewall distributed denial of service (DDoS) detection andprevention, and control-plane protection●Cisco Session Border Control (SBC) for terminating and interconnecting media terminations with fullaccounting and flow control●Cisco Multicast Visual Quality Experience (VQE) and video Call Admission Control (CAC) for enhanceduser experiences●Hardware-accelerated traffic classification and traffic shaping with support for up to 464,000 queues●Flexible traffic prioritization and efficient WAN bandwidth use with minimum, maximum, and excessbandwidth allocation with priority propagationUse CasesThe ESPs address the following applications and use cases:●Service provider broadband: The Cisco ASR 1000 Series Router serves as a broadband aggregation routerthat terminates up to 64,000 subscriber sessions. It supports features such as SBC for voice over IP (VoIP) and video services (including Cisco TelePresence® communications systems) and hardware-assisted per-user firewall for security.●Service provider-managed customer premises equipment (CPE): The Cisco ASR 1000 Router serves as aWAN aggregation router with high-density Gigabit Ethernet or WAN link aggregation and 10 GigabitEthernet uplink capabilities. Key benefits are Layer 2 and Layer 3 VPN functions and line-rate IP Multicast support for triple-play (data, voice, and video) deployments.●Multimedia provider edge (PE): The Cisco ASR 1000 Series Router interfaces with enterprise and serviceprovider-provisioned voice and multimedia services directly at the edge. You do not need an overlaynetwork, network appliances, or service blades, lowering operating expenses (OpEx) and offering flexible deployment models. This router supports protected signaling for both voice and video services andfacilitates 32,000 voice calls concurrent with up to 200 Gbps of data traffic with accounting, firewall, andcall-quality features enabled.●Enterprise WAN aggregation: At the WAN aggregation headend, the Cisco ASR 1000 Router facilitates abranch-office architecture that offers excellent investment protection with services and scale. Solutionbenefits consist of a multigigabit encryption rate (up to 78-Gbps IPsec cryptography throughput) andoptimization of the WAN to route around brownouts in the service provider network to guaranteemission-critical applications.●Enterprise Internet gateway: As an Internet gateway, the ASR 1000 delivers multigigabit Cisco IOS Firewallcapability without the need for service blades. All firewall processing occurs in silicon 2.5-, 5-, 10-, 20-, 40-, 100-, or 200-Gbps speeds. In addition, the router provides high-speed logging through Sampled NetFlow Version 9 and ongoing forwarding with baseline and firewall features enabled.●Enterprise Intelligent WAN (IWAN): The scalable Cisco ASR 1000 Router smoothly enables the intelligentWAN architecture that allows enterprises to reduce expensive WAN costs by adopting business-classInternet as a transport while maintaining privacy, confidentiality with crypto, and regulatory compliance witha zone-based firewall.●Enterprise Data Center Interconnect (DCI): The scalable Cisco ASR 1000 Router securely enables theinterconnection of data centers to the cloud to consume services and migrate workloads to provide disaster recovery and normal data center management operations.Platform Support and CompatibilityTo benefit from feature-rich services of Cisco ASR 1000 Routers, Cisco IOS XE Software Release 2.4 or later is required. For the newly added Cisco ASR 1001-X Router, Cisco IOS XE Software Release 3.12 or later is required. For ESP data-plane throughput compatibilities by ASR platform, refer to Tables 1 through 8.Table 1. Cisco ASR 1000 Series Integrated ESP in Cisco ASR 1002-HX Chassis Compatible HardwareTable 2. Cisco ASR 1000 Series Integrated ESP in the ASR 1001-HX Chassis Compatible HardwareTable 3. Cisco ASR 1000 Series Integrated ESP in Cisco ASR 1001-X Chassis Compatible HardwareTable 4. Cisco ASR 1000 Series Integrated ESP in Cisco ASR 1002-X Chassis Compatible Hardware* Supports 1 + 1 redundancy when configured with two 10-Gbps Cisco ASR 1000 ESP modules.Table 5. Cisco ASR 1000 Series 20-Gbps ESP (ASR1000-ESP20) Compatible Hardware* Supports 1 + 1 redundancy when configured with two 20-Gbps Cisco ASR 1000 ESP modules.Table 6. Cisco ASR 1000 Series 40-Gbps ESP (ASR1000-ESP40) Compatible Hardware* Supports 1 + 1 redundancy when configured with two 40-Gbps Cisco ASR 1000 ESP modules.Table 7. Cisco ASR 1000 Series 100-Gbps ESP (ASR1000-ESP100) Compatible Hardware* Supports 1 + 1 redundancy when configured with two 100-Gbps Cisco ASR 1000 ESP modules. Table 8. Cisco ASR 1000 Series 200-Gbps ESP (ASR1000-ESP200) Compatible HardwareProduct SpecificationsTables 9 through 13 list specifications of all ESPs in the ASR 1000 Series product family. Table 9. Specifications of Integrated ESP Module in Cisco ASR 1002-HX ChassisTable 10. Specifications of Integrated ESP Module in the Cisco ASR 1001-HX ChassisTable 11. Specifications of Integrated ESP Module in Cisco ASR 1001-X ChassisTable 12. Specifications of Cisco ASR 1000 Series 5-, 10-, 10-N-, 20-, 40-, 100-, and 200-Gbps ESP ModulesTable 13. Specifications of Integrated ESP Module in Cisco ASR 1002-X ChassisSystem RequirementsTable 14 details the system requirements of the ASR 1000 ESPs.Table 14. System RequirementsFor 20-Gbps Cisco ASR 1000 ESP: Cisco ASR 1004 Router chassis with one instance of Cisco ASR 1000 SeriesRoute Processor and one instance of Cisco ASR 1000 Series SPA Interface ProcessororCisco ASR 1006 Router chassis with at least one instance of Cisco ASR 1000 Series Route Processor and oneinstance of Cisco ASR 1000 Series SPA Interface ProcessorFor 40-Gbps Cisco ASR 1000 ESP: Cisco ASR 1006 Router chassis with at least one instance of Cisco ASR 1000Series Route Processor and one instance of Cisco ASR 1000 Series SPA Interface ProcessororCisco ASR 1004 Router chassis with at least one instance of Cisco ASR 1000 Series Route Processor and oneinstance of Cisco ASR 1000 Series SPA Interface ProcessororCisco ASR 1013 Router chassis with at least one instance of Cisco ASR 1000 Series Route Processor and oneinstance of Cisco ASR 1000 Series SPA Interface ProcessororCisco ASR 1006-X Router chassis with at least one instance of Cisco ASR 1000 Series Route Processor and oneinstance of Cisco ASR 1000 Series SPA Interface Processor or Cisco ASR 1000 Ethernet Line CardorCisco ASR 1009-X Router chassis with at least one instance of Cisco ASR 1000 Series Route Processor and oneinstance of Cisco ASR 1000 Series SPA Interface Processor or Cisco ASR 1000 Ethernet Line CardFor 100-Gbps Cisco ASR 1000 ESP: Cisco ASR 1006 Router chassis with at least one instance of Cisco ASR 1000Series Route Processor and one instance of Cisco ASR 1000 Series SPA Interface ProcessororCisco ASR 1013 Router chassis with at least one instance of Cisco ASR 1000 Series Route Processor and oneinstance of Cisco ASR 1000 Series SPA Interface Processor or Cisco ASR 1000 Ethernet Line CardorCisco ASR 1006-X Router chassis with at least one instance of Cisco ASR 1000 Series Route Processor or CiscoASR 1000 Ethernet Line CardorCisco ASR 1009-X Router chassis with at least one instance of Cisco ASR 1000 Series Route ProcessorFor 200-Gbps Cisco ASR 1000 ESP: Cisco ASR 1013 Router chassis with at least one instance of Cisco ASR 1000Series Route Processor and one instance of Cisco ASR 1000 Series SPA Interface Processor or Cisco ASR 1000Ethernet Line CardorCisco ASR 1009-X Router chassis with at least one instance of Cisco ASR 1000 Series Route Processor and oneinstance of Cisco ASR 1000 Series SPA Interface Processor or Cisco ASR 1000 Ethernet Line CardSoftware Cisco IOS XE Software Release 2.1 (for 5- and 10-Gbps ESPs only) or later(10-N- and 20-Gbps ESPs: Release 2.2 or later)Cisco IOS XE Software Release 2.4 (for 2.5-Gbps ESP integrated in the Cisco ASR 1002-F chassis)Cisco IOS XE Software Release 3.1.0S (for 40-Gbps ESP) or laterCisco IOS XE Software Release 3.2.0S (for 40-Gbps ESP support on Cisco ASR 1004) or laterCisco IOS XE Software Release 3.2.0S (for integrated ESP in Cisco ASR 1001 chassis) or laterCisco IOS XE Software Release 3.7.0S (for integrated ESP in Cisco ASR 1002-X chassis) or laterCisco IOS XE Software Release 3.7.1S or later for 100-Gbps ESPCisco IOS XE Software Release 3.10.0S or later for 200-Gbps ESPCisco IOS XE Software Release 16.2.1S or later for ASR 1002-HX ESPCisco IOS XE Software Release 16.3.1S or later for ASR 1001-HX ESPPerformance and ScalingAll performance numbers are based on the RFC-2544 test methodology.Table 15 lists the performance and scaling features offered by the ASR 1002-HX chassis with an integrated ESP module.Table 15. Cisco ASR 1002-HX with Integrated ESP ModuleTable 16 lists the performance and scaling features offered by the ASR 1001-HX chassis with an integrated ESP module.Table 16. Cisco ASR 1001-HX with Integrated ESP ModuleTable 17 lists the performance and scaling features offered by the Cisco ASR 1001-X chassis with an integrated ESP module.Table 17. Cisco ASR 1001-X with Integrated ESP Module and 8-GB MemoryTable 18 lists the performance and scaling features offered by the Cisco ASR 1002-X chassis with an integrated ESP module.Table 18. Cisco ASR 1002-X with Integrated 36-Gbps ESP Module and 8-GB MemoryTable 19 lists the performance and scaling features offered by the Cisco ASR 1000 Series 20-Gbps ESP module. Table 19. Cisco ASR 1000 Series 20-Gbps ESP Performance and ScalingTable 20 lists the performance and scaling features offered by the Cisco ASR 1000 Series 40-Gbps ESP module. Table 20. Cisco ASR 1000 Series 40-Gbps ESP Performance and ScalingTable 21 lists the performance and scaling features offered by the Cisco ASR 1000 Series 100-Gbps ESP module. Table 21. Cisco ASR 1000 Series 100-Gbps ESP Performance and ScalingTable 22 lists the performance and scaling features offered by the Cisco ASR 1000 Series 200-Gbps ESP module. Table 22. Cisco ASR 1000 Series 200-Gbps ESP Performance and ScalingPlease refer to the Cisco ASR 1000 Series Routing Processor data sheet for a list of software features and benefits applicable to broadband, service provider edge, and enterprise deployments.Ordering InformationTable 23 gives ordering information for the Cisco ASR 1000 Series ESPs.Table 23. Ordering InformationFor the ordering guide, download the complete ASR 1000 Series Ordering Guide.Cisco ServicesCisco offers a wide range of services programs to accelerate customer success. These innovative servicesprograms are delivered through a unique combination of people, processes, tools, and partners, resulting in highlevels of customer satisfaction. Cisco Services can help you protect your network investment, optimize networkoperations, and prepare your network for new applications to extend network intelligence and the power of yourbusiness. For more information about Cisco Services, refer to Cisco Technical Support Services or CiscoAdvanced Services.Warranty InformationFind warranty information by searching the Cisco warranty finder athttps:///WarrantyFinder.aspx.Cisco CapitalFinancing to Help You Achieve Your ObjectivesCisco Capital can help you acquire the technology you need to achieve your objectives and stay competitive. Wecan help you reduce CapEx. Accelerate your growth. Optimize your investment dollars and ROI. Cisco Capital®financing gives you flexibility in acquiring hardware, software, services, and complementary third-party equipment.And there’s just one predictable payment. Cisco Capital is available in more than 100 countries. Learn more.For More InformationFor more information about the Cisco ASR 1000 Series or the ESPs, visit https:///go/asr1000 orcontact your local Cisco account representative.Printed in USA C78-731640-20 12/17。

H3C SecCenter A1000 开局指导书(V1.00)

H3C SecCenter A1000安全管理中心开局指导书Deployment Instructions for XXX Beta Test(仅供内部使用)(For internal use)拟制: Drafted by: 谢剑平 日期: Date: 2007/04/10 审核:Reviewed by: 吕振峰 日期: Date: 2007/04/10 审核:Reviewed by: 日期: Date: yyyy/mm/dd 批准:Approved by:日期: Date:yyyy/mm/dd华为3Com 技术有限公司Huawei-3Com Technologies Co., Ltd.版权所有 侵权必究 All rights reserved修订记录Revision Records目录 Catalog1. 介绍Introduction (5)1.1.系统介绍Instruction to the System (6)1.2.组网介绍Introduction to Networking (6)1.3.系统结构介绍Introduction to System Architecture (8)硬件规格 (8)SecCenter A1000支持的数据采集方式 (9)SecCenter A1000与其它系统的通讯 (11)2. 业务配置Service Configuration (11)2.1.SecCenter A1000网络接口出厂配置 (11)2.2.SecCenter A1000系统的远程访问方式 (12)2.3.SecCenter A1000系统启动及关机 (13)2.4.SecCenter A1000的部署位置 (14)2.5.SecCenter A1000的网络接口配置 (15)2.6.通过Web方式登录SecCenter A1000 (17)SecCenter A1000 Web客户端的软件需求 (17)2.7.SecCenter A1000 License授权操作指南 (18)2.8.配置设备的syslog主机地址 (20)2.8.1.设备启用license方法 (21)2.9.SecCenter A1000采集端口配置 (22)2.10.SecCenter A1000接收网流报文操作指南 (24)Stream (24)2.10.2.SecPath防火墙二进制流日志 (24)flow/CFlow (24)2.10.4.网流报文正常接收验证 (25)2.11.Windows主机操作指南 (26)2.11.1.手动增加Windows主机方法 (26)2.11.2.主机启用license方法 (27)2.11.3.Windows WMI接口测试 (28)2.11.4.主机采集监视策略设置 (29)2.12.Unix主机操作指南 (31)2.12.1.手动增加Unix主机方法 (31)2.12.2.主机启用license、采集监视及策略配置方法 (32)2.12.3.Unix主机的syslog发送、SSH接口配置方法 (32)2.13.数据库DB Audit操作指南 (32)3. 目前还存在的问题,需要安装维护中注意的事项Current Problems and Matters Deserving Attention in Installation and Maintenance (33)3.1.报告数据滞后问题 (33)3.2.报告无数据输出问题 (33)3.3.Forensics查询数据滞后问题 (33)3.4.手动删除设备后不能再自动发现设备问题 (33)3.5.进程重新启动问题 (34)3.6.License失效问题 (34)3.7.DB Audit功能无操作成功提示问题 (35)3.8.Unix主机使用SSH接口无连接测试问题 (36)4. 扩容及升级Expansion and Upgrade Method (37)4.1.采用外部存储系统保存原始数据配置方法 (37)4.2.SecCenter A1000系统升级方法 (38)4.3.分布式部署SecCenter A1000 (42)4.3.1.分布式部署SecCenter A1000组网方式 (42)4.3.2.分布式部署SecCenter A1000软件定制方法 (43)4.3.3.分布式部署方式下的license授权问题 (48)开局指导书Customer sites Deployment Instructions关键词:Key words:防火墙、IPS、IDS、Windows主机、Unix主机、Syslog、NetStream、NetFlow、数据库、法规遵从报告、Web管理界面、数据库审计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

与使用条件无关,使电机的效率经常保 持在最大的自学习。

ASR*学习

*Automatic Speed Regulator

惯性 学习

■配备新方式的在线自学习

运行中可以一直检出电机特性的变化,进行高精度的速度控制。

给客户的机械带来最适宜响 应性的学习。以往比较花时 间的调试过程也大幅缩短。

2.变频器开创的环境性能

・节能 ・符合环境 ・安全环境

3.改变机械等级的业界最强性能

・加速机械小型化的简洁设计 ・可根据客户喜好定制变频器 ・轻松调试 ・确实可靠的制动功能 ・多种通信选购件 ・长寿命设计 ・简单维护

U080601-2/34

超群的电机驱动性能

最先进的电机驱动技术

■实现所有电机的控制。

■原有产品■

■A1000■

减少23.3%

(注)对噪音值进行频率分析,峰值比较

抑制电源高次谐波

■标配高次谐波抑制用的直流电抗器。(22kW以上) ■我们也备有抑制高次谐波的12相、18相整流选购件*、高次谐波抑制滤波器。

*:准备中。客户需要准备3卷线、4卷线变压器。

U080601-14/34

变频器开创的环境性能

输出电流

抑制起动电流,无振动的快 速起动

输出电流

利用再生能量继续运行

【最适宜用途】 风机、泵驱动等有旋转体的流体机械

【最适宜用途】 薄膜生产线或纤维生产线等的瞬时停电对策

U080601-9/34

超群的电机驱动性能

符合用途的瞬时停电措施

■可实现2秒钟*的瞬时停电补偿。

・符合半导体制造设备规格。 ・可减少UPS(无停电电源装置)等特殊的设备。 ・检出瞬时停电时的电圧降低,并输出。

无论是感应电机或是同步电机(IPM电机/SPM电机)都能实现高性能的电流矢量控制

■实现了感应电机、同步电机用的变频器库存的通用化。 ■可以通过参数设定,切换感应电机和同步电机。

通过参数 简单切换

感应电机

特点 容量 范围

同步电机 SPM电机 (SMRA系列)

・超小形,超轻量 ・节能・高效率 ・全封闭无风扇结构

■A1000■

电源电圧

电源电圧

旋转速度

自由运行状态,长时间旋 转,容易有危险

自由运行停止

旋转速度

电机快速地减速停止, 很安全

减速停止

U080601-17/34

改变机械等级的业界最强性能

加速机械小型化的简洁设计

■世界最小级别的变频器与小形、轻量的同步电机组合, 加速了机械的小形化

●变频器体积比

400V 75kW示例

■我们也备有防尘,防滴形的IP54*等的保护结构产品。

*:准备中

符合RoHS

■标准产品即符合RoHS(欧州特定有害物质使用限制)指令。

符合RoHS

U080601-13/34

变频器开创的环境性能

符合环境

降低噪音

■采用SwingPWM方式,抑制电磁噪音的同时,降低了刺耳的噪音。

●原有产品与Swing PWM方式的噪音比较

The Answer is A1000

安川变频器 高性能矢量控制

A1000

符合RoHS

(注) 部分机型申请中。

200V级 0.4~110kW / 400V级 0.4~355kW

安川電機(上海)有限公司

变频器事业部

2009.03.06

U080601-1/31

主要特点

1.超群的电机驱动性能

・最先进的电机驱动技术 ・无传感器定位控制 ・革新的转矩特性 ・内置丰富的自学习功能 ・平滑的运行 ・符合用途的瞬时停电措施

U080601-16/34

变频器开创的环境性能

安全环境

停电时的安全停止

■配备了停电时电机不是自由运行,而是能快速安全地减速停止的 KEB(Kinetic Energy Back-up)功能。

●KEB功能,能更安全地快速减速

【最适宜用途】 最适用于工作机械主轴电机,或薄膜生产线等的停电措施。

■原有产品■

●编制特殊动作

例:无传感器的简易位置控制功能 <开发中>

●编制检出功能

例:机械劣化诊断(机械的转矩脉动检出)

■标配USB接口,可以直接连接电脑。

●通过USB接口与电脑的连接

(注)配备WV103电缆用通信接口。 请将操作器取下后使用。

U080601-20/34源自改变机械等级的业界最强性能

轻松调试

■自动设定最适宜的参数

超群的电机驱动性能

革新的转矩特性(驱动同步电机IPM电机时)