基于DSP和FPGA的通用数字控制器硬件设计

基于DSP、FPGA和单片机的大尺寸激光数控加工系统的软硬件设计

使用单片机控制人机界 面、 使用 D P对加工数据进行处理并 由 F G S P A输 出加工信 号 , 硬件 上保证 了系统 的高速运 从 算和精密加工 。此外系统将加工数据保 存 于非易 失性 存储器 中 , 使得 系统拥 有脱 机加 工 的能 力 。通 过对 以 D P和 S F GA为 核心 的加工控 制部 分的软 、 P 硬件进行优化 , 该系统达到 了设计 目标并取得 了令人 满意的加 工效果 。 关键词 :数控加工 ;激光 ;D P F G ;单片机 S; PA

加工信号产生的全部工作 , 或者 由计算机生成加工信号直

接驱 动加 工部件 。对 于前 一 种做 法 , 片 机 的数 据处 理 能 单 力往往 达不 到要 求 , 限制 了 性 能 的发 挥 。而 后 一 种 做 法 ,

维普资讯

电

EL ECTRoNI C

子

测

量

技 术

TE CHNoI0GY ,

第3 O卷 第 6 期

20 0 7年 6 月

基 于 DS F GA 单 片 机 的 大 尺 寸 P、 P 和

激 光 数 控 加 工 系 的软硬 件 设计 * 统

张师伟 傅 星 杨 恒 宗 邱 维 宝 邬 勇 胡小唐

( 津大学 精 密测试技 术及仪 器 国家重点 实验 室 天津 天 307) 0 0 2

摘

要 :为 了满足大尺寸激光加工 的精度 和速度要求 , 本文设计 了以 D P F G S 、P A和单片机为核心的数控 系统 。系统

Abta t Tos tsy t erq ie e t fp eiin a d s e d frlr esz ae ahnn aCNC y tm a e nt e sr c : aif h e urm nso rcso n p e o ag -ielsrm c iig, s se b s do h DS F GA n co o tolri e eo e . ir cntolri s O c n r lte h ma - o ue tra e DS S P。 P a d mir c n r l d v lp d M co o r l u e t o to h u n c mp tri e fc 。 P i e S e S d n u e Op o est ed t , n PGA su e O o tu h ahnn in 1Th ad r e to e b v n u e h sd t r cs h aa a d F i s dt u p tt em c iig sg a. eh r waem nin a o ee s r st e d c p bl iso ih s e d a d p e iin o c iig n a dt n,h aa a es v d i ls mo y ta k st e a a it fhg -p e n rcso fma hnn .I d ii t e d t r a e n f h me r h tma e h ie o a ma hn r fl e c iewo k ofi .By o t zn h e in o ot r n ad r ,h y tm e c e h ein g as a d n pi ig te d sg fs fwae a d h r wa e t e s se ra h s t e d sg o l, n mi s t fi ah nn fet r b an c ai yn m c iig efcsa eo tiek s g

基于DSP—FPGA的通用数字控制器硬件设计

系统 两大 类 , 随着 数 字技术 的发展 , 模拟 控制 系统

h d a e de in a eve ii d t oug a tc la plc to ar w r sg r rfe hr h pr c ia p ia in.

Ke r s g n r l p r o e d g t lc n r l r i ia sg a r c s o s ( P);f l r g a ywo d : e e a — u p s i i o t o l ;dg t l i n lp o e s r DS a e i d p o r mma l a e e b e g t a r y( GA) o rma a e n ;b s ra FP ;p we n g me t u

设 计 方案 、 C U板 上 的 电 源 管 理 电 路 、 字 信 号 处 理 器 D P及 其 外 围设 计 、 场 可 编 程 门 阵 列 F G 的 配 主 P 数 S 现 P A 置 电路 、 线 驱 动 电 路 作 了 详 细 说 明 。实 际 应 用 验 证 了该 数 字 控 制 器 硬 件 设 计 的正 确 性 和可 靠 性 总 关 键 词 : 用 数 字 控 制 器 ; 字 信 号 处 理 器 ; 场 可 编 程 门阵 列 ; 源 管理 ; 线 通 数 现 电 总

Ab ta t I r e o m a r w a e a o t r e r lp p s g t lc nt o lrs a a d z ton a sr c :n o d r t keha d r nd s f wa eofg ne a— ur o e diia o r le t nd r ia i nd mo dulrz to a ia i n,a m p o t e f m a e o e ltm e, t bi t a nt—nt re e c nd i r veis p ror nc f r a i s a l y nd a ii e f r n e, t ar i he h dwa e d sgn r e i wa s i d ba e n s de crbe s d o DSP + FPG A ne a — r os gia on r le ge r lpu p edi t lc t o lr.a lus r t d t sgn ofc t o — nd il ta e hede i on r l

基于DSP和FPGA的转台控制器的设计实现

a c r c f t r i g a g e i . 1 i h i e r i c e sn rd c e sn t l f u p ti g p le c u a y o u nn n l s0 O n t e l a n r a i g o e r a ig s y e o t u tn u s . n o Ke wo d :s e - t r h r c e it so lc r ma n tc s a trn ; DS y r s t p mo o ;c a a t rs i fe e t o g e i c te i g c P

线性启 动或停止 的方式 可以使转 动角度 的精度满 足 0 0 度的要求 。 .1

关 键 词 :步 进 电机 ; 电磁 散 射 特 性 ;D P S 中 图分 类 号 :TN l. 5 文 献 标 识 码 :A 912

De i n o u n a l o r le a e n DSP a sg ft r t b ec nto lr b s d o nd FPGA

d vc n o u e . Th e t g r s l s o h t t e c n r l r c n a h e e v ro s t s i g r q ie n n h e ie a d c mp t r e t s i e u t h ws t a h o t o l a c iv a i u e t e u r me t a d t e n e n

1 系统 构 成 0 引 言

系统 主要 由 DS P和 F GA控 制模 块 、 P 串行 口通 讯 模

在室 内电磁 散射测 量 系统 中 , 了获得 被 测 目标 的全 为

块 、 盘和 显示模 块 以及步 进 电机 脉 冲输 出模块 几 部分 构 键

DSP+FPGA 多种设计方案

1,DSP+FPGA 实时信号处理系统2,FPGA+DSP实时三维图像信息处理系统3,采用FPGA+DSP结构的多通道高速数据采集与实时图像处理系统的设计与实现方案4,基于DSP与FPGA的蓝牙数据采集系统设计5,基于DSP和FPGA的通用图像处理平台设计6,基于FPGA+DSP的实时图像处理系统设计与实现7,基于DSP的实时图像目标搜索与跟踪系统设计1,DSP+FPGA 实时信号处理系统实时信号处理系统要求必须具有处理大数据量的能力,以保证系统的实时性;其次对系统的体积、功耗、稳定性等也有较严格的要求。

实时信号处理算法中经常用到对图象的求和、求差运算,二维梯度运算,图象分割及区域特征提取等不同层次、不同种类的处理。

其中有的运算本身结构比较简单,但是数据量大,计算速度要求高;有些处理对速度并没有特殊的要求,但计算方式和控制结构比较复杂,难以用纯硬件实现。

因此,实时信号处理系统是对运算速度要求高、运算种类多的综合性信息处理系统。

1信号处理系统的类型与常用处理机结构根据信号处理系统在构成、处理能力以及计算问题到硬件结构映射方法的不同,将现代信号处理系统分为三大类:·指令集结构(ISA)系统。

在由各种微处理器、DSP处理器或专用指令集处理器等组成的信号处理系统中,都需要通过系统中的处理器所提供的指令系统(或微代码)来描述各种算法,并在指令部件的控制下完成对各种可计算问题的求解。

·硬连线结构系统。

主要是指由专用集成电路(ASIC)构成的系统,其基本特征是功能固定、通常用于完成特定的算法,这种系统适合于实现功能固定和数据结构明确的计算问题。

不足之处主要在于:设计周期长、成本高,且没有可编程性,可扩展性差。

·可重构系统。

基本特征是系统中有一个或多个可重构器件(如FPGA),可重构处理器之间或可重构处理器与ISA结构处理器之间通过互连结构构成一个完整的计算系统。

从系统信号处理系统的构成方式来看,常用的处理机结构有下面几种:单指令流单数据流(SISD)、单指令流多数据流(SIMD)、多指令流多数据流(MIMD)。

基于DSP和FPGA的通用数字信号处理系统设计

p e r f o r m d a t a p r o c e s s i n g a n d a c c o mp l i s h t h e c o n t r o l o f US B i n t e r f a c e,ADC ,DA C,e t c .r e s p e c t i v e l y .Th e s y s t e m c a n i m— p l e me n t s p e c t r a l a n a l y s i s ,d i g i t a l f i l t e r d e s i g n a n d o t h e r c l a s s i c d i g i t a l s i g n a l p r o c e s s i n g a l g o r i t h ms .Ha r d wa r e d e b u g r e —

Ab s t r a c t :I n n o wa d a y s ,t h e f u n c t i o n a n d s t r u c t u r e o f e l e c t r o n i c e q u i p me n t a r e b e c o mi n g i n c r e a s i n g l y c o mp l i c a t e d .Th e r e —

s u h s s u g g e s t t h a t i t me e t s t h e d e s i g n r e q u i r e me n t s , a n d c o u l d b e i mp l e me n t e d t o r e a l p r o j e c t a n d d i g i t a l s i g n a l p r o c e s s i n g

基于DSP+FPGA的数字信号处理系统设计

。

尤 其是 数据 传输 和运 算 速 度方 面 ,虽 然采 用 并 用 ,数 百万 门高 密度 的F G 问 世 ,新 型 的F G 采 PA PA

行 处理技 术 可 以提 高 系统 的运 算速 度 ,但是 并行 处 用 了大量 的新技 术 更加适 应 于信 号处理 的实 现 。归

理 使得 数据 传输 率 大大 提 高 ,D P 身 同定 的数据 纳起来 具有 如下 特点 : S本 ] 总 线宽度 和高 速数 据传输 的信 号完 整性使 得 并行处

[ 日 2 0 — 2 2 收稿 期] 7 1- 4 0

() 3 分布式存储器

f 作者简介] 郑伟亮 ( 9 0 ),男 ( 18 一 汉),讲师,E ma : g J zt - iz n w@si—m. lh i r n

维普资讯

第4 期

郑 伟 亮 :基 于 D P F G 的 数 字 信 号 处 理 系统 设 计 s+ P A

等模 块 。用 F G 来 实 现某 些 信 号处 理 算法 可 以很 资 源降低 了2 %。 PA 5

好地解 决并行 性和 运算 速度 问题 ,而且 其灵 活性 , 使 得 F G 构 成 的 系统 非常 易 于修 改 、易于 测 试及 PA ( 高速 I 接 口 2) / O 新 型F GA 件具 有上 百 个接 收 器 和发 送 器通 P 器

维普资讯

第5 第4 卷 期

2 0 年 l月 07 2

深圳信息职业技术学院学报

V 1 o o.N . 5 4

De . o0 c2 7

基于D P F G 的数字信号处理系统设计 S+P A

郑 伟 亮 ,张 贝 贝

( 深圳信 息职业技 术 学院 应用英语 系 ,广 东 深圳 5 8 2 ) 10 9

基于DSP和FPGA的通用数字信号处理系统设计

2 硬件设计

2.1 DSP设 计

在 TM¥320C6455数 字信 号 处 理 器 中 ,具 有 1.2GHz的频 率 。配 备 了 C64x+数 字 信 号 处 理 器 内核 ,并 且 对 PCI、千 兆 以 太 网控 制 器 、64住 EMIF接 口 、I2C接 口、JTAG 仿 真 接 口、DDR2

拟 ,因而 在 FPGA 并 行 配置 管脚 连 接 CPLD。在 每 个 FPGA 当 中 ,都 对 一路 R¥232接 口 、RS485接 口 、RS422接 口进 行 了应 用 .极 大 的提 升 了系统 的 可扩 展 性 FPGA 通 过 McBSP与 DSP 连 接 .实现 了快速 的数 据 交换 。

1 总体设 计

进 行 发 出 。由 DSP程 序 进 行 数 据 信 号 处 理 ,然后 通过 FPGA 当

在 通 用 数 字 信 号 处 理 系统 当 中 ,主 要 包 括 了外 设 电 路 、 FPGA控 制 电路 、数 字信 号 处理 单 元 等 部 分 。 其 中外 设 电路 主 要 包括 语音 信 号 控 制 电路 、USB接 1 7 电路 、信 号发 生 采 集 电 路 等 部 分 。FPGA 主要 是 对 电路 接 口时 序控 制 功 能加 以 实现 ,同 时 进 行 数 据 的缓 冲 工作 【”。 数 字 信 号 处 理 单 元 ,主 要 是 处 理 数 字 信 号 的 功 能 。在 系统 的运 行 当 中 ,上位 机 选择 数 字 信 号 处 理 功 能 ,通 过 USB接 口 ,向 FPGA 传 送 控 制 命 令 。FPGA 在 对 命 令 进 行 接 收 之 后 .向 DSP进 行 传 输 ,由 DSP针 对 命 令 要 求 来

基于DSP和 FPGA的通用数字信号处理系统设计

基于DSP+FPGA的数字伺服控制器的设计

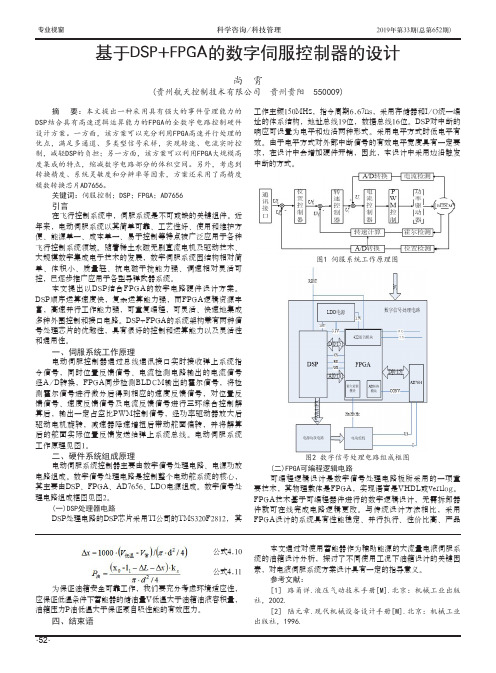

科学咨询/科技管理2019年第33期(总第652期)摘 要:本文提出一种采用具有强大的事件管理能力的DSP结合具有高速逻辑运算能力的FPGA的全数字电路控制硬件设计方案。

一方面,该方案可以充分利用FPGA高速并行处理的优点,满足多通道、多类型信号采样,实现转速、电流实时控制,减轻DSP的负担;另一方面,该方案可以利用FPGA大规模高度集成的特点,缩减数字电路部分的体积空间。

另外,考虑到转换精度、系统灵敏度和分辨率等因素,方案还采用了高精度模数转换芯片AD7656。

关键词:伺服控制;DSP;FPGA;AD7656引言在飞行控制系统中,伺服系统是不可或缺的关键组件。

近年来,电动伺服系统以其简单可靠、工艺性好、使用和维护方便、能源单一、成本单一、易于控制等特点被广泛应用于各种飞行控制系统领域。

随着稀土永磁无刷直流电机及驱动技术、大规模数字集成电子技术的发展,数字伺服系统因结构相对简单、体积小、质量轻、抗电磁干扰能力强、调速相对灵活可控,已逐步推广应用于各型导弹武器系统。

本文提出以DSP结合FPGA的数字电路硬件设计方案。

DSP顺序运算速度快,复杂运算能力强,而FPGA逻辑资源丰富,高速并行工作能力强,可重复编程,可灵活、快速地集成多种外围控制和接口电路。

DSP+FPGA的系统架构兼有两种信号处理芯片的优越性,具有很好的控制和运算能力以及灵活性和通用性。

一、伺服系统工作原理电动伺服控制器通过总线通讯接口实时接收弹上系统指令信号,同时位置反馈信号、电流检测电路输出的电流信号经A/D转换,FPGA同步检测BLDCM输出的霍尔信号,将检测霍尔信号进行微分后得到相应的速度反馈信号,对位置反馈信号、速度反馈信号及电流反馈信号进行三环综合控制解算后,输出一定占空比PWM控制信号,经功率驱动器放大后驱动电机旋转,减速器降速增扭后带动舵面偏转,并将解算后的舵面实际位置反馈发送给弹上系统总线。

电动伺服系统工作原理见图1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图 2 C P U 板结构图 F i . 2 T h e s t r u c t u r e o f C P U c a r d g

其工 P U 板 用 在 一 种 变 频 系 统 控 制 中, 该 C 上位机或 操 控 面 板 通 过 R 作过程如下 : S 2 3 2串口 将变频系统的给定信息传送给 D 同时 , S P, F P GA 将外围 I O 采集到的 系 统 反 馈 信 息 通 过 总 线 也 传 将结果发 送到 D S P, D S P 进 行 数 据 运 算 和 处 理, 送到 F 并产生 P GA, F P GA 实现最终的逻辑控制 , 然后通过 C PWM 波 形 , P U 板 的I O 端口去控制 功率单元组件 。 C P U 板与外部 I O 板点对点的通信是通过板 这相当于将I 内的 F P GA 实 现 的 , O 总线放到 因此容易实现I F P GA 内完 成 , O 资 源 共 享。 对 该控制器支持双 C 于较复杂 的 控 制 系 统 , P U板 协同工作 , 此时 F P GA 具 备 多 口 S R AM 的 功 能 , 它不仅可以实现 板 内 D S P与 F P GA 内 部 资 源 之 同时也支持两个 C 间的 信 息 交 换 , P U 板内的 D S P 之间的通信 。 2. 1 电源 / D S P 的内核电压和外围 I O 电压分别为 1. 9 5 2

本文介绍的通用数字控制器使用数字信号处 理器 D S P 和大规模现场可编程门阵列 F P GA。 复 杂 运 算 能 力 强, 而 D S P 具有顺 序 运 算 速 度 快 , 高速并行工作能力强 , F P GA 具有逻辑资源丰富 , , 、 可重复编程 可灵活 快速地集成多种外围控制和 接口电路 。D S P+F P GA 的系统架构兼有两种 信 号处理芯片的优 越 性 , 使控制器具有很好的控制 和运算能力 , 同时具有很好的灵活性和通用性 。

( 1. T i a n i n D e s i n a n d R e s e a r c h I n s t i t u t e o E l e c t r i c D r i v e, T i a n i n3 0 0 1 8 0, C h i n a; j g f j 2. T i a n i n E n t r x i t I n s e c t i o n a n d Q u a r a n t i n e B u r e a u, T i a n i n3 0 0 4 5 7, C h i n a) j y-E p j : e n e r a l -p u r o s e A b s t r a c t I n o r d e r t o m a k e h a r d w a r e a n d s o f t w a r e o f d i i t a l c o n t r o l l e r s t a n d a r d i z a t i o n g p g , , , m o d u l a r i z a t i o n a n d i m r o v e i t s e r f o r m a n c e o f r e a l t i m e s t a b i l i t a n d a n t i -i n t e r f e r e n c e t h e h a r d w a r e a n d p p y , d e s i n w a s d e s c r i b e d b a s e d o n D S P+ F P GA d i i t a l c o n t r o l l e r a n d i l l u s t r a t e d t h e d e s i n o f e n e r a l -p u r o s e g g g g p , , a n d m a i n C P U b o a r d o w e r m a n a e m e n t c i r c u i t e r i h e r a l d e s i n o f d i i t a l s i n a l r o c e s s o r a n d c o n t r o l l e r p g p p g g g p , c o n f i u r a t i o n c i r c u i t b u s d r i v e r c i r c u i t o f f i e l d r o r a mm a b l e a t e a r r a i n d e t a i l . T h e c o r r e c t n e s s a n d r e l i a b i l - g p g g y i t o f h a r d w a r e d e s i n a r e v e r i f i e d t h r o u h a l i c a t i o n . r a c t i c a l y g g p p p : ; ; e n e r a l -p u r o s e r o c e s s o r s( r o r a mm a b l e a t e K e w o r d s d i i t a l c o n t r o l l e r d i i t a l s i n a l D S P) f i e l d g p p p g g g g g y ; ; a r r a o w e r F P GA) m a n a e m e n t b u s y( p g

E L E C T R I C D R I V E 2 0 1 1 V o l . 4 1 N o . 3

电气传动 2 0 1 1 年 第4 1 卷 第3 期

基于 D S P-F P GA 的通用数字控制器硬件设计

D e s i n o f G e n e r a l -p D i i t a l C o n t r o l l e r B a s e d D S P-F P G A u r o s e g g p

1 1 2 , WANG S h o u - l i YUAN Y u a n YU B o ,

王首礼1 , 袁媛1 , 于波2 ( 天津 3 1.天津电气传动设计研究所 , 0 0 1 8 0; , ) 2.天津出入境检验检疫局 天津 3 0 0 4 5 7

为了使通用数字控制器的 硬 件 电 路 与 软 件 程 序 标 准 化 和 模 块 化 , 提 高 数 字 控 制 器 的 实 时 性、 稳定 摘要 : 性、 抗干扰性 , 介绍了一种基于 D 对控制器及主 C S P+F P GA 系统架构的 通 用 数 字 控 制 器 硬 件 设 计 , P U 板的 设计方案 、 主C 数字信号处理器 D 现场可编程门阵列 F P U 板上的电源管理电路 、 S P 及其外围设计 、 P GA 的配 总线驱动电路作了详细说明 。 实际应用验证了该数字控制器硬件设计的正确性和可靠性 。 置电路 、 关键词 : 通用数字控制器 ; 数字信号处理器 ; 现场可编程门阵列 ; 电源管理 ; 总线 中图分类号 : T P 2 3 文献标识码 : A

辅助电压和外围 3V, F P GA 的 内核电压、 V 和 3. / I O 电压分别为1 . 2V, 3 . 3V 和 3 . 3V, F P G A 的配 / 置芯片内核电压和外 围 I O 电压分别为1 . 8V 和 因此, 系统中 需 要 4 种 电 源。TM 3 . 3V, S 3 2 0 F 2 8 1 2 供电需要先给外围 3. 再接 3V 的 电 源 引 脚 上 电 , 通 1. 当外围电压上升到 9V 的 芯 片 内 核 电 源 ; 内核 电 压 才 上 升 到 0. 这样能保证 2. 5V 时 , 3V, 片内各个模 块 上 电 时 能 正 确 复 位 。 而 掉 电 时 , 在 1. 9V 的电 压 达 到 1. 5V 之 前 器 件 复 位 将 变 [ 2] 低 。 如果 TMS 3 2 0 F 2 8 1 2上 下 电 时 不 能 满 足 上 影响器件 述要求则可能导 致 输 出 端 出 现 大 电 流 , 寿命 甚 至 损 坏 器 件 , 所 以 需 要 考 虑 供 电 顺 序; 而 S a t a n 3 系列 F P GA 及其配置芯片可以同时上下 p / 电, C 电源模块的 通过资料查阅和仿真 T r a c k 引脚来 实 现 。 同 时 , 估计 , 因此本 1. 2V, 3. 3V 所需要的电流比较 大 , / 设计 选 用 T I 公 司 的 D C D C 电 源 模 块 如图3所 P TH 0 8 T 2 3 0 提 供 1. 2V, 3. 3V 电 压 , 示, L D O 电源芯片 T P S 7 4 8 0 1, T P S 7 3 1 1 8提供 分别如图 4、 图 5 所示 。 1. 9V, 1. 8V 电压 ,

1 设计方案

如图 1 所示 , 本数字控制器采用标准6 U欧 式插卡结构 , 由 8 个槽组成 , 第 1# , 5# 槽为 C P U 板插槽 , 其余 6 个槽为I O 板插槽 。 可以支持 2 套

, : 王首礼 ( 男, 高级工程师 , 1 9 5 3- ) E m a i l w a n s h o u l i t r i e d . c o m. c n 作者简介 : @ g 图 1 控制器结构图 F i . 1 T h e s t r u c t u r e o f c o n t r o l l e r g

实时控制系统分为模拟控制系统和数字控制 系统两大类 , 随着数字技术的发展 , 模拟控制系统

1] 。 已经逐步被取代 [

控制系统并行工作 , 2个 C P U 板之间通过点 到 点 的数据 、 地址和控制总线进行通信 , 其中数据总线 地址总线1 寻 址 范 围: 1 6 位, 2位( 0 X 0 0 0 0~ ) , 、 、 、 控制 总 线 包 括 时 钟 复 位 读 数 据 写 0 X 0 F F F 数据 、 中断等 。C P U 板 到I O 板也采用点对点的 通信方式 , 通 过I 开关量输 O 板与外围 A D, D A, 入, 开关量输 出 等 各 种 功 能 单 元 连 接 ; C P U 板也 自带 I 可以与功率单元相连 。 O 端口 ,