eda期中试卷

eda期中试卷

《EDA技术》期中测试一、选择题(每小题2分,共计20分。

)1、VHDL语言共支持四种常用库,其中哪种库是用户的VHDL设计当前工作库()。

A.IEEE库B.VITAL库C.STD库D.WORK工作库2、VHDL的process进程语句是并行语句,它的内部是由( )语句构成的A. 并行语句和顺序语句B.顺序语句C.并行语句D.任意语句3、元件例化语句的作用是()。

A.描述元件模块的算法B.改善并行语句及其结构的可读性C.产生一个与某元件完全相同的一组并行元件D.在高层次设计中引用前面已经设计好的元件或电路模块4、在VHDL的并行语句之间,可以用( )来传递信息。

A.常量(Constant)B.变量(Variable)C.信号(Signal)D.变量和信号5、以下关于VHDL中常量的声明正确的是()。

A.Constant delay :Integer = 8B.Constant delay:Integer := 8C.Variable delay:Integer = 8D.Variable delay:Integer := 86、在VHDL语言中,下列对时钟边沿检测描述中,错误的是( )。

A. if clk’event and clk = ‘1’ thenB. if rising_edge(clk) thenC. if clk’event and clk = ‘0’ thenD.if clk’stable and not clk = ‘1’ then7、下列关于VHDL标识符的说法正确的是()(多选)A.标识符由26个英文字母和数字0~9以及下划线组成,其中字母不区分大小写。

B.标识符必须由英文字母开始,不连续使用下划线,且不能以下划线结束,C.标识符中可以包含空格D.标识符不允许与VHDL中的关键字重合8、下列对FPGA结构与工作原理的描述中,正确的是( )。

A.FPGA全称为复杂可编程逻辑器件B.FPGA是基于乘积项结构的可编程逻辑器件C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置D.在Altera公司生产的器件中,MAX7000系列属FPGA结构9、在VHDL中,关于变量与信号的区别,下列说法不正确的是()。

(完整版)EDA历年试卷答案

附表二:武汉工业学院课程考核试题参考答案及评分标准学年:2007-2008一、简答题(25分,共5小题,每小题5分)1.一个完整的VHDL语言程序通常包括以下5个部分:(每条1’)实体说明(Entity):定义电路实体的外观:I/O接口的规格;结构体(Architecture):描述电路的内部功能;配置(Configuration):决定采用哪一个结构体;程序包(Package):定义使用哪些自定义元件库;库(Library):定义元件库。

2.主要从以下几方面进行选择:(每条1’)(1)逻辑单元:CPLD适用于逻辑型系统,FPGA适用于数据型系统。

(2)内部互连资源与连线结构:CPLD适用于实现有限状态机,FPGA适用于实现小型化、集成化。

(3)编程工艺:CPLD采用EPROM结构,内部逻辑一经编程后还会以丢失,FPGA采用RAM型编程,是易失性器件,需与配置芯片配合使用。

(4)规模:中小规模电路设计可采用CPLD,大规模逻辑电路的设计采用FPGA。

(5)封装形式:小规模电路:PLCC,引脚数量大的系统宜选用SMD的TQFP、PQFP、BGA等封装形式。

3. MAX+PLUSII的设计流程如下:(每步1’)(1)设计输入(2)设计检查(3)设计编译(4)时序/功能仿真(5)定时分析注:用流程框图表示也算回答正确。

4. 这个过程可以分为:(1)系统性能描述与行为模拟:设计从系统的功能和性能要求开始。

(2)系统结构分解:将系统分解为若干子系统,子系统又可以再分解为若干功能模块。

(3)产生系统结构模型:(4)描述叶子模块:用数据流进行描述(5)逻辑综合与设计实现:针对给定硬件结构组件进行编译、优化、转换和综合,最终获得门级电路甚至更底层的电路描述文件。

5.顺序语句:特点:在程序执行时,按照语句的书写顺序执行,前面的语句的执行结果可能直接影响后面语句的执行。

(1’)用途:主要用于模块的算法部分,用若干顺序语句构成一个进程或描述一个特定的算法或行为。

最新08届eda期中试卷A及答案资料

2A.用Q1,Q2,D信号要好些。

未标信号扣5分D<= X or Q1; 放在时钟上升沿里扣5分4A. 信号用counter好些用变量或信号,用integer或std_logic_vector型3A. 图最好选用答案的图用变量或信号,用integer或std_logic_vector型6A.实体名不允许为JKFFIf prn写在外面扣5分or 写成加号扣5分7A:程序 A B赋高阻5分,A<=B, B<=A, 无分图10分.1A.简述信号与变量的区别。

(至少列举5个)答案:1 赋值符号不同信号用 <= 变量用 :=2 功能不同信号常常是物理硬件的节点变量用来描述算法3 信号是全局量,用于结构体,实体,块中变量是局部量,用于进程,函数,子程序4 信号的赋值需要有δ延时变量是立即赋值5 进程中的敏感表只能是信号2A. 用VHDL描述下面电路图。

(实体名用cir1)答案:library IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CIR1 ISPORT ( X, CLK : IN STD_LOGIC;Y : OUT STD_LOGIC);END ;ARCHITECTURE ONE OF CIR1 ISSIGNAL A, B, C: std_logic;BEGINB <= not (X OR A) ;PROCESS (CLK)BEGINIF CLK'EVENT AND CLK = '1' THENA <= C ;C <= B;END IF;END PROCESS;Y <= C;END ONE;3A. 频率计控制电路的工作波形如图所示,试用VHDL设计该电路。

(注意时钟信号的下降沿有效) (实体名用tfctrl)答案:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity tfctrl isport(clk:in std_logic;en,lock,clear: out std_logic);end ;architecture bhv of tfctrl issignal temp: std_logic_vector(3 downto 0);beginprocess(clk) beginif falling_edge(clk) thenif temp<15 then temp<=temp+1; else temp<="0000";end if;if temp<8 then en<='1'; else en<='0'; end if;if temp=9 then lock<='1'; else lock<='0';end if;if temp=13 then clear<='1'; else clear<='0';end if;end if;end process;end ;答案2: 用case语句library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity tfctrl isport(clk:in std_logic;en,lock,clear: out std_logic);end ;architecture bhv of tfctrl issignal temp: integer range 15 downto 0;beginprocess(clk) beginif falling_edge(clk) thenif temp<15 then temp<=temp+1; else temp<=0;end if;case temp iswhen 0 to 7 => en<='1'; lock<='0'; clear<='0';when 9 => en<='0'; lock<='1'; clear<='0';when 13 => en<='0'; lock<='0'; clear<='1';when others => en<='0'; lock<='0'; clear<='0';end case;end if;end process;end ;4A. 试用VHDL设计一个六分频电路,要求50%的占空比。

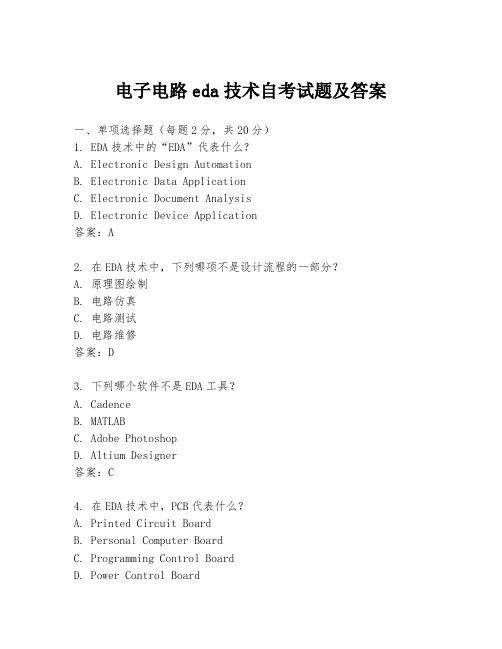

电子电路eda技术自考试题及答案

电子电路eda技术自考试题及答案一、单项选择题(每题2分,共20分)1. EDA技术中的“EDA”代表什么?A. Electronic Design AutomationB. Electronic Data ApplicationC. Electronic Document AnalysisD. Electronic Device Application答案:A2. 在EDA技术中,下列哪项不是设计流程的一部分?A. 原理图绘制B. 电路仿真C. 电路测试D. 电路维修答案:D3. 下列哪个软件不是EDA工具?A. CadenceB. MATLABC. Adobe PhotoshopD. Altium Designer答案:C4. 在EDA技术中,PCB代表什么?A. Printed Circuit BoardB. Personal Computer BoardC. Programming Control BoardD. Power Control Board答案:A5. VHDL是一种用于什么目的的硬件描述语言?A. 软件编程B. 电路设计C. 数据库管理D. 图像处理答案:B二、多项选择题(每题3分,共15分)1. 下列哪些是EDA技术的优势?A. 提高设计效率B. 减少设计错误C. 降低设计成本D. 增加设计复杂性答案:ABC2. 在EDA技术中,以下哪些步骤是设计流程的一部分?A. 原理图绘制B. 电路仿真C. 电路测试D. 电路维修答案:ABC3. 下列哪些是常见的EDA工具?A. CadenceB. MATLABC. Adobe PhotoshopD. Altium Designer答案:ABD三、填空题(每题2分,共10分)1. 在EDA技术中,______是用于描述数字电路行为的一种语言。

答案:VHDL2. EDA技术可以用于设计______、模拟电路和混合信号电路。

答案:数字电路3. PCB设计中,______是用于连接电子元件的导电路径。

EDA期中测试题

1、在横线上填入合适的语句完成D触发器的设计。

library ieee;use ieee.std_logic_1164.all;entity d_flip isport(d, clk: in std_logic;);end d_flip;architecture rtl of d_flip isbeginprocess( )beginif then;;end process;end rtl;2、在横线上填入合适的语句完成2输入或非门的设计。

library ieee;use ieee.std_logic_1164.all;nor2 isport(a,b:in std_logic;y:out std_logic);end nor2;architecture behave of isbegin;end behave;3、已知电路原理图如下,请用一个process和两个process两种方式完成程序设计P1344、已知电路原理图如下,请用VHDL完成程序设计P1345、设计一个带有异步清零功能的十进制计数器。

计数器时钟clk上升沿有效、清零端CLRN、进位输出co。

6、阅读下列VHDL程序,画出相应RTL图LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY TRIS ISPORT ( CONTROL : IN STD_LOGIC;INN : IN STD_LOGIC;Q : INOUT STD_LOGIC;Y : OUT STD_LOGIC );END TRIS;ARCHITECTURE ONE OF TRIS ISBEGINPROCESS (CONTROL, INN, Q)BEGINIF (CONTROL = '0') THENY <= Q;Q <= 'Z';ELSEQ <= INN;Y <= 'Z';END IF;END PROCESS;END ONE;。

eda原理及应用试题及答案

eda原理及应用试题及答案一、选择题(每题2分,共20分)1. EDA(Electronic Design Automation)的中文意思是:A. 电子设计自动化B. 电子文档自动化C. 电子数据自动化D. 电子设备自动化答案:A2. EDA技术不包括以下哪一项:A. 电路仿真B. PCB设计C. 电子制图D. 硬件描述语言答案:C3. 在EDA中,HDL指的是:A. 高级数据链接B. 高级设计语言C. 硬件描述语言D. 硬件开发语言答案:C4. 下列哪个不是EDA软件工具的功能:A. 逻辑综合B. 布局布线C. 代码编译D. 时序分析答案:C5. 在EDA中,用于描述数字逻辑电路行为的HDL是:A. VerilogB. VHDLC. C语言D. Java答案:A6. EDA技术在以下哪个领域应用最为广泛:A. 软件开发B. 机械设计C. 电子设计D. 建筑设计答案:C7. 以下哪个不是EDA工具所支持的仿真类型:A. 功能仿真B. 时序仿真C. 物理仿真D. 行为仿真答案:C8. 在EDA设计流程中,通常最后进行的步骤是:A. 逻辑综合B. 布局布线C. 编译D. 测试答案:D9. 以下哪个不是EDA设计流程中的步骤:A. 需求分析B. 逻辑设计C. 电路测试D. 市场调研答案:D10. EDA技术可以提高以下哪方面的效率:A. 电路设计B. 产品销售C. 客户服务D. 物流管理答案:A二、填空题(每题2分,共20分)1. EDA技术的核心是______,它允许设计师在没有实际硬件的情况下对电路进行测试和验证。

答案:仿真2. 在EDA中,______是一种高级的编程语言,用于描述和设计电子系统。

答案:硬件描述语言3. 逻辑综合是将______转换为门级网表的过程。

答案:HDL代码4. PCB设计中,EDA工具可以帮助设计师进行______和______。

答案:布局;布线5. 时序分析是确保电路在规定的______内正确工作的分析。

最新EDA试卷及答案资料

EDA试卷及答案一、单项选择题:(20分)1.IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为_____ D_____。

A .瘦IP B.固IP C.胖IP D.都不是2.综合是EDA设计流程的关键步骤,在下面对综合的描述中,____ D _____是错误的。

A.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D.综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

3.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是__C__。

A. FPGA全称为复杂可编程逻辑器件;B. FPGA是基于乘积项结构的可编程逻辑器件;C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

4.进程中的信号赋值语句,其信号更新是___C____。

A.按顺序完成;B.比变量更快完成;C.在进程的最后完成;D.都不对。

5. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述_____B______。

A.器件外部特性;B.器件的内部功能;C.器件的综合约束;D.器件外部特性与内部功能。

6.不完整的IF语句,其综合结果可实现____ A ____。

A. 时序逻辑电路B. 组合逻辑电路C. 双向电路D. 三态控制电路7.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化_____ B____。

①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法A. ①③⑤ B. ②③④C. ②⑤⑥ D. ①④⑥8.下列标识符中,_____B_____是不合法的标识符。

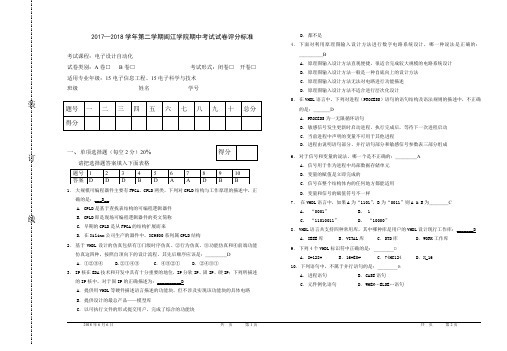

2017-2018-2学期EDA期中考试试卷含答案

适用专业年级:15 电子信息工程、15 电子科学与技术 班级 姓名 学号

装

题号 得分

一二三四五六七八

九

十

总分

的是:_______D A.PROCESS 为一无限循环语句 B.敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动 C.当前进程中声明的变量不可用于其他进程 D.进程由说明语句部分、并行语句部分和敏感信号参数表三部分组成

(1)答:第 9 行, 原因:状态机数据类型声明错误,关键字应为 TYPE (2)答:第 32 行,原因:case 语句缺少 when others 处理异常状态情况 2.修改相应行的程序(如果是缺少语句请指出大致的行数) : 错误 1 错误 2 行号: 9 行号: 32 程序改为:SIGNAL 改为 TYPE 程序改为:之前添加一句 when others => c_st <= st0;

共 页 第4页

五、VHDL 程序设计 50 %

1.设计一个 3-8 译码器 10 分 输入端口: DIN EN 输出端口: DOUT 解: 输入端,位宽为 3 位 译码器输出使能,高电平有效 译码器输出,低电平有效

得分

2.设计一个分频器,分频数为 16 分频,要求输出波形的高低电平维持时间相同。 10 分

得分

-----------------------------------1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35

1. ASIC 设计中可以采用半定制法,按逻辑实现方式的不同,半定制法可再分为 自顶向下 的方法已经是 EDA 技术的首选设计方法,是 ASIC 或 FPGA 开发的主要设 两种类型。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《EDA技术》期中测试一、选择题(每小题2分,共计20分。

)1、VHDL语言共支持四种常用库,其中哪种库是用户的VHDL设计当前工作库()。

A.IEEE库B.VITAL库C.STD库D.WORK工作库2、VHDL的process进程语句是并行语句,它的内部是由( )语句构成的A. 并行语句和顺序语句B.顺序语句C.并行语句D.任意语句3、元件例化语句的作用是()。

A.描述元件模块的算法B.改善并行语句及其结构的可读性C.产生一个与某元件完全相同的一组并行元件D.在高层次设计中引用前面已经设计好的元件或电路模块4、在VHDL的并行语句之间,可以用( )来传递信息。

A.常量(Constant)B.变量(Variable)C.信号(Signal)D.变量和信号5、以下关于VHDL中常量的声明正确的是()。

A.Constant delay :Integer = 8B.Constant delay:Integer := 8C.Variable delay:Integer = 8D.Variable delay:Integer := 86、在VHDL语言中,下列对时钟边沿检测描述中,错误的是( )。

A. if clk’event and clk = ‘1’ thenB. if rising_edge(clk) thenC. if clk’event and clk = ‘0’ thenD.if clk’stable and not clk = ‘1’ then7、下列关于VHDL标识符的说法正确的是()(多选)A.标识符由26个英文字母和数字0~9以及下划线组成,其中字母不区分大小写。

B.标识符必须由英文字母开始,不连续使用下划线,且不能以下划线结束,C.标识符中可以包含空格D.标识符不允许与VHDL中的关键字重合8、下列对FPGA结构与工作原理的描述中,正确的是( )。

A.FPGA全称为复杂可编程逻辑器件B.FPGA是基于乘积项结构的可编程逻辑器件C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置D.在Altera公司生产的器件中,MAX7000系列属FPGA结构9、在VHDL中,关于变量与信号的区别,下列说法不正确的是()。

A.信号用于作为进程中局部数据存储单元B.在进程中,对信号赋值在进程结束时起作用;对变量的赋值则是立即生效C.信号在整个结构体内的任何地方都能适用D.变量和信号的赋值符号不一样E.信号声明在子程序或进程的外部;而变量的声明在子程序或进程的内部10、在元件例化(COMPONENT)语句中,用( )符号实现名称映射,将例化元件的端口名与连接的信号名关联起来。

A. =B.:=C.<=D.=>二、名词解释,写出下列缩写的中文(或者英文)含义(每小题2分,共计10分。

)1、FPGA2、VHDL3、时序仿真4、RTL5、LUT三、简答题(每小题5分,共计10分。

)1、VHDL程序一般包含几个组成部分?每个部分的作用是什么?2、并行信号赋值语句有几类?比较其异同。

四、程序填空(每小题10分,共计20分。

)1、这是一个带有异步清零和使能端的在时钟脉冲上升沿触发的100进制计数器。

试解释相关的语句。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all ; ①entity cnt100b isport( c lk, rst, en : in std_logic;cq : out std_logic_vector(7 downto 0); -- 计数输出cout: out std_logic); -- 进位输出end entity cnt100b;architecture bhv of cnt100b isbeginprocess (clk, rst, en) isvariable cqi : std_logic_vector(7 downto 0); ③beginif rst = '1' thencqi := (others=> '0'); ④elseif clk’event and clk=’1’then⑤if en = '1' thenif cqi(3 downto 0) < "1001" thencqi:= cqi+1;elseif cqi(7 downto 4) < "1001" thencqi := cqi + 16; ⑥elsecqi := (others => '0'); ⑦end if;cqi(3 downto 0):= (others => '0'); ⑧end if;end if;cq <=cqi; ⑨end if;if cqi = “10011001”then ⑩cout <= '1';elsecout <= '0';end if;end if;end process;end architecture bhv;2、下面程序是8位分频器电路的VHDL描述,试补充完整。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE. ___________ .ALL;ENTITY PULSE ISPORT ( CLK : IN STD_LOGIC;D : IN ___________ (7 DOWNTO 0);FOUT : OUT STD_LOGIC );END ENTITY PULSE;ARCHITECTURE one OF ___________ ISSIGNAL FULL : STD_LOGIC;BEGINP_REG: PROCESS(CLK)___________CNT8 : STD_LOGIC_VECTOR(___________ DOWNTO 0);BEGINIF ___________ THENIF CNT8 = "11111111" THENCNT8 ___________ ; --当CNT8计数计满时,输入数据D被同步预置给计数器CNT8FULL <= '1'; --同时使溢出标志信号FULL输出为高电平ELSE CNT8 ___________ ; --否则继续作加1计数FULL <= '0'; --且输出溢出标志信号FULL为低电平END IF;END IF;END PROCESS P_REG;P_DIV: PROCESS( ___________ )V ARIABLE CNT2 : STD_LOGIC;BEGINIF FULL'EVENT AND FULL = '1' THENCNT2 ___________ ; --如果溢出标志信号FULL为高电平,D触发器输出取反IF CNT2 = '1' THEN FOUT <= '1';ELSE FOUT <= '0';END IF;END IF;END PROCESS P_DIV;END;五、程序改错(共计10分。

)请仔细阅读七段译码显示器程序,找出错误语句,并给出正确的语句。

1 library ieee;2 use ieee.std_logic_1164.all;3 entity decoder47 is4 port(lt,ibr,ib_ybr:in bit;5 a: in std_logic_vector(3 downto 0);6 y:out std_logic_vector(6 downto 0););7 end decoder47;8 architecture art of decoder is9 begin10 process(lt,ibr,ib_ybr,a)11 signal s: std_logic_vector(3 downto 0);12 begin13 s<=a(3)&a(2)&a(1)&a(0);14 if lt='0' and ib_ybr='1' then15 y<="1111111"; --检查七段显示管是否正常16 elsif ibr='0' and a="0000" then17 y<="0000000";18 else19 case s is20 when"0000"=>y<="1111110"; --7E21 when"0001"=>y<="0110000"; --3022 when"0010"=>y<="1101101"; --6D23 when"0011"=>y<="1111001"; --7924 when"0100"=>y<="0110011"; --3325 when"0101"=>y<="1011011"; --5B26 when"0110"=>y<="0011111"; --5F27 when"0111"=>y<="1110000"; --7028 when"1000"=>y<="1111111"; --7E29 when"1001"=>y<="1110011"; --7B30 when"1010"=>y<="0001101"; --0D31 when"1011"=>y<="0011001"; --1932 when"1100"=>y<="0100011"; --2332 when"1101"=>y<="1001011"; --4B33 when"1110"=>y<="0001111"; --0F34 when"1111"=>y<="0000000";35 when others=>null;36 end case;37 end if;38 end process;39 end behav;六、程序设计(共计30分。