实验报告-有限状态机for11.6

实验3有限状态机

结果评估

根据实验目标和数据分析结果,对实现的有限状态机进行评估。评估指标可以包括功能完整性、性能效 率、可扩展性等。通过评估,我们可以了解实现的效果如何,以及需要改进的地方。

与流程图的区别

流程图描述的是一系列的决策和转移, 而有限状态机强调的是系统的状态和 状态之间的转换。

与数据结构模型的区别

与模拟器的区别

模拟器用于模拟系统的行为,而有限 状态机是一种用于描述系统行为的计 算模型。

有限状态机不仅关注数据结构,更关 注状态之间的转移逻辑和行为。

02 有限状态机的实现方式

THANKS FOR WATCHING

感谢您的观看

不足

在实验过程中,我们发现自己在有限状态机的设计和实现上还存在一些不足之处。例如,在状态转移逻辑的设计 上,我们有时会忽略一些重要的状态转移条件,导致程序运行结果不正确。此外,在代码实现方面,我们也存在 一些语法错误和逻辑错误,需要进一步加强代码审查和测试。

对未来研究的建议与展望

要点一

建议

为了进一步提高有限状态机的应用效果和性能,我们建议 在未来的研究中,可以从以下几个方面进行改进。首先, 深入研究有限状态机的设计方法和技巧,提高状态转移逻 辑的准确性和可靠性。其次,加强有限状态机的测试和验 证,及时发现和修复程序中的错误和问题。最后,探索有 限状态机在其他领域的应用,如人工智能、游戏开发等。

04 实验结果与讨论

结果展示

状态转移图

根据实验数据,绘制了有限状态机的状态转移图, 清晰地展示了各个状态之间的转移关系。

有限状态机(FSM)的设计

begin

state<=B;z=0;

end

else

state<=IDLE;

B:if(x==1)

begin

state<=C;z=0;

end

else

state<=IDLE;

C:if(x==1)

begin

state<=D;z=1;

end

else

state<=IDLE;

D:if(x==1)

实验报告四

有限状态机(FSM)的设计

1、实验目的

1、了解FSM的应用范围和两种类型的不同特点;

2、掌握FSM的电路结构和设计特点。

二.实验内容

设计一个串行数据检测器,连续4个或4个以上的1时输出为1,其他情况下输入情况为0,编写测试模块并给出仿真波形

三、实验步骤

1.程序编程

module ceshi(x,z,clk,rst,clk1);

#500 $stop;

end

ceshi m(x,z,rst,clk1);

Endmodule

3.对应引脚

4仿真结果

input x,clk,rst;

output z;

reg z;

output clk1;

reg clk1;

reg[2:0] state;

reg [27:0] n;

parameter IDLE='d0,A='d1,B='d2,C='d3;

always@(posedge clk)

begin

if (n==24999999)

wire x,z,clk1;

assign x=data[23];

有限状态机设计

CASE Q IS WHEN 0=> IF DIN = D(7) THEN Q <= 1 ; ELSE Q <= 0 ; END IF ; WHEN 1=> IF DIN = D(6) THEN Q <= 2 ; ELSE Q <= 0 ; END IF ; WHEN 2=> IF DIN = D(5) THEN Q <= 3 ; ELSE Q <= 0 ; END IF ; WHEN 3=> IF DIN = D(4) THEN Q <= 4 ; ELSE Q <= 0 ; END IF ; WHEN 4=> IF DIN = D(3) THEN Q <= 5 ; ELSE Q <= 0 ; END IF ; WHEN 5=> IF DIN = D(2) THEN Q <= 6 ; ELSE Q <= 0 ; END IF ; WHEN 6=> IF DIN = D(1) THEN Q <= 7 ; ELSE Q <= 0 ; END IF ; WHEN 7=> IF DIN = D(0) THEN Q <= 8 ; ELSE Q <= 0 ; END IF ; WHEN OTHERS => Q <= 0 ; END CASE ; END IF ; END PROCESS ; PROCESS( Q ) BEGIN IF Q = 8 THEN AB <= "1010" ; ELSE AB <= "1011" ; END IF ; END PROCESS ;END behav ;

实验四_有限状态机设计(2学时)

实验四有限状态机设计(2学时)实验内容一:状态机是指用输入信号和电路状态(状态变量)的逻辑函数去描述时序逻辑电路功能的方法,也叫时序机。

有限状态机是指在设计电路中加入一定的限制条件,一般用来实现数字系统设计中的控制部分。

根据时序电路输出信号的特点可将时序电路划为Mealy 型和Moore 型两种。

Moore型电路中,输出信号仅仅取决于存储电路的状态。

Mealy型电路中,输出信号不仅取决于存储电路的状态,而且还取决于输入变量。

图1是某Mealy型电路的状态转换图,图中圆圈内的S0、S1等代表电路的状态,状态转换箭头旁斜杠“/”上边的数字代表输入信号,斜杠“/”下边的数字代表输出信号。

假设电路的当前状态为S0,当输入信号为0时,电路的下一个状态仍为S0,输出信号为0;当输入信号为1时,电路的下一个状态为S1,输出为1。

图1 Mealy状态机下面的程序中使用两个进程来描述该状态机。

第一个进程负责状态转化,在CP上升沿到达时,当前状态(PresetState)向下一个状态(NextState)的转换;第二个进程负责检测输入信号(DIN)和当前状态(PresetState)的值,并由CASE-WHEN 语句决定输出信号(OP)和下一个状态值(NextState)的值。

请补充下图中虚线“…”部分省略掉的程序,然后对完整程序进行编译,并用Tools->Netlist Views->State Machine Viewer和RTL Viewer工具查看该状态机的状态图和RTL顶层图。

……实验内容二:论文《基于VHDL的一个简单Mealy状态机》中设计了一个Mealy状态机用来检测数据流“1101010”,用以验证状态机在数据检测上的应用。

请在读懂文中程序的基础上,在Quartus Ⅱ软件中通过编译仿真得到状态图和波形图,仿真中输入波形的设置应能体现该状态机的用途。

实验报告:本次实验占用两个学时,请于12周周四(5月12日)上课时交实验报告。

有限状态机课程设计报告EDASodaMachine自动售货机

1有限状态机有限状态机(Finite State Machine )是一种具有内部记忆的抽象机器模型,是时序电路的一种,通过有限状态机课实现高效率高可靠逻辑控制。

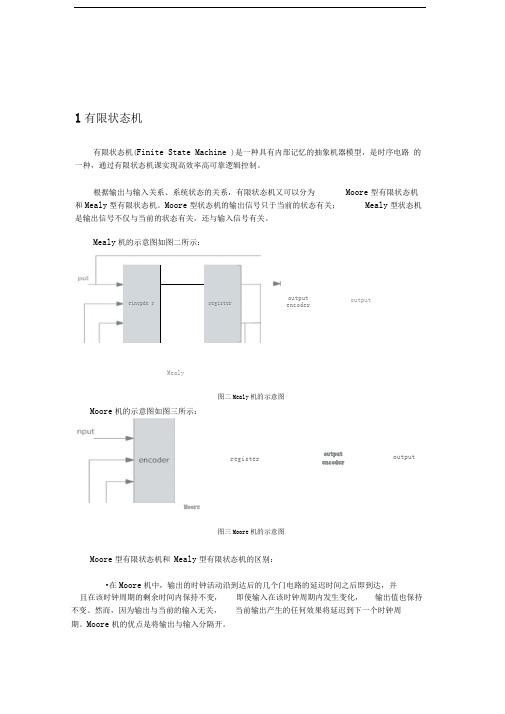

根据输出与输入关系、系统状态的关系,有限状态机又可以分为Moore型有限状态机和Mealy型有限状态机。

Moore型状态机的输出信号只于当前的状态有关;Mealy型状态机是输出信号不仅与当前的状态有关,还与输入信号有关。

Mealy机的示意图如图二所示:Mealy图二Mealy机的示意图Moore机的示意图如图三所示:Moore图三Moore机的示意图Moore型有限状态机和Mealy型有限状态机的区别:•在Moore机中,输出的时钟活动沿到达后的几个门电路的延迟时间之后即到达,并且在该时钟周期的剩余时间内保持不变,即使输入在该时钟周期内发生变化,输出值也保持不变。

然而,因为输出与当前的输入无关,当前输出产生的任何效果将延迟到下一个时钟周期。

Moore机的优点是将输出与输入分隔开。

einepde r registeroutputencoderoutputregisteroutputencoderoutput• 在Mealy 机中,因为输出是输入的函数,如果输入改变,则输出可以在下一个时钟周期的中间发生改变。

这使得Mealy 机比Moore 机,对输入变化的响应要早一个时钟周期,一旦输入信号或状态发生变化,输出信号随着输入信号变化。

• 实现同样功能,Moore 机要比Mealy 机需要更多的状态。

通过分析本次实验,利用Mealy 机更加容易理解,并且使用Moore 会使用更多的状态,所以本次实验使用Mealy 型有限状态机。

2 Soda Machine机的设计2.1 Soda Machine机的状态转换图Soda Machine 机的状态转换图如图四所示。

Soda Machine图四Soda Machine 机的状态转换图图中共有10个状态,为ST0 — ST9。

有现状态机设计实验报告

湖南科技学院综合设计性实验报告实验名称:有限状态机的设计实验项目性质:设计性所涉及课程:微机原理与接口技术计划课时:2课时系别:电子与信息工程系班级:通信工程1302班学生姓名:许露平(201308002216)指导教师:蒋恩松湖南科技学院电子与信息工程系一、实验目的掌握Verilog HDL描述有限状态机的设计方法,能够进行简单的数字系统设计。

二、实验原理有限状态机是由寄存器组和组合逻辑构成的硬件时序电路,其状态(即由寄存器组的1和0的组合状态所构成的有限个状态)只可能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态,究竟转向哪一状态还是留在原状态不但取决于各个输入值,还取决于当前所在状态。

三、实验内容“110101”序列检测码,在连续输入的一串数据中,判断是否包含“110101”序列。

要求:画出状态转移图,编码实现,功能仿真。

1、分析检测110101如果采取进行每位二进制数检测的话则需要列出6种状态,并且由于这种检测的关键在于正确码的收到必须是连续的,这就要求必须记住前一次的正确码及正确序列,直到在连续的检测中所收到的每一位码都与与预置数的对应码相同。

在检测过程中,任何一位不相等都将回到初始状态重新开始检测,检测工作比较繁忙。

如果把110101拆成11、01、01,则只有2种状态,若考虑00总共有3种状态,即S0=00,S1=11,S2=01。

用Z记录检测到110101序列的个数,用A,B表示输入的序列,则可根据分析的设计思路画出状态图如下所示:2、Verilog HDL设计代码如下:module jiance(S,clk,Z,reset);input reset,clk;input [1:0] S;output Z;reg Z;parameter S0=2'b00,S1=2'b11,S2=2'b01; reg [1:0] state;always @(posedge clk)beginif(reset)beginstate=S0;Z=0;endelsebegincase(state)S0:beginif(S==2'b11)beginstate=S1;Z=0;endelsebeginstate=S0;Z=0;endendS1:beginif(S==2'b01)beginstate=S2;Z=0;endelsebeginstate=S0;Z=0;endendS2:beginif(S==2'b01)beginstate=S2;Z=1;endelsebeginstate=S0;Z=0;endenddefault: beginstate=S0;Z=0;endendcaseendendendmodule四、实验结果实验结果:(1)给出仿真图形(最好打印)波形仿真如图所示:仿真状态机结果如下图所示:状态机图状态机电路图(2)根据仿真图形,给出你的结论。

生活中有限状态机实验报告

生活中的有限状态机——自动售货机

——骆晓芳

在百度百科中,有限状态机这样解释:有限状态机,(英语:Finite-state machine, FSM),又称有限状态自动机,简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型。

有限状态机是一种具有离散输入输出系统的模型,在任何时刻都处于一个特定的状态。

对于事件驱动的程序设计,它是非常有用的设计模型。

在某一个状态下有事件发生时,根据当前状态和输入事件的不同,选择如何处理该事件以及是否需要转换到下一个状态。

自动售货机我想从三个方面来分析它的有限状态机(以下是用例图):

一,从顾客来分析

顾客投币选择饮料

货币有0.5,1.0,机器可找零,每次投入一种硬币,机器可以输出货物,也可找零:

二.售货机器来分析

售货机根据顾客的投币来找零和出货,售货机对顾客的输入进行识别后出货并判断顾客投币是否足够是否需要找零:

补货员又分为两个部分,查看及取走钱币及查看及补充饮料:

自动售货机类图:。

fsm有限状态机实验报告

74LS73JK 触发器,当 J 与 K 状态相反时,输出 Q 的状态与 J 相同。本实验模拟的 74LS194 功 能要实现四输入四输出,因而需要四个触发器。 对于清零的工作状态的实现,可通过四个触发器连接同一个清零端来解决。考虑另外四种工 作状态,可以使用四个四选一(两个八选二)的数据选择器实现 J 的输入。当 S1、S0 分别 为 00、01、10、11 时实现的四个功能,可以通过 A0、A1、A2 和 A3 分别连接对应的 Qn, Qn-1(或 DSR)、Qn+1(或 DSL)与需要送入的信号来实现。 3,通过状态转换图设计同步状态机 集成下降沿 J-K 触发器 74LS73 构成时序电路,其功能表如下:

五,实验反思

1,注意检验方法。 在完成 197 的拓展设计后,因为将某些引脚设计成了节点形式,但是在仿真运行时没有将其 连接到合适的电位上,导致了以下错误的发生。知道了测试时自己设计的内部图和平时应用 芯片时的差别。

2,197 的拓展实现参考了其芯片的内部图,多次研究后才知道其具体设计方法,新芯片 74LS76 的应用也让设计更加方便。

四,实验内容

1,利用 JK 触发器,设计具备完整功能 74LS197 的模块电路 (1)基础设计:【仅实现 16 进制计数功能】 依次连接 4 个 JK 触发器,其中每个触发器的 Q 输出作为下一级的时钟输入。 将 74LS197 同时接入相同电路,检验两者输出波形是否相同,可知所得电路是否完成了

197 的设计。 设计图:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

步骤2:系统结构设计

系统采用如图2所示的结构。

Step2 structure design

Block diagram of the controller is as shown in Figure 2.

步骤3:组合逻辑电路部分

1.控制器电路的组合逻辑电路部分真值表如图3所示。

2.根据真值表可以得到输出和各内部输出的公式如下。

2.理解有限状态机和时序逻辑电路的概念;掌握二者的关系和各自的组成。

项目要求Requirement

设计控制器电路

(1)按照如下规则控制5个指示灯的打开或关闭:

在1个周期内,关闭所有灯;接下来的周期内,打开指示灯1和2;在之后的周期里,打开1、2、3和4;最后打开所有的灯。随后重复以上4个阶段:灯灭、1和2,1、2、3和4,全亮。如此反复。

Figure 3. truth table for the combinational logic circuit

2.Formula for all the output or inner output of the system according to the truth table

•

•

•

•

•

3.Thecombinational logic circuit should be as shown in figure 4.

步骤5仿真

仿真并检查电路是否能正常工作

Step5 simulation

Simulate and check whether the circuit functions well.

项目结果Result

将最终的电路图复制到下面

Paste your final circuit here!

项目实施Implementation

步骤1:状态图

指定有限状态机的状态图如图1所示。

Step1 the state diagram

State diagram for the required finite state machine is as follows:

Figure 1. State diagram for the controllerFigure 2. Block diagram for the controller

(2)电路中应包含开关,开关关闭时,系统按照上面的规n and implement a controller circuit withmultisim.

(1) The controller’s job is to have the fivelights flash on and off as follows: During one cycle, all lights will be off. The next cycle, lights 1 and 2 will be on. The next cycle, lights 1, 2, 3, 4 will be on. The still next cycle, all five lights will be on. Then the sequence repeats: next cycle, no lights on, followed by 1 and 2 on, followed by 1,2,3 and 4 on, and so forth.

Figure 4. the combinational logic circuit

4. Implement the logic circuit withmultisimusing the components given in the file“Components.ms11”.

步骤4:存储的单元和时钟

控制器采用如图5所示的存储单元结构(参见文件storage element.ms11)。根据图2连接组合逻辑电路部分和存储单元(电路中的时钟使用“Components.ms11”中的 表示)。

Step4 Storage elements and the clock

. Circuit of the storage element has been given in the file“storage element.ms11”. Connect thestorage elements and the combinational logic circuit according to figure e the component to represent the clock in the circuit.

3.根据真值表可得组合逻辑电路结构如图4所示。

4.使用multisim软件按照图4,实现控制器的组合逻辑电路部分。

Step3 combinational logic circuit

1. Truth table of the combinational logic circuit of the controller is as follows:

实验名称

有限状态机的时序逻辑电路实现

The sequential logic circuit that implements a finite machine

实验时间

2012.11.6

实验地点

class room

实验人员(学号+姓名)

项目目的Purpose

1.用有限状态机描述给定问题,并使用时序逻辑电路实现。