基于verilog的SPI设计

[FPGA][Verilog][SPI]简单的读写SPI接口EEPROM-93C46程序

![[FPGA][Verilog][SPI]简单的读写SPI接口EEPROM-93C46程序](https://img.taocdn.com/s3/m/1221e485ec3a87c24028c428.png)

Write19: begin mo <= 0; cs <= 0; end

Read0: cs <= 0; Read1://110+add(7bit) begin cs <= 1; mo <= 1; end Read2: mo <= 1; Read3: mo <= 0;//110 Read4: mo <= 0; Read5: mo <= 1; Read6: mo <= 1; Read7: mo <= 1; Read8: mo <= 1; Read9: mo <= 1; Read10: mo <= 1; Read11: begin mo <= 0; led[7] <= mi; end Read12: led[7] <= mi; Read13: led[6] <= mi; Read14: led[5] <= mi; Read15:

从开始读数据手册,到研究时序,到编写 Verilog 程序,到仿真调试时序,整整 花了有 3-4 天时间。 最后时序已经完全正确, 却读不出任何数据,经过一个晚上的排查才发现是开发 板上的 DI DO SK CS 标号标错了,泪奔~~ 本来我想写一个完整的 SPI 接口出来,想了几天都没有头绪,最后还是写了一个 最简单的写数据读数据的小程序,如果做成接口也勉强可以用。 程序的功能很简单,往地址 0111111 的位置写了 00001111 的数据,地址都还没 有做成接口,固定在程序里面的。 具体用了一个状态机共 53 个状态,每一个状态都是一个 SCK 信号的处理,当然 有分为三个大状态,分别为 ENWR、WRITE、READ 93C46 要首先写 ENWR 信号才能写入数据,具体还得研究数据手册 通过这次 93C46 和上次写 18B20 的经历, 我感觉到数据手册的确是相当的重要的, 需要仔细推敲,分析每一个时序图!下次要做 I2C 接口的 24C02,1、2、3 线就 都学过拉。 当然作为初学者程序是写的那是超级的烂,欢迎拍砖

SPI总线的原理与Verilog设计实现

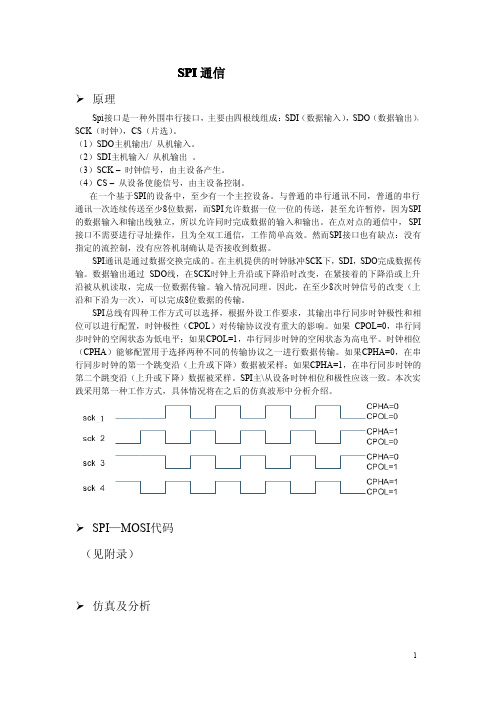

SPI总线的原理与Verilog设计实现一、软件平台与(硬件)平台软件平台:1、(操作系统):Windows-8.12、开发套件:ISE14.73、(仿真)工具:Model(Sim)-10.4-SE硬件平台:1、(FPGA)型号:Xilinx公司的XC6SLX45-2CSG3242、Flash型号:WinBond公司的W25Q128BV Qual SPI Flash存储器二、原理介绍SPI(Serial Peripheral Interface,串行外围设备(接口)),是Motorola公司提出的一种同步串行(接口技术),是一种高速、全双工、同步(通信)总线,在(芯片)中只占用四根管脚用来控制及数据传输,广泛用于EEP(ROM)、Flash、RTC((实时时钟))、(ADC)((数模转换器))、(DSP)((数字信号)(处理器))以及数字信号解码器上。

SPI通信的速度很容易达到好几兆bps,所以可以用SPI总线传输一些未压缩的(音频)以及压缩的(视频)。

下图是只有2个chip利用SPI总线进行通信的结构图时序图如下所示:从上面的时序图可以很清楚的看出,当ROM的地址加1以后,ROM的数据是滞后了一个时钟才输出的,而ROM数据输出的时刻(这个时候ROM的输出数据并没有稳定)刚好是spi_module模块发送下个数据最高位的时刻,那么这就有可能导致数据发送错误,从以上时序图就可以看出8’h33和8’h24两个数据正确发送了,但是8’h98这个数据就发送错误了。

为了解决这个问题,其实只需要把spi_module模块的发送状态机在加一个冗余状态就行了,spi_module模块的发送状态机一共有0~15总共16个状态,那么我在加一个冗余状态,这个状态执行的操作和最后那个状态执行的操作完全相同,这样就预留了一个时钟的时间用来预先设置好要发送的数据,这样的效果是发送数据的最后一个bit实际上占用了3个时钟周期,其中第一个时钟周期把O_tx_done 拉高,后两个时钟周期把O_tx_done拉低。

SPI协议的Verilog 实现

// //接收数据存入 out_data

6

begin case(addr) 1'b0: begin in_buffer = in_data; busy = 1'b1; end 转入工作状态 1'b1: begin busy = 1'b0;end endcase end end else begin if(cs) begin clkcount = clkcount + 1'b1; if(clkcount >= 8'b10) // 控制 SCK 周期 begin clkcount = 0; if((count % 2) == 0) //待发数据存入缓存区,

DataPort[5]-DataPort[0] : busy、sdo 、addr、cs、wr、rd DataPort[21]-DataPort[14] :待发送 8bit 数据 DataPort[13]-DataPort[6] : 接收的 8bit 数据

3

� 总结

完成时间:12.4--12.12 前期:该阶段主要是熟悉 SPI 工作原理,进一步掌握和认识 SPI 通信协议。Chipscore 的使 用之前未曾接触, 在这一阶段, 我先通过简单编程结合开发板抓取数据进行分析达到 对其的基本掌握。 中期:在熟悉 SPI 的工作原理之后,开始尝试编写代码。写了两三次代码,效果均不理想, 很多问题在编写代码的时候没有考虑清楚,导致到了仿真阶段结果与预期有所差距, 且代码冗长复杂。参考了一些资料,效果也不是很好,特别是数据传输暂停部分, 很 多都省略了。不过借鉴别人写的代码也让我收获了不少编写的经验,有些情况下, 运 用不同的逻辑思维可以让代码更简洁、 更具有健壮性。 当然期间也遇到了一些自己无 法解决的问题,非常感谢福星学长耐心的指导,让我学到了不少知识和经验。 后期:该阶段主要是对代码进行再修改、波形仿真以及抓数据调试。 问题及分析: 小问题遇到不少,不过大多都通过 error 的提示,或者上网搜索,找到了问题的原因, 并予以解决。也有软件上的原因,比如:第一次装 ISE 的时候可能没有安装好,上板调试的 时候,cable 不能识别。经过测试分析发现 ISE 里的 drive 没有装上。考虑到这样一个问题的 出现可能还会附带有一些软件上的漏洞,重装了一遍 ISE,问题解决。 使用 chipscope 的时候,芯片配置不对连接失败,查阅该电路板的资料,重新配置,问 题解决。在 chipscope 里面有些触发信号找不到,经分析是被优化了,通过简单修改代码避 免它被优化后,问题解决。运行 chipscope 后发现 waveform 始终没反应,经过一番分析, 认 为时钟线的引脚配置有问题,重换一个时钟信号线 I/O 引脚,问题解决。解决后发现抓取的 波形没有明显的高低跳变,经分析可能是参考时钟选取不对,重选后问题解决。

verilog基本电路设计(包括:时钟域同步、无缝切换、异步fifo、去抖滤波))

Verilog基本电路设计(包括:时钟域同步、无缝切换、异步FIFO、去抖滤波))Verilog基本电路设计共包括四部分:单bit跨时钟域同步时钟无缝切换异步FIFO去抖滤波Verilog基本电路设计之一: 单bit跨时钟域同步(帖子链接:/thread-605419-1-1.html)看到坛子里不少朋友,对于基本数字电路存在这样那样的疑惑,本人决定开贴,介绍数字电路最常见的模块单元,希望给初学者带来帮助,也欢迎大佬们前来拍砖。

如果想要做数字设计,下面这些电路是一定会碰到的,也是所有大型IP,SOC设计必不可少的基础,主要包括异步信号的同步处理,同步FIFO,异步FIFO,时钟无缝切换,信号滤波debounce等等,后面会根据大家反馈情况再介绍新电路。

首先介绍异步信号的跨时钟域同步问题。

一般分为单bit的控制信号同步,以及多bit的数据信号同步。

多bit的信号同步会使用异步FIFO完成,而单bit的信号同步,又是时钟无缝切换电路以及异步FIFO电路的设计基础,这里先介绍单bit信号同步处理。

clka域下的信号signal_a,向异步的clkb域传递时,会产生亚稳态问题。

所有的亚稳态,归根结底就是setup/hold时间不满足导致。

在同一个时钟域下的信号,综合以及布线工具可以在data路径或者clock路径上插入buffer使得每一个DFF的setup/hold时间都满足;但是当signal_a在clkb域下使用时,由于clka与clkb异步,它们的相位关系不确定,那么在clkb的时钟沿到来时,无法确定signal_a此时是否处于稳定无变化状态,也即setup/hold时间无法确定,从而产生亚稳态。

这种异步信号在前后端流程里面是无法做时序分析的,也就是静态时序分析里常说的false_path。

消除亚稳态,就是采用多级DFF来采样来自另一个时钟域的信号,级数越多,同步过来的信号越稳定。

对于频率很高的设计,建议至少用三级DFF,而两级DFF同步则是所有异步信号处理的最基本要求。

用于SoC的SPI接口设计与验证

用于SoC的SPI接口设计与验证匡春雨;马琪;陈科明【摘要】The RTL design and functional simulation of SPI IP core applied to SoC design is presented in this paper. The AMBA 2.0 bus standards is adopted to achieve the communication between the peripheral devices and the internal system through SPI. As fore data transmission section,the traditional design method was abandoned,which needs a specific shift regis-ter for serial/parallel transfer. The shifting transmission register and receive register are put together by the reuse registers to im-prove the speed and save the hardware resources. IP is verified with an SoC verification platform under SoC environment. The re-sults of simulation at the clock frequency of 100 MHZ show that the design can achieve data transmission and meet the require-ments of time-sequence design.%给出了一个可用于SoC设计的SPI接口IP核的RTL设计与功能仿真。

基于UVM的SPI接口IP核的设计与验证

基于UVM的SPI接口IP核的设计与验证SPI(Serial Peripheral Interface)是一种常用的串行外设接口,广泛应用于数字系统中。

为了实现SPI接口的功能,需要设计和验证相应的IP核。

本文将介绍基于UVM(Universal Verification Methodology)的SPI接口IP核的设计与验证。

首先,我们需要了解SPI接口的基本原理。

SPI接口由一个主设备和一个或多个从设备组成。

主设备通过时钟信号控制数据的传输,同时使用片选信号选择从设备。

主设备通过一个数据线发送数据,并通过另一个数据线接收从设备返回的数据。

SPI接口的主要特点是数据传输速度快、灵活性高,适用于多种外设连接。

在设计SPI接口的IP核时,我们需要考虑以下几个方面。

首先,IP核需要支持不同的SPI模式,包括不同的时钟极性和相位设置。

其次,IP核需要能够处理不同的数据位宽,并支持全双工和半双工传输模式。

此外,IP核还需要支持多个从设备的片选信号,并能够处理中断请求。

为了验证SPI接口的IP核,我们采用了UVM方法。

UVM 是一种基于SystemVerilog的验证方法学,提供了一套丰富的验证库和方法。

我们可以利用UVM提供的功能,建立一个完整的验证环境,并编写验证测试用例。

在验证SPI接口的IP核时,我们需要分别验证其主设备和从设备的功能。

对于主设备,我们可以编写测试用例来验证其发送数据的正确性、时序和时钟控制的准确性。

对于从设备,我们可以编写测试用例来验证其接收数据的正确性和片选信号的选择准确性。

通过使用UVM方法,我们可以模拟SPI接口的IP核,并在仿真平台上验证其功能和性能。

通过编写一系列的测试用例,我们可以确保IP核在不同的工作场景下都能正常工作。

综上所述,本文介绍了基于UVM的SPI接口IP核的设计与验证。

通过设计一个支持多种模式、不同数据位宽和多个从设备的IP核,并利用UVM方法进行验证,我们可以确保IP核在实际应用中的正确性和可靠性。

【CPLD+Verilog】CPLD实现SPI接口

CPLD 实现SPI 接口1 实现原理CPLD 实现SPI 接口模块,通过对寄存器的操作,实现SPI 接口功能,对外部SPI 设备进行访问。

CPLD 内部SPI 模块逻辑框图如下所示。

CLK_DIVRX_SHIFT_REGSTATUS LOGICspi_clkspi_cs spi_dospi_tx_data_we_pulsereset_n spi_tx_data spi_rx_data spi_clk_div spi_rx_data_rd_pulsespi_dispi_tx_data_we_busy spi_rx_data_rd_ready spi_data_tx_we_overflow spi_data_rx_rd_nop spi_data_rx_rd_overtime cpld_clkCONTROL LOGICCOUNT LOGIC通过对主时钟分频,得到的SPI 接口时钟,其分频值可通过spi_clk_div 值设定,最小为6分频,当设置分频值低于6分频时,默认6分频。

SPI 接口的片选信号spi_cs 在写数据传输寄存器spi_tx_data 时,通过自动产生写脉冲spi_tx_data_we_pulse ,逻辑综合生成。

spi_rx_data_rd_pulse 在读取接收数据spi_rx_data 的数据时自动产生。

spi_di 和spi_do 分别由数据移位寄存器通过数据移位产生和接收。

spi_clk 由内部分频时钟和传输状态逻辑综合输出,在有数据时输出,无数据时保持高电平。

状态逻辑spi_tx_data_we_busy 信号分别表示数据正在传输,无法写入spi_tx_data 寄存器; spi_rx_data_rd_ready 信号表示数据接收完成,可读取spi_rx_data 寄存器的值。

错误状态逻辑spi_data_tx_we_overflow 信号表示在spi_tx_data 寄存器中写入了待传输值后,还未传输就又写入新的传输数据,表示写数据溢出。

基于Verilog HDL的信号处理板卡中双向端口的设计

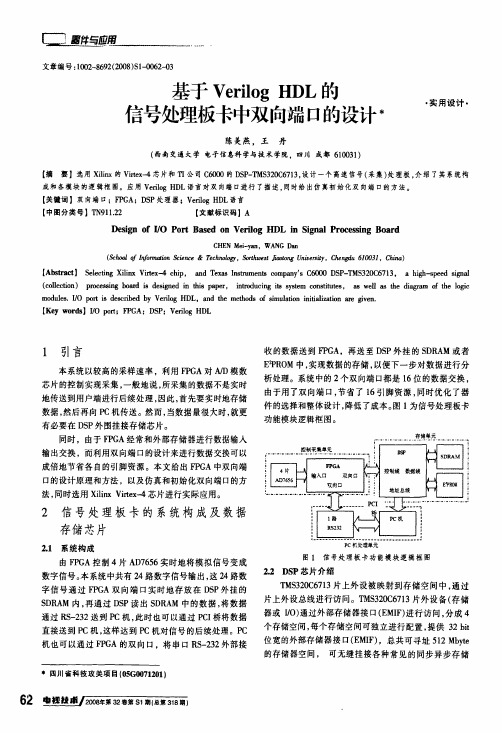

文章编号:1002—8692(2008)S1-0062-03基于V er i l og H D L的信号处理板卡中双向端口的设计术实用设计陈美燕.王丹(西南交通大学电子信息科学与技术学院,四川成都610031)【摘要J选用X i l i n x的V i r t ex--4芯片和11公司C6000的D SP—TM S320C6713,设计一个高速信号(采集)处理板,介绍了其系统构成和各模块的逻辑框图。

应用V er i l og H D L语言对双向端口进行了描述。

同时给出仿真初始化双向端口的方法。

【关键词】双向端口;FPG A;D SP处理器;V er i l og H D L语言【中图分类号】T N911.22【文献标识码】AD es i gn of I,o PO r t B a se d o n V er i l og H D L i n Si gn al Pr oces s i ng B oa r dC H EN M ei-yan,W A N GD an(Sch ool of I n f or m at i o n Sci e nce&T ec hnol ogy,Sor t hwest J i aot o ng U ni vers渺,Chengh610031,C hi n a)【A bs t ra ct】Sel e ct i ng X i l i nx V i r t ex-4chi p,and Texas I ns t r um ent s c om pa ny7s C6000D SP-1M S320C6713,a hi gh-spee d s i g nal (c ol l ec t i on)pr oc ess i ng boa r d i s de si gne d i n t hi s pa pe r,i nt r oduc i ng i t s sys t em co nst i t ut es,a8w el l a8t he di a gr am of t he l ogi c m odul es.I/O pert i s de scr i bed by V er i l og H D L。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

武汉理工大学本科学生毕业设计(论文)开题报告目录摘要 (I)Abstract (II)1 绪论 (3)1.1课题研究背景 (3)1.2 SPI研究目的及意义 (4)1.3 本章小结 (4)2 SPI原理分析 (5)2.1 SPI介绍 (5)2.2 SPI工作模式 (6)2.3 SPI传输模式 (6)2.4 SPI协议 (7)2.5 本章小结 (8)3 方案论证 (10)3.1在51系列单片机系统中实现 (10)3.2 用可编程逻辑器件设计SPI (11)3.3 本章小结 (11)4 SPI的电路设计 (12)4.1 SPI设计系统的功能 (12)4.2 SPI各部分具体实现 (12)4.2.2 SPI系统中所用的寄存器 (13)4.2.3 SPI速率控制 (14)4.2.4 SPI控制状态机 (14)4.2.5 SPI程序设计流程图 (15)4.3 SPI仿真及开发板上调试验证分析 (16)4.3.1 仿真分析 (16)4.3.2开发板上调试 (18)4.4 本章小结 (20)5 论文总结 (21)致谢 (22)参考文献 (23)附录1 (24)附录2 (28)摘要随着专用集成电路(ASIC)设计技术的进步以及超大规模集成电路(VLSI)工艺技术的飞速发展,以及其价格的日益降低,采用FPGA编程的硬件电路来实现诸如SPI接口也日益切实可行,相对软件实现具有更好的优点。

SPI接口是一种常用的标准接口,由于其使用简单方便且节省系统资源,很多芯片都支持该接口,SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间等等。

由于SPI接口是一种事实标准,并没有标准协议,大部分厂家都是参照Motorola的SPI接口定义来设计的,但正因为没有确切的版本协议,不同厂家产品的SPI接口在技术上存在一定的差别,容易引起歧义,有的甚至无法互联(需要用软件进行必要的修改)。

本文基于一种使用较为普遍的协议来进行设计,并参照Motorola公司的MC68HC11A8单片机中的SPI模块定义来设计的简化的SPI接口,用Verilog语言进行编写设计,并在ISE 软件上进行设计仿真,并在基于Xlinx公司的Spartan-3E芯片的Digilent公司出品的Nexys2开发板上用在线逻辑分析仪chipscope进行板上调试验证观察结果,并完成实现功能,并具有一些独创性的设计。

关键词:FPGA Verilog SPI协议 chipscope ISEAbstractWith the advances in design technology of ASIC and VLSI’s rapid development, and its price is lower, the hardware circuit based on FPGA programming interface to achieve such as SPI is feasible, and it realizes better than software. SPI interface is a common standard interface, due to its simple and convenient use and save system resource , a lot of chips support this interface. SPI interface is extensively applied in EEPROM, FLASH, real-time clock, AD converter, and digital signal processor and digital signals decoder, etc.Due to the interface is a fact SPI standard, and it has no standard protocol, most manufacturers design the SPI refer to the interface definition of Motorola's reference.Because of no definite agreement, there is a lot of different versions of the products in the technology exists on SPI interface, easy cause of ambiguity, some even cannot interconnect (need to do some m odification).Based on a common protocols for design, and the company MC68HC11A8 microcontroller of Motorola module definition to design the SPI simplified SPI interface, with Verilog language writing, and in the design of the software design ISE simulation, and based on the Xlinx company Digilent chip Spartan 3E - the Nexys2 development board with online logic analyzers chipscope on board, and debugging validation observations, and complete functionality has some distinctive design.Keywords:FPGA Verilog SPI protocol chipscope ISE1 绪论在研究SPI串行外围接口之前,我们首先要对其背景及其研究的目的要有所了解。

1.1课题研究背景数据传送有串行传送和并行传送两种方。

并行传送以其高速度占领了数据传送领域很长一段时间,采用并行传送的集成电路、外围设备可谓不计其数,从CPU、RAM/ROM到打印机。

从原理上讲,串行传输是按位传输方式,只利用一条信号线进行传输,例如:要传送一个字节(8位)数据,是按照该字节中从最高位逐位传输,直至最低位。

而并行传输是一次将所有一字节中8位信号一并传送出去。

自然最少需要8根信号线。

如果按每次传送的数据流量来看,并行传输要远快于串口,在电脑发展初期,由于数据传输速率不是很高,并行传输还是很快的。

但并行传输也有它的缺点:(1)干扰问题上面的人已经提到。

其根本原因是由于传输速率太快,一般达到100M以上,信号线上传递的频率将超过100MHz,想想看,调频收音机的频率也不过88~108MHz,也就是说,若用并行传输的话,是8根天线放在一起来传输信号,易发生干扰。

但如果加强屏蔽,减小信号线间的耦合电容,是可以继续增大传输速率的,不过这将变得不现实,因为这必然导致信号线将耗用更多金属,截面积更大。

但这并不是不能解决的问题。

(2)并行传输速率提升困难的最主要原因是同步问题并行传输时,发送器是同时将8位信号电平加在信号线上,电信号虽然是以光速传输的,但仍有延迟,因此8位信号不是严格同时到达接受端,速率小时,由于每一字节在信号线上的持续时间较长,这种到达时间上的不同步并不严重,随着传输速率的增加,与8位信号到达时间的差异相比,每一字节的持续时间显得越来越短,最终导致前一字节的某几位与后一字节的几位同时到达接受端,这就造成了传输失败,而且随着信号线的加长这种现象还会越发严重,直至无法使用。

——这是并口传输的致命缺点。

串行传输由于只有一位信号在信号线上,没有位同步问题,因此传送频率可以继续提高,当前传输速率已经达到1Gb/s(1000M)以上,而且还在提高,而并行传输在100Mb/s 左右就停滞不前了,可以预见,串行传输将会比并行传输越来越快。

为此,串行传输已经成为当今外设接口的主流传输方式,为此,摩托罗拉公司开发出了同步外设接口(SPI),并随着时间不断改进,由于其占用线的资源少,且稳定可靠,该总线大量用在与EEPROM、ADC、FLASH和显示驱动器之类的慢速外设器件通信,现在很多单片机等都有SPI模块来连接外围设备,从而使主机与外设传输数据更加方便。

1.2 SPI研究目的及意义SPI是一种同步串行通讯方式,是一种三线同步总线,它是一种常用的标准接口,由于其使用简单方便且节省系统资源,很多芯片都支持该接口,SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间等等。

当然,串口通信还有其他的接口方式,S PI接口和UART相比,多了一条同步时钟线,对通信双方的时序要求不严格不同设备之间可以很容易结合,而且通信速度非常快。

一般用在产品内部元件之间的高速数据通信上面,如大容量存储器等。

这就凸现SPI的好处。

为此,研究SPI接口,可以更容易了解并外围器件传输过程,并对其已定义的进行改进,并使之更加可靠,功能强化。

SPI接口的扩展有硬件和软件两种方法,软件模拟SPI接口方法虽然简单方便,但是速度受到限制,在高速且日益复杂的数字系统中,这种方法显然无法满足系统要求,所以采用硬件的方法实现最为切实可行。

这使得与SPI有关的软件就相当简单,使CPU有更多的时间处理其他事务。

SPI接口是一种事实标准,并没有标准协议,大部分厂家都是参照Motorola的SPI接口定义来设计的,但正因为没有确切的版本协议,不同厂家产品的SPI接口在技术上存在一定的差别,容易引起歧义,有的甚至无法互联(需要用软件进行必要的额修改)。

当前,基于主从处理器结构的系统架构已经成为一种主流(如 DSP+FPGA,MCU+FPGA 等),FPGA是在ASIC的基础发展出来的,它克服了专用ASIC不够灵活的缺点。

与其他中小规模集成电路相比,其优点主要在于它有很强的灵活性,即其内部的具体逻辑功能可以根据需要配置,对电路的修改和维护很方便。

目前,FPGA的容量已经跨过了百万门级,使得FPGA成为解决系统级设计的重要选择方案之一。

在这种架构下,应用FPGA来构建SPI通信接口是切实可行的。

并FPGA是可编程并可重复擦写的,从而具有更大的灵活性,在协议不标准的情况下,可根据外围设备的不同而灵活的改动SPI设计,使设计周期大大降低,并与外围设备连接更加方便。

1.3 本章小结本章主要介绍了SPI的背景,及研究的目的与意义,进而可以知道SPI提出的目的以及其现阶段的发展状况,从而可以对SPI的这些理解达到举一反三的目的。