HDL第五章语法与要素

HDL语言的主要描述语句

HDL语言的主要描述语句5.1 顺序描述语句5.2 并发描述语句5.3 GENERA RE语句5.4 属性(attrib ute)描述5.1顺序描述语句●WAIT语句●断言语句●信号赋值语句●变量赋值语句●IF语句●CASE语句●LOOP语句●NEXT 语句●过程调用语句●NULL语句(只占位置的空操作,对信号赋空值,表示关闭)1.WAIT语句●WAIT语句用于多种不同的目的,常用于为综合工具指定时钟输入。

另一用途是将进程的执行延时一段时间或者是为了动态地修改进程的敏感表。

●wait 语句的执行会暂停进程的执行,直到信号敏感表发生变化或某种条件满足为止<。

若进程中含信号敏感表,则必须紧跟在p roce es之后,这等价于该进程最后一个语句为wa it on 语句;此时不能用显式的wai t语句。

●4种不同条件:WAIT ---无限等待WAIT ON ---敏感信号量变化WAIT UNTIL ---条件满足WAIT FOR ---指定的持续时间●WAIT ON*格式:WAIT ON 信号[,信号];*例1:WAIT ON a,b;表示,当a或b变化时,进程便执行后继的语句*例2:proces s(a,b)beginy<=a and b;end proces s;proces sbeginy<=a and b;wait on a,b;end proces s;以上两进程等价。

●WAIT UNTIL*表示当检测到某个信号出现之前,进程被终止*格式:WAIT UNTIL条件表达式*例:WAIT UNTIL信号 = 数值;WAIT UNTIL信号‘eventand 信号 = 数值;WAIT UNTILnot 信号’stableand 信号 = 数值;wait untilCLK='1';wait untilCLK'eventand CLK='1';wait untilnot CLK'stable and CLK='1';电路综合时,以上3种情况硬件无差别。

Verilog HDL数字设计与综合(第二版) 第五章课后习题答案

1.利用双输入端的nand门,用Verilog编写自己的双输入端的与门、或门和非门,把它们分别命名为my_or,my_and和my_not,并通过激励模块验证这些门的功能。

答:`timescale 1ns/1ns/**************************** ********** my_and *********** ****************************/ module my_and(in1,in2,out); input in1,in2;output out;wire out1;nand a1(out,out1,out1);nand a2(out1,in1,in2); endmodule/**************************** ********** my_or ************ ****************************/ module my_or(in1,in2,out);input in1,in2;output out;wire out1,out2;nand o1(out,out1,out2);nand o2(out1,in1,in1);nand o3(out2,in2,in2); endmodule/**************************** ********** my_not *********** ****************************/ module my_not(in,out);input in;output out;nand n1(out,in,in);endmodule/**************************** ********** test ***************************************/module test;reg a,b;wire and_c,or_c,not_c;initialbegina<=0;b<=0;#10 a<=0;b<=1;#10 a<=1;b<=0;#10 a<=1;b<=1;#10 $stop;endmy_and myand1(a,b,and_c);my_or myor1(a,b,or_c);my_not mynot1(a,not_c); endmodule2.使用上题中完成的my_or,my_and和my_not门构造一个双输入端的xor门,其功能是计算z第5章门级建模41= x’y + x y’,其中x和y为输入,z为输出;编写激励模块对x和y的四种输入组合进行测试仿真。

verilogHDL培训教程华为

verilogHDL培训教程华为近年来,随着人工智能、物联网和5G等新兴技术的快速发展,数字电路设计和FPGA开发方面的需求也越来越迫切。

而Verilog HDL已成为数字电路设计中最受欢迎和广泛使用的硬件描述语言之一。

因此,华为公司推出了一系列的Verilog HDL培训教程,帮助从业人员快速获得这个技能。

华为Verilog HDL培训教程的特点华为Verilog HDL培训教程主要针对初学者和中级学员,旨在让学生掌握Verilog HDL基础和应用。

教程内容科学、系统,结合了中国实际情况,给人耳目一新的感觉。

华为Verilog HDL培训教程遵从"理论与实践相结合"的原则,保证学生能够灵活应用所学知识。

在理论教学方面,华为Verilog HDL培训教程先后介绍和讲解了Verilog HDL的基础概念、语法、数据类型、运算符、模块等。

在实践操作方面,华为Verilog HDL培训教程采用基于FPGA芯片的开发板完成实验,让学生能够真正体验到数字电路设计的工程化过程。

此外,华为Verilog HDL培训教程融合了多元化的教学形式,通过讲解PPT、操作演示视频、实验文档等多种形式进行教学。

教材编制过程中对各章节的课程设计进行了充分的考虑,让学生可以从基础入手,系统性、完整性地掌握Verilog HDL语言。

总之,华为Verilog HDL培训教程尽力使学习过程严谨、声音,减少因知识不足而带来的错误和困惑。

华为Verilog HDL培训教程的课程设置华为Verilog HDL培训教程旨在让学员了解数字电路设计中最常用的硬件描述语言-- Verilog HDL,并在FPGA开发板上完成一些典型实验。

华为Verilog HDL培训教程包含以下章节:第一章:Verilog HDL基础概念在本章中,学生将学习Verilog HDL的起源、产生背景、基本概念、Verilog HDL的体系结构、Verilog HDL模块体系结构等知识。

第5章-Verilog HDL语法规范(第4讲)-5.4

Verilog HDL语言要素 --标识符

转义标识符 转义标识符可以在一条标识符中包含任何可打印字符。 转义标识符以\(反斜线)符号开头,以空白结尾。

注:空白可以是一个空格、一个制表字符或换行符。

Verilog HDL语言要素 --标识符

下面给出转义标识符的例子

\busa+index \-clock \***error-condition*** \net1/\net2 \{a,b} \a*(b+c)

Verilog HDL语言规范

Verilog HDL语言要素

Verilog语言要素主要包括:

注释 间隔符 标识符 关键字 系统任务和函数 编译器命令 运算符 数字 字符串和属性

Verilog HDL语言要素 --注释

在Verilog HDL中有两种形式的注释。该语法规定和C语 言一致。

单行注释 起始于双斜杠“//”,表示该行结束,以及新的一行开始。单行 注释符号“//”在块注释语句内并无特定含义。

特殊字符表示 \n \t \\ \” \ddd

意义 换行符 Tab键 符号\ 符号” 3位八进制数表示的ASCII 值(0<<d<<7)

Verilog HDL语言要素 --属性

随着工具的扩展,除了仿真器使用Verilog HDL作为其 输入源外,还包含另外一个机制,即在Verilog HDL源文 件中指定对象、描述和描述组的属性。

以 `(重音符号)开始的某些标识符是编译器指令。 在编译Verilog HDL语言时,特定的编译器指令均有效,即:

编译过程可跨越多个文件,直到遇到其它不同编译程序指令 为止。

Verilog HDL语言要素 --编译器命令

编译器命令的Verilog HDL描述例子

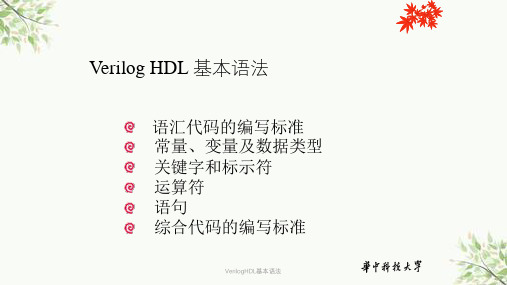

VerilogHDL基本语法课件

VerilogHDL基本语法

9

变量

变量即在程序运行过程中其值可以改变的量 Verilog HDL中共有19种数据类型;其中3个最基本的数据类

型为: • 网络型(nets type) • 寄存器型(register type ) • 数组型(memory type)

VerilogHDL基本语法

10

变量

线网类型:nets type表示Verilog结构化元件间的物理连线。它 的值由驱动元件的值决定;如果没有驱动元件连接到线网,线 网的缺省值为z。 寄存器类型:register type表示一个抽象的数据存储单元,它只 能在always语句和initial语句中被赋值,并且它的值从一个赋值 到另一个赋值被保存下来。寄存器类型的变量具有x的缺省值。

每个向量 位宽为n

共有m个reg 型向量

14

变量

register型变量与nets型变量的根本区别是:

❖register型变量需要被明确地赋值,并且在 被重新赋值前一直保持原值。

❖register型变量必须通过过程赋值语句赋值! 不能通过assign语句赋值!

❖在过程块内被赋值的每个信号必须定义成 register型!

VerilogHDL基本语法

阻态z • 为提高可读性,在较长的数字之间可用下划线_隔开!但不可以

用在<进制>和<数字>之间。 • 当常量未指明位宽时,默认为32位。

VerilogHDL基本语法

6

常量

• 17 //位宽, 基数符号不写会采用default值

(32bit十进制)

DigitalDesignPrinciplesandPractices第五版课程设计

Digital Design Principles and Practices 第五版课程设计课程前言数字设计原理和实践(DDPP)的第五版是面向初学者的数字设计课程。

本课程所涵盖的领域包括数字逻辑设计、计算机组成、数字信号处理和硬件描述语言(HDL)语法。

DDPP第五版的主要目标是使学生理解数字系统的基本原理和设计方法,并掌握一些基本的数字设计工具和技术。

本课程不仅强调数字系统的硬件实现,还介绍了一些常见的数字信号处理和通信应用,同时也会提供一些软件应用和仿真工具的使用。

课程内容第一章:数字系统概述本章主要介绍数字系统的基本概念,包括数字电子学的发展历史、数字系统的基本组成部分、数字信号和模拟信号的区别以及数字系统的应用领域。

第二章:数字电路基础本章介绍数字逻辑元件和数字电路的基本原理,包括数字量的表示和计算、逻辑门电路的实现、布尔代数和卡诺图的运算方式。

第三章:计算机组成本章介绍计算机硬件的基本组成部分,包括中央处理器(CPU)、主存储器、输入输出系统和系统总线。

第四章:数字信号处理本章介绍数字信号的基本概念和数字信号处理的原理,包括数字信号的采样、量化、编码和解码、数字信号处理的基本方法和算法以及数字滤波器的设计过程。

第五章:HDL语法本章介绍硬件描述语言(HDL)的基本语法和设计原理,包括HDL的分类和应用、HDL的语法和设计原则、HDL的模块化设计和建模技术以及HDL的仿真和综合方法。

课程评估课程的最终成绩将由以下几个因素决定:•期末考试(50%)•课堂作业(25%)•项目(25%)考虑到本课程具有实验性质,所以将开展一个实验项目,要求学生设计一个数字系统并进行测试和评估。

这将在本课程的第9周到第12周期间完成,占课程总成绩的25%。

课程资源为了更好地支持学生的学习,本课程提供以下资源:•教材:《数字设计原理与实践》(第五版)•仿真软件:Xilinx ISE、ModelSim•设计软件:Vivado、Quartus•硬件平台:FPGA开发板、数字信号处理器(DSP)总结数字设计原理与实践(DDPP)第五版是一门介绍数字系统基本原理和设计方法的课程。

第5章-Verilog语言要素

5.3.2 Variable型

variable型变量必须放在过程语句(如initial、always)中,通 过过程赋值语句赋值;在always、initial等过程块内被赋值的 信号也必须定义成variable型。 variable型(以前叫register型)是数据存储单元的抽象,但不 能表示真正的硬件,相当于计算机高级语言中的变量。 常用variable型变量:

整数(integer)

Examples:

8'b11000101 //位宽为八位的二进制数11000101

8'hd5

//位宽为八位的十六进制数d5;

5'O27

//5位八进制数

4'D2

//4位十进制数2

4'B1x_01

//4位二进制数1x01

5'Hx

//5位x(扩展的x),即xxxxx

4'hZ

//4位z,即zzzz

assign larger=(a>b);

assign equal=(a==b);

assign less=(a<b);

endmodule

【例5.4】 采用参数定义的二进制计数器

module count_w(en,clk,reset,out);

input clk,reset,en; parameter WIDTH=8;

◆ 整数

◆ 实数

◆ 字符串

整数(integer)

整数按如下方式书写:

+/-<size> '<base><value> 即 +/-<位宽>'<进制><数字> size 为对应二进制数的宽度;base为进制;value是 基于进制的数字序列。 进制有如下4种表示形式: ◆ 二进制(b或B) ◆ 十进制(d或D或缺省) ◆ 十六进制(h或H) ◆ 八进制(o或O)

Verilog HDL基础

还可以在模块实例引用时,改变引用模块或实例中已 定义的参数。

module decode(A,F) parameter IN_Width=4,OUT_Width=16; …

endmodule;

4.4 变量--数据类型

wire型

用assign赋值的组合逻辑信号,输入输出信号 默认为wire型,取值为0、1、x和z

4.2 Verilog基本语法—语言要素

间隔符: Verilog 的间隔符主要起分隔文本的作用, 可以使文本排列有序,便于阅读与修改。

间隔符包括空格符(\b)、TAB 键(\t)、换行符(\n) 及换页符。

注释符:注释只是为了改善程序的可读性,在编译时 被忽略。

多行注释符“/* --- */”:用于写多行注释; 单行注释符“//”:以开始到行尾结束为注释文字。

如:8’b01010011,8’h53

x代表不定值,z代表高阻,每个字符所代表的 宽度取决于所用进制

下划线:用来分隔数,以提高程序可读性

如16’b0011101001010001可写成 16’b0011_1010_0101_0001

4.4常量--parameter

Parameter用来定义一个标识符代表一个常量,称为 符号常量,用以提高程序的可读性,经常用于定义变 量的宽度。

4.7 循环移位寄存器(1)

always @ (posedge clk) if(preset) begin q3=0; q2=1; q1=1; end begin q3=q2; q2=q1; q1=q3; end;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4、关键字 Verilog 系统内部使用的词,关键字用户不可用重定义其它含义。 所有的关键字都是小写字母组成。例如always是关键字,但是 ALWAYS不是关键字。

5. 2 常量

Verilog 中常量主要有三种类型:整数、实数、字符串 5.2.1 整数。 +/-<size>‟<base><value> +/-<二进制位宽>‟<进制><数字序列>

例如:8‟b1001xxxx

8‟b1010zzzz

与 8‟h9x相同

与 8‟haz相同

4)如果没有定义一个整数的位宽,则其宽度为响应数所需的二进制位。 例如:‟o721 // 9位二进制数111010001 „hAF //8位二进制数10101111 5)如果定义的位宽比实际的位数长,则通常左边添0补位,但如果数的 最左边为x或z,则左边添x或z。

wire [ 19:0] addrbus ;

//定义位宽 20位wire型变daddrbus

wire [0:7] a ; // 定义位宽为8位的wire型变量

2)tri型

功能与使用方法与wire型相同,只是为了增加程序的可读性,可更 清楚表示该信号综合后的电路具有三态的功能。 3)supply0 h和supply1型 supply0用于对“地”建模,即低电平0;supply1网用于对电源建 模,即高电平1;例如:

5.3 数据类型

数据类型是用来表示数字电路中的物理连线、数据存储和 传输单元等物理量。 Verilog HDL有下列四种逻辑值状态: 1) 0:低电平、逻辑0或逻辑非(“假”) 2) 1:高电平、逻辑1或“真”

3) x或X:不确定或未知的逻辑状态

4) z或Z:高阻态

Verilog HDL 中的变量部分为如下两种类数据类型:net型和variable型

例如: 10‟b10

10‟bx0x1

//左边添8位0,即0000000010

// 左边添6位x,即xxxxxxx0x1

如果定义的位宽比实际的位小,则左边(高位)的位数被截掉。 例如:3‟b1001_0011 5‟H0FFF 同 同 3‟b011 5‟H1F

6)?是高阻态z的另一种表示方法,在表示数字时完全等同替代。 7)整数可以带正、负符号,正、负号必须写在最左面。负数通常用 二进制补码表示。

parameter MSB=15 ;

assign sum= a+b ;

//参数定义,可以改变MSB值

input [MSB:0 ] a,b ; output [MSB+1 :0] sum ; endmodule

module count_w(en,clk,reset,out) ; //八位二进制计数器 input clk,reset,,en ; parameter WIDTH=8 ; //参数定义,可以改变SIZE值 output [WIDTH-1:0] out ; wire [WIDTH-1:0] out ; always @(posedge clk or negedge reset )

例如:-8‟h72 // -72H的 8位二进制补码10001110

8)当位宽与进制缺省时表示是十进制数。 例如32 //表示十进制数32 -15 // 表示十进制数-15 9)在位宽与‟之间,以及进制和数字之间允许出现空格但 ‟与进制之间以 及数字之间不允许出现空格。 例如: 6 ‘b 110001 //合法,表示6位二进制数110001

进制有以下4种形式:

二进制 : b或B,不区别大写、小写字母; 十进制: d或D或缺省,不区别大写、小写字母;

十六进制:h或H ,不区别大写、小写字母;

八进制: o或O ,不区别大写、小写字母;

合格的整数书写例子。 8‟b11011010 //位宽为8位二进制数11011010

8‟hd5

5‟o27 4‟D2

参数名通常用大写字母表示,而标识名、变量采用小写字母表示。

module compare_w(a,b,larger,equal,less) ; //六位数据比较器

parameter SIZE=6 ;

input [SIZE-1:0 ] a,b ;

//参数定义,可以改变SIZE值

output larger,equal,less ; wire larger,equal,less ; assign larger=(a>b) ; assign equal=(a==b) ; assign less=(a<b) ; endmodule module add_w(a,b,sum) ; //十六位加法器

[ MSB : LSB] 方括号左边的数字表示向量的最高位,右边的数字表示最低位。

例如:

wire [ 3 : 0 ] bus ; // 4 位总线标量 bus[3]bus[2]bus[1]bus[0] reg [ 0 :7 ] rc ; // 8 位寄存器rc[0]rc[1]rc[2]rc[3]…rc[7]

wire 数据名1,数据名2,…数据名 i; //变量位宽为一位。

例如:wire a,b; //定义两个位宽一位的wire型变量a和b。 或: wire [ n-1: 0 ] 数据名1,数据名2,…数据名 Ii; //变量位宽为n位。 或: wire [ n: 1 ] 数据名1,数据名2,…数据名 Ii; //变量位宽为n位。 例如:wire [7:0 ] databus ; //定义位宽 8位wire型变量databus。

定义格式如下: reg 数据名1,数据名2,…数据名 i; //变量位宽为一位。 例如:reg a,b; //定义两个位宽为一位的reg型变量a和b。

或: reg [ n-1: 0 ] 数据名1,数据名2,…数据名 i; //变量位宽为n位。

或: reg [ n: 1 ] 数据名1,数据名2,…数据名 i; //变量位宽为n位。 例如:reg [7:0 ] qout ; //定义位宽 为8位reg型变量qout。 reg [ 8:1] qout ; //定义位宽 为8位reg型变量qout。

字符符的作用主要是在仿真时,显示一些相关的信息,或者指定显 示格式。字符串属于reg型变量,其宽度为此字符串中的字符个数乘以8. 例如: reg [8*12:1] stringvar ; /* tringvar 是reg型变量,该变量可以存放包 含12个字符的字符串,共96bit */

begin

stringvar=“Hello word!” ; //变量stringvar存放字符串(包含12个字符) end

end

end endmodule ````` `

5.4 向量

1、向量与标量 标量:宽度为一位的变量。如果在变量声明中没有指定位宽,则默认 为标量。 例如: wire a ; // 标量 a reg clr ; //reg型标量 clr

向量(vector):宽度为大于一位的变量。向量的宽度定义形式为:

不合格的整数书写例子。

3‟ b001 // ‟ 与基数b之间不允许出现空格

4‟d-4

( 3 +2 )‟b10

// 数值不允许正、负符号( +或-)正、负符号只

// 允许出现在最左面 //位宽为不可以是表达式

在书写数字时需要注意: 1)在较长数字之间可以因 _ 分开,用来提高可读性,但第一个数字 之前不可以加下划线。 2)无位宽说明时,默认为为32位(二进制)。 3)x或z在二进制中代表一位 x或z,在八进制中代表3位x或z,在十六 位进制中代表4为x或z.

2)integer型 多用于表示循环变量,表示循环次数。integer型变量只

能被整体使用,不能作为位向量使用。

定义格式变量同reg: integer i,j ; //i、j被定为两个integer变量。

5.4 参数

Verilog用参数parameter来定义符号常量。参数经常用于定义时

延和变量的宽度。使用参数说明的参数只被赋值一次。参数说明形式 如下:

1、 线网类型。net类型表示Verilog结构化元件间的物理连线。它的值由 驱动元件的值决定,例如连续赋值或门的输出。如果没有驱动元件连接

到线网,线网的缺省值为z。可综合的net 型变量有:wire型、tri型、

supply1和supply0。见教材P126表5.2

1)wire型

是最常用的net型数据变量,,Varilog HDL模块中的输入/输出信 号未被明确指定数据类型时都被默认为wire型。可以取值0、1、X、 Z,如果wire型变量没有被连接到驱动,其值为高阻态Z。 wire型变量定义格式为:

6‟ b110001

6‟b 110 001

//不合法,在 ‟ 与进制 b 之间出现空格

//不合法,在 数字之间出现空格

5.2.2 实数

实数可以用下列两种形式定义: 1) 十进制计数法;例如

2) 科学计数法; 这种形式的实数举例如下:

5.2.3 字符串

字符串是双引号内的字符序列。字符串不能分成多行书写。例如:

2、位选择和域选择 有两类向量:标量类向量,未加特别说明定义的向量; 向量类向量,定义时用关键字vectored说明。 例如: wire vectored [7:0 ] databus ; //8位向量类标量databus reg [31 : 0 ] rega ; //32位标量类向量rega

Verilog HDL 只允许对标量类向量进行位选择和域选择。 位选择:在表达式中选择向量中的某一位。 域选择 :表达式中选择向量中相邻几位。 在进行位选择、域选择时,必须等号左右两端的位宽一致。 例如:

//位宽为8位十六进制数d5(即二进制数11010101)

//位宽为5位八进制数27(即二进制数10111) //位宽为4位十进制数2(即二进制数0010)