数字设计(Digital Design)习题解答5

数字设计(Digital Design)习题解答1

1INTRODUCTIONE X E R C I S E S O L U T I O N S1.2Three definitions of “bit”:(1) A binary digit (p. 1).(2)Past tense of “bite” (p. 1).(3) A small amount (pp. 6, 10).1.3ASIC Application-Specific Integrated CircuitCAD Computer-Aided DesignCD Compact DiscCO Central OfficeCPLD Complex Programmable Logic DeviceDAT Digital Audio TapeDIP Dual In-line PinDVD Digital Versatile DiscFPGA Field-Programmable Gate ArrayHDL Hardware Description LanguageIC Integrated CircuitIP Internet ProtocolLSI Large-Scale IntegrationMCM Multichip Module1–12DIGITAL CIRCUITSMSI Medium-Scale IntegrationNRE Nonrecurring EngineeringOK Although we use this word hundreds of times a week whether things are OK or not, we have probably rarely wondered about its history. That history is in fact a brief one, the word being first recorded in1839, though it was no doubt in circulation before then. Much scholarship has been expended on theorigins of OK, but Allen Walker Read has conclusively proved that OK is based on a sort of joke.Someone pronounced the phrase “all correct” as “oll (or orl) correct,” and the same person or someoneelse spelled it “oll korrect,” which abbreviated gives us OK. This term gained wide currency by beingused as a political slogan by the 1840 Democratic candidate Martin Van Buren, who was nicknamedOld Kinderhook because he was born in Kinderhook, New York. An editorial of the same year, refer-ring to the receipt of a pin with the slogan O.K., had this comment: “frightful letters . . . significant ofthe birth-place of Martin Van Buren, old Kinderhook, as also the rallying word of the Democracy of thelate election, ‘all correct’ .... Those who wear them should bear in mind that it will require their moststrenuous exertions ... to make all things O.K.” [From the American Heritage Electronic Dictionary(AHED), copyright 1992 by Houghton Mifflin Company]PBX Private Branch ExchangePCB Printed-Circuit BoardPLD Programmable Logic DevicePWB Printed-Wiring BoardSMT Surface-Mount TechnologySSI Small-Scale IntegrationVHDL VHSIC Hardware Description LanguageVLSI Very Large-Scale Integration1.4ABEL Advanced Boolean Equation LanguageCMOS Complementary Metal-Oxide SemiconductorJPEG Joint Photographic Experts GroupMPEG Moving Picture Experts GroupOK(see above)PERL According to some, it’s “Practical Extraction and Report Language.” But the relevant Perl FAQ entry, in perlfaq1.pod, says “never write ‘PERL’, because perl isn't really an acronym, apocryphal folkloreand post-facto expansions notwithstanding.” (Thanks to Anno Siegel for enlightening me on this.) VHDL VHSIC Hardware Description Language1.8In my book, “dice” is the plural of “die.”。

数字设计(Digital Design)习题解答6

119E X E R C I S E S O L U T I O N S SequentialLogic Design Principles77.27.3The latch oscillates if S and R are negated simultaneously. Many simulator programs will exhibit this same behavior when confronted with such input waveforms.S R Q QNS R QQN120DIGITAL CIRCUITS7.57.8Just tie the J and K inputs together and use as the D input. 7.9Excitation and output equations:Excitation/transition table; state/output table:7.15Excitation equations:Excitation/transition table; state table:7.18Excitation and output equations:QNQ Q QTEN J K CLKD1Q1′Q2+=D2Q2′X ⋅=Z Q1Q2′+=ENQ1Q201001011011010100001111010Q1*Q2*ENS1ZA C D 1BC C 0C A B 1DCC1S*D2Q (1Q0)Q1′Q2′⋅()⊕⊕=D1Q2=D0Q1=Q2Q1Q0Q2*Q1*Q0*000100001000010101011001100010101110110111111011S S*A E B A C F D B E C F G G H HDJ0K0EN ==J1K1Q0EN ⋅==MAX EN Q1Q0⋅⋅=EXERCISE SOLUTIONS 121Note that the characteristic equation for a J-K flip-flop is . Thus, we obtain the following transition equations:Transition/output table; state/output table:State diagram:Timing diagram:7.20This can be done algebraically. If all of the input combinations are covered, the logical sum of the expressionson all the transitions leaving a state must be 1. If the sum is not 1, it is 0 for all input combinations that are uncovered. For double-covered input combinations, we look at all possible pairs of transitions leaving a state.The product of a pair of transition equations is 1 for any double-covered input combinations.(a)State D , Y = 0 is uncovered.(b)State A , (X+Z ′) = 0 is uncovered. State B , W = 1 is double-covered; (W+X ) = 0 is uncovered. State C ,(W+X+Y+Z ) = 0 is uncovered; (W ⋅X + W ⋅Y + Z ⋅Y + Z ⋅X ) = 1 is double covered. State D , (X ⋅Y + ⋅X ′⋅Z + W ⋅Z ) = 0is uncovered; (W ⋅X ′⋅Z + W ⋅X ⋅Y ⋅Z ) = 1 is double-covered;Q ∗J Q ′⋅K ′Q ⋅+=Q0∗EN ′Q0⋅EN Q0′⋅+=Q1∗EN ′Q1⋅EN Q0⋅Q1′⋅EN Q0′Q1⋅⋅++=ENQ1Q2010000,001,00101,010,01010,011,01111,000,1Q1*Q2*, MAXENS1A A,0B,0B B,0C,0C C,0D,0DD,0A,1S*, MAXAENEN ENEN ′EN ′EN ′EN ′ENBCDCLK EN Q0Q1MAX122DIGITAL CIRCUITS7.21Table 9–4 on page 804 shows an output-coded state assignment. Here is a corresponding transition list:The excitation equations and circuit diagram follow directly from this transition list.7.25The minimum setup time is the clock period times the duty cycle. That is, the minimum setup time is the timethat the clock is 1.7.27As shown in Section 7.9.1, the excitation equation for the latch of Figure 7–72 is Below, we analyze Figure X7.27 in the same way:The feedback equation isThe feedback equations are the same, and so the circuits have identical steady-state behavior.The circuit in Figure X7.27 is better in two ways. It uses one less gate, and it has one less load on the D input. 7.29The AND gate in the original circuit is replaced with a NAND gate. As a result, the second flip-flop stores theopposite of the value stored in the original circuit; to compensate, swap connections to its Q and QN outputs.SL3Z L2Z L1Z R1Z R2Z R3ZTransition expression S*L3Z *L2Z *L1Z *R1Z *R2Z *R3Z *IDLE 000000(LEFT + RIGHT + HAZ)′IDLE 000000IDLE 000000LEFT ⋅HAZ ′⋅RIGHT ′L1001000IDLE 000000HAZ + LEFT ⋅RIGHT LR3111111IDLE 000000RIGHT ⋅HAZ ′⋅LEFT ′R1000100L1001000HAZ ′L2011000L1001000HAZ LR3111111L2011000HAZ ′L3111000L2011000HAZ LR3111111L31110001IDLE 000000R1000100HAZ ′R2000110R1000100HAZ LR3111111R2000110HAZ ′R3000111R2000110HAZ LR3111111R30001111IDLE 000000LR31111111IDLEY ∗C D ⋅C ′Y ⋅D Y⋅++=D C(C ⋅ D)′((C ⋅ D)′ ⋅ C) + Y ′C ⋅D + (((C ⋅ D)′ ⋅ C) + Y ′)′((C ⋅ D)′ ⋅ C)′QQNY ∗YY ∗C D ⋅C D ⋅()′C ⋅()Y ′+()′+=C D ⋅()C D ⋅()′C ⋅()′Y ⋅+=C D ⋅C D ⋅()(C ′)Y ⋅++=C D ⋅D C ′+()Y ⋅+=C D ⋅D Y ⋅C ′Y⋅++=EXERCISE SOLUTIONS 123The OR gates in the original circuit are also replaced with NAND gates. As a result, each input must be con-nected to a signal of the opposite polarity as before, that is, to the complementary flip-flop output. In the case of connections to the second flip-flop, we swapped outputs twice, so the connections remain the same.The final circuit below uses three 2-input NAND gates.7.45 A transition table corresponding to the state table is shown below:This table leads to the following Karnaugh maps for the excitation logic, assuming a “minimal cost” treatment of unused states.A BQ2Q1Q000011110Z0000010010100100001011011010010001000100110010000110110111100101100001101100100110101101111001011100011011001001Q2*Q1*Q0*D Q Q CLK D QQCLK XZCLK000111100001111000011110A BQ1 Q200011110A B A BA B A BA B A BA B A BABA BA BQ1Q2Q0=0Q1 Q2Q1Q2Q0=1100001111000011110Q1 Q200011110Q1Q2Q0=0Q1 Q2Q1Q2Q0=1000111100001111000011110Q1 Q200011110Q1Q2Q0=0Q1 Q2Q1Q2Q0=1D0D1D21100110011001100001100000000000011000000111111111111000001000010d d d d d d d d d d d d 0000011011101111111A ′0011Q1′⋅ Q2′ ⋅ A Q0Q0′ ⋅ Q1 ⋅ B 01Q0′ ⋅ Q2 ⋅ AQ0′ ⋅ Q1 ⋅ AQ1 ⋅ A ⋅ BQ2 ⋅ A ⋅ B124DIGITAL CIRCUITSThe resulting excitation equations areIgnoring inverters, a circuit realization with the new equations requires one 2-input gate, six 3-input gates, and one 5-input gate. This is more expensive than Figure 7–54, by four gates.7.49The new state assignment yields the followingtransition/excitation table and Karnaugh maps:This yields the following excitation equations:Compared with the results of original state assigment, these equations require two more 3-input AND gates,plus a 6-input OR gate inplace of a 4-input one. However, if we are not restricted to a sum-of-products realiza-tion, using the fact that might make this realization less expensive when discrete gates are used.D0A ′=D1Q1′Q2′⋅A ⋅Q0+=D2Q2A ⋅B ⋅Q0′Q2⋅A ⋅Q0′Q1⋅A ⋅Q1A ⋅B ⋅Q0′Q1⋅B⋅++++=X YQ1Q000011110Z0000011101 1 010******** 11111000100 1010000100Q2*Q1*or D1D20001100001111000011110X YQ1 Q200011110X YQ1Q2D1X YQ1 Q2X Q1Q2D21110101100000101010110101010010111Y Q1 ⋅ Q2′ ⋅ X ′Q1 ⋅ Q2′ ⋅ Y ′Q1′ ⋅ Q2 ⋅ Y Q1′ ⋅ X ⋅ YQ2 ⋅ X ′ ⋅ Y ′Q2 ⋅ X ⋅ YQ2′ ⋅ X ′ ⋅ Y Q2′ ⋅ X ⋅ Y ′Q1 ⋅ X ′ ⋅ Y ′Q1′ ⋅ Q2 ⋅ XD1Q1′Q2X ⋅⋅Q1′Q2Y ⋅⋅Q1′X Y ⋅⋅Q1Q2′X ′⋅⋅Q1Q2′Y ′⋅⋅Q1X ′Y ′⋅⋅+++++=D2Q2X Y ⋅⋅Q2′X Y ′⋅⋅Q2′X ′Y Q2X ′Y ′⋅⋅+⋅⋅++=D2Q2X Y ⊕⊕=EXERCISE SOLUTIONS 1257.57Here is the transition list:The transition/excitation and output equations below follow directly from the transition list.Starting from the IDLE state, the following transitions may be observed:For each input combination, the machine goes to the R1 state, because R1’s encoding is the logical OR of the encodings of the two or three next states that are specified by the ambiguous state diagram.SQ2Q1Q0Transition expressionS*Q2*Q1*Q0*IDLE000(LEFT+RIGHT+HAZ)′IDLE 000IDLE000LEFT L1001IDLE000HAZ LR3100IDLE 000RIGHTR1101L10011L2011L20111L3010L30101IDLE 000R1 1011R2111R2 1111R3110R31101IDLE 000LR311IDLESQ2Q1Q0LEFTRIGHTHAZQ2*Q1*Q0*S*IDLE000101101R1IDLE 000 011101R1IDLE 000 110101R1IDLE11111R1D2Q2∗Q2′Q1′Q0′HAZ ⋅⋅⋅== Q2′Q1′Q0′RIGHT⋅⋅⋅+ Q2Q1′Q0⋅⋅+ Q2Q1Q0⋅⋅+Q2′Q1′Q0′HAZ RIGHT +()⋅⋅⋅Q2Q0⋅+=D1Q1∗Q2′Q1′Q0⋅⋅== Q2′Q1Q0⋅⋅+ Q2Q1′Q0⋅⋅+ Q2Q1Q0⋅⋅+Q0=D0Q0∗Q2′Q1′Q0′LEFT⋅⋅⋅== Q2′Q1′Q0′RIGHT ⋅⋅⋅+ Q2′Q1′Q0⋅⋅+ Q2Q1′Q0⋅⋅+Q2′Q1′Q0′LEFT RIGHT +()⋅⋅⋅Q1′Q0⋅+=126DIGITAL CIRCUITSThe behavior aboveis not so good and is a result of synthesis choices—state encoding and logic synthesis method. If a different state encoding were used for R1, or if a different synthesis method were used (e.g., prod-uct-of-s-terms), then the results could be different. For example, starting with the transition list given earlier,we can obtain the following set of transition equations using the product-of-s-terms method:These equations yield the following transitions:This is obviously different and still not particularly good behavior.7.58Let E(SB), E(SC), and E(SD) be the binary encodings of states SB , SC , and SD respectively. Then, the bit-by-bit logical OR of E(SB) and E(SC). This is true because the synthesis method uses the logical OR of the next values for each state variable and, by extension, the logical OR of the encoded states.SQ2Q1Q0LEFTRIGHTHAZQ2*Q1*Q0*S*IDLE 000 000000IDLE IDLE 000 011100LR3IDLE 000 110001L1IDLE111IDLED2Q2∗Q2Q1Q0LEFT RIGHT HAZ +++++()== Q2Q1Q0LEFT ′+++()⋅ Q2Q1Q0′++()⋅ Q2Q1′Q0′++()⋅ Q2Q1′Q0++()⋅ Q2′Q1′Q0++()⋅ Q2′Q1Q0++()⋅Q2Q1RIGHT HAZ +++()Q2Q1LEFT ′++()Q2Q0′+()Q1′Q0+()Q2′Q0+()⋅⋅⋅⋅=D1Q1∗Q2Q1Q0LEFT RIGHT HAZ +++++()== Q2Q1Q0LEFT ′+++()⋅ Q2Q1Q0HAZ ′+++()⋅ Q2Q1Q0RIGHT ′+++()⋅ Q2Q1′Q0++()⋅ Q2′Q1′Q0++()⋅ Q2′Q1Q0++()⋅Q2Q1Q0++()Q1′Q0+()Q2′Q0+()⋅⋅=D0Q0∗Q2Q1Q0LEFT RIGHT HAZ +++++()== Q2Q1Q0HAZ ′+++()⋅ Q2Q1′Q0′++()⋅ Q2Q1′Q0++()⋅ Q2′Q1′Q0′++()⋅ Q2′Q1′Q0++()⋅ Q2′Q1Q0++()⋅Q2Q0LEFT RIGHT +++()Q2Q0HAZ ′++()Q1′()Q2′Q0+()⋅⋅⋅=E SD ()E SB ()E SC ()+=EXERCISE SOLUTIONS 1277.68As far as I know, I was the first person to propose BUT -flops, and Glenn Trewitt was the first person to analyzethem, in 1982. To analyze, we break the feedback loops as shown in the figure to the right.The excitation and output equations areThe corresponding transition/state table isThe two stable total states are circled. Notice that state 00 is unreachable.When X1 X2 = 00 or 11, the circuit generally goes to stable state 11, with Q1 Q2 = 11. The apparent oscillation between states 01 and 10 when X1 X2 = 11 may not occur in practice, because it contains a critical race that tends to force the circuit into stable state 11.When X1 X2 = 01 or 10, the Q output corresponding to the HIGH input will oscillate, while the other output remains HIGH .Whether this circuit is useful is a matter of opinion.7.71When X =1, the circuit was supposed to “count” through its eight states in Gray-code order. When X =0, itremains in the current state. If this were the case, I suppose it could be used as a 3-bit random number genera-tor. However, I messed up on the logic diagram and the circuit actually does something quite different and completely useless, compared to what I intended when I wrote the problem. Someday I’ll fix this problem.Also, metastability may occur when X is changed from 1 to 0. 7.79Figure X5.59 requires two “hops” for each input change. Figure 7–66 is faster, requiring only one hop for eachinput change. On the other hand, Figure 7–66 cannot be generalized for n >2.7.90Either this exercise is a joke, or a correct answer is much too dangerous to publish. Nevertheless, Earl Levineoffers two possible answers:(Stable output)Was the last answer to this question “yes”?(Oscillating output)Was the last answer to this question “no”?X2X1Q1Q2Y1∗Y2∗Y1Y2Y1X1Y1⋅()X2Y2⋅()′⋅[]′=X1′Y1′X2Y2⋅++=Y2X2Y2⋅()X1Y1⋅()′⋅[]′=X2′Y2′X1Y1⋅++=Q1Y1=Q2Y2=X1X2Y1Y2000111100011111111 0111101011 1111101101 1011110101Y1*Y2*。

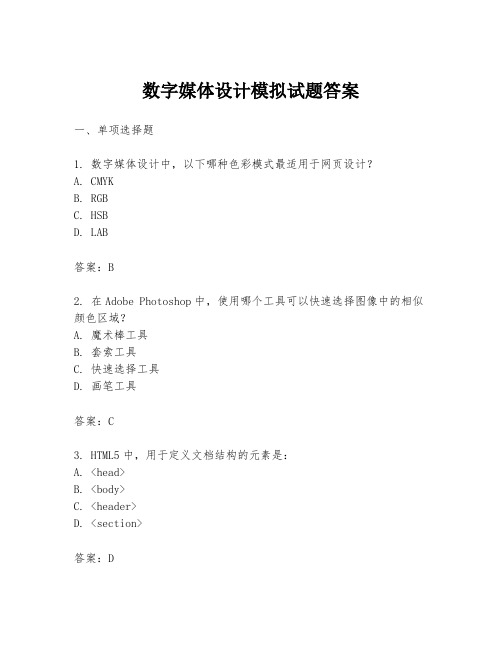

数字媒体设计模拟试题答案

数字媒体设计模拟试题答案一、单项选择题1. 数字媒体设计中,以下哪种色彩模式最适用于网页设计?A. CMYKB. RGBC. HSBD. LAB答案:B2. 在Adobe Photoshop中,使用哪个工具可以快速选择图像中的相似颜色区域?A. 魔术棒工具B. 套索工具C. 快速选择工具D. 画笔工具答案:C3. HTML5中,用于定义文档结构的元素是:A. <head>B. <body>C. <header>D. <section>答案:D4. CSS中,哪个属性用于设置元素的背景图片?A. background-colorB. background-imageC. background-positionD. background-repeat答案:B5. 在数字媒体设计中,以下哪个术语描述的是用户界面的直观性和易用性?A. 可用性B. 可访问性C. 可读性D. 可扩展性答案:A二、多项选择题1. 在Adobe Illustrator中,以下哪些工具可以用于创建矢量图形?A. 钢笔工具B. 铅笔工具C. 画笔工具D. 形状工具答案:A、B、D2. 以下哪些原则是良好用户界面设计的关键要素?A. 一致性B. 反馈C. 容错性D. 简洁性答案:A、B、C、D3. 在数字媒体设计项目中,团队成员可能包括哪些角色?A. 项目经理B. 用户体验设计师C. 前端开发工程师D. 数据分析师答案:A、B、C三、判断题1. 所有的网页设计都应该优先考虑搜索引擎优化(SEO)。

答案:错误2. 动画在用户界面设计中仅用于娱乐目的。

答案:错误3. 用户体验(UX)设计专注于提高产品的功能性和性能。

答案:错误四、简答题1. 请简述响应式网页设计的基本原理及其对用户体验的影响。

答:响应式网页设计是一种设计方法,它使得网页能够根据不同的设备和屏幕尺寸自动调整布局。

其基本原理是通过使用流体网格、灵活的图片和媒体查询等技术,确保网页内容在任何设备上都能清晰、完整地展示。

数字设计原理与实践第四版课后习题答案

数字设计原理与实践 (第四版 )_课后习题答案数字设计原理与实践 (第四版) 是一本广泛使用于电子工程、计算机科学等领域的教材,它介绍了数字电路的基础知识和设计方法。

课后习题是巩固学习内容、提高理解能力的重要部分。

下面是一些课后习题的答案,供参考。

第一章绪论1. 什么是数字电路?数字电路是一种使用二进制数表示信息并通过逻辑门实现逻辑功能的电路。

2. 简述数字系统的设计过程。

数字系统的设计过程包括需求分析、系统规格说明、逻辑设计、电路设计、测试和验证等步骤。

3. 简述数字电路的分类。

数字电路可以分为组合逻辑电路和时序逻辑电路两类。

组合逻辑电路的输出只取决于当前输入,时序逻辑电路的输出还受到过去输入的影响。

4. 什么是门电路?门电路是由逻辑门组成的电路,逻辑门是实现逻辑运算的基本模块。

第二章组合逻辑电路设计基础1. 简述一下布尔代数的基本概念。

布尔代数是一种用于描述逻辑运算的数学系统。

它包括逻辑变量、逻辑表达式、逻辑运算等概念。

2. 简述编码器和译码器的功能和应用。

编码器用于将多个输入信号转换为较少的输出信号,译码器则将少量输入信号转换为多个输出信号。

它们常用于数据压缩、信号传输和地址译码等应用中。

3. 简述多路选择器的功能和应用。

多路选择器根据选择信号选择其中一个输入信号并输出,它可以实现多个输入信号的复用和选择。

它常用于数据选择、信号传输和地址译码等应用中。

第三章组合逻辑电路设计1. 简述组合逻辑电路的设计方法。

组合逻辑电路的设计方法包括确定逻辑功能、编写逻辑表达式、绘制逻辑图和验证电路正确性等步骤。

2. 请设计一个3位二进制加法器。

一个3位二进制加法器可以通过将两个2位二进制加法器和一个与门连接而成。

3. 简述半加器和全加器的功能和应用。

半加器用于实现两个二进制位的相加,它的输出包括和位和进位位。

全加器则用于实现三个二进制位的相加,它的输出包括和位和进位位。

它们常用于二进制加法器的设计。

第四章时序逻辑电路设计基础1. 简述触发器的功能和应用。

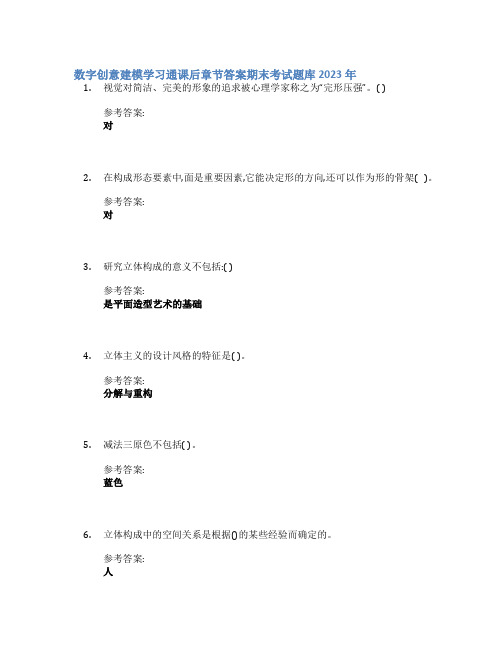

数字创意建模学习通课后章节答案期末考试题库2023年

数字创意建模学习通课后章节答案期末考试题库2023年1.视觉对简洁、完美的形象的追求被心理学家称之为“完形压强”。

( )参考答案:对2.在构成形态要素中,面是重要因素,它能决定形的方向,还可以作为形的骨架( )。

参考答案:对3.研究立体构成的意义不包括:( )参考答案:是平面造型艺术的基础4.立体主义的设计风格的特征是( )。

参考答案:分解与重构5.减法三原色不包括( )。

参考答案:蓝色6.立体构成中的空间关系是根据()的某些经验而确定的。

参考答案:人7.色彩的层次是指()。

参考答案:色彩表现上的前后距离和空间感,包括平面层次和实体层次两种8.金字塔造型可以看成是瓦楞折的变异构成。

( )参考答案:错9.立体的三种基本视图不包括:()。

参考答案:透视图10.光的三原色称之为( )。

参考答案:加法混合11.在Web上使用的图像格式有()。

参考答案:GIF/JPEG/PNG12.具象具备( )特性。

参考答案:明显的可识别性13.平面构成中,基本形或骨骼渐变构成至少要有()以上的变化才有渐变感。

参考答案:三个14.在立体构成中,线是具有长度、宽度和深度三度空间的实体线,不仅有粗细、长短的变化,它还有软与硬的区别。

( )参考答案:对15.使用RGB模式的图像中,呈现红色的组合是()。

参考答案:R200/G30/B3016.科学家们经过长期的探索和研究,认为能组合出各种色彩的最基本的色是( )。

参考答案:三原色17.加法指()群化组合构成的加工方法。

参考答案:单体18.在空间构成中可细分为()。

参考答案:二维空间的平面构成、色彩构成与三维空间的立体构成19.基本形是指构成图形的基本元素单位,是构成一个重复式彼此关联的符合形象的单位。

( )参考答案:对20.近似的表现是一种形体间的轻度差异。

( )参考答案:对21.近似的表现是一种()。

参考答案:轻微的差异22.美的表现形式,从总体可归纳为两大类:()和打破常规的美。

数字设计基础与应用第版第章习题解答完整版

数字设计基础与应用第版第章习题解答HEN system office room 【HEN16H-HENS2AHENS8Q8-HENH1688】第1章 数字逻辑基础1-1 将下列二进制数转换为十进制数。

(1) 2(1101) (2) 2(10110110) (3) 2(0.1101) (4) 2(11011011.101) 解(1)3210210(1101)12120212(13)=⨯+⨯+⨯+⨯=(2)75421210(10110110)1212121212(182)=⨯+⨯+⨯+⨯+⨯=(3) 124210(0.1101)1212120.50.250.0625(0.8125)---=⨯+⨯+⨯=++= (4) 76431013210(11011011.101)22222222 12864168210.50.125 (219.625)--=+++++++=+++++++=1-2 将下列十进制数转换为二进制数和十六进制数(1) 10(39) (2) 10(0.625) (3) 10(0.24) (4) 10(237.375) 解(1)10216(39)(100111)(27)== (2) 10216(0.625)(0.101)(0.A)==(3)近似结果: 16210)3.0()00111101.0()24.0(D =≈ (4) 10216(237.375)(1110'1101.011)(0ED.6)==1-3 将下列十六进制数转换为二进制数和十进制数(1) 16(6F.8) (2) 16(10A.C) (3) 16(0C.24) (4) 16(37.4) 解(1) 16210(6F.8)(1101111.1)(111.5)==(2) 16210(10A.C)(1'0000'1010.11)(266.75)== (3) 16210(0C.24)(1100.0010'01)(12.140625)== (4) 16210(37.4)(11'0111.01)(55.25)== 1-4 求出下列各数的8位二进制原码和补码(1) 10(39)- (2) 10(0.625) (3) 16(5B) (4) 2(0.10011)- 解(1)10(39)(1'0100111)(1'1011001)-==原码补码 (2) (0.1010000)(0.1010000)==10原码补码(0.625) (3) 16(5B)(01011011)(01011011)==原码补码(4) 2(0.10011)(1.1001100)(1.0110100)-==原码补码1-5 已知10X (92)=-,10Y (42)=,利用补码计算X +Y 和X -Y 的数值。

数字设计:原理与实践第五版习题答案

数字设计:原理与实践第五版习题答案第一章:数字系统基础1. 哪些数学符号代表布尔逻辑运算?分别代表哪些逻辑操作?布尔逻辑运算包括与(AND)、或(OR)、非(NOT)、异或(XOR)等运算。

它们的对应数学符号表示如下:•与(AND):$\\cdot$ 或 $\\land$•或(OR):+或 $\\lor$•非(NOT):$\\overline{A}$ 或eee•异或(XOR):$\\oplus$2. 简述数字系统的信号表示和信号处理单元。

数字系统的信号表示使用离散量来表示连续或离散的信号,其中离散量指代具有离散数值的量。

信号处理单元是指对输入信号进行处理和操作的硬件模块,用于实现特定的功能或执行特定的任务。

3. 什么是布尔函数?它可以用哪些方法表示?布尔函数是指以布尔逻辑运算为基础,将一个或多个布尔变量映射为单一布尔值的函数。

布尔函数可以用真值表、逻辑表达式和逻辑图等方法表示。

4. 简述数字系统的设计方法。

数字系统的设计方法包括以下几个步骤:1.确定问题的需求和约束条件。

2.将问题抽象为逻辑功能的实现。

3.设计逻辑电路并进行仿真验证。

4.实现电路设计并进行实验验证。

5.优化电路设计并进行性能评估。

6.完成设计文档和报告。

第二章:组合逻辑电路设计1. 什么是组合逻辑电路?简述其基本特征。

组合逻辑电路是指将组合逻辑块进行组合形成的电路,其输出仅依赖于当前的输入。

它的基本特征包括:•输入输出之间无时序关系。

•只有组合逻辑块,没有存储元件。

•输出仅取决于当前输入。

2. 简述逻辑门的功能和特点。

逻辑门是实现布尔逻辑运算的基本构件,其功能和特点如下:•与门(AND):多个输入信号全部为高时,输出高;否则输出低。

•或门(OR):多个输入信号有一个为高时,输出高;否则输出低。

•非门(NOT):输入信号为高时,输出低;否则输出高。

•异或门(XOR):多个输入信号中奇数个为高时,输出高;否则输出低。

3. 什么是选择器和解码器?选择器是一种组合逻辑电路,根据选择信号将一组输入信号中的某一个作为输出。

数字设计(Digital Design)习题解答4

1 1 0 1 1 1 1 1 1 1 0 1 1 0 0 0

4.9 (a) F = X ′ ⋅ Y + Y ′ ⋅ X = ( X + Y ) ⋅ ( X ′ + Y ′ ) (b) F = A ⋅ B = ( A + B ) ⋅ ( A + B ′ ) ⋅ ( A ′ + B ) 4.12 (1) Including inverters makes the problem too difficult. (2) In modern PLD-based designs, inverters do cost nothing and really can be ignored. 4.13

XY Z 0 1 1 1 Y F=X⋅Y+Z (a) (b) 00 01 11 1 1 1 Z Z X 10 X⋅Y YZ W′ ⋅ Y′ ⋅ Z 00 01 11 Y 10 1 X F = W′ ⋅ X + X′ ⋅ Y′ ⋅ Z + X ⋅ Y 1 X⋅Y 1 WX 00 01 1 1 1 1 1 Z 11 W 10 W′ ⋅ X X′ ⋅ Y′ ⋅ Z′

Y+Z

Y

4.19

W′ ⋅ Y′ ⋅ Z (a) WX 00 YZ 00 01 11 Y 10 X F = W ′ ⋅ Y′ ⋅ Z + W ′ ⋅ X′ ⋅ Z + W ⋅ X ⋅ Y + W′ ⋅ X′ ⋅ Y′ or X′ ⋅ Y′ ⋅ Z′ 1 W⋅X⋅Y W′ ⋅ X′ 1 1 1 1 Z d Y 10 1 W⋅Y⋅Z X 11 d d 1 W 01 11 10 d X′ ⋅ Y′ ⋅ Z′ (b) WX 00 YZ 00 01 1 1 W 01 11 10 1 d Z X′ ⋅ Y′ X′ ⋅ Z

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5–1E X E R C I S E S O L U T I O N S COMBINATIONAL LOGIC DESIGN PRINCIPLES55.4READY ′ is an expression, with ′ being a unary operator. Use a name like READY_L or /READY instead.5.8Both LOW -to-HIGH and HIGH -to-LOW transitions cause positive transitions on the outputs of three gates (every second gate), and negative transitions on the other three. Thus, the total delay in either case isSince and for a 74LS00 are identical, the same result is obtained using a single worst-case delay of 15 ns.5.12The smallest typical delay through one ’LS86 for any set of conditions is 10 ns. Use the rule of thumb, “mini-mum equals one-fourth to one-third of typical,” we estimate 3 ns as the minimum delay through one gate.Therefore, the minimum delay through the four gates is estimated at 12 ns.The above estimate is conservative, as it does not take into account the actual transitions in the conditions shown. For a LOW -to-HIGH input transition, the four gates have typical delays of 13, 10, 10, and 20 ns, a total of 53 ns, so the minimum is estimated at one-fourth of this or 13 ns. For a HIGH -to-LOW input transition, the four gates have typical delays of 20, 12, 12, and 13 ns, a total of 57 ns, so the minimum is estimated at 14 ns.5.15 A decoder with active-low outputs ought to be faster, considering that this decoder structure can be imple-mented directly with inverting gates (which are faster than noninverting) as shown in Figures 5–35 and 5–37.5.16The worst-case ’138 output will have a transition in the same direction as the worst-case ’139 output, so we uset pHL numbers for both, which is the worst combination. The delay through the ’139 is 38 ns, and from thet p 3t pLH(LS00)3t pHL(LS00)+=315⋅315⋅+=90 ns=t pLH t pHL5–2DIGITAL CIRCUITSactive-low enable input of the ’138 is 32 ns, for a total delay of 70 ns. Using “worst-case” numbers for the parts and ignoring the structure of the circuit, an overly pessimistic result of 79 ns is obtained.We can also work the problem with 74HCT parts. Worst-case delay through the ’139 is 43 ns, and from the active-low enable input of the ’138 is 42 ns, for a total delay of 85 ns. Ignoring the structure of the circuit, an overly pessimistic result of 88 ns is obtained.We can also work the problem with 74FCT parts. Worst-case delay through the ’139 is 9 ns, and from the active-low enable input of the ’138 is 8 ns, for a total delay of 17 ns. Ignoring the structure of the circuit, a slightly pessimistic result of 18 ns is obtained.Finally, we can work the problem with 74AHCT parts. Worst-case delay through the ’139 is 10.5 ns, and fromthe active-low enable input of the ’138 is 12 ns, for a total delay of 22.5 ns. Ignoring the structure of the circuit,a slightly pessimistic result of 23.5 ns is obtained. 5.195.21Both halves of the ’139 are enabled simultaneously when EN_L is asserted. Therefore, two three-state driverswill be enabled to drive SDATA at the same time. Perhaps the designer forgot to put an extra inverter on the signal going to 1G or 2G , which would ensure that exactly one source drives SDATA at all times.5.22The total delay is the sum of the decoding delay through the 74LS139, enabling delay of a 74LS151, and delaythrough a 74LS20: .5.25The worst-case delay is the sum of the delays through an ’LS280, select-to-output through an ’LS138, andthrough an ’LS86: .5.30The worst-case delay is the sum of four numbers:•In U1, the worst-case delay from any input to C4 (22 ns).•In U2, the worst-case delay from C0 to C4 (22 ns).•In U3, the worst-case delay from C0 to C4 (22 ns).•In U4, the worst-case delay from C0 to any sum output (24 ns).Thus, the total worst-case delay is 90 ns.5.35With the stated input combination, Y5_L is LOW and the other outputs are HIGH . We have the following cases:(a)Negating G2A_L or G2B_L causes Y5_L to go HIGH within 18 ns.(b)Negating G1 causes Y5_L to go HIGH within 26 ns.(c)Changing A or C causes Y5_L to go HIGH within 27 ns (the change propagates through 3 levels of logic internally), and causes Y4_L or Y1_L respectively to go LOW within 41 ns (2 levels).(d)Changing B causes Y5_L to go HIGH within 20 ns (2 levels), and causes Y7_L to go LOW within 39 ns (3levels). The delays in the ’LS138 are very strange—the worst-case for 3 levels is shorter than for 2 levels!383015++83ns =504130++121 ns =t pHLEXERCISE SOLUTIONS5–3 5.395.46The inputs are active low and the outputs are active high in this design.5–4DIGITAL CIRCUITS 5.47EXERCISE SOLUTIONS5–5 5.54An internal logic diagram for the multiplexer is shown below.5–6DIGITAL CIRCUITSA truth table and pin assignment for the mux are shown below.The mux can be built using a single PLD, a PAL20L8 or GAL20V8; the pin assignment shown above is based on the PLD. The corresponding ABEL program, MUX3BY5.ABL , is shown below. module Mux_3x5title '5-Bit, 3-Input Multiplexer J. Wakerly, Marquette University'MUX3BY5 device 'P20L8';" Input pinsI1D0, I1D1, I1D2 pin 23, 1, 2;I2D0, I2D1, I2D2 pin 3, 4, 5;I3D0, I3D1, I3D2 pin 6, 7, 8;I4D0, I4D1, I4D2 pin 9, 10, 11;I5D0, I5D1, I5D2 pin 18, 17, 16;S0, S1 pin 13, 14;" Output pinsY1, Y2, Y3, Y4, Y5 pin 22, 21, 20, 19, 15;" Set definitionsBUS0 = [I1D0,I2D0,I3D0,I4D0,I5D0];BUS1 = [I1D1,I2D1,I3D1,I4D1,I5D1];BUS2 = [I1D2,I2D2,I3D2,I4D2,I5D2];OUT = [Y1, Y2, Y3, Y4, Y5 ];" ConstantsSEL0 = ([S1,S0]==[0,0]);SEL1 = ([S1,S0]==[0,1]);SEL2 = ([S1,S0]==[1,0]);IDLE = ([S1,S0]==[1,1]);equationsOUT = SEL0 & BUS0 # SEL1 & BUS1 # SEL2 & BUS2 # IDLE & 0;end Mux_3x5InputsOutputsS1S01Y 2Y 3Y 4Y 5Y 001D02D03D04D05D0011D12D13D14D15D1101D22D23D24D25D21100000EXERCISE SOLUTIONS5–7 5.55This is the actual circuit of a MUX21H 2-input multiplexer cell in LSI Logic’s LCA 10000 series of CMOSgate arrays. When S is 0, the output equals A; when S is 1, the output equals B.5.605.67The ’08 has the same pinout as the ’00, but its outputs are the opposite polarity. The change in level at pin 3 ofU1 is equivalent to a change at pin 4 of U2 (the input of an X OR tree), which is equivalent in turn to a change at pin 6 of U2 (the parity-generator output). Thus, the circuit simply generated and checked odd parity instead of even.The change in level at pin 6 of U1 changed the active level of the ERROR signal.5.69This problem is answered in Section 5.9.3 of the text, which makes it a silly question.5–8DIGITAL CIRCUITS5.755.79The function has 65 inputs, and the worst 65-input function (a 65-input parity circuit) has terms in theminimal sum-of-products expression. Our answer can’t be any worse than this, but we can do better.The expression for has 3 product terms: The expression for is If we substitute our previous expression for c1 in the equation above and “multiply out,” we get a result with product terms. Let us assume that no further reduction is possible.Continuing in this way, we would find that the expression for has product terms and, in general, the expression for has product terms.Thus, the number of terms in a sum-of-products expression for is no more than , fewer if minimiza-tion is possible.2651–c 1c 1c 0x 0⋅c 0y 0⋅x 0y 0⋅++=c 2c 2c 1x 1⋅c 1y 1⋅x 1y 1⋅++=331++7=c 3771++15=c i 2i 1+1–c 322331–EXERCISE SOLUTIONS5–9 5.805–10DIGITAL CIRCUITS5.825.915.93The obvious solution is to use a 74FCT682, which has a maximum delay of 11 ns to its output. How-ever, there are faster parts in Table 5–3. In particular, the 74FCT151 has a delay of only 9 ns from any select input to Y or . To take advantage of this, we use a ’138 to decode the SLOT inputs statically and apply the resulting eight signals to the data inputs of the ’151. By applying GRANT[2–0] to the select inputs of the ’151, we obtain the MATCH_L output (as well as an active-high MATCH, if we need it) in only 9 ns!。