电子技术基础复习题-时序逻辑电路

阎石《数字电子技术基础》(第6版)考研真题精选-第6章 时序逻辑电路【圣才出品】

第6章时序逻辑电路一、选择题1.下列逻辑电路中哪个是时序逻辑电路:()。

[江苏大学2016研]A.二进制译码器B.二进制加法器C.移位寄存器D.数据选择器【答案】C【解析】ABD三项都属于组合逻辑电路,C项移位寄存器是由触发器组成的,具有存储功能,它属于时序逻辑电路。

2.同步时序电路和异步时序电路比较,其差异在于后者()。

[重庆大学2015研] A.没有触发器B.没有统一的时钟控制C.没有稳定状态D.输出只与内部状态有关【答案】B【解析】A项是组合逻辑电路和时序逻辑电路的区别;C项是无稳态电路与稳态电路的区别;D项是米勒型电路和摩尔型电路的区别。

3.对于状态表6-1,下列说法正确的是:()。

[北京邮电大学2015研]表6-1A.状态A和B肯定等价B.状态D和E肯定等价C.状态A和C肯定等价D.状态B和F肯定等价【答案】B【解析】根据状态表6-1可知,状态D和E在输入0后,次态都为自身且输出Z=0,而在输入1后,次态都变为C且输出Z=0。

所以,可以视为两者状态等价,同样的分析方法用于A、C、D三项,可以发现这三个选项是错误的。

二、填空题1.时序电路中“等价状态”是______,在实际应用中起______作用。

[重庆大学2014研]【答案】相同的输入下,输出相同且次态也相同;化简【解析】状态等价是指在相同的输入变量条件下,次态相同且输出也相同,等价的状态主要用于化简状态转换表,也就是减少电路的状态数量,可以优化构成相应电路的硬件结构。

2.一个模值为6的计数器,状态转移图如图6-1所示,若初始状态为000,则经过100个CP脉冲后,其状态为______。

[北京邮电大学2015研]图6-1【答案】110【解析】每经过一个CP脉冲,计数器的状态按照顺序变化一次,100/6=16···4,所以经过了100CP脉冲后,计数器循环了16个完整计数周期,然后又进行了4次状态变化,所以此时状态为110。

电子技术基础-触发器和时序逻辑电路

常用集成边沿触发器有: 双JK边沿触发器:CT3112/4112、CT2108等。 单JK边沿触发器:CT2101/2102(下降沿触发)、CT1070(上 升沿触发)。

8.2.1 时序逻辑电路的概述

时序逻辑电路:含有具有记忆能力的存储器件,任何一个 时刻的输出状态不仅取决于当时的输入信号,还与电路的原状 态有关。

X1

Y1

Xn

组合逻辑电路

Ym

… …

… …

Q1

W1

存储电路

Qj

Wk

8.2.2 时序逻辑电路的分析 步骤:

(1)由逻辑图写出方程式(时钟方程、输出方程、 驱动方程、状态方程)。 (2)列写状态转换真值表。

3.有记忆功能:在无外来触发信号作用时, 电路将保持原状态不变。

4.有计数功能:来一个计数脉冲,电路翻转 一次,计数一次。

5.缺点:计数时存在空翻问题。

8.1.3 JK触发器

一种功能完善,应用极广泛的电路。 Q Q

1.电路组成

两个可控 RS触发器通过一源自从触发器个非门(反相器)相连,分别称

SCR

主触发器和从触发器。

111

0

111

000

1

(6)状态图

(7)时序图

2.异步时序电路分析举例

例8.5 图示为74LS290主体电路,试分析这部分电路的逻 辑功能。

[解] (1)三个异步触发的下降延JK触 发器:CPB控制FF0的CP,Q1控 制FF1的CP,Q2控制FF2的CP。

《电子技术基础》第6章时序逻辑电路的分析与设计-1

6.1 时序逻辑电路的基本概念

1. 时序电路的一般化模型

I1 Ii

O1

Oj

Sm 特点: Ek 1)时序逻辑电路由组合电路(逻辑门)和存储电路( 一般由触 发器构成) 组成。 2)电路的输出由输入信号和原来的输出状态共同决定.

4/9/2019 12:58:22 PM

… … S1 …

… E1 … …

组合电路

1/0 1/0 1/0

01 01 0/0 10 10

00

11

10

01

0/1 11 11

1/1

0/0

电路进行减1计数 。 电路功能:可逆4进制计数器 Y可理解为进位或借位端。

4/9/2019 12:58:22 PM

D2 Q

n 1

(3) 根据状态方程组和输出方程列出状态表

Sn→Sn+1

S = Q2Q1Q0

Q

n 1 0

Q Q

n 1

n 0

Q

n 1 1

Q

n 0

n 1 Q2 Q1n

状态表

n 1 n n 1 n 1 n Q Q Q Q Q Q 0 1 0 1 2

n 2

(4) 画出状态图 0 1 0 1 0 1 0 1 1 0 0 0 1 0 0 0

存储电路

时序电 路输入 信号

I1

Ii

O1 Oj

组合电路

时序电 路输出 信号

存储电路激 励信号(触发 器的输入)

… …

… …

存储电路输 出信号 (电路状态S) 各触发器的状态Q

S1 Sm …

E1

… Ek

存储电路

各信号之间的逻辑关系方程组为:

O = F1(I,Sn) E = F2

数字电子技术基础-第六章_时序逻辑电路(完整版)

T0 1

行修改,在0000 时减“1”后跳变 T1 Q0 Q0(Q3Q2Q1)

为1001,然后按

二进制减法计数

就行了。T2 Q1Q0 Q1Q0 (Q1Q2Q3 )

T3 Q2Q1Q0

50

能自启动

47

•时序图 5

分 频

10 分 频c

0

t

48

器件实例:74 160

CLK RD LD EP ET 工作状态 X 0 X X X 置 0(异步) 1 0 X X 预置数(同步) X 1 1 0 1 保持(包括C) X 1 1 X 0 保持(C=0) 1 1 1 1 计数

49

②减法计数器

基本原理:对二进 制减法计数器进

——74LS193

异步置数 异步清零

44

(采用T’触发器,即T=1)

CLKi

CLKU

i 1

Qj

j0

CLKD

i 1

Qj

j0

CLK0 CLKU CLKD

CLK 2 CLKU Q1Q0 CLK DQ1Q0

45

2. 同步十进制计数器 ①加法计数器

基本原理:在四位二进制 计数器基础上修改,当计 到1001时,则下一个CLK 电路状态回到0000。

EP ET 工作状态

X 0 X X X 置 0(异步)

1 0 X X 预置数(同步)

X 1 1 0 1 保持(包括C)

X 1 1 X 0 保持(C=0)

1 1 1 1 计数

39

同步二进制减法计数器 原理:根据二进制减法运算 规则可知:在多位二进制数 末位减1,若第i位以下皆为 0时,则第i位应翻转。

Y Q2Q3

电子技术基础 作业题10

电子技术基础作业题10网络收集仅供参考没有讲过的内容可以不做。

一、填空题:(每空0.5分,共33分)1、时序逻辑电路按各位触发器接受时钟脉冲控制信号的不同,可分为同步时序逻辑电路和异步时序逻辑电路两大类。

在异步时序逻辑电路中,各位触发器无统一的时钟脉冲控制信号,输出状态的变化通常不是同一时刻发生的。

2、根据已知的逻辑电路,找出电路的输入和其现态及输出之间的关系,最后总结出电路逻辑功能的一系列步骤,称为时序逻辑电路的分析。

3、当时序逻辑电路的触发器位数为n,电路状态按二进制数的自然态序循环,经历的独立状态为2n个,这时,我们称此类电路为二进制计数器。

二进制计数器除了按同步、异步分类外,按计数的加减规律还可分为加计数器、减计数器和可逆计数器。

4、在十进制计数器中,要表示一位十进制数时,至少要用四位触发器才能实现。

十进制计数电路中最常采用的是8421 BCD代码来表示一位十进制数。

5、时序逻辑电路中仅有存储记忆电路而没有逻辑门电路时,构成的电路类型通常称为莫尔型时序逻辑电路;如果电路中不但除了有存储记忆电路的输入端子,还有逻辑门电路的输入时,构成的电路类型称为米莱型时序逻辑电路。

6、分析时序逻辑电路时,首先要根据已知逻辑的电路图分别写出相应的驱动方程、输出方程和次态方程,若所分析电路属于异步时序逻辑电路,则还要写出各位触发器的时钟脉冲方程。

7、时序逻辑电路中某计数器中的无效码,若在开机时出现,不用人工或其它设备的干预,计数器能够很快自行进入有效循环体,使无效码不再出现的能力称为自启动能力。

8、在分频、控制、测量等电路中,计数器应用得非常广泛。

构成一个六进制计数器最少要采用三位触发器,这时构成的电路有6个有效状态,2个无效状态。

9、寄存器可分为数码寄存器和移位寄存器,集成74LS194属于双向移位寄存器。

用四位移位寄存器构成环行计数器时,有效状态共有4个;若构成扭环计数器时,其有效状态是8个。

10、寄存器是可用来存放数码、运算结果或指令的电路,通常由具有存储功能的多位触发器组合起来构成。

电工与电子技术习题参考答案第9章

第9章时序逻辑电路习题解答9.1 d R端和d S端的输入信号如题9.1图所示,设基本RS触发器的初始状态分别为1和0两种情况,试画出Q端的输出波形。

题9.1图解:9.2 同步RS触发器的CP、R、S端的状态波形如题9.2图所示。

设初始状态为0和1两种情况,试画出Q端的状态波形。

题9.2图解:9.3 设主从型JK触发器的初始状态为0,J、K、CP端的输入波形如题9.3图所示。

试画出Q端的输出波形(下降沿触发翻转)。

解:如题9.3图所示红色为其输出波形。

第9章时序逻辑电路225题9.3图9.4 设主从型JK触发器的初始状态为0,J、K、CP端输入波形如题9.4图所示。

试画出Q端的输出波形(下降沿触发翻转)。

如初始状态为1态,Q端的波形又如何?解:如题9.4图所示红色为其输出波形。

题9.4图9.5 设维持阻塞型D触发器的初始状态为0,D端和CP端的输入波形如题9.5图所示,试画出Q端的输出波形(上升沿触发翻转)。

如初始状态为1态,Q端的波形又如何?解:如题9.5图所示红色为其输出波形。

第9章时序逻辑电路226题9.5图9.6 根据CP时钟脉冲,画出题9.6图所示各触发器Q端的波形。

(1)设初始状态为0;(2)设初始状态为1。

(各输入端悬空时相当于“1”)题9.6图解:第9章时序逻辑电路2279.7 题9.7图所示的逻辑电路中,有J和K两个输入端,试分析其逻辑功能,并说明它是何种触发器。

题9.7图=⋅⋅⋅=⋅+⋅解:由图得D Q F J Q Q F J QJ K Q n D Q n+10 0 0 0 00 0 1 1 10 1 0 0 00 1 1 0 01 0 0 1 11 0 1 1 11 1 0 1 11 1 1 0 0此电路为D触发器和与非门组成的上升沿触发的JK触发器。

9.8 根据题9.8图所示的逻辑图和相应的CP、d R、D的波形,试画出Q1和Q2端的输出波形。

设初始状态Q1=Q2=0。

题9.8图解:第9章时序逻辑电路2289.9 试用4个D触发器组成一个四位右移移位寄存器。

大学课程《数字电子技术基础》试题及答案

大学课程《数字电子技术基础》试题及答案一、填空题时序逻辑电路1.所谓时序逻辑电路是指电路的输出不仅与当时的有关,而且与电路的有关。

答:输入,历史状态2.含有触发器的数字电路属于逻辑电路。

答:时序3.计数器按照各触发器是否同时翻转分为式和式两种。

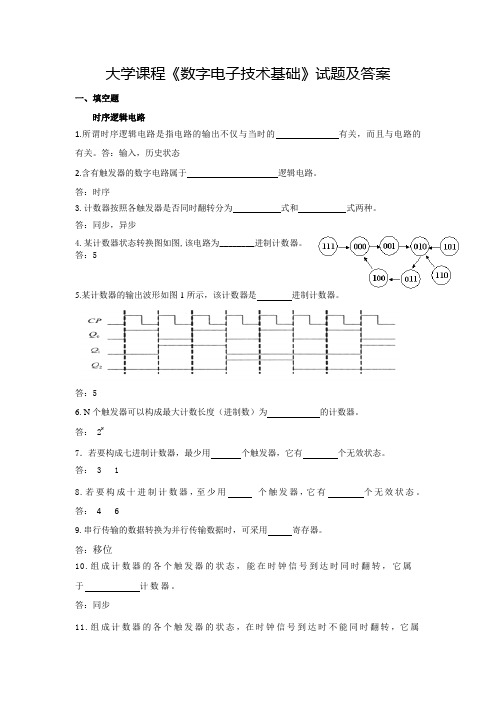

答:同步,异步4.某计数器状态转换图如图,该电路为________进制计数器。

答:55.某计数器的输出波形如图1所示,该计数器是进制计数器。

答:56. N个触发器可以构成最大计数长度(进制数)为的计数器。

答: 2N7.若要构成七进制计数器,最少用个触发器,它有个无效状态。

答: 3 18.若要构成十进制计数器,至少用个触发器,它有个无效状态。

答:4 69.串行传输的数据转换为并行传输数据时,可采用寄存器。

答:移位10.组成计数器的各个触发器的状态,能在时钟信号到达时同时翻转,它属于计数器。

答:同步11.组成计数器的各个触发器的状态,在时钟信号到达时不能同时翻转,它属于计数器。

答:异步12.两片中规模集成电路10进制计数器串联后,最大计数容量为()位。

答:10013.驱动共阳极七段数码管的译码器的输出电平为()有效。

答:低二、选择题时序逻辑电路1.时序逻辑电路中一定包含。

A、触发器B、组合逻辑电路C、移位寄存器D、译码器答:A2.在同步计数器中,各触发器状态改变时刻()。

A、相同B、不相同C、与触发器有关D、与电平相同答:A3.同步时序逻辑电路和异步时序逻辑电路比较,其差别在于后者。

A.没有触发器B. 没有统一的时钟脉冲控制C.没有稳定状态D. 输出只与内部状态有关答:B4.有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP 作用下,四位数据的移位过程是()。

A. 1011--0110--1100--1000--0000B. 1011--0101--0010--0001--0000C. 1011--1100--1101--1110--1111D. 1011--1010--1001--1000—0111答:A Array 5.某计数器的状态转换图如右:其计数的容量为( )A.8 B. 5C. 4D. 3答:B6.同步时序逻辑电路和异步时序逻辑电路比较,其差别在于后者。

《电工与电子技术》考试【 触发器和时序逻辑电路】题目类型【问答题】难度【易】

为什么触发器能寄存0或1?

答案:

因为

问题【3】删除修改

基本RS触发器、钟控触发器和边沿触发器在什么时候会因为干扰而可能产生误动作?

答案:

基本RS触发器在任何时候都会受干扰而产生误触发;钟控触发器在CP脉冲高电平期间会因干扰而误触发;而边沿触发器只有在CP脉冲上升沿或是下降沿时才会受干扰产生误触发。

问题【4】删除修改

触发器的逻辑功能有哪几种描述方法?

答案:

触发器的逻辑功能的描述方法有:真值表法;逻辑函数表达式;真值表法;波形图法和状态转换图法等5种。

问题【5】删除修改

钟控触发器的电路结构型式,逻辑功能及触发方式三者之间有什么关系?逻辑功能相同的触发器,触发方式是否相同?

答案:

电路结构不同,逻辑功能和触发器方式便可能不同。但同一种逻辑功能的触发器,可以采用不同的电路结构,便有不同的触发方式。因此,逻辑功能相同的触发器,触发方式不一定相同。

问题【9】删除修改

什么是并行输入、串行输入、并行输出、串行输出?

答案:

并行输入,即当寄存指令来到时,待寄存的各位数据同时存放到各位触发器;串行输入,即在移位脉冲的作用下,待存数据逐位向左或向右移入各触发器;并行输出,即当取指指令来到时,被存放的数据同时在各位触发器的输出端取出;串行输出,即在移位脉冲的作用下,被存数据由最高位或最低位逐位取出。

问题【10】删除修改

什么是异步计数器,什么是同步计数器两者有什么区别?

答案:

异步计数器,即计数脉冲不是同时加到各位触发器的C端,因此各位触发器的翻转有先后次序,即是异步的。同步计数器,即计数脉冲是同时加到各位触发器的C端,因此各位触发器的翻转和计数脉冲同步。同步计数器运算速度快,可靠性高。而异步计数器不仅运算速度慢,而且可能产生误码,如由状态“0111”变到“1000”的过程实际上是111→0110→0100→0000→1000。同步计数器则在同一时刻由0111→1000。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《电子技术基础》复习题

时序逻辑电路

一、填空题:

1.具有“置0”、“置1”、“保持”和“计数功能”的触发器是()

2.触发器有门电路构成,但它不同门电路功能,主要特点是:()

型触发器的直接置0端Rd、置1端Sd的正确用法是()

4.按触发方式双稳态触发器分为:()

5.时序电路可以由()组成

6.时序电路输出状态的改变()

7.通常寄存器应具有()功能

8.通常计数器应具有()功能

9. M进制计数器的状态转换的特点是设初态后,每来()个CP时,计数器又重回初态。

10.欲构成能记最大十进制数为999的计数器,至少需要()个双稳触发器。

11. 同步时序逻辑电路中所有触发器的时钟端应()。

二、选择题:

1.计数器在电路组成上的特点是()

a)有CP输入端,无数码输入端 b) 有CP输入端和数码输入端 c) 无CP输入端,有数码输入端

2.按各触发器的状态转换与CP的关系分类,计数器可分为()计数器。

a)加法、减法和加减可逆 b)同步和异步 c)二、十和M进制

3. 按计数器的状态变换的规律分类,计数器可分为()计数器。

a)加法、减法和加减可逆 b)同步和异步 c)二、十和M进制

4 按计数器的进位制分类,计数器可分为()计数器。

a)加法、减法和加减可逆 b)同步和异步 c)二、十和M进制

5. n位二进制加法计数器有()个状态,最大计数值是()。

a)2n-1 b)2n c)2n-1

6.分析时序逻辑电路的状态表,可知它是一只()。

(a) 二进制计数器(b)六进制计数(c) 五进制计数器

7. 分析如图所示计数器的波形图,可知它是一只()。

(a) 六进制计数器(b) 七进制计数器(c) 八进制计数器

8、逻辑电路如图所示,当A=“0”,B=“1”时,C脉冲来到后JK触发器()。

(a) 具有计数功能(b) 保持原状态(c) 置“0” (d) 置“1”

9、逻 辑 电 路 如 图 所 示, 分 析 C ,S ,R 的 波 形,当 初 始 状 态 为“0”时, t 1 瞬 间 输 出 Q 为 ( )。

(a) “0” (b) “1” (c) Q n

10、555 集 成 定 时 器 电 路 如 图 所 示, 为 使 输 出 电 压 u O3 由 低 电 压 变 为 高 电 压, 则 输 入 端 6 和 2 的 电 压 应 满 足 ( )。

(a)u U I6CC <2

3,u U I2CC <1

3 (b)u U I6CC >2

3,u U I2CC >

1

3 (c)u U I6CC <2

3

,u U I2CC >

1

3

11、 逻 辑 电 路 如 图 所 示, 当 A=“0”,B=“1” 时,C 脉 冲 来 到 后 D 触 发 器 (

)。

(a) 具 有 计 数 功 能 (b) 保 持 原 状 态 (c) 置“0” (d) 置“1”

12、 时 序 逻 辑 电 路 如 图 所 示, 原 状 态 为“0 0”, 当 发 出 寄 存 和 取 出 指 令 后 的 新 状 态 为 ( )。

(a) 1 1

(b) 1 0

(c) 0 1

13、 分 析 某 时 序 逻 辑 电 路 状 态 表, 判 定 它 是( )。

(a) 二 进 制 计 数 器 (b) 十 进 制 计 数 器 (c) 其 它计 数 器

三、非客观题:

1.由555 集 成 定 时 器 组 成 的 电 路 如 图 所 示。

已 知U CC V =6 , R 1=2 k?,R 2= k?, C 1= μF ,C 2=33 μF ,C 3=100 μF ,合 上 开 关S ,8? 扬 声 器 发 出 声 响 , 试 分 别 计 算R P =0 和R P =100 k? 时 的 声 响 频 率。

2:已 知 逻 辑 电 路 图 及 C ,S D ,R D 的 波 形, 试 画 出 输 出Q 0,Q 1 的 波 形 (设Q 0,Q 1

的 初 始 状 态 均 为“0”)。

3、已 知 逻 辑 电 路 图 和 C 脉 冲 的 波 形 , 试 写 出 F 0 和F 1 的 逻 辑 式, 并 列 出 F 0,F 1的 状 态 表 (设Q 0,Q 1 初 始 状 态 均 为“0”

)。

4、试 列 出 如 下 所 示 逻 辑 电 路 图 的 状 态 表? 画 出 波 形 图, 并 指 出 是 什 么 类 型 的 计 数 器(设Q 0,Q 1 的 初 始 状 态 均 为“0”)。

5、列 出 逻 辑 电 路 图 的 状 态 表, 写 出 输 出F 的 逻 辑 式, 画 出 输 出Q 0,Q 1 及F 的 波 形 图, 计 算F 的 脉 宽 t W 和 周 期T (设 C 脉 冲 频 率 为1 kHz , 各 触 发 器 初 始 状 态 均 为“0”)。

6、非客观题:

已 知 逻 辑 电 路 图 及 C 脉 冲 波 形, 试 画 出 输 出 Q 0,Q 1 的 波 形(设Q 0,Q 1 的 初

始 状 态 均 为“0”)。

7、逻 辑 电 路 如 图 所 示,各 触 发 器 的 初 始 状 态 为“0”, 已 知C 脉 冲 的 波 形。

试 画 出 输 出Q 0,Q 1 和F 的 波 形 图。

8、

已 知 逻 辑 电 路 图 及 C 脉 冲 的波 形, 各 触 发 器 的 初 始 状 态 均 为 0, 画 出 输 出

Q 0,Q 1,Q 2 的 波 形。

9、逻 辑 电 路 如 图 所 示,各 触 发 器 的 初 始 状 态 为“0”, 若 已 知C 和A 的 波 形。

试 画 出Q 0,Q 1 的 波 形。

10、由555 集 成 定 时 器 组 成 的 电 路 如 图 所 示。

HL 为 信 号 灯,已 知U CC V =12

, R 1=27 k?,R 2=15 k?,R P =500 k?,C 1= μF ,C 2=50 μF ,C 3=50 μF 。

试 求: 当R P 的 阻 值

调 到 最 大 时, 信 号 灯HL 亮 和 灭的 时 间 为 多 少?

11、试分析下图电路的逻辑功能,并画出其状态转换图和工作波形。

(设触发器的初态为零)

《电子技术基础》复习题-时序逻辑电路参考答案

一、填空题: 1. JK 触发器 2.有记忆功能

3.有小圆圈时,不用时接高电平“1”;没有小圆圈时,不用时接低电平“0”

4.电平触发、主从触发和边沿触发

5.触发器或触发器和的组合门电路

6.与时序电路该时刻输入信号的状态和时序电路的原状态有关

7.存数、取数、清零与置数

8.清零、置数、累计CP 个数

9. M

10. 1099912=⇒≥-N N

11、连在一起

二、选择题: 1.(b )、2. (b ) 、 3. (a )、 4. (c) 、 5. (b )、 6.(c) 、7. (a )、 8、( b ) 9. (b) 、10、( a ) 、11、( a ) 、12、( b) 、13、( b )

三、非客观题:

1、 为谐振电路 R P k =100Ω时 f R R R C =

++=1

0720386122

.().P Hz

R f R R C P Hz ==

+=0

1

072355122

.().

2、

3、逻 辑 式:F Q Q F Q Q 001110==

状 态

4、首 先 根 据 各 触 发 器 的 激 励 函 数 表 达 式 画 出 波 形 图。

J Q 01=,"1"0=K ;

J Q 10=, K 11=""由 波 形 图 可 列 出 状 态 表。

由 状 态 表 可 知 这 是 一 个 三 进 制 计

数 器。

由 于 两 只 触 发 器 受 同 一C 脉 冲 控 制, 故 为 同 步 型。

且 数 值 是 增

加 的, 即 加 法 计 数 器, 因 此 可 知 这 是 一 只 同 步 三 进 制 加 法 计 数 器。

5、功 能 表 和 波 形 图 如 下, F =Q Q 01, 由 波 形 图 可 知:t W =2ms ,3ms 。

6、

状 态 表 波 形 图

7、

8、

状 态 表:

结 论:三 位 二 进 制 异 步 减 法 计 数 器 9、

10、信 号 灯HL 灭 的 时 间 为:t R C 1223

60707151050100525==⨯⨯⨯⨯=-... s s

信 号 灯HL 亮 的 时 间 为:

t R R R C 212207=++.()P =⨯⨯+⨯+⨯⨯⨯=-0727105001015105010193336.() s s

11、解:异步2位二进制加法计数器。

10

11

00

01。