EDA考试题目+答案

EDA训练STM32最小系统

EDA训练题目STM32最小系统班级 09电子(2)班学号200910330236姓名曹小迪时间2012-12-04景德镇陶瓷学院EDA训练任务书姓名曹小迪__ 班级__09电子(2)班指导老师金光浪设计课题:STM32最小系统设计任务与要求查找一个感兴趣的电工电子技术应用电路,要求电子元件50个以上,根据应用电路的功能,确定封面上的题目,然后完成以下任务:1、分析电路由几个部分组成,并用方框图对它进行整体描述;2、对电路的每个部分进行分别单独说明,画出对应的单元电路,分析电路原理、元件参数、所起的作用、以及与其他部分电路的关系等等;3、用Protel软件或其他EDA软件绘出整体电路图,进行实验分析,进行实验分析绘制PCB,并在图中的标题栏中加上自己的班级名称、学号、姓名等信息;4、对整体电路原理进行完整功能描述;5、列出标准的元件清单;6、其他。

设计步骤1、查阅相关资料,开始撰写设计说明书;2、先给出总体方案并对工作原理进行大致的说明;3、依次对各部分分别给出单元电路,并进行相应的原理、参数分析计算、功能以及与其他部分电路的关系等等说明;4、总体电路的绘制,实验分析和绘制PCB及总体电路原理相关说明;5、其他6、列出标准的元件清单;7、列出设计中所涉及的所有参考文献资料。

设计说明书字数不得少于5000字参考文献李宁. 基于MDK的STM32处理器开发应用. 北京:北京航空航天大学出版社,2008 王永虹,郝立平. STM32系列ARM Cortex-M3微控制器原理与实践. 北京:北京航空航天大学出版社,2008张睿编著. Altium Designer 6.0原理图与PCB设计. 北京:电子工业出版社,2007刘小伟,刘宇,温培和编著. Altium designer 6.0电路设计实用教程. 北京:电子工业出版社,2007.2目录1、总体方案与原理说明 (1)2、单元电路1——核心系统 (2)3、单元电路2——电源 (3)4、单元电路3——扩展接口 (4)5、单元电路4——下载接口 (4)6、单元电路5——按键和LED (5)7、单元电路6——H-JTAG (5)8、总体电路原理相关说明 (6)9、PCB设计................................................................................. 错误!未定义书签。

eda技术及应用第三版课后答案谭会生

eda技术及应用第三版课后答案谭会生【篇一:《eda技术》课程大纲】>一、课程概述1.课程描述《eda技术》是通信工程专业的一门重要的集中实践课,是通信工程专业学生所必须具备的现代电子设计技术技能知识。

eda是电子技术的发展方向,也是电子技术教学中必不可少的内容。

本课程主要介绍可编程逻辑器件在电子电路设计及实现上的应用,介绍电路原理图和pcb图的设计技术。

开设该课程,就是要让学生了解大规模专用集成电路fpga和cpld的结构,熟悉一种以上的硬件描述语言,掌握一种以上的开发工具的使用等,掌握电路原理图和pcb图的现代设计技术与方法,从而提高学生应用计算机对电子电路和高速智能化系统进行分析与设计的能力。

2.设计思路本课程坚持“以学生为中心”的原则,以项目任务驱动的方式,采取理论知识与案例相结合的方式授课,提高学生的学习主动性。

通过必要的理论知识讲授、大量的实践训练和案例分析,培养学生的动手设计和实践能力,掌握eda开发的整个流程和基本技巧。

课程采用演示讲授和实践相结合,边讲边练的方法,让学生切身体会并掌握eda开发产品的流程和方法。

本课程集中2周时间开设,注重实践性,边讲边练,让学生切身体会并掌握eda开发技术。

3.实践要求(1)纪律和安全要求①不得将食物带入实验室,每次实训后请将使用后的废弃物带走。

违反者每次扣罚平时分2分。

②实训期间不得做与实训无关的其他事情,不得大声喧哗或做其他影响实训正常进行的事宜。

违反者每次扣罚平时分2分。

③实训期间,若学生有事不能正常参加实训,须提前以书面形式请假,并按指导教师的安排补做实训。

未经指导教师许可,学生不得任意调换实训时间和实训地点。

违反者每次扣罚平时分4分。

④学生不得以任何理由替代他人进行实训,违者直接取消实训成绩。

⑤学生除操作自己所分配的计算机外,不得操作实验室内其他任何设备。

违者每次扣罚平时分2分。

(2)业务要求实训所使用的软件protel和quartus ii,所有数据均通过服务器中转以及储存在服务器上,所以重启自己所用的电脑不会造成数据丢失。

eda课程设计30个题目

1数字频率计1)设计一个能测量方波信号的频率的频率计。

2)测量的频率范围是0 999999Hz。

3)结果用十进制数显示。

2乒乓球游戏机1)用8个发光二极管表示球;用两个按钮分别表示甲乙两个球员的球拍2)一方发球后,球以固定速度向另一方运动(发光二极管依次电量),当球达到最后一个发光二极管时,对方击球(按下按钮)球将向相反方向运动,在其他时候击球视为犯规,给对方加1分;都犯规,各加1分;3)甲乙各有数码管计分4)裁判有一按钮,可系统初始化,每次得分后,按下一次3彩灯控制器1)设计一个彩灯控制器,使十个彩灯(LED管)能连续发出四种以上不同的显示形式(如奇数依次亮),;2)随着彩灯显示图案的变化,发出不同的音响声(可用不同频率的矩形波产生)。

4速度表1)显示汽车时速Km/h2)车轮每转一圈,有一个传感脉冲;每个脉冲代表1m的距离3)采样周期设为10S4)*要求显示到小数点后2位5)数码管显示6)*超速报警5拔河游戏机1)设计一个能进行拔河游戏的电路。

2)电路使用15个(或9个)发光二极管,开机后只有中间一个发亮,此即拔河的中心点。

3)游戏双方各持一个按钮,迅速地、不断地按动,产生脉冲,谁按得快,亮点就向谁的方向移动,每按一次,亮点移动一次。

4)亮点移到任一方终端二极管时,这一方就获胜,此时双方按钮均无作用,输出保持,只有复位后才使亮点恢复到中心。

5)*用数码管显示获胜者的盘数6 6 数字跑表1)具有暂停/启动功能2)具有重新开始功能3)用6个数码管分别显示百分秒、秒和分钟4)能计两个人跑步时间,并能选择显示77 电梯控制器1)5层电梯控制器,用5个led显示电梯行进过程,并用数码管显示电梯当前所在楼层位置,每层电梯入口处设有上楼和下楼请求按钮,按下按钮,则相应楼层的led亮2)电梯到达请求楼层,相应的请求led灯灭,电梯门打开,开门5S,电梯自动关门,继续上行(下行)3)每层设有电梯上行和下行指示灯4)能记忆电梯内部的请求信号88 篮球计分器1)具有30秒计时、显示2)可对计时器清零、置数、启动和暂停3)30秒倒计时4)两个数码管显示两队比分5)超时报警并可解除报警99电子琴1)设计一个简易电子琴;2)利用一基准脉冲产生1,2,3,。

EDA考试复习题目全集(1)

《 EDA技术与项目训练》选择题1. 一个项目的输入输出端口是定义在 A 。

A. 实体中B. 结构体中C. 任何位置D. 进程体2. 描述项目具有逻辑功能的是 B 。

A. 实体B. 结构体C. 配置D. 进程3. 关键字ARCHITECTURE定义的是A。

A. 结构体B. 进程C. 实体D. 配置4. MAXPLUSII中编译VHDL源程序时要求 C 。

A.文件名和实体可不同名B.文件名和实体名无关C. 文件名和实体名要相同D. 不确定5. 1987标准的VHDL语言对大小写是 D 。

A. 敏感的B. 只能用小写C. 只能用大写D. 不敏感6. 关于1987标准的VHDL语言中,标识符描述正确的是 A 。

A. 必须以英文字母开头B.可以使用汉字开头C.可以使用数字开头D.任何字符都可以7. 关于1987标准的VHDL语言中,标识符描述正确的是 B 。

A. 下划线可以连用B. 下划线不能连用C. 不能使用下划线D. 可以使用任何字符8. 符合1987VHDL标准的标识符是 A 。

A. A_2B. A+2C. 2AD. 229. 符合1987VHDL标准的标识符是 A 。

A. a_2_3B. a_____2C. 2_2_aD. 2a10. 不符合1987VHDL标准的标识符是 C 。

A. a_1_inB. a_in_2C. 2_aD. asd_111. 不符合1987VHDL标准的标识符是 D 。

A. a2b2B. a1b1C. ad12D. %5012. VHDL语言中变量定义的位置是 D 。

A. 实体中中任何位置B. 实体中特定位置C. 结构体中任何位置D. 结构体中特定位置13. VHDL语言中信号定义的位置是 D 。

A. 实体中任何位置B. 实体中特定位置C. 结构体中任何位置D. 结构体中特定位置14. 变量是局部量可以写在 B 。

A. 实体中B. 进程中C. 线粒体D. 种子体中15. 变量和信号的描述正确的是 A 。

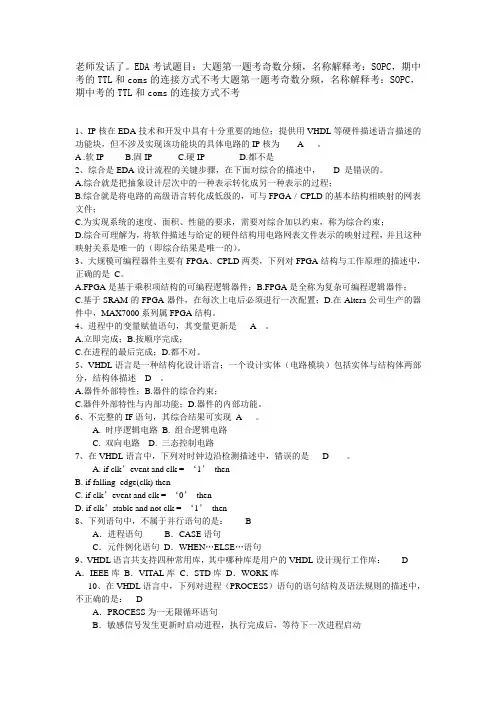

EDA期末必考选择题及答案

老师发话了。

EDA考试题目:大题第一题考奇数分频,名称解释考:SOPC,期中考的TTL和coms的连接方式不考大题第一题考奇数分频,名称解释考:SOPC,期中考的TTL和coms的连接方式不考1、IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为____A___。

A .软IP B.固IP C.硬IP D.都不是2、综合是EDA设计流程的关键步骤,在下面对综合的描述中,___D_是错误的。

A.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的)。

3、大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是_C。

A.FPGA是基于乘积项结构的可编程逻辑器件;B.FPGA是全称为复杂可编程逻辑器件;C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

4、进程中的变量赋值语句,其变量更新是___A__。

A.立即完成;B.按顺序完成;C.在进程的最后完成;D.都不对。

5、VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述__D__。

A.器件外部特性;B.器件的综合约束;C.器件外部特性与内部功能;D.器件的内部功能。

6、不完整的IF语句,其综合结果可实现_A___。

A. 时序逻辑电路B. 组合逻辑电路C. 双向电路D. 三态控制电路7、在VHDL语言中,下列对时钟边沿检测描述中,错误的是___D____。

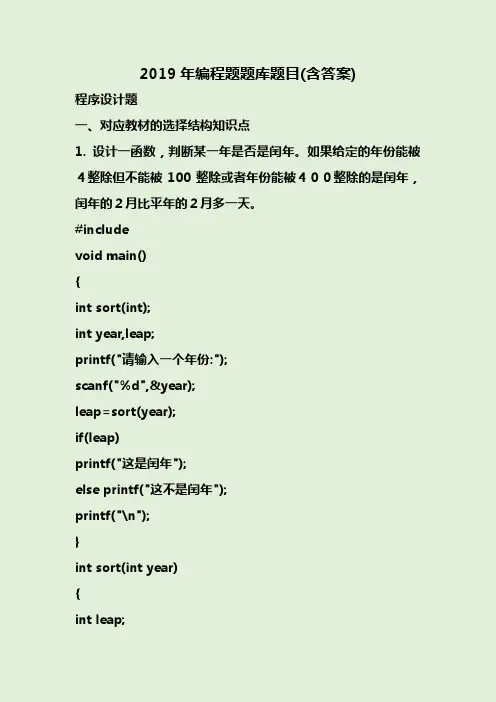

2019年编程题题库题目(含答案)

2019年编程题题库题目(含答案)程序设计题一、对应教材的选择结构知识点1. 设计一函数,判断某一年是否是闰年。

如果给定的年份能被4整除但不能被100整除或者年份能被400整除的是闰年,闰年的2月比平年的2月多一天。

#includevoid main(){int sort(int);int year,leap;printf("请输入一个年份:");scanf("%d",&year);leap=sort(year);if(leap)printf("这是闰年");else printf("这不是闰年");printf("\n");}int sort(int year){int leap;if(year%400==0||year%100!=0&&year%4==0)leap=1;else leap=0;return leap;}2.设计一函数,对于给定的一个百分制成绩,输出相应的五分制成绩。

设:90 分以上为‘A ’;80~89 分为‘B ’;70~79 分为‘C ’;60~69 分为‘D ’;60 分以下为‘E ’。

#includevoid main(){int exchange(int score);int score;char grade;printf("请输入一个百分制成绩:");scanf("%d",&score);grade=exchange(score);printf("五分制成绩是:");printf("%c\n",grade);}int exchange(int score){char grade;int n;n=score/10;switch(n){case 10:case 9: grade='A';break;case 8: grade='B';break;case 7: grade='C';break;case 6: grade='D';break;default: grade='E';}return grade;}3.设计一函数,对输入的字符串,统计其中字母个数,数字个数、空格个数及其它符号个数。

EDA技术实用教程考试复习题目试题库(关于VHDL)

《EDA技术与项目训练》选择题1. 一个项目的输入输出端口是定义在 A 。

A. 实体中B. 结构体中C. 任何位置D. 进程体2. 描述项目具有逻辑功能的是 B 。

A. 实体B. 结构体C. 配置D. 进程3. 关键字ARCHITECTURE定义的是 A 。

A. 结构体B. 进程C. 实体D. 配置4. MAXPLUSII中编译VHDL源程序时要求 C 。

A.文件名和实体可不同名B.文件名和实体名无关C. 文件名和实体名要相同D. 不确定5. 1987标准的VHDL语言对大小写是 D 。

A. 敏感的B. 只能用小写C. 只能用大写D. 不敏感6. 关于1987标准的VHDL语言中,标识符描述正确的是 A 。

A. 必须以英文字母开头B.可以使用汉字开头C.可以使用数字开头D.任何字符都可以7. 关于1987标准的VHDL语言中,标识符描述正确的是 B 。

A. 下划线可以连用B. 下划线不能连用C. 不能使用下划线D. 可以使用任何字符8. 符合1987VHDL标准的标识符是 A 。

A. A_2B. A+2C. 2AD. 229. 符合1987VHDL标准的标识符是 A 。

A. a_2_3B. a_____2C. 2_2_aD. 2a10. 不符合1987VHDL标准的标识符是 C 。

A. a_1_inB. a_in_2C. 2_aD. asd_111. 不符合1987VHDL标准的标识符是 D 。

A. a2b2B. a1b1C. ad12D. %5012. VHDL语言中变量定义的位置是 D 。

A. 实体中中任何位置B. 实体中特定位置C. 结构体中任何位置D. 结构体中特定位置13. VHDL语言中信号定义的位置是 B D 。

A. 实体中任何位置B. 实体中特定位置C. 结构体中任何位置D. 结构体中特定位置14. 变量是局部量可以写在 B 。

A. 实体中B. 进程中C. 线粒体D. 种子体中15. 变量和信号的描述正确的是 A 。

《EDA技术》期末测试参考答案

《EDA技术》期末测试参考答案《EDA技术》期中测试参考答案⼀、选择题(每⼩题2分,共计20分。

)1、VHDL语⾔共⽀持四种常⽤库,其中哪种库是⽤户的VHDL设计当前⼯作库()。

A.IEEE库B.VITAL库C.STD库D.WORK⼯作库2、VHDL的process进程语句是并⾏语句,它的内部是由( )语句构成的A. 并⾏语句和顺序语句B.顺序语句C.并⾏语句D.任意语句3、元件例化语句的作⽤是()。

A.描述元件模块的算法B.改善并⾏语句及其结构的可读性C.产⽣⼀个与某元件完全相同的⼀组并⾏元件D.在⾼层次设计中引⽤前⾯已经设计好的元件或电路模块4、在VHDL的并⾏语句之间,可以⽤( )来传递信息。

严格讲是D,但选C也可,因为⼀般情况下并⾏语句之间是⽤信号来传递信息的。

A.常量(Constant)B.变量(Variable)C.信号(Signal)D.变量和信号5、以下关于VHDL中常量的声明正确的是()。

A.Constant delay :Integer = 8B.Constant delay:Integer := 8C.Variable delay:Integer = 8D.Variable delay:Integer := 86、在VHDL语⾔中,下列对时钟边沿检测描述中,错误的是( )。

A. if clk’event and clk = ‘1’ thenB. if rising_edge(clk) thenC. if clk’event and clk = ‘0’ thenD.if clk’stable and not clk = ‘1’ then7、下列关于VHDL标识符的说法正确的是()(多选)A.标识符由26个英⽂字母和数字0~9以及下划线组成,其中字母不区分⼤⼩写。

B.标识符必须由英⽂字母开始,不连续使⽤下划线,且不能以下划线结束,C.标识符中可以包含空格D.标识符不允许与VHDL中的关键字重合8、下列对FPGA结构与⼯作原理的描述中,正确的是( )。

EDA考试重点加考题

EDA考试重点加考题EDA(电⼦设计⾃动化)利⽤EDA⼯具,采⽤可编程器件,通过设计芯⽚来实现系统功能,这样不仅可以通过芯⽚设计实现多种数字逻辑系统功能,⽽且由于管脚定义的灵活性,⼤⼤减轻了电路图设计和电路板设计的⼯作量和难度,从⽽有效地增强了设计的灵活性,提⾼了⼯作效率;同时基于芯⽚的设计可以减少芯⽚的数量,缩⼩系统体积,降低能源消耗,提⾼系统的性能和可靠性。

ASIC(Application Specific Integrated Circuits)直译为“专⽤集成电路”,与通⽤集成电路相⽐,它是⾯向专门⽤途的电路,以此区别于标准逻辑(Standard Logic)、通⽤存储器、通⽤微处理器等电路Asic优点1 提⾼了产品的可靠性。

(2) 易于获得⾼性能(3) 可增强产品的保密性和竞争⼒。

(4) 在⼤批量应⽤时,可显著降低产品的综合成本。

(5) 提⾼了产品的⼯作速度。

(6) 缩⼩了体积,减轻了重量,降低了功耗。

系统结构设计ASIC 分解逻辑设计电路设计逻辑布线模拟可测性分析及故障模拟版图设计及模拟验证设计定型制作样⽚样⽚功能评价投产ASIC 按功能的不同可分为数字ASIC、模拟ASIC和微波ASIC;按使⽤材料的不同可分为硅ASIC和砷化镓ASIC。

按照设计⽅法的不同,设计ASIC可分为全定制和半定制两类。

全定制法是⼀种基于晶体管级的设计⽅法,半定制法是⼀种约束性设计⽅法。

约束的⽬的是简化设计、缩短设计周期、提⾼芯⽚成品率。

EDA(Electronic Design Automation)即电⼦设计⾃动化。

EDA技术指的是以计算机硬件和系统软件为基本⼯作平台,继承和借鉴前⼈在电路和系统、数据库、图形学、图论和拓扑逻辑、计算数学、优化理论等多学科的最新科技成果⽽研制成的商品化通⽤⽀撑软件和应⽤软件包。

EDA技术可粗略分为系统级、电路级和物理实现级三个层次的辅助设计过程;从另⼀个⾓度来看,EDA技术应包括电⼦电路设计的各个领域,即从低频电路到⾼频电路,从线性电路到⾮线性电路,从模拟电路到数字电路,从分⽴电路到集成电路的全部设计过程。

电设l试题集及答案

电子系统设计试题库一、填空题1、电子系统分为模拟型、数字型、及两者兼而有之的混合型三种。

2、所谓黑箱辨识方法,就是考察黑箱的输入、输出及其动态过程来定量地研究黑箱的功能特性、行为方式,从而探索其内部结构和机理。

3、印制电路板按板层可分为单层板、双层板和多面板。

4、电烙铁按加热方式分,有直热式、感应式、气体燃烧式等。

5、在焊接元器件时,常用的焊料是铅锡焊料。

6、印制电路板的地线可以采用并联分路式、汇流排式、大面积接地和一字形接地等布线形式。

7、电子测量仪器大体可分为专用仪器和通用仪器两大类。

8、测试技术包括调整和测试两部分。

9、电磁干扰产生的途径主要有平行线、天线效应、电磁感应。

10、典型的模拟电路系统主要由传感器件、信号放大与变换电路(模拟电路)和执行机构三部分组成。

11、晶体管串联反馈调整型稳压电源是一个闭环反馈控制系统,主要由调整元件、比较放大、基准电压、取样回路四部分组成。

12、随机存储器按存储机理不同可分为静态RAM 和动态RAM 。

13、数字模拟转换器常用的技术指标为分辨率和转换速率。

14、光电耦合器主要由发光二极管和光敏三极管组成。

15、热敏电阻有正温度系数热敏电阻和负温度系数热敏电阻之分。

16、常用电子元器件有电阻器、电容器、变压器、二极管、三极管等。

17、由PN结构成的半导体二极管具有的主要特性是单向导电性,电路符号是D 。

18、两个电感元件,L1=20mH,L2=20 mH,则并联起来后的等效电感L = 10 mH。

19、某三极管的型号为3DD1,其中第一个字母D表示NPN 型硅管。

20、某色标法四环电阻的第一、二、三、四色环分别为黄、蓝、红和金色,则其标称阻值为 4.7KΩ,允许偏差为±5%。

21、电容并联电路中,起决定性作用的是容量大的电容,串联电路中,起决定性作用的是容量小的电容。

22、用万用表测量电阻时,选好合适的档位后,在测量前应该先对万用表进行欧姆调零,对元器件进行放电。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

简答:

1.VHDL中变量与信号的主要区别

一、变量是一个局部量,只能在进程和子程序,无延时,立即发生,主要作用是在进程中作为临时的数据存储单元。

从VHDL语句功能和行为仿真来看,信号与变量的差异主要表现在接受信息的方式和信息保持与传递的区域大小上。

(1)如:信号可以设置传输延迟量,而变量则不能;

(2)如:信号可作为模块间的信息载体,如在结构体中个进程间传递信息;变量只能作为局部的信息载体,如只能在所定义的进程中有效。

(3) 变量的设置有时只是一种过渡,最后的信息传输和界面间的通信都是靠信号来完成综合后的信号将对应更多的硬件结构。

2.ASIC、FPGA、EDA、ISP的含义

ASIC:专用集成电路FPGA:可编程逻辑器件EDA:电子设计自动化ISP:因特网服务提供商

3.常用的库的名称(IEEE STD WORK VITAL)

5.进程语句的特点

(1)进程与进程,或其它并行语句之间的并行性,体现硬件电路并行运行特征。

(2)进程内部的顺序语句具有顺序与并行双重性。

顺序行为体现硬件的逻辑功能,并行行为体现硬件特征。

进程内部使用顺序语句,对一个系统进行算法、行为和逻辑功能进行描述,可以具有高抽象性的特点,可以与具体的硬件没有关联。

这种顺序仅是指语句执行上的顺序(针对于HDL的行为仿真),并不意味着PROCESS语句在综合后所对应的硬件逻辑行为也同样具有顺序性。

VHDL程序无法进行诸如软件语言那样的“单步”调试,因为整个程序是一个整体,不能割裂每一句,只能通过仿真波形来了解程序的问题。

(3)进程有启动与挂起两种状态。

(4)进程与进程,或其它并行语句之间通过信号交流。

(5)时序电路必须由进程中的顺序语句描述,而此顺序语句必须由不完整的条件语句构成。

推荐在一个进程中只描述针对同一时钟的同步时序逻辑,而异步时序逻辑或多时钟逻辑必须由多个进程来表达。

6.实体定义时端口方向OUT与BUFFER有何不同?

OUT:输出端口。

定义的通道为单向输出(写)模式,即通过此端口只能将实体内的数据流向外部。

BUFFER:缓冲端口。

其功能与INOUT类似,区别在于当需要输入数据时,只允许内部回读输出的信号,即允许反馈。

如:在计数器的设计中,将计数器输出的计数信号回读,作为下一次计数的初值。

与OUT模式相比,BUFFER回读信号不是由外部输入的,而是由内部产生、向外输出信号。

即OUT结构体内部不能再使用,BUFFER结构体内部可再使用。

编程:

编程实现下图所示的控制时序,K为输入信号;处于状态St2时输出信号yout=’1’,其他状态下yout=’0’。

(此题也会反过来考,给出程序要求画出对应时序图)。