C5402 DMA结合MCBSP在数据采集系统中的应用

基于TMS320VC5402和XBee模块的UART应用研究

基于TMS320VC5402和XBee模块的UART应用研究作者:蒲显城罗飞来源:《计算技术与自动化》2013年第04期摘要:基于DSP的漏水检测仪器在实现漏点定位时需要使用无线通信模块,TI公司的TMS320VC5402只提供了同步串行接口McBSP,而无线模块XBee为异步串口。

本文采用16倍过采样的方法,结合直接存储器访问(DMA),通过对相关寄存器的适当配置,将McBSP 软件模拟成通用异步接收/发送器(UART),从而实现DSP与XBee模块的连接通信。

再通过对XBee模块的适当配置,可将从机检测信号无线传给主机,在主机中处理两路信号,从而确定出漏点位置。

试验得到的漏点位置在误差范围内,证明了该法的可行性。

关键词:DSP;McBSP;DMA;XBee;UART中国分类号:TP274 文献标识码:A1 引言数字信号处理器(DSP)具有强大的数据处理能力,使其在高速数字信号处理方面得到广泛的应用。

TMS320VC5402(以下简称C5402)是TI公司的一款低功耗、高性能的16位定点DSP芯片,在音频信号处理等方面得到应用。

选用其作为漏水检测仪器的核心处理芯片,对管道振动信号进行频谱分析,快速判断出是否漏水,而在进行漏水点定位时需要在管道两端同时采集信号,并将两端信号进行互相关运算,进而确定出漏点位置。

因此为了迅速找出漏点,需要快速地将其中一端采集信号无线传输给另一端。

Digi公司的无线通信模块XBee室外最大传输距离可达120米,无线数据传输速率为250 kbps,功耗仅为几毫瓦,满足设计需要。

C5402的McBSP为同步串口,而XBee为异步串口。

常用的DSP应用系统中扩展异步串行接口的方法有:1)利用专用的异步串口芯片(如TI公司的TL16C550),在DSP的并行总线上进行扩展;2)利用McBSP进行适当的硬件扩展(如MAXIM公司的MAX3111);3)利用CPLD/FPGA实现UART;4)利用DSP通用I/O、外部中断以及定时器编程实现UART。

五邑大学_TMS320VC5402定时器实验(DSP报告作业_)

班级:学号:

报告人:

一、TMS320VC5402定时器实验

一实验目的

1.了解DSP汇编程序与C语言程序的构成;

2.了解DSP程序各段的含义;

3.熟悉如何编写中断服务程序;

4.掌握片内定时器的设置方法;

5.掌握长时间间隔的定时器的处理

二实验内容

1. DSP的初始设置;

周期寄存器(PRD)是一个16位的存贮器映射寄存器,它是用来重装时间寄存器(TIM)寄存器的值的。

定时器控制寄存器(TCR)是一个16位的存贮器映射寄存器,包含了定时器的控制与状态信息。

2、CMD文件简介

cmd文件用于DSP代码的定位。由3部分组成:

1、(1)输入/输出定义:

.obj文件:链接器要链接的目标文件。

.stack为C程序系统堆栈保留存储空间,用于保存返回地址、函数间的参数传递、存储局部变量和保存中间结果;

.sysmem用于C程序中malloc、calloc和realloc函数动态分配存储空间

.vectors用于自定义的“.vectors”段,这里是中断向量表

.switch用于C程序中的switch语句

.data已初始化的数据段

3中断向量表文件

中断服务程序的地址(中断向量)要装载到存储器的合适区域。一般用中断向量表文件编制中断向量表,中断向量表文件多采用汇编语言编写;在文件中一般用汇编指令.sect来生成一个表,表中各中断占4个字。这个表包含中断向量的地址和跳转指令。因为中断跳转地址的标志符在汇编语言模块外部使用,所以标志符用.ref或.global定义。

int2: .space 4*16;INT2, SINT2

tint0: BD timer;TINT0, SINT3

TMS320C5402与TLC320AD50C的接口设计

TMS320C5402与TLC320AD50C的接口设计芯片接口设计是一种基于芯片的设备及其电路的连接方式。

在芯片接

口设计中,相关接口被设计成标准的接口,使其可以被多种不同的芯片所

使用。

TMS320C5402与TLC320AD50C是一种典型的芯片接口。

TMS320C5402是一款高性能的DSP芯片,它拥有32位元的指令体系

结构,能够提供强大的计算能力和高效的运算速度。

TMS320C5402具有可

编程的芯片外围电路,可以根据用户的需求进行定制以满足特定应用场景

的要求。

另外,TMS320C5402也提供多种接口,如分立元件接口

(Discrete I/O interface)、RJ45接口(RJ45 interface) 、串口接口(Serial Interface) 、总线接口(Bus Interface)等。

TLC320AD50C是一款高性能的数字音频处理IC。

其内部具有2路数字

音频处理器,各路数字音频处理能力可以达到32位96KHZ的水平,可以

满足用户对数字音频处理高要求的应用。

此外,TLC320AD50C既具有多种

主要32位、24位、16位的数据接口,如I2S、I2C、I2L、SPI等,也具

有可选的数字接口,如TDM、S/PDIF、EIAJ、SCMS等。

因此,为了使TMS320C5402与TLC320AD50C之间的接口更加简洁高效,我们可以采用I2C接口设计。

I2C接口也被称为串行总线接口,是一种可

以在多个芯片之间传递信息的串行接口,具有高带宽、低成本、低电压电

平等特点,适用于多种多台设备的集成。

首先。

在TMS320VC5402上实现的嵌入式TCPIP协议栈

摘要:实现一个运行在16位数字信号处理器TMS320VC5402上的小型嵌入式TCP/IP协议栈。

对TCP/IP协议中的IP协议、ARP协议、UDP协议进行分析,完成基于TCP/IP协议的嵌入式网络系统。

关键词:DSP TMS320VC5402 TCP/IP协议栈嵌入式系统引言随着嵌入式系统应用范围的不断扩展及网络应用的日益普及,使得越来越多的嵌入式系统需要支持网络功能。

TCP/IP是目前一种被广泛采用的网络协议。

TCP/IP是一套把因特网上的各种系统互连起来的协议组,已成为事实上最常用的网络标准之一。

本文对TCP/IP 协议中的IP协议、ARP协议和UDP协议进行了分析,利用DSP的专用汇编语言实现了自己的通信协议。

由此可使DSP直接对Ethernet发来的数据包解分析,并能按照TCP/IP协议正确打包和发送,最终实现DSP与PC机的数据通信,成功地完成了语音数据的采集和发送,实现了DSP与PC机的语音数据传输。

1 TCP/IP协议分析一般在嵌入式系统中实现的TCP/IP协议都是面向数据采集和传输的,所以大部分实现都是IP协议、ARP协议、UDP协议或者是TCP协议。

本文完成的是IP协议、ARP协议和UDP协议。

一般认为TCP/IP为四层协议,实现的协议栈结构如图1所示。

DSP程序自下而上实现以下协议:①媒介访问控制MAC(Media Access Control),向以太网收发数据。

传送的数据格式为Ethernet数据帧格式。

Ethernet帧的长度是可变的,但都大于64字节,小于1518字节。

它包括头部、数据和尾部三部分。

8字节的前导用于帧同步,CRC域用于帧校验。

目的地址和源端地址是指网卡的物理地址(MAC地址),具有唯一性。

②地址解析协议ARP(Address Resolution Protocol),使得物理地址和IP地址可以对应起来。

在Ethernet上,使用地址解析协议ARP协议来实现IP地址到MAC地址的动态转换。

DSP课程设计--基于TM320VC5402语音采集压缩存储与回放

目录摘要 (Ⅰ)第1章概述 (1)1.1设计目的 (1)1.2设计要求 (1)第2章系统硬件设计方案 (2)2.1 TMS320VC5402芯片的基本原理 (2)2.2 语音采集与输出模块 (4)第3章软件设计与系统仿真 (5)3.1软件设计流程图 (5)3.2 CCS操作过程 (5)3.3系统仿真 (5)第4章课程设计总结 (8)参考文献 (9)附录:源程序代码 (10)第1章概述1.1设计目的在CCS环境下基于TMS320VC5402芯片的语音采集压缩存储与回放。

通过这次课程设计,加深对CCS集成开发环境的以及DSP试验系统箱的使用。

锻炼逻辑思维能力、动手能力以及独立解决问题的能力,对以后更深入地学习和应用数字信号处理及相关知识作准备。

1.2设计要求(1)了解DSP开发工具及其安装过程(2)熟悉DSP开发软件CCS使用(3)熟悉工程文件的建立方法、汇编程序开发调试过程(4)熟悉常用C5402系列指令的用法(5)在老师的指导下,独立完成课程设计的全部内容,并按要求编写课程设计论文,能正确阐述和分析设计和实验结果。

第2章系统硬件设计方案2.1 TMS320VC5402芯片的基本原理TMS320VC5402 数字信号处理器是TI公司为实现低功耗,高速实时信号处理而专门设计的16位定点数字信号处理器,采用改进的哈佛结构,具有高度的操作灵活性和运行速度,适用于远程通信等实时嵌入式应用的需要。

广泛应用于电子测试、电子设计、模拟仿真、通信工程中。

TMS320VC5402具有的主要优点如下:(1) 围绕一组程序总线、三组数据总线和四组地址总线而建立的改进哈佛结构,提高了系统的多功能性和操作的灵活性。

(2) 具有高度的并行性和专用硬件逻辑的CPU设计,提高了芯片的性能。

(3) 具有完善的寻址方式和高度专业化指令系统,更适用于快速算法的实现和高级语言编程的优化。

(4) 模块化结构设计,使派生器件得到了更快的发展。

主动声呐接收信号数据采集和处理系统设计

主动声呐接收信号数据采集和处理系统设计杜芸强;毕淑娥【摘要】介绍了一种基于TM320VC5402和STC12C5A32S2的小功率主动声呐接收信号的处理系统设计方案,并详细阐述了方案硬件系统平台的设计及具体构成,同时也对采集后声呐信号的后续处理做了简要介绍.该数据采集与处理系统具有一定的通用性和可扩展性,具有一定的工程应用价值.【期刊名称】《电声技术》【年(卷),期】2010(034)009【总页数】4页(P57-60)【关键词】数据采集;高速A/D;串口通信;DSP【作者】杜芸强;毕淑娥【作者单位】华南理工大学,电力学院,广东,广州,510640;华南理工大学,电子与信息学院,广东,广州,510640【正文语种】中文【中图分类】TB561 引言声呐是目前用来进行水下观测、定位、识别和通信的主要设备,它在海洋开发中的应用日益广泛。

而声呐工作状态的优劣,很大程度上取决于声呐信号处理技术。

声呐信号处理技术通常要求处理的频带尽可能得宽、动态范围要尽可能得大,以便得到更宽的频率搜索范围,获取更多的信息量,这就要求A/D转换速度快、采样精度高,以便满足系统处理的要求。

笔者设计了一种基于TMS320C5402和STC12C5A 32S2的数据采集和处理系统,其中STC12C5A32S2集成了8通道10位高速ADC,速度可达300 k次/s,可实现高速的数据采集。

系统主要包括3个部分:高速AD采样部分、STC12C5A32S2与DSP数据传输部分以及DSP电路部分,分别完成模拟数字转换、数据传输与存储以及信号处理算法的实现。

2 系统硬件设计本文设计的基于DSP的小功率主动声呐接收信号处理系统硬件原理框图如图1所示,小功率主动声呐传感器接收到超声波,经压电效应转换成电信号送入模拟信号预处理电路进行预处理;STC12C5A32S2集成了模数转换功能,模拟信号预处理后的信号经模数转换后的数字信号通过该单片机的串口送入DSP,然后在DSP中进行相应的算法处理,处理后结果可通过HPI接口上报或输出。

DSP 第11讲 McBSP

5~4

XINTM

3

XSYNCERR

发送同步错误。 XSYNCERR=0时,无发送同步错误 XSYNCERR=1时,McBSP检查到发送同步错误

发送移位寄存器(XSR[1,2])空 /XEMPTY=0时,XSR[1,2]为空 /XEMPTY=1时,XSR[1,2]不为空 发送准备好 XRDY=0时,发送器没有准备好 XRDY=1时,发送器准备好发送DXR[1,2]中的数据 发送器复位,可以复位和使能发送器 XRST=0时,串行接口发送器被禁止并且处于复位状态 XRST=1时,串行接口发送器被使能

80

保留 CLKS_STAT DX_STAT DR_STAT FSXP FSRP CLKXP CLKRP

14~13

RJUST

12~11

CLKSTP

l0~8

保留

§11.3 McBSP的配置—SPCR1、SPCR2、PCR

位 7 6 名 称 DXENA ABIS 功 能 DX使能位 DXENA=0时,DX使能关;DXENA=1时,DX使能开 ABIS模式 ABIS=0时,禁止ABIS模式;ABIS=1时,使能ABIS模式 接收中断模式 RINTM=00时,接收中断RINT由RRDY(字结束)和ABIS模式下的帧结束信号驱动 RINTM=01时,接收中断RINT由块结束或多通道操作下的帧结束信号产生 RINTM=10时,接收中断RINT由一个新的帧同步信号产生 RINTM=11时,接收中断RINT由RSYNCERR产生 接收同步错误 =0时,无接收同步错误; =1时,McBSP检查到接收同步错误

发送帧同步模式位 FSXM=0时,帧同步信号由外部器件驱动 FSXM=1时,采样率发生器的帧同步模式位(SRGR2的FSGM位)决定帧同步信号 接收帧同步模式位 FSRM=0时,帧同步信号由外部器件驱动,FSR为输入引脚 FSRM=1时,片内采样率发生器产生帧同步信号,FSR为输出引脚(除非SRGR的 GSYNC=1) 发送器时钟模式位 CLKXM=0时,发送器时钟由外部时钟驱动,CLKX为外部时钟输入引脚 CLKXM=1时,CLKX为输出引脚,并且由内部采样率发生器驱动 在SPI模式下(当CLKSTP为非0值): CLKXM=0时,McBSP为从器件,并且时钟(CLKX)由系统的SPI主器件驱动。CLKR由内 部CLKX驱动;CLKXM=1,McBSP为主器件,并产生时钟(CLKX)去驱动它的接收时钟 (CLKR)和系统的SPI从器件的移位时钟

基于dsp的语音采集及滤波器设计

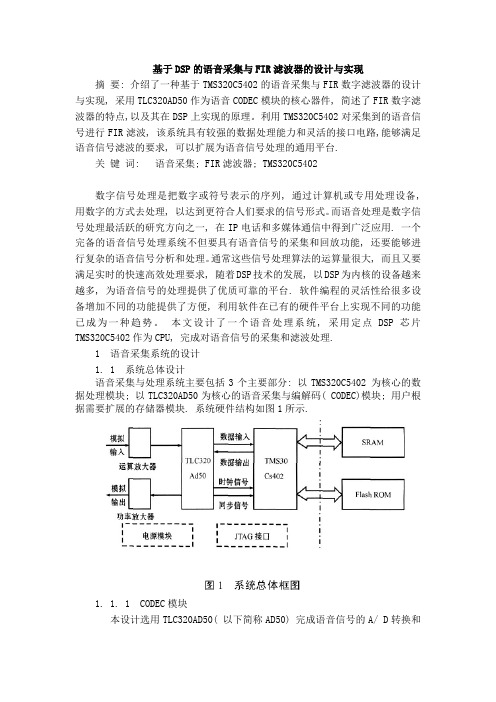

基于DSP的语音采集与FIR滤波器的设计与实现摘要: 介绍了一种基于TMS320C5402的语音采集与FIR数字滤波器的设计与实现, 采用TLC320AD50作为语音CODEC模块的核心器件, 简述了FIR数字滤波器的特点,以及其在DSP上实现的原理。

利用TMS320C5402对采集到的语音信号进行FIR滤波, 该系统具有较强的数据处理能力和灵活的接口电路,能够满足语音信号滤波的要求, 可以扩展为语音信号处理的通用平台.关键词: 语音采集; FIR滤波器; TMS320C5402数字信号处理是把数字或符号表示的序列, 通过计算机或专用处理设备, 用数字的方式去处理, 以达到更符合人们要求的信号形式。

而语音处理是数字信号处理最活跃的研究方向之一, 在IP电话和多媒体通信中得到广泛应用. 一个完备的语音信号处理系统不但要具有语音信号的采集和回放功能, 还要能够进行复杂的语音信号分析和处理。

通常这些信号处理算法的运算量很大, 而且又要满足实时的快速高效处理要求, 随着DSP技术的发展, 以DSP为内核的设备越来越多, 为语音信号的处理提供了优质可靠的平台. 软件编程的灵活性给很多设备增加不同的功能提供了方便, 利用软件在已有的硬件平台上实现不同的功能已成为一种趋势。

本文设计了一个语音处理系统, 采用定点DSP芯片TMS320C5402作为CPU, 完成对语音信号的采集和滤波处理.1 语音采集系统的设计1. 1 系统总体设计语音采集与处理系统主要包括3个主要部分: 以TMS320C5402 为核心的数据处理模块; 以TLC320AD50为核心的语音采集与编解码( CODEC)模块; 用户根据需要扩展的存储器模块. 系统硬件结构如图1所示.1. 1. 1 CODEC模块本设计选用TLC320AD50( 以下简称AD50) 完成语音信号的A/ D转换和D/ A转换. AD50是TI公司生产的一款集成有A/ D和D/ A的音频芯片, DSP与音频AD50连接后, 可使用一个缓冲串行口来同时实现语音信号的采集和输出, 从而可以节省DSP的硬件开销. AD50使用过采样技术提供从数字信号到模拟信号和模拟信号到数字信号的高分辨率低速信号转换. 该器件包括2个串行的同步转换通道, 分别用于各自的数据传输. 语音信号直接从AD50的模拟信号输入端输入, AD50对其进行采样, 并将采样后的数据传送至DSP. DSP应用相应的算法对数据进行处理, 并将处理后的数据传送到AD50的D/ A输入端. AD50再对DSP处理后的数据进行数模转换, 变为语音信号后输出到音响设备.本系统中TLC320AD50与TMS320C5402之间采用串行通信, 通过DSP芯片的MCBSP串口实现.接口电路如图2所示.1. 1. 2 MCBSP的工作原理TMS320C5402有2个McBSP 多通道缓存串行口. McBSP提供了全双工的通信机制, 以及双缓存的发送寄存器和三缓存的接收寄存器, 允许连续的数据流传输, 数据长度可以为8、12、16、20、24、32; 同时还提供了A律和L律压扩. 数据信号经DR和DX引脚与外设通讯, 控制信号则由CLKX、CLKR、FSX、FSR等4个引脚来实现[ 4]. CPU和DMA控制器可以读取DRR[ 1, 2] 的数据实现接收, 并且可以对DXR[ 1, 2] 写入数据实现发送. 串行口控制寄存器SPCR[ 1, 2] 和引脚控制寄存器PCR用来配置串行口; 接收控制寄存器RCR[ 1, 2] 和发送控制寄存器XCR[ 1, 2]用来设置接收通道和发送通道的参数; 采样率发生器寄存器SRGR[ 1, 2] 用来设置采样率. TMS320C5402芯片串口控制寄存器功能强大, 用户通过编程不但可以设置时钟信号的极性及输入输出方向, 还可以设置同步信号的极性及输入输出方向.1. 1. 3 AD50与DSP的同步通信在应用中, 将TLC320AD50C接至DSP的同步串口, 并将TLC320AD50设置在主动工作模式下, 即由TLC320AD50 提供帧同步信号和移位时钟,TMS320C5402的管脚电压为3. 3V, 可以与AD50直接相连. 串口的移位时钟SCLK由AD发出, 串行数据在SCLK的驱动下经DIN、DOUT 移进、移出, 在SCLK的下降沿采样DIN 数据, 在SCLK下降沿送出数据到DOUT. XF控制首次或二次通信, XF为低时是AD50的首次通信, 是正常的AD、DA的数据; XF为高时是AD50的二次通信, 这时可以读写AD50的4个寄存器. 进入二次通信有软件的方法, 即把AD50设为15+1位数据模式, 最后一位标记下一个数据是否为二次通信数据, 1表示是, 0表示否.一次通信格式的16位都用来传输数据. DAC的数据长度由寄存器1的D0位决定. 启动和复位时, 默认值为15+ 1模式, 最后一位要求二次通信. 如果工作在16位传输模式下, 则必须由FC产生二次通信请求. 二次通信格式则用来初始化和修改TLC320AD50C内部寄存器的值. 在二次通信中可通过向DIN写数据来完成初始化.二次通信格式如图3所示, D13= 1表示读DIN的数据, D13= 0表示向DIN 写数据.系统复位后, 必须通过DSP 的DX接口向TLC320AD50C的DIN 写数据, 因为采用一片TLC320AD50C, 只需初始化寄存器1、寄存器2、寄存器4. 由于通信数据长度为16位, 初始化是应通过RCR1和XCR1设置McBSP的传输数据长度为16.2 语音采集语音信号的采集, 是通过话筒经模拟放大输入到AD50, AD50作相应的低频滤波并进行A/ D转化, 再通过MCBSP通道输入DSP芯片. 语音信号采集程序包括以下几个部分:( 1) DSP初始化. 对DSP的寄存器以及缓冲串口进行初始化.( 2) AD50初始化. 通过DSP的缓冲串口和XF引脚对AD50进行初始化, 再设置AD50的4个控制寄存器; 确定AD50的4个控制寄存器设置正确后,AD50才能开始采集数据. 此时, 可以用示波器检测AD50的DOUT引脚, 能发现引脚是否有连续的信号输出.( 3) 设置DSP的中断, 从缓冲串口读取数据. 如果此时在缓冲串口连续读取数据, 就可以在仿真软件CCS中查看读取的数据是否正确.( 4) DSP存放数据. 可以将缓冲串口读取的数据存放到DSP的RAM单元, 连续存放, 可通过CCS的图形显示功能判断AD50采样的数据是否正确.3 语音滤波语音去噪在语音信号上应用较多, 在实质上和普通的数字信号去噪没有什么区别, 使用滤波器和各种算法均可以实现语音信号的去噪, 使得含有噪声的信号更加清晰. 但语音信号的去噪和一般的数字信号去噪又存在着很大的差别, 因为语音信号的频谱覆盖在100Hz~3. 4kHz, 较为丰富的信号主要集中在1kHz 附近, 所以一般的滤波去噪时必须考虑语音信号的自身特征.本系统中应用的AD50内置了低通滤波器, 可以通过设置来有效滤除信号中混杂的高频干扰信号, 而对于低于100Hz的干扰信号, 则无能为力. 因此, 要用DSP进行编程设计一个软件可实现高通滤波器, 由处理器来完成信号的去噪, 采用FIR滤波.3.1 FIR滤波器的基本结构及特点有限冲激响应( FIR)滤波器的基本结构是一个分节的延时线, 把每一节的输出加权累加, 得到滤波器的输出. 数学上表示为y(n) =EN-1n=0h(n)x(n-m), (0[ n[ N- 1) (1) 对(1)式进行Z变换, 整理后可得出FIR滤波器的传递函数为H(z) = EN-1n=0h(n)z-n, (0[ n[ N- 1) (2)由( 2)式可知FIR滤波器的一般结构如图1所示.图1 FIR数字滤波器直接实现形式3.2 FIR滤波器的DSP实现原理由( 1)式可知, FIR滤波器的冲激响应为h(0), h(1), ,, h(N- 1). x(n)表示滤波器在n时刻的输入, 则n时刻的输出为y(n) = h(0)x(n) +h(1)x(n- 1) + ,+ h(N- 1)x[ n- (N- 1) ],这是一个乘、加的过程, 可以使用DSP中的MAC 指令实现该运算. 图2说明了使用循环寻址实现FIR滤波器的方法. 为了能正确使用循环寻址, 必须先初始化BK, 块长为N. 同时, 数据缓冲区和冲激响应( FIR滤波器的系数)的开始地址必须是大于N的2的最小幂的倍数. 例如, 当N= 11时, 大于N的最小2的幂为16, 则数据缓冲区的第一位地址应该是16的倍数, 因此数据缓冲区起始地址的最低4位必须是0.在图2中, 滤波系数指针初始化时指向h(N- 1), 经过一次FIR滤波计算后, 在循环寻址的作用下,仍然指向h(N- 1). 而数据缓冲区指针指向的是需要更新的数据, 如x(n). 在写入新数据并完成FIR运算后, 该指针指向x(n- (N- 1)) , 所以, 使用循环寻址可以方便地完成滤波窗口数据的自动更新.4 FIR滤波器设计实例给定FIR数字带通滤波器的技术指标为: 2个通带截止频率分别为4kHz和6kHz, 2个阻带截止频率分别为3kHz和7kHz, 采样频率均为25kHz. 输入为一个混合信号f = [ cos(2000Pt) + cos(10000Pt) + cos(20000Pt)] /6,利用Matlab设计FIR带通滤波器的系数, 将得到的滤波器系数乘以32768(即215)后舍尾取整可得DSP中滤波器系数列表. 用. word汇编命令将各滤波器系数直接输入到DSP程序中; 模拟输入数据由C语言程序实现, 然后用. copy命令将C语言程序生成的数据文件firinput拷贝到DSP程序中. DSP程序实现读入数据、滤波、显示波形等方面的任务. 完成FIR滤波器的程序框图如图3所示, 可知FIR滤波器的DSP实现主要由以下4方面的内容组成.4.1 模拟输入数据的生成用C语言程序生成输入数据, 通过. copy汇编命令将生成的数据文件拷贝到汇编程序中, 作为FIR滤波器的输入数据. C语言程序运行后所生成的数据文件名为firinpu,t 生成firinput数据文件的C语言程序如下所示:#include"stdio. h"#include"math. h"main( ){int ;idouble f[ 256];FILE*fp;if( ( fp= fopen( "e: \ \ firinput", "wt") ) = =NULL){printf( "canct openfile! \n");}for( i=0; i< =255; i++ ){f[ i] =( cos( 2* 3. 14159265* *i 1000/25000) + cos( 2* 3. 14159265* *i 5000/25000) +cos( 2* 3. 14159265* *i 10000/25000) ) /6;fprintf( fp, " . word %ld\n", ( long) ( f[ i]* 32768) );}fclose( fp);}4.2 DSP初始化程序 DSP初始化程序包括了对堆栈指针( SP)、软件等待状态寄存器( SWWSR)、中断寄存器( IFR)、中断屏蔽寄存器( IMR)以及处理器工作状态寄存器( PMST)的初始化; 另外还对各变量赋值, 具体的程序如下: . def _c_int00. mmregsswcr . set 2bht_ar2 . set 066ht_ar3 . set 067hout_wave_buf . set 0d00hdata_in . set 0f00hN . set 51fir_coef_buf . set 100hfir_data . set 200h. textrs b_c_int00_c_int00:stm#2020h, pmstssbx intmssbx sxmssbx frctstm #10h, 26hstm #10h, 36hstm #0ffh, spld #0, dpstm #0ffffh, ifrstm #20h, imrstm #02492h, swwsrstm #0, swcr可看出, FIR滤波器的系数列表将存在100h开始的单元中, 输入数据将存在200h开始的单元中, 而输出数据将存在0d00h开始的单元中.4.3 滤波系数以及输入数据的调入由于滤波器系数一开始是存在程序存储器中, 输入数据则是存在程序外的文件中, 程序对这2组数据进行处理时, 需要把两者都调到数据存储器中, 具体实现程序如下:stm #fir_data, ar6rpt #255mvpd #inpu,t*ar6+stm #fir_coef_bu,f ar6rpt #N-1mvpdfir_coe,f*ar6+stm #fir_coef_bu,f t_ar2stm #fir_data, t_ar3这段程序实现的是把输入数据调到以200h开始的单元, 而把滤波系数调到从100h开始的单元.4.4 滤波子程序一次滤波的过程实质上就是对2组数进行有规律的乘加计算, 具体程序如下:fir:mvdm #t_ar2, ar2 ; 将起始滤波系数地址100h 赋给ar2mvdm #t_ar3, ar5 ; 将起始输入数据地址200h 赋给ar5stm #data_in, ar3 ; ar3=0f00hstm #255, brc ; 定义块循环次数rptbdloop-1 ; 定义块循环结束地址stm #N, bk ; 定义循环缓冲器大小ld *ar5+, a ; 将新数据读到累加器a中 stl a,*ar3+% ; 将新数据读入栈顶rptz a, #(N-1) ; 定义循环次数, 之前先将a累加器清0mac *ar2+0%,*ar3+0%, a ; a=ar2*ar3+a, 每完成一次计算ar2、ar3 ; 指针所对应地址+1sth a, * ar6+ ; 将计算结果保存输出loop这个程序段将重复执行256次, 从而实现对于数据的读入、处理、输出等功能.5 结语本文介绍了一个实时数据采集处理系统的设计和实现, 系统以DSP芯片和TLC320AD50芯片为核心,有很强的数据处理能力和灵活的外围接口电路, 实验证明, 可较好地实现语音的滤波. 该系统可扩展为3G手机语音识别系统, 也可以作为语音信号处理算法研究和实时实现的通用平台参考文献: :[ 1] 邹彦. DSP原理及应用[ M]. 北京:电子工业出版社, 2005.[2] 乔瑞萍, 崔涛,张芳娟. TMS320C54x原理及应用[M].西安: 西安电子科技大学出版社, 2005.[3] 黄海波, 蒋伟荣. 通用语音处理系统的DSP实现[ J] . 微计算机信息, 2006,22( 5) :173- 175.[4] 张勇, 曾炽祥,周好斌. TMS320C5000系列DSP汇编语言程序设计[M]. 西安:西安电子科技大学出版社, 2004.[ 5] 卢山, 田野,郭黎利. 利用DSP技术实现FIR滤波器[ J]. 应用科技, 2002, 29( 11): 19-21.[ 6] 张伟利, 朱煜. FIR滤波器在TMS320C5402中的实现[ J].微处理机, 2005( 2): 4- 6.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

C5402 DMA结合MCBSP在数据采集系统中的应用

1前言

在以C5402 DSP为核心组成的数据采集系统中,用户一般需要在采集完一段数据后对其进行处理。

采用查询方式采集数据会占用大量CPU的资源,采用中断方式来采集数据虽可以提高CPU的利用率,但是在采集数据的每个时刻还是由CPU来完成,同时降低了程序的可读性。

本文设计的数据采集系统利用C5402的存储器直接存储控制DMA与多通道缓冲串行口McBSP结合来设计系统,使得CPU正常工作与DMA数据采集并行进行,提高了DSP的运行效率。

2. C5402 DMA的特点C5402存储器直接存储控制DMA能在不占用CPU资源的情况下,实现DSP存储器间数据的自由传送。

C5402有6个可独立编程的DMA通道,每个DMA通道受各自的5个16位寄存器控制:源地址寄存器DMSRC、目的地址寄存器DMDST、单元计数寄存器DMCTR、同步事件和帧计数寄存器DMSFC、发送模式控制寄存器DMMCR。

1. 源地址寄存器DMSRC规定DMA要传送源数据的首地址。

这些地址可以指向DSP内部存储器、外部存储器、片内外设和一些特殊的外部装置。

2. 目的地址寄存器DMDST规定DMA要传送数据目的地址的首地址。

这些目的地址可以是DSP内部存储器、外部存储器、片内外设和一些特殊的外部装置。

3. 单元计数寄存器DMCTR规定DMA传送数据的个数为DMCTR寄存器的值加1个。

4. 同步事件和帧计数寄存器DMSFC规定DMA传送数据的同步事件类型和传送一块数据所含帧信号的个数: DBLW位设置DMA工作在单字模式(=0b)或双字模式(=1b)。

工作在单字模式时每个数据单元设置为16位,双字模式时每个数据单元设置为32位。

Frame Count位设置每块数据所含帧信号的个数。

DSYN位设置选择如下方式作为DMA同步事件:0000b:无同步事件。

0001b:McBSP0接收事件(REVT0)。

0010b:McBSP0发送事件(XEVT0)。

0101b:McBSP1接收事件(REVT1)。

0110b:McBSP1发送事件(XEVT1)。

1101b:定时器0中断事件。

1110b:外部中断3(INT3)中断事件。

1111b:定时器1中断事件。

其它:保留。

5.传输模式控制寄存器DMMCR规定了DMA通道的传输模式: AUTOINIT位是DMA自动初始化设置位,可设置成自动初始化使能(=1b)和自动初始化不使能(=0b)。

当DMA工作在自动初始化模式时,CPU在一个DMA事件完成后自动装载下一个DMA初始化设置并继续进行数据传送。

DINM位和IMOD位设置DMA中断产生方式。

DINM=0时DMA中断被屏蔽,当DINM=1时中断按IMOD位设置产生。

CTMOD位设置发送计数模式控制,DMA可工作在多帧模式(=0b)和自动缓冲ABU模式(=1b)。

SIND位和DIND位用来设置源地址和目的地址的自动调整方式,可选择如下方式:不调整(=000b)、访问后自动加1(=001b)、访问后自动减1(=010b)、访问后按照单元地址索引寄存器DMIDX0的设置进行调整(=011b)、访问后按照单元地址索引寄存器DMIDX1的设置进行调整(=100b)、访问后按照单元地址索引寄存器DMIDX0和帧地址索引寄存器DMFRI0的设置进行调整(=101b)、访问后按照单元地址索引寄存器DMIDX1和帧地址索引寄存器DMFRI1的设置进行调整(=110b)、保留(=111b)。

DMS位和DMD位用来选择源数据和目的数据所存的空间,可选择成程序空间(=00b)、数据空间(=01b)、I/O空间(=10b)或保留(11b)。

此外,DMA的6个通道还受通道优先级和使能控制寄存器DMPREC控制。

在这个寄存器中相应的DPRC位置1选择相应的通道为高优先级,相应的DE位置1选通相应的通道为使能通道并开始工作。

3. 接口设计在这个系统中,使用的A/D数据转换芯片是语音信号编码解码芯片TLC320AD50。

它是TI公司生产的一个16位、音频范围、内含抗混叠滤波器和重构滤波器的串行模拟接口芯片。

它完成语音信号的数字化采样,并将转换完的数据传给DSP进行后续处理。

C5402提供两个高速、全双工、多通道缓冲串行口McBSP。

它依靠三个信号实现发送数据和接收数据:数据线D(R/X)、帧同步线FS(R/X)和移位时钟线CLK(R/X)。

DX和DR引脚完成与外部设备进行通信时数据的发送和接收,由CLKX、CLKR、FSX、

FSR实现时钟和帧同步的控制。

发送数据时,CPU将要发送的数据写到发送数据寄存器DXR,在FSX和CLKX作用下,由DX引脚输出。

接收数据时,来自DR引脚的数据在FSR和CLKR作用下,从数据寄存器DRR中读出数据。

CLKX、CLKR、FSX、FSR既可以由内部采样率发生器产生,也可以由外部设备驱动。

设置DMA1通道与McBSP1通道结合来读取TLC320AD50转换完的数据。

选择McBSP1通道的接收寄存器DRR11(41h)为DMA传送数据的首地址,并选择源地址工作在访问后不调整方式,选择DMA通道同步事件McBSP1接收事件为DMA同步事件,来实现DMA和McBSP的结合。

TLC320AD50转换完的数据按McBSP1的设置被送到C5402内部接收寄存器DRR11中,再由DMA将DRR11中的数读到指定数据存储区来完成数据采集。

DMA在传送外部来的数据时不会影响CPU的正常运行,当DMA采集完一组规定个数的数据后产生一个DMA中断事件中断CPU,来通知CPU对其进行相应的处理,此时DMA可以按照设定继续采集下一组数据,实现了数据采集与CPU处理的并行操作。

4. 软件设计本系统软件由C5402初始化程序、McBSP1初始化程序、TLC320AD50初始化程序、DMA1通道初始化程序和数据处理程序构成。

C5402初始化程序完成DSP堆栈、CPU 时钟和运行状态的设置。

McBSP1初始化程序设置McBSP1的工作状态:运行在时钟自由运行状态下,接收/发送帧同步信号和移位时钟信号都由外界驱动,每帧一字,每字16位,接收数据和发送数据都无延时。

TLC320AD50初始化程序完成TLC320AD50相关寄存器的设置:选择INP/INM为模拟信号输入端,15+1位ADC和15+1位DAC模式,工作在主机模式,不带从机,采样频率为10.67KHz,模拟信号输入和输出放大增益均为0dB。

DMA1通道初始化程序初始化DMA1,具体程序如下: …… stm #0005h, 55h ;选择DMA1通道stm #0041h, 56h ;设置McBSP1接收端为DMA事件的源地址 stm #0200h, 56h ;设置DMA事件的目的地址 stm #0100h-1,56h ;设置直接传送数据个数为0100h个 stm #5000h,56h ;设置McBSP1接收同步模式,一帧接收一个字 stm #404dh, 56h ;设置DMA工作在多帧模式,源地址不调整,目的地址按单元地址索引寄存器DMIDX0的值为步长进行调整 stm #20h, 55h stm #0001h, 57h ;设置单元地址索引寄存器DMIDX0的值为1 stm #0282h, 54h ;设置DMA1通道为高优先级并使能DMA1通道 ……

5. 结束语本文提出的DMA结合多通道缓冲串行口McBSP组成数据采集系统的实现方法,大大减少CPU的工作量,简化软件设计,有效地利用DSP的硬件资源,提高信号采集系统的执行效率,已经在本校信号处理实验室的DSP系统中得到很好的应用。