硅平面结终端_场限环的实验研究

大直径硅晶片化学机械抛光及其终点检测技术的研究与应用

硅片 CMP 机台整个系统由一个旋转的硅片夹持 器、承载抛光垫的工作台和抛光液输送装置三大部分 组成。化学机械抛光时,旋转的工件以一定的压力 压在旋转的抛光垫上,由亚微米或纳米磨粒和化学溶 液组成的抛光液在硅片与抛光垫之间流动,抛光液在 抛光垫的传输和旋转离心力的作用下,均匀分布其 上,在硅片和抛光垫之间形成一层液体薄膜,液体 中的化学成分与硅片产生化学反应,将不溶物质转化 为易溶物质,然后通过磨粒的微机械摩擦将这些化学 反应物从硅片表面去除,溶入流动的液体中带走, 即在化学成膜和机械去膜的交替过程中实现超精密表 面加工,从而达到平坦化的目的[4]。CMP 可以用下 列Preston方程式来表示

Si3N4 停止层 浅沟槽

SiO2

C M P 去除

硅

图 3 浅沟槽隔离 CMP 示意图

⑷多晶硅的 CMP。此为将 STI 过程的沟槽加 深,以 CVD 方式沉积氧化硅或氮化硅后,再以多 晶硅作为堆积材料,用 CMP 去除深沟外多余的多 晶硅,并以在硅晶片上及沟槽内长成的氧化硅或氮 化硅膜作为 CMP 的抛光停止层即终点,此方法常 见于沟槽电容的制造过程中,如图 4 所示。

GCT VLD-FLR复合终端结构的设计

GCT VLD-FLR复合终端结构的设计大功率深结器件通常采用台面磨角技术和横向变掺杂(VLD)技术来提高其终端击穿电压,但由于VLD掺杂剖面难以精确控制并且对表面电荷比较敏感,所以不能有效得保证终端耐压特性和可靠性。

为解决上述问题,本文以4.5kV GCT为例,提出了一种横向变掺杂-场限环(VLD-FLR)复合终端结构,采用Sentaurus-TCAD软件对其进行了二维数值仿真和研究。

主要内容如下:第一,为了缓解VLD终端末尾电场集中问题并提高其可靠性,提出了深浅两级VLD-FLR复合终端结构。

该终端结构采用深、浅结两级VLD来增加耗尽层的曲率半径,并在其末尾处增加了浓度较高的场限环,以降低终端击穿电压对表面电荷的敏感度。

分析了深浅两级VLD-FLR复合终端的两种工艺实现方案,根据其掺杂剖面对该复合终端进行电特性分析,确定其终端结构参数,并结合器件电场强度分布、电流密度分布及击穿特性曲线研究了复合终端的耐压机理。

最后分析了终端结构参数对终端击穿电压的影响,讨论了深浅两级VLD-FLR终端的工艺容差。

第二,为了解决深浅两级VLD-FLR复合终端芯片面积较大的问题,提出了浅结VLD-FLR复合终端结构,该终端结构只采用了浅结VLD和浓度较高的场限环。

分析了浅结VLD-FLR复合终端的三种工艺实现方案,根据其掺杂剖面对该复合终端进行电特性分析,确定其终端结构参数,并结合器件电场强度分布、电流密度分布及击穿特性曲线研究了复合终端的耐压机理,讨论了浅结VLD-FLR终端的工艺容差。

最后,对比分析了深浅两级VLD-FLR和浅结VLD-FLR复合终端结构的击穿电压、击穿点位置、终端尺寸及工艺容差。

第三,对比分析了高、低温及钝化膜中固定电荷密度对深浅两级VLD-FLR和浅结VLD-FLR复合终端击穿特性的影响,找出最优化的工艺方案。

SBD器件击穿失效机理解析

SBD 器件击穿失效机理解析■MS&MOS 结构●金属(Metal)-半导体(Semi.)接触在所有器件的结构中都起着非常重要的作用。

肖特基二极管就是一种利用势垒金属(M)与硅(Si)接触的MS 整流型器件,故又称之为MS 二极管。

●金属(Metal)-氧化物(Oxide)-半导体(Semi.)结构,即MOS[*]结构无疑是当今微电子技术的核心结构。

甚至PN 结型器件都可以按其物理功能归结到MOS 结构中,例如,肖特基二极管[**]的场板限环结构(包括SiO2表面上的银迁移层及溢流的PbSn 焊料层等异常情况)都可归结为Metal-SiO2-Si 即MOS 结构。

因此,仅以台面器件之规审视外延平面结的肖特基器件是很不够的,必须从MS&MOS 结构入手方可洞察秋毫。

故本文试从研究MOS 结构出发,深入解析SBD 器件金属场板/场氧限环终端结构及击穿失效机理。

[*]由于早期MOS 管ESD 的高失效率,上个世纪60年代,人们给MOS 管一个绰号:摸死管。

[**]1938年肖特基(W.Schottky )首次令人信服地揭示了金属-半导体接触结构中耗尽层的形成以及载流子的输运原理。

在经历74年后的今天,SBD 非但没被其他器件取代,反而在电子整机日益高频化、低功耗、低噪声的应用中展现出强大的生命力。

SBD 长盛不衰的事实被人们形象地描述为长寿的“猫咪胡须”(Cat's whisker)整流器。

■Si-SiO2系统在利用平面工艺制造的硅器件表面上,一般都覆盖一层SiO2薄膜。

这层SiO2对硅表面起着保护作用,对器件的稳定性影响很大。

试验发现在Si-SiO2系统中,存在着多种形式的电荷或能级状态,一般可归纳为四种基本类型。

(1)氧化层可动离子主要是带正电的钠离子、钾离子等。

这些离子在一定温度和偏压下,可在SiO2中迁移,对器件的影响最大的是钠离子。

钠离子来源于化学试剂、气氛、玻璃器皿、治具、高温材料、扩散炉管和舟以及人体污染等。

p-n结的显示与结深的测量

实验 p-n 结的显示与结深的测量在用平面工艺制造晶体管和集成电路中,一般用扩散法制作p-n 结。

由于扩散杂质与外延层杂质的类型不同,所以在外延层中某一个位置,其掺入杂质浓度与外延层杂质浓度相等,从而形成了p-n 结。

将p-n 结材料表面到p-n 结界面的距离称为p-n 结结深,一般用X j 表示。

由于基区宽度决定着晶体管的放大倍数β、特征频率f T 等电参数,而集电结结深X jc 和发射结结深X je 之差就是基区宽度,因此必须了解并掌握测量结深的原理和方法。

测量结深的方法有磨角法、滚槽法,也可以采用阳极氧化剥层法直接计算得出。

本实验采用磨角法。

本实验的目的是学会用磨角器磨角法制作p-n 结,采用电解水氧化法显示p-n 结;并利用金相显微镜测量结深。

一、实验原理在测量结深时,首先要对p-n 结表面进行染色显示,以明确p 区和n 区的界面位置。

本实验采用电解水氧化法显示p-n 结。

该方法简单方便、容易掌握、实验效果好,最大的优点是对同一样片可反复氧化显示,直至清晰满意。

在此,首先介绍电解水氧化法显示p-n 结的原理,然后再介绍用磨角法测量结深的一般过程。

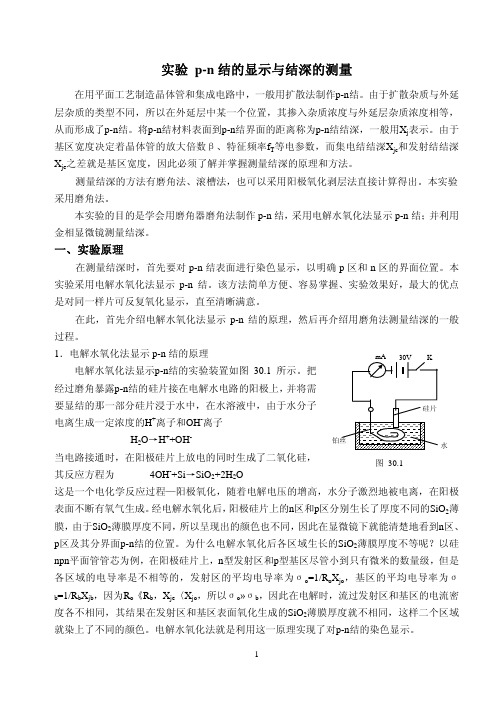

1.电解水氧化法显示p-n 结的原理水图 30.1电解水氧化法显示p-n 结的实验装置如图30.1所示。

把经过磨角暴露p-n 结的硅片接在电解水电路的阳极上,并将需要显结的那一部分硅片浸于水中,在水溶液中,由于水分子电离生成一定浓度的H +离子和OH -离子H 2O →H ++OH -当电路接通时,在阳极硅片上放电的同时生成了二氧化硅,其反应方程为 4OH -+Si →SiO 2+2H 2O这是一个电化学反应过程—阳极氧化,随着电解电压的增高,水分子激烈地被电离,在阳极表面不断有氧气生成。

经电解水氧化后,阳极硅片上的n 区和p 区分别生长了厚度不同的SiO 2薄膜,由于SiO 2薄膜厚度不同,所以呈现出的颜色也不同,因此在显微镜下就能清楚地看到n 区、p 区及其分界面p-n 结的位置。

场板和场限环及其复合使用技术设计及优化

场板和场限环及其复合使⽤技术设计及优化场板和场限环终端技术的原理及优化设计摘要:本⽂分别介绍了场板和场限环以及它们复合使⽤的结终端保护技术的基础理论知识,针对它们各⾃具有的敏感参数,通过优化和实验仿真实现最优耐⾼压设计。

关键词:结终端技术场板场限环⾼压功率器件1.引⾔现代功率器件是在⼀硅⽚上并联上万个相同的单元组成,各单元间表⾯电压⼤致相同,但最外端(终端)单元与衬底间的电压却相差很⼤。

应采取⼀些措施⽤以减⼩表⾯电场,提⾼击穿电压。

这种技术便称为结终端技术JTT(Junction Termination Technique) 【1】.现代硅功率器件⼀般都采⽤浅平⾯结结构,典型的结深值为4-7um 。

在这么浅的结深下,器件如果没有加任何终端保护措施,击穿电压将要⽐理想情况下即平⾏平⾯结的耐压值低50%【2】。

因此结终端保护成为⾼压器件设计的⼀项关键性技术。

结终端保护技术要解决的问题主要是:①采⽤平⾯⼯艺制造的PN 结,杂质原⼦在光刻掩模窗⼝的边⾓区经扩散后形成了柱⾯结和球⾯结, 由于这两个结存在的曲率, 导致电场集中,雪崩击穿将⾸先在这些区域发⽣,从⽽使PN 结的击穿电压降低。

这种效应对浅结深PN 结的影响特别显著(如图1)。

图1 浅扩散平⾯结(a )和深扩散平⾯结(b )电场分布②实际平⾯PN 结(⾮平⾏平⾯结)⼀般都采⽤SiO2作保护层,由于SiO2层内存在可移动电荷和陷阱,SiO2与Si 的界⾯存在固定的正电荷,以及SiO2表⾯还可能粘附其它各种电荷,这些电荷的存在将造成表⾯电场的集中和不稳定,其值较体内平⾏平⾯结的电场⼤2⾄3倍,从⽽严重影响了器件的耐压特性(如图2)。

图2 氧化层有正电荷时的耗尽区因此,结终端保护技术主要是通过增⼤扩散结的曲率半径和降低界⾯(或表⾯)电荷的影响来提⾼器件的耐压⽔平。

场板(Field Plates)、场限环(Field Limiting Rings)及其结合使⽤技术是⽬前在实际应⽤中经常采⽤⼜⼗分有效的结终端保护措施。

终端结构简介

终端结构简介好的终端设计能有效提高器件的耐压、可靠性和降低器件漏电。

终端按基本结构可分为两大类型:延伸型和截断型。

延伸型终端延伸型终端主要是通过在主结外围设置一些特殊结构来降低或分担主结处的高电场,从而起到提高击穿电压的作用。

延伸型的终端结构主要有:场板 (Field Plate,FP)、场限环 (Field Limit Ring,FLR)、结终端扩展 (Junction Termination Extension,JTE)、横向变掺杂 (Variation of Lateral Doping,VLD)、RESURF 等。

1. 场板 (Field Plate,FP)场板可以单独使用降低结电场峰值,提高击穿电压。

另一方面,也可以减少杂质电荷对器件稳定性的影响,此时场板不能作为耐压结构。

若要做耐压结构,需要调整场板的长度,使场板外侧的电场峰值小于P型掺杂区外侧底部的电场峰值。

在图 1.7(a) 中,场板覆盖在结边缘处的场氧上。

1) 当场板上没有施加偏压时,场板不起作用,N 区的耗尽层与柱面结类似。

2) 当场板上施加相对于漏极的正向偏压时,场板会吸引 N- 区的电子向表面移动,从而导致耗尽层向着 P 区收缩,这会增加 P 区外侧的电场强度,从而使击穿电压降低。

3) 当场板施加相对于漏极的负向偏压时,会起到相反的作用,使得耗尽层向外扩张,减小了P 区外侧的电场,从而提高了击穿电压。

如果场板上施加的电压合适,此终端结构能够将柱面结电压提升到平行平面结电压,但是这种方法需要额外的封装引线,并且需要设计场板偏置电路,这在功率器件中是不现实的。

一种有效的方法是将 P 区与场板相连,如图 1.7(b) 所示。

在这种情况下,场板的电势是与P 区相等的负偏压,使得耗尽层向外扩展,在一定程度上可以提高击穿电压。

但同时会在硅表面靠近场板边沿处引入一个高电场,如果设计的不合理也会导致此处提前击穿而降低击穿电压。

场板由于简单有效,直到现在仍然广泛应用,并且出现了电阻场板、多级场板、多段场板等新的技术,而场板与其他终端结构的搭配使用,在提高终端效率、减小表面电荷影响、增加器件稳定性也有帮助。

浮空场限坏终端结构的仿真分析

2 . 1 单场限环结构的分析

为了设计的简化,基 于 B.J .Baliga的击穿电压理 论 ,当主结的耗尽层宽度超过环间距时,浮空场限 环电势与阴极施加偏压的平方根成正比;当施加的 反偏电压不足以使耗尽层从主结越过浮空场环时, 浮 空 场 环 的 电 势 等 于 阴 极 施 加 的 反 向 偏 压 [4]。并求 解出环间距与平行平面结击穿时耗尽层厚度 ! PP的归一化表达为

!S

"n

" m~ " fFR

Wp p ~ ! BUpp ! BU pp

K2L K1

结合电场双曲线变化与电离系数Fulop幂定律

评 估 电 离 积 分 的 方 法 ,可 以 得 到 柱 面 结 归 一 化 击 穿

电 压 BUpp、主 结 电 压 Um与浮空场限环电压Uffr,以

及归一化环间距分别为

神 +2 士 ) 7 ] ~ 亡 ) 7

3 . 2 环宽度的确定

为单个场限环结构中环宽度(W)与击穿电压的 关 系 如 图 1 所 示 。环 间 距 d) 为一个参数。从图中我 们可以注意到对应不同的环间距,增加环的宽度, 击穿电压不一定就增大。 由于在设计中,应考虑通 过使用最小的终端面积来是实现所需要的击穿电 压 能 力 的 大 小 ,是 功 率 器 件 平 面 终 端 设 计 的 一 个 难 点 。不难看出在环宽为20 ! m 之后变化会稍微平缓 一 些 ,所以这个设计中我们将环宽定为20 ! m。

电力电子器件

浮空场限坏终端结构的仿真分析 和参数优化

范 春 雨 ,关 艳 霞 ,潘 福 泉 (沈阳工业大学信息科学与工程学院,辽 宁 沈 阳 ,110870) 摘 要 :为 了 提 高 功 率 半 导 体 器 件 的 耐 压 ,常常在其结构终端上设置浮空场限环,而环宽、环间距以

场板和场限环及其复合使用技术设计及优化

场板和场限环终端技术的原理及优化设计摘要:本文分别介绍了场板和场限环以及它们复合使用的结终端保护技术的基础理论知识,针对它们各自具有的敏感参数,通过优化和实验仿真实现最优耐高压设计。

关键词:结终端技术 场板 场限环 高压 功率器件1. 引言现代功率器件是在一硅片上并联上万个相同的单元组成,各单元间表面电压大致相同,但最外端(终端)单元与衬底间的电压却相差很大。

应采取一些措施用以减小表面电场,提高击穿电压。

这种技术便称为结终端技术JTT(Junction Termination Technique) 【1】.现代硅功率器件一般都采用浅平面结结构,典型的结深值为4-7um 。

在这么浅的结深下,器件如果没有加任何终端保护措施,击穿电压将要比理想情况下即平行平面结的耐压值低50%【2】。

因此结终端保护成为高压器件设计的一项关键性技术。

结终端保护技术要解决的问题主要是:① 采用平面工艺制造的PN 结,杂质原子在光刻掩模窗口的边角区经扩散后形成了柱面结和球面结, 由于这两个结存在的曲率, 导致电场集中,雪崩击穿将首先在这些区域发生,从而使PN 结的击穿电压降低。

这种效应对浅结深PN 结的影响特别显著(如图1)。

图1 浅扩散平面结(a )和深扩散平面结(b )电场分布② 实际平面PN 结(非平行平面结)一般都采用SiO2作保护层,由于SiO2层内存在可移动电荷和陷阱,SiO2与Si 的界面存在固定的正电荷,以及SiO2表面还可能粘附其它各种电荷,这些电荷的存在将造成表面电场的集中和不稳定,其值较体内平行平面结的电场大2至3倍,从而严重影响了器件的耐压特性(如图2)。

图2 氧化层有正电荷时的耗尽区因此,结终端保护技术主要是通过增大扩散结的曲率半径和降低界面(或表面)电荷的影响来提高器件的耐压水平。

场板(Field Plates)、场限环(Field Limiting Rings)及其结合使用技术是目前在实际应用中经常采用又十分有效的结终端保护措施。