13九天ZeniEDA教程

HTCG13ROOT 刷机详解新手指引

HTCG13ROOT 刷机详解新手指引鉴于RUU——即官方制作的系统有很多限制,这给我们的使用带来了很多不便,所以这里特意为新手整理出了一些常见问题以及解决办法,提供给刚入手的新人作为引导。

(1)SOFF/ROOT识别方法相信很多新入手安卓的玩家经常听到ROOT这个词,也经常听说没ROOT的手机就不叫安卓了,但却不明白这是什么意思。

其实,没ROOT过的手机还是能正常使用的,如果你平常不怎么玩手机的话。

如果你只需要能用一般手机所需要的功能就足够的话,建议不要尝试ROOT,毕竟ROOT的过程中也是有风险的。

区别:ROOT:root就是最高权限的意思,可以说是android一种防病毒的方式,也可以说是电脑的administrator管理员。

root是Linux体系中的超等管理员用户帐户,安卓体系是基于Linux 为平台研发的,所以取得root权限后,你就有了系统的最高权力,它可以访问和修改你手机几乎所有的文件,任意删除系统自带程序,修改字体等。

S-OFF,S-ON:S是Security Lock的简写,保护锁的意思。

S-OFF就是保护关。

S-ON就是保护开。

安全锁,是硬件设计商用于保护自己固件不被刷写而设计的。

如果这个安全锁是关闭的,那么对手机内的闪存芯片的刷写保护就关闭了,言外之意就是可以随便刷ROM了,所以,如果你的手机是S-OFF的,那么你就可以随意刷自己喜欢的ROM.SON刷机较SOFF 麻烦,但是也是可以刷机的。

刷机教程详见上面的帖子。

识别方法:查看手机是S-OFF还是S-ON的方法:关机(或是拨电池重装),按住音量-键不放,点一下电源键,看到屏幕亮起就放手,顶部有写S-OFF还是S-ON。

退出查看界面方法:用音量键选到reboot,按开机键确定,手机会自动重启。

查看是否取得ROOT权限很简单,在你的菜单里面看有没有一个权限管理程序,有的话就代表你已经有ROOT权限了,如下图所示(2)常见名词解释一、APK是干求用的?APK 是Android Package 的缩写,即Android安装包.APK 是类似Symbian Sis 或Sisx 的文件格式.通过将APK 文件直接传到Android 模拟器或Android 手机中执行即可安装.简单的说APK就好比电脑的EXE文件.安装APK 的方法:1.在电脑上安装“ 豌豆荚”“91助手”一类的软件,USB连接手机,双击下载在电脑上的APK文件2.从手机端的应用市场下载并安装文件二、ROM是神马?ROM,是用来刷你手机系统的数据文件,也就是Android 系统的封装包,通过手机的工程模式解压安装到手机中形成你手机的操作系统。

kadaas9113使用说明

kadaas9113使用说明

XXX是国内名气较大的智能锁品牌,旗下产品线齐全。

kadaas9113使用说明:XXX指纹锁密码修改设置方法XXX指纹锁开门密码为6位数字,先触摸唤醒区,点亮按键指示灯,输入开门密码加#号结束。

输入两个*号,再输入管理密码加#号进入管理模式,按1进行进入用户设置修改管理密码,找到修改管理密码的安装,根据语音提示就可以。

XXX指纹锁初始管理密码为“12345678”。

XXX指纹录入基本步骤:1、采集,验证指纹时请正确放置手指。

2、方法,将手指放在指纹采集窗上,力度适中,尽量平放。

开锁操作,先触摸唤醒区,点亮按键指示灯,放入已存储手指指纹即可。

XXX指纹锁详细使用说明书:

1、进入管理模式:先输入两个*号,再输入管理密码加#号结尾,即可成功进入管理模式。

2、设置菜单索引,管理模式进入主菜单,然后进行其他菜单操作。

XXX指纹锁使用注意事项温馨提示:XXX所有正品都配备语音操作提示,用户可以按照语音提示进行操作。

安全模式之下,需要同时验证密码和指纹才可以开锁。

另外,用指纹或者密码开锁,验证成功后,如果未能及时转动执手开门,出于安全,系统将在5秒内自动重新上锁。

使用应急钥匙开锁将附带警报,警报声将持续1分钟。

恢复出厂设置以后,全部添加指纹和密码都会清除,需要重新添加。

应急供电,当电池电力耗尽时无法启动系统,可用9V叠层电池连接面板

下端的应急供电口即可启动系统临时开门。

电池电压低于4.8V时,系统语音将提示电量低请更换电池,注意及时更换。

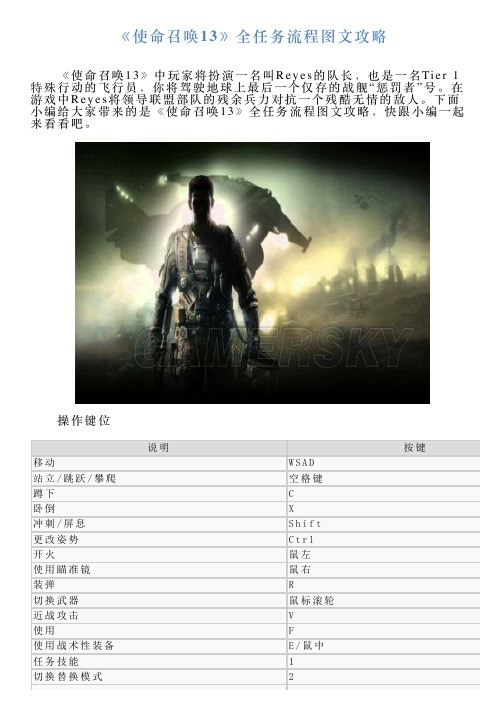

《使命召唤13》全任务流程图文攻略

不久,底格里斯号的费兰舰长赶到。 连线瑞恩斯上将,他说明目前进入与移民防卫阵线的全面战争。目前 能执行任务的战舰只有底格里斯号和征戒号。晋升雷耶斯为中校,任命为 惩戒号的代理舰长。

获知敌人在进攻日内瓦的同时,还袭击了月球港又,那里有重建舰队 需要的重要物资,必须将它夺回来。 此次行动由雷耶斯率队登陆月球,底格里斯号会提供火力支援。

接下来体验一下反重力手雷的作用,这种手雷会制造出一个反重力 场,范围内的目标会失去攻击力,飘浮在空中。 你也可以往自己脚下扔一枚反重力手雷,这样可以浮到空中歼击下面 的敌兵。

来到研发实验室,前方有一群敌兵。 潜行到房间左侧的平台上面,这里居高临下是个不错的伏击点,并且 还有铁箱作为掩体。 率先发动攻袭,将这伙敌人剿灭干净!

step1.靠近港又时,击毙地方FKV上抬头的敌兵,然后车辆就可以撞 进港又内。

step2.奥马尔拉起雷耶斯之后进入到门廊,按F键将舱门打开。 在大厅当中发现这里的大部分平民都是遭到从背后射杀。 在这里要爆发一场战斗,最好的办法就是射击窗户,当窗户破碎之后 强大的气流会将敌兵卷走,随后窗户会检测到破碎而落下卷闸,那么雷耶 斯和他的同伴就能够通过。

大门打开,会有大量的敌兵潮涌过来,在门开的一瞬扔两只猎歼手雷 进去。 然后,躲到门边等着一只机甲人出现。

这只机甲有三个部位可以打残,双腿、左臂和右臂。双腿代表行动 力,左臂是重机枪,右臂是火箭发射器。 如果你先打残它的一只腿,它就失去的行动力,任你欺凌了。

问 题 是 手 上 的 F - S PA R 焊 枪 弹 容 量 少 得 可 怜 , 突 突 几 下 就 弹 尽 了 。 在大厅的两侧各有一个弹药补给点,左边在小屋里,右边在箱子上。 每个补给点只提供一次弹药,所以要珍惜,每批弹药要打残它的一个 部位。 将它的双臂武器打废,它也就完蛋了。

V13授权安装方法

V13授权安装方法V13是一款经典的授权安装软件,可用于自动化安装电脑上的软件和驱动。

在以下的文章中,我将介绍V13授权安装的详细步骤。

请注意,这个方法需要一些技术知识和一些时间,所以请耐心阅读并按照步骤进行操作。

第一步:准备工作2.解压缩安装文件到你选择的目录。

第二步:安装授权2.在安装向导界面,选择“安装授权”并点击下一步。

3.在授权规则页面,选择你希望使用的授权方式。

通常有两种方式可供选择:在线授权和离线授权。

在线授权需要连接到互联网,并且可以即时完成授权。

而离线授权需要用户在联网的情况下生成一个授权文件,然后将该文件导入到V13软件中完成授权。

选择授权方式后,点击下一步。

在线授权方式:4.V13软件会自动检测你的计算机连接到互联网。

如果你的计算机已经连接到互联网,点击“在线授权”按钮。

5.在弹出的授权页面,输入你的授权信息,包括产品密钥和注册码。

这些信息通常会在你购买V13软件时提供。

输入完毕后,点击“授权”按钮。

6.如果授权成功,你将看到一个成功的提示页面。

点击“完成”按钮。

离线授权方式:4.如果你选择离线授权方式,V13软件会生成一个离线授权文件。

请确保你的计算机有互联网连接。

5.点击“离线授权”按钮,在弹出的窗口中选择一个保存授权文件的路径,并点击“保存”按钮。

6.在联网的情况下,将生成的授权文件拷贝到可以访问互联网的计算机上,然后打开V13软件。

7.在V13软件中,选择“导入离线授权文件”并选择你保存授权文件的路径。

点击“导入”按钮。

8.如果授权成功,你将看到一个成功的提示页面。

点击“完成”按钮。

第三步:安装软件和驱动1.在V13软件中,选择你想要安装的软件或驱动,并点击“安装”按钮。

2.V13软件将自动安装所选软件或驱动,并显示安装进度。

3.安装完成后,你可以安装其他的软件或驱动,或者退出V13软件。

凯迪仕9113用户使用说明书6113折页用户手册

请在拆开包装箱后按以下清单仔细核对,如发现有缺漏,请及时向我们或代理商索取。

3.1 安装前门向确认

名 称 备 注 本智能锁可以适用于左外开、左内开、右外开、右内开,四种开向的门。

5.1

如何进入管理模式

重要提示: 根据产品具体型号(后缀数字),阅读和设置相应功能.

1.密码:出厂管理密码为“12345678”,用户密码为空,用户密码为10组6-12位. 2.卡片:管理卡1张,用户卡容量100张. 3.指纹:指纹库为空.指纹容量为100枚. 注意:要求智能锁安装后立刻初始化设置,用户自行添加,以确保安全。(详情见7.6项) 4.低电压报警时,请及时更换相同型号的电池并注意正负极的安装,确保锁的正常使用。 注意:新旧电池不能混用。(详情见7.7-7.8项) 5.长期不用或以防万一,机械钥匙请随身携带,不可放在室内;机械钥匙应急开锁时, 锁会报警一分钟(详情见7.3项)。

密码………… 7 . 1 . 1 卡片………… 7 . 1 . 3

详情见 第5项说明

管理密码

12

底部示意图

4.5

13 12

将连接线穿过锁体过线口。外面板 上的机械钥匙拨片与方轴对准锁体 上的两个转动口插入,使外面板紧 贴门外面。

4.6

将固定板紧贴门内面,旋紧固定 螺丝。

密码………… 7 . 1 . 1

1.无线模块

1.添加遥控 2 .删除遥控 3 .全部删除

4.9

4.10

拧动内外执手、保险旋钮、机械 钥匙,检查各部件是否连接完好。

注意

安装说明使用图片仅供参考,产品以实物为准。

1 .前面板组件( 1个) 2 .连接螺管( 3个) 3 .锁体( 1个) 4 .固定板( 1个) 5 . M6X20十字槽沉头螺钉( 2个) 6 .实心方条( 2个)

伦茨GDC软件操作入门

GDC

操作入门

1、GDC软件综述

� GDC程序可以“在线模式”和“离线模式”使用:

� 离线模式 � 可以在没有与目标系统(控制器)相连接条件下使用。该功能允许离线设定参数、

编程等工作。 � 在线模式 � 通过PC的串口、并口或系统总线实现GDC与目标系统(控制器)间的通讯。该模式

点击Continue 你可以发现Assign AIF module to the basic unit对话 框,在该对话框中你可以指定需要的模块。 � 通过以下列表中的AIF module for ...指定相应的AIF模块。

GDC

操作入门

6、在GDC软件中指定控制器上FIF模块形式

� 如果目标控制器上连接有FIF模块,你可以通 过GDC查看FIF模块对应的参数,以实现FIF模 块参数设置。

� 通过以下列表中的FIF module for ...指定需要的FIF模块。

GDC

操作入门

7、快速调试

� 在目标控制器(变频器或伺服控制器)的说明文档调入GDC中 后,快速调试对话框将自动地出现在GDC的当前界面中。

GDC

操作入门

3、寻找目标系统(在线)

� “Driver connected to bus”的对话窗

� 所有的目标系统和系统所带的AIF/FIF模块都列在“Driver connected to bus”的对话窗中。

� 如果该对话框未出现,可以通过GDC主菜单Window → Drives connected to bus选择该窗体。

GDC

操作入门

LENZE GDC操作入门

制作人:何宇

GDC

目录

操作入门

太极十三式歌诀 精编拳谱

十三势歌诀一名十三势行功歌诀十三总势莫轻视,命意源头在腰隙。

变转虚实须留意,气遍身躯不稍滞。

静中触动动犹静,因敌变化示神奇。

势势存心揆用意,得来不觉费工夫。

刻刻留心在腰间,腹内松静气腾然。

尾闾中正神贯顶,满身轻利顶头悬。

仔细留心向推求,屈伸开合听自由。

入门引路须口授,功夫无息法自修。

若言体用何为准?意气君来骨肉臣。

详推用意终何在?益寿延年不老春!歌兮歌兮百卌字,字字真切义无遗。

若不向此推求去,枉费功夫贻叹息。

【题名解】十三势者,一般将掤、捋、挤、按,採、挒、肘、靠,称为八劲势;进退顾盼定,称为五步。

两者合之,称为十三势。

其实,此乃掤、捋、挤、按,採、挒、肘、靠,进、退、顾、盼、定,十三法。

有说为掤捋、挤按,採挒、肘靠,进退、顾盼、定(中),为六法半的。

应当还有正隅,虚实,收放,吞吐,刚柔,单双,重(轻)之六法半。

此两个六法半合称为十三法。

而由此十三法演化出的攻防拳势,称为十三势。

因为,以阴阳同时存在的法则来看拳势,就出现了掤中有捋,挤中有按,採中有挒,肘中有靠,进中有退,顾中有盼、定(中)分重轻;正中有隅,虚中有实,收中有放,吞中有吐,刚中有柔,单中有双,重(轻)里显定(中)。

反之亦然。

捋中有掤,按中有挤,挒中有採,靠中有肘,退中有进,盼中有顾,定(中)分重轻;隅中有正,实中有虚,放中有收,吐中有吞,柔中有刚,双中有单,轻(重)里显中(定)。

而十二势的法式中皆存在逢中必定分轻重,故定(中),轻(重)这俩“半个法”能说明一势之公用法则的性质,故立为一势而论。

这就是太极拳十三势说法的由来。

如:吞吐法,或吞中有吐,或吐中有吞。

皆是逢中必定,定必用中。

然吞吐之势或轻或重(沉),皆可见景生情而用之;同理,在如:挤按法,或挤中有按,或按中有挤。

亦皆是逢中必定,定必用中。

然挤按之势或轻或重(沉),皆可见景生情而用之。

又名“行功歌诀”者,乃说的是本此诀言的精旨妙义而练功、而运使,才能达到健身、技击,功德艺境并行不悖的预期效果。

9--耶拿Zeenit700原子吸收光谱仪操作维护规程

耶拿Zeenit700原子吸收光谱仪操作维护规程1.火焰模式1.1开机1.2进入操作软件在软件主界面的上部,从左到右排列着Method、Spectrometer、Flame等工具栏图标,一次完整的测量基本上按这些图标依次进行。

但也有些例外,如Autosampler(自动进样器),因该仪器未购置火焰法自动进样器,所以不用设置。

下面按操作步骤逐一进入这些图标的界面。

1.3 Spectrometer图标(光谱参数设置)在Spectrometer图标的界面,从左到右依次有Optical parameters、Energy/Gain、Intergration parameters等标签,操作顺序也基本上按这些标签依次进行。

下面逐一选择这些标签:点界面右下[OK],退出Spectrometer界面1.4 Flame图标(火焰和气体控制)1.5 Calibration图标(校准/ 标样测量)重新点击标签Table,在这里进行测量的具体操作:标线测量结束后,仍在Table标签界面中:1.6 Method图标(方法保存/导入)方法(method),贮存元素灯、分析线、灯电流、狭缝等信息,最重要的是保存了某次测量的标线。

已保存的标线可以在以后调用。

(样品数据的保存和导入见1.7)1.7 Samples图标(样品测量)重新点击Sample table标签,在这里进行测量的具体操作。

测量结束后,仍在Sample table标签界面中1.8 Print图标(结果打印)1.9 关机2.石墨炉模式2.1开机2.2进入操作软件2.3 Spectrometer图标(光谱参数设置)2.4 Furnace图标(石墨炉)2.5 Autosampler图标(自动进样器)2.6 Calibration 图标(校准 / 标样测量)重新点击Table 标签,在这里进行标线测量的具体操作。

标线测量结束后,仍在Table标签界面中2.7 Method 图标(方法保存)2.8 Samples 图标(样品测量)重新点击Sample table标签,在这里进行样品测量的具体操作。

CE傻瓜教程全九课

CE傻瓜教程一:基本操作先简单介绍下什么叫CE,CE的全称是Cheat Engine,最新的版本是6.1(作者是Dark Byte)CE是目前最优秀的游戏修改器,不是之一,这个工具绝对值得你去学习(只要花一点时间就够了)。

忘记金山游侠,GM8,FPE之类的修改工具的吧,CE会让你爱不释手。

一、先下载CE 5.6.1,这个汉化版相当不错哦(不需要安装),推荐各位下载使用。

二、打开CE目录下的2个文件:三、附加进程(图示):CE傻瓜教程二:精确数值扫描接着第一关的操作按下一步进入教程第二关,需要扫描的精确数值是100现在开始搜索精确数值 100 数值中输入100点击首次扫描按钮一般游戏就是4字节,这里不需要改动,默认就好。

这次扫描我们得到 59 个结果,里面肯定有我们要找的那个血值,不过好像太多了。

关键一步:回到 Tutorial 点击打我按钮,此时血值已有变化了:我们再输入 96 点击再次扫描按钮结果只剩1个(这就是我们要找的),我们双击此地址将其添加到地址栏:只有1个结果了,这个就是我们要找的内存地址,双击将其加入到地址栏图示操作:把 95 改成 1000 点击确定按钮此时教程的下一步按钮变成可用闯关成功。

操作虽然简单,但是大家需要明白这其实是一个筛选的过程,这样操作就能把地址找出来。

本关的小技巧:1、双击下图对应位置可快速更改数值。

2、双击地址可快速将其加入到地址栏CE傻瓜教程三:未知初始数值第3关的密码是 419482这一关很重要,因为某些游戏中血显示的不是数字而是血条,这样的话教程2中的方法就失效了。

本关就你要教会你如何修改这些讨厌的未知数此时点击新扫描然后选择未知初始数值点击首次扫描然后出现了肯定是N多的结果,因为太多了,CE没有显示出来。

老办法,回到 Tutorial ,点击打我,CE会告诉你血量减了多少,比如-1这里面我们换个思路,假设CE没告诉我减少了多少或者我根本没看清,这时应该怎么办呢?注意看下面的操作一、扫描减少的数值下拉框,选择减少了的数值,按再次扫描(此时血量减少了)二、扫描不变的数值然后选择没变动的数值(此时血量没有变化)三、反复操作再回到Tutorial ,点击打我 => 扫描减少了的数值 => 扫描没变动的数值反复操作,最后就会只剩14个地址四、简单判断简单判断下(Tutorial中告诉你了这个数值是小于500的),很容易就找到了最终的地址。

德国Zennium电化学工作站安装及使用入门

Zennium电化学工作站安装及使用入门2011年11月18日注意事项:1.防静电:静电会损坏仪器的输入放大器!因此,在接触电极接口或电极引线接头前,需要释放身上的静电。

2.长期不用仪器,电源应断开。

3.仪器所处实验环境,湿度不能超过65%。

4.仪器运行时的环境温度:10°C-30°C。

5.在实验过程中,不要运行杀毒软件的扫描程序。

只能以下列顺序连接电极引线:1.TEST ELECTRODE2.TEST ELECTRODE SENSE3.REFERENCE ELECTRODE4.COUNTER ELECTRODE1.硬件安装安装软件之前,确保计算机:1、计算机运行的是Windows XP或Windows20002、VGA控制器设置为24或32位色彩深度3、电源控制功能(特别是硬盘的休眠模式)要禁用4、在实验过程中,不要运行杀毒软件的扫描程序1.1USBLinkUSB连接器在仪器的后面。

安装Thales软件时将自动安装USB驱动程序。

USBLink支持USB标准1.1和2.0。

安装过程如下:1.用一条标准的USB连接线连接USB-IFC到计算机的USB端口2.从光盘运行其根目录下的setup.exe安装Thales软件3.在仪器设置页面选择USBLink4.保存设置5.按照说明进行操作6.完成安装程序1.2鼠标为了方便操作Thales软件,推荐使用三键鼠标。

返回上一级菜单,终止正在运行的程序和退出会话不作任何改变,需要点击鼠标中键。

我们推荐使用随仪器附带的鼠标。

鼠标设备驱动程序在Thales安装光盘里。

如果需要,它们将随着安装Thales软件自动安装。

2.软件安装Thales-CD文件介绍:2.1安装程序如果Windows的自动运行功能可用,将Thales CD插入光驱会启动安装程序。

数秒后完成装载。

如果没有自动启动,运行CD根目录下的setup.exe。

安装程序将会:1.检查Logitech鼠标安装2.复制Thales文件夹到c:\3.复制Flink文件夹到c:\4.复制系统驱动到Windows\System(32)文件夹(不是用于USBLink!)5.安装Hardcopy软件(可选的)6.选择和配置IM与计算机的接口下面我们逐步看安装过程:启动安装程序后,问是否需要查看帮助文件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

原理图。

• 创建一个新的

library 元件库A

1)Zeni VDE的设计流程

各种图形方式 的设计输入

格式转换

系统编译

读入 标准格式电路描

述语言(如 Hspice 、

写出

VHDL、

EDIF等)

功能模式

输出波形

3)ZeniVERI的设计流程

ZeniVERI 是一个集成版图验证环境,具有百万门级的 版图数据处理能力。它的主要工具包括 设计规则检 查(DRC)、网表提取(NE)、电学规则(ERC)、 网表比较(LVS)等。

• 调用方法2:在原理

图编辑器左侧的快捷 图标中,直接点击快 捷图标,弹出Add Instance的对话框, 通过对Analog库、 PMOS单元和Symbol 视图,NMOS单元和 Symbol视图的选择, 相应的器件符号便可 调用到编辑器窗口中

• 构建方法1:在原理图编辑器的左上角(黄色

圈起部分)为基本器件的快捷方式,直接点 击系统提供的电源符号和地符号,相应的符 号便可调用到编辑器窗口中。

• 分别将Model Setup、Stimulus Setup、Analysis Setup设置

完成后,单击Analog Simulation Deck对话框中<Run>键, 便可运行基于Spice3的仿真验证。

从设计管理器中创建INV单元Symbol 视图

• 在DM界面的Library列表中,将鼠标移置A库

1)ZeniVDE的设计流程

• 该模块是一个可视化的高层次电路设计环境,

它不仅能将设计者以图形方式实现的复杂设 计思想转换成可综合的硬件描述语言(HDL: Handware Description Language)代码,而 且支持多种标准格式的电路描述语言(CDL: Cricuit Description Language),ZeniVDE的 这种功能使之与其他EDA电路设计工具有良好 的接口。此外, ZeniVDE系统中,集成的HDL 语言编译和模拟器、图形设计和模拟调试环 境紧密结合,以保证设计的正确性。

中a单元名的位置,单击鼠标右键,弹出常 用命令菜单。具体如图所示:

按i键,弹出添加的电路图单元, 如图所示

• 在弹出的常用命令菜单中,选择New View命令,弹出

New Cell/View的对话框;具体如图所示:

• Library Name为demo,即demo为

当前工作库CellName为INV,即已 构建的单元名为INV;

• 快捷键: • Shift+Z放大;ctrl+z缩小;Shift+c 复制; q属

性;M+F3镜像; R翻转 ;P引脚 ;

• 根据Analog Simulation Deck的对话框,分别对Model

Setup、Stimulus Setup、Analysis Setup进行设置。

• 设置Model Setup:

缩写为ZeniPDT)提供了一个功能强大的版

图编辑环境,用户可以进行多层次、多单元

的版图编辑,还可以进行多窗口的实时编辑。 版图编辑器PDT还可以调用九天工具中的版 图验证工具(ZeniVERI),实现在线的版图

验证功能,具备层次化编辑和在线设计规则 检查(Online DRC)能力,并提供标准数据 写出接口。

• 再在新建的元件库A

里新建一个单元文件 cell 取名为a,并在 ViewType栏上选择 Schematic原理图工 作页面,然后就可以 在Schematic 上添加 元件,如MOS管, 引脚等,并用导线连 接上。保存 ,检测 电路是否有错误,如 无错误,那一个电路 图就画完了。路程如 下图:

• 在构建反

n

n

p 掺杂半导体衬底

n 型 MOS 管

漏极

源极

衬底 耗尽型电路符号

漏极

源极 衬底

增强型电路符号

漏极

•

pmos管的结构及符号

Cmos管结构

ZeniDM)是九天(Zeni4)系统的总控模块。它对 设计库、设计单元、设计视图等进行统一管理。集 成了原理图编辑器(Schematic Editor)和版图编辑 器(Physical Design Tools)两大支柱工具,同时也 包含库列表编辑器(Library Path Editor)、工艺管 理器(Technology Center)、原理图自动转换为版 图工具(Netlist To Layout)、原理图数据转换工 具(Edif-In/Edif-Out )、版图数据转换工具 (GDS-In/GDS-Out)等多种辅助设计工具。

• 九天EDA工具创建了功能强大的模拟仿真环境,为电

路模拟前的数据准备,以及模拟后的数据分析、结果 返标提供完整服务。

• 九天EDA工具还提供了从原理图到版图的自动生成工

具(Netlist to Layout,N2L),实现了从原理图网表 到版图的映射。

Zeni系列工具功能及特点

• 设计管理器(Zeni Design Manager,缩写为

向器原理 图时,需 要调用基 本器件 PMOS和 NMOS, 九天系统 的系统库 Analog中 提供了一 系列的基 本器件, 可以直接 调用。

画图技巧

• PMOS和NMOS的器件符号调用到编辑器窗口后,单击

鼠标左键,确定器件在编辑器中的位置;取消器件调

用,按<ESC>键,或单击鼠标中键,或在Add

单元库,进行布局布线、自动生成原理图。其生成结果 以EDIF格式描述输出,可以被Cadence、Synopsys、 Mentor等公司的工具直接接受。另外,该工具可以直接 读取Cadence数据库的原理图和网表,进行显示以及提

供给九天系统的验证工sical Design Tools,

九天ZeniEDA教程

制作者: 2010年10月1日

Zeni系列工具概述

• 九天EDA工具为全定制电路设计提供完整解决方案 • 九天EDA工具集成了原理图编辑器(ZeniSE)、版图

编辑器 (ZeniPDT)、版图验证工具(ZeniVERI, ZeniHVERI)、寄生参数 提取工具(ZeniPE)、信号完 整性分析工具(ZeniSI),并将前后端各工具的数据置 于统一的设计管理器之中,为用户提供一个集成化的 设计环境。

在Analog Simulation Deck的对话框中,通过鼠标双击对话框中的Model Setup,便可弹出添加Add Model Setup的对话框;通过<Browse> 键,选择需要的Model文件。

• 设置Stimulus Setup

通过鼠标单击Stimulus Setup前面的小三角标,三角标旋转, 便可看到Zeni工具已自动识别出的原理图中端口A、Vdd、 Gnd,分别用鼠标双击端口名,为其添加激励参数;各端 口具体设置如图所示:

保持一致,用户也可以根据自己的使用需要 定义View Name;单击OK键,便弹出符号图 的编辑窗口,具体如图所示:

•画号之后,连线,添加引脚,并进行仿真

(和电路图仿真一样)。

版图的设计

• Mos 管的结构 • 版图设计的一些规则 • 用Zeni软件画版图

Nmos管结构和符号

源极

栅极

导体

绝缘体

栅极

栅极

使用九天系统进行全定制IC设计的基本流程: 首先将芯片加工需要的工艺信息输入数据库, 然后进行原理图的设计与模拟验证,在得到 正确的原理图和网表后可进行版图设计;最 后在进行版图验证以得到最终正确的版图。

• ERC模块:根据用户命令文件,对有NE提

取的电路进行电学规则检查,检查内容包

括:

• 器件连接性检查; • 节点连器件个数及器件连结点个数; • 短路、开路检查; • 直流通路检查。

• 在符号图的编辑窗口中构建器件符号,如添

加引脚(Add Pin)

,Add Circle

等,具体如下图:

View Name为symbol,即构建单元的新视图类 型为symbol View Type为symbol,通过鼠标 在下拉菜单中选择视图类型为symbol;选定 View Typ时,View Name会自动与View Type

• 它的具体流程如下:

2)ZeniPDT的设计流程

设置环境

建库

个人化设置

层次化编辑

版图验证 ZeniVERT

标准格式版图 读入

数据GDS、

版图数据库

CIF等

写出

• 原理图编辑器(Zeni Schematic Editor,

缩写为ZeniSE)提供了一个显示、建立、编 辑电路原理图的设计环境。支持多窗口的编 辑环境,支持自顶向下或自底向上的层次式 设计方法,支持图形数据转换为网表数据, 支持SPICE、CDL、VHDL、Verilog及混合网 表等类型的网表数据生成。

• 设置Analysis Setup • 通过鼠标双击Analysis Setup,便可弹出 Add Analysis

Setup的对话框;分别设置Step、Stop、Start的参数值,具 体设置如图所示:

设置器件参数 • 在反向器设计中,基本器件PMOS和NMOS

都来自Analog库中,器件的参数都已设置; 在原理图中,只需选中基本器件,单击鼠标 右键,弹出所选器件Property的对话窗口; 在对话框中,分别给PMOS和NMOS填写相 应的参数值(具体可参PLL/INV/Schematic 中的参数设置)。也可用块捷键:选中器件 然后按Q键弹出参数设定对话框,进行参数 设置。

工艺选择

电路原理图输入 与模拟(Zeni VDE)

版图设计 (Zeni PDT)

设计验证 (Zeni VERI)

利用Zeni软件画电路图

• 原理图主要是由

Instance、Pin等