【CPLD Verilog】CPLD实现同步FIFO

verilog同步和异步FIFO,可直接仿真和综合解读

EDA/SOPC课程设计报告题目:同异步FIFO模块的设计与验证姓名:xxx学号:120260320同组人:xxx指导教师:xxx成绩:目录目录 (II)第1章课程设计的要求 (1)1.1 课程设计的目的 (1)1.2 课程设计的条件 (1)1.3 课程设计的要求 (1)第2章课程设计的内容 (2)2.1 设计思路 (2)2.2 软件流程图 (2)2.3 HDL代码阐述 (2)2.4 ModelSim验证 (2)第3章课程设计的心得 (3)第1章课程设计的要求1.1 课程设计的目的●掌握FIFO设计的基本原理与方法●培养Verilog语言模块化设计的思想意识●完成一个FIFO的设计与验证●掌握较大工程的基本开发技能●培养综合运用Modelsim工具进行硬件开发的能力●培养数字系统设计的基本能力●加强对课堂Verilog语言学习的理解与升华1.2 课程设计的条件●设计条件ISE、Modelsim等开发软件的使用1.3 课程设计的要求●设计要求1 设计同步FIFO并验证(包括仿真验证、FPGA验证)●设计要求2 设计异步FIFO并验证(包括仿真验证、FPGA验证)●设计要求3 采用Design Compiler完成其逻辑综合,评估其面积和时序●设计要求4 完成综合后的SDF反标仿真第2章课程设计的内容2.1 设计思路FIFO(First Input First Output),即先进先出队列。

在计算机中,先入先出队列是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令(指令就是计算机在响应用户操作的程序代码,对用户而言是透明的)。

如下图所示,当CPU在某一时段来不及响应所有的指令时,指令就会被安排在FIFO队列中,比如0号指令先进入队列,接着是1号指令、2号指令……当CPU完成当前指令以后就会从队列中取出0号指令先行执行,此时1号指令就会接替0号指令的位置,同样,2号指令、3号指令……都会向前挪一个位置,这样解释大家清楚了吧?在设计之初,我们只对FIFO有一个模糊的了解,只知道它是一个先入先出的队列,但是对于它是如何组成和如何工作并不了解,于是我们设计的首要任务就是查阅资料,逐步完善我们对于同步FIFO和异步FIFO的了解。

verilogfifo读写详细讲解

verilogfifo读写详细讲解FIFO是一种先进先出的数据结构,其全称为First-In-First-Out。

在Verilog中,可以使用以下代码实现FIFO的读写操作。

首先,我们需要定义FIFO的模块。

如下所示:```verilogmodule fifo #(parameter DATA_WIDTH = 8) (input clk, // 时钟信号input reset, // 复位信号input read, // 读使能信号input write, // 写使能信号input [DATA_WIDTH-1:0] data_in, // 输入数据output reg [DATA_WIDTH-1:0] data_out, // 输出数据output reg empty, // FIFO为空信号output reg full // FIFO为满信号);```在FIFO的模块中,我们定义了以下信号:clk表示时钟信号,reset表示复位信号,read表示读使能信号,write表示写使能信号,data_in表示输入数据,data_out表示输出数据,empty表示FIFO为空信号,full表示FIFO为满信号。

在模块的内部,我们可以使用一个或多个寄存器来实现FIFO的功能。

在这里,我们使用两个寄存器data_reg和next_data_reg来存储数据,使用两个计数器empty_count和full_count来记录FIFO的空和满状态。

```verilogreg [DATA_WIDTH-1:0] data_reg; // 数据寄存器reg [DATA_WIDTH-1:0] next_data_reg; // 下一个数据寄存器reg [DATA_WIDTH-1:0] data_out_reg; // 输出数据寄存器reg empty_count; // 空计数器reg full_count; // 满计数器```接下来,我们定义FIFO的行为。

实现fifo的关键代码

实现FIFO的关键代码实现该FIFO的关键部分verilog代码如下:(1)将指向下一个读地址的读指针转为格雷码表示:assign rgraynext = (rbinnext >> 1)^rbinnext。

(2)将指向下一个写地址的写指针转为格雷码表示:assign wgraynext = (wbinnext >> 1)^wbinnext。

(3)将读指针用两级触发器与写时钟同步:always @(posedge wclk or negedge wrst_n)if(!wrst_n) {wq2_rptr,wq1_rptr} <= 0;else {wq2_rptr,wq1_rptr} <= {wq1_rptr,rptr};(4)将写指针用两级触发器与读时钟同步:always @(posedge rclk or negedge rrst_n)if(!rrst_n) {rq2_wptr,rq1_wptr} <= 0;else {rq2_wptr,rq1_wptr} <= {rq1_wptr,wptr};(5)产生写满标志:assignwfull_val = (wgraynext == {~wq2_rptr[ADDRSIZE:ADDRSIZE-1],wq2_rptr[ADDRSIZE-2:0]});always @ (posedge wclk or negedge wrst_n)if(!wrst_n) wfull <= 1’b0;else wfull<= wfull_val;(6)产生读空标志:assign rempty_val = (rgraynext == rq2_wptr);always @ (posedge rclk or negedge rrst_n)if(!rrst_n) rempty <= 1’b1;else rempty<= rempty_val;(7)产生FIFO存储单元,并写入、读出数据:always@ (posedge wclk)if(winc&&!wfull) mem[waddr] <= wdataassign rdata = gp15?mem[raddr] : 16’bzzzzzzzzzzzzzzzz;。

verilog fifo原理

verilog fifo原理FIFO(FirstInFirstOut)是一种常用的存储器结构,用于在数据传输过程中暂存数据。

在数字电路和系统设计中,FIFO被广泛应用于数据缓存、接口通信等领域。

本文将介绍VerilogFIFO的基本原理和设计方法。

一、FIFO的结构FIFO通常由输入端、输出端和存储器组成。

输入端和输出端分别对应数据的输入和输出,而存储器则用于暂存数据。

FIFO的读写操作遵循FIFO的先进先出(FIFO)原则,即最早进入FIFO的数据最先被读取。

在Verilog中,可以使用模块(module)和语句(statement)来实现FIFO。

常见的VerilogFIFO结构包括数据寄存器(dataregister)、读写指针(read/writepointer)、存储器单元(memorycell)和控制逻辑(controllogic)等部分。

二、FIFO的工作原理1.读写操作FIFO的读写操作遵循FIFO的基本原则。

在写操作时,新数据被写入存储器;在读操作时,最早进入FIFO的数据最先被读取。

控制逻辑负责管理读写指针,以确保正确的读写操作顺序。

2.缓冲作用FIFO的主要作用是缓冲数据,即在数据传输过程中,将输入端的数据存储到FIFO中,待FIFO满后再从输出端输出数据。

这样可以在一定程度上缓解数据传输的时序问题,提高数据传输的可靠性和效率。

3.溢出和欠流控制当FIFO满时,控制逻辑会停止新的写操作,以避免数据溢出。

同样地,当FIFO空时,控制逻辑会暂停新的读操作,以防止欠流(underflow)现象的发生。

这些控制逻辑的实现通常需要借助状态机(statemachine)和条件语句(conditionstatement)等Verilog语言特性。

以下是一个简单的VerilogFIFO设计示例:modulefifo(inputwireclk,reset,en_write,en_read,outputwire [7:0]data_out);reg[7:0]data_reg[15:0];//数据寄存器regread_pointer,write_pointer;//读写指针integeri;parameterSIZE=16;//FIFO容量//控制逻辑和状态机always@(posedgeclkorposedgereset)beginif(reset)beginread_pointer<=0;//复位时读写指针都归零write_pointer<=0;for(i=0;i<SIZE;i=i+1)begindata_reg[i]<=8'h00;//清空FIFOendendelseif(en_write)begindata_reg[write_pointer]<={data_reg[write_pointer],data_in };//新数据写入FIFOwrite_pointer<=write_pointer+1;//写指针加一if(write_pointer==SIZE)write_pointer<=0;//FIFO满时归零写指针endelseif(en_read)begindata_out<=data_reg[read_pointer];//读出最早进入FIFO的数据read_pointer<=read_pointer+1;//读指针加一if(read_pointer==SIZE)read_pointer<=0;//FIFO空时归零读指针endelsebegin//其他情况不做处理endendendmodule以上示例中,我们使用了一个16位的数据寄存器和两个指针(read_pointer和write_pointer)来管理FIFO的读写操作。

同步FIFO

Transmit Data in

Data word #n

. .

Data Data Data Data

word word word word

#3 #2 #2 #1

Receive Data Out 图1 FIFO functional diagram

Write Pointer

empty empty Data word #n

FIFO 应用

高速同步数据采集卡

同步FIFO在高速视频图像采集处理系统中的应用 高速同步FIFO存储器在数字信号源中的应用

应用——

高速同步FIFO存储器在数字信号源中的应用

高速数字信号源是数字信号处理系统中的一种常用设备,目的是 输出人为编制的任意数字信号,用来验证和测试后续数字处理设备的 功能和性能指标。对于一个大型的数字系统而言,高速数字信号源的 研制是必不可少的。 数字信号源主要采用CYPRESS 公司的CY7C4245芯片来实现对数据 流的高速转换、处理,其设计思想在多种领域中都具有广泛的应用价 值。

5.在时钟的下降沿处 a.判断读操作时,out_data是否等于exp_data,否则stop; b.cycle_count加1; c.当(fast_write||cycle_count&1’b1)&&~full时,write_n=0, in_data加1; 否则 write_n=1; d.当(fast_read||cycle_count&1’b1)&&~empty时,read_n=0 , exp_data加1,否则read_n=1; e.当full=1时, fast_write=0 ,fast_read=1,filled_flag=1; f.当filled_flag=1&&empty 时,仿真结束; 6.在fifo_count值发生变化时,检测empty、full、half三个状态信号是否正 确;当fifo_count=depth时, fast_write=1 ,fast_read=0, filled_flag=1 。

verilog基本电路设计(包括:时钟域同步、无缝切换、异步fifo、去抖滤波))

Verilog基本电路设计(包括:时钟域同步、无缝切换、异步FIFO、去抖滤波))Verilog基本电路设计共包括四部分:单bit跨时钟域同步时钟无缝切换异步FIFO去抖滤波Verilog基本电路设计之一: 单bit跨时钟域同步(帖子链接:/thread-605419-1-1.html)看到坛子里不少朋友,对于基本数字电路存在这样那样的疑惑,本人决定开贴,介绍数字电路最常见的模块单元,希望给初学者带来帮助,也欢迎大佬们前来拍砖。

如果想要做数字设计,下面这些电路是一定会碰到的,也是所有大型IP,SOC设计必不可少的基础,主要包括异步信号的同步处理,同步FIFO,异步FIFO,时钟无缝切换,信号滤波debounce等等,后面会根据大家反馈情况再介绍新电路。

首先介绍异步信号的跨时钟域同步问题。

一般分为单bit的控制信号同步,以及多bit的数据信号同步。

多bit的信号同步会使用异步FIFO完成,而单bit的信号同步,又是时钟无缝切换电路以及异步FIFO电路的设计基础,这里先介绍单bit信号同步处理。

clka域下的信号signal_a,向异步的clkb域传递时,会产生亚稳态问题。

所有的亚稳态,归根结底就是setup/hold时间不满足导致。

在同一个时钟域下的信号,综合以及布线工具可以在data路径或者clock路径上插入buffer使得每一个DFF的setup/hold时间都满足;但是当signal_a在clkb域下使用时,由于clka与clkb异步,它们的相位关系不确定,那么在clkb的时钟沿到来时,无法确定signal_a此时是否处于稳定无变化状态,也即setup/hold时间无法确定,从而产生亚稳态。

这种异步信号在前后端流程里面是无法做时序分析的,也就是静态时序分析里常说的false_path。

消除亚稳态,就是采用多级DFF来采样来自另一个时钟域的信号,级数越多,同步过来的信号越稳定。

对于频率很高的设计,建议至少用三级DFF,而两级DFF同步则是所有异步信号处理的最基本要求。

使用verilog_hdl实现8位宽,256位的深的同步fifo的实验原理

使用verilog hdl实现8位宽,256位的深的同步fifo的实验原理1. 引言1.1 概述本文旨在介绍如何使用Verilog HDL实现一个具有8位宽和256位深度的同步FIFO(First In, First Out)电路。

FIFO是一种常用的数据缓存结构,被广泛应用于数字系统中,具有先进先出的特性,能够实现数据的有序存储和检索。

文章将从FIFO的简介开始讲解,然后深入探讨同步FIFO设计时需要考虑的要点,并通过使用Verilog HDL进行设计和实现过程,最后对实验结果进行仿真验证、波形分析以及功能测试与性能评估。

1.2 文章结构本文总共包括五个部分。

首先是引言部分,概述了本文的目标和内容。

接下来是实验原理部分,从FIFO基本概念入手,详细介绍了同步FIFO设计时需要注意的要点以及Verilog HDL语言的简介。

然后是设计与实现部分,给出了8位宽、256位深度同步FIFO电路的设计思路,并逐步引导读者完成Verilog HDL代码的编写。

紧接着是实验结果与分析部分,通过仿真验证、波形分析以及功能测试与性能评估来验证所设计的同步FIFO电路是否符合预期。

最后是结论与展望部分,对实验结果进行总结,并探讨未来可能的改进方向和应用领域。

1.3 目的本文的主要目的是介绍使用Verilog HDL实现8位宽、256位深度同步FIFO电路的原理和方法。

读者可以通过本文了解到FIFO的基本原理和设计要点,以及如何使用Verilog HDL进行FIFO电路的实现。

通过本文,希望读者能够掌握基本的数字电路设计技巧和Verilog HDL编程能力,并在实践中提高对于同步FIFO电路设计的理解和应用能力。

同时,读者还可以通过仿真验证和功能测试等手段深入理解所实现的同步FIFO电路的性能特点,并为相关领域的研究与应用提供参考依据。

2. 实验原理:2.1 FIFO简介FIFO(First-In-First-Out)是一种常见的数据缓冲区结构,它的基本原则是按照先进先出的顺序处理输入和输出数据。

利用FPGA实现同步FIFO设置方法

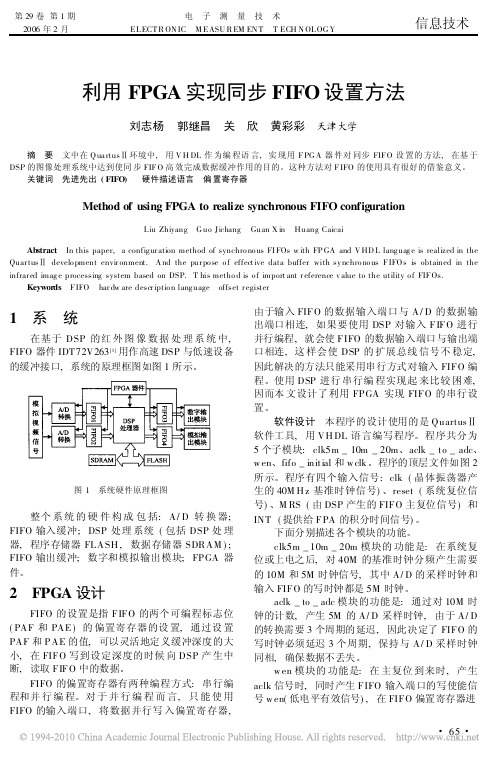

第29卷第1期 2006年2月电 子 测 量 技 术EL ECT R ON IC M EASU R EM EN T T ECH N OL OG Y信息技术利用FPGA 实现同步FIFO 设置方法刘志杨 郭继昌 关 欣 黄彩彩 天津大学摘 要 文中在Q ua rtus 环境中,用V H DL 作为编程语言,实现用F PG A 器件对同步FIF O 设置的方法,在基于DSP 的图像处理系统中达到使同步FIF O 高效完成数据缓冲作用的目的。

这种方法对F IFO 的使用具有很好的借鉴意义。

关键词 先进先出(FIFO) 硬件描述语言 偏置寄存器Method of using FPGA to realize synchronous FIFO configurationL iu Zhiyang G uo Jichang Guan X in Huang CaicaiAbstract In this paper,a config ur ation method of synchro no us FI FOs w ith FP GA and V HD L lang uag e is realized in the Quar tus develo pment envir onment.A nd the pur po se o f effect ive data buffer with sy nchro no us F IFO s is obtained in the infrar ed imag e processing system based on DSP.T his metho d is o f import ant r eference v alue to the utility o f FIF Os.Keywords F IFO har dw are descr iption lang uage offset r egister1 系 统在基于DSP 的红外图像数据处理系统中,FIFO 器件IDT72V263[1]用作高速DSP 与低速设备的缓冲接口,系统的原理框图如图1所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CPLD实现同步FIFO

1 实现原理

CPLD实现8个字节的同步FIFO,实现8个字节数据的缓存。

CPLD内部模块逻辑框图如下所示。

Data_a_we_pulse写数据到FIFO的使能信号。

Data_a_rd_pulse从FIFO读取数据的使能信号。

Data_a_in和Data_a_out分别表示写入FIFO和从FIFO读出的数据的值。

Data_a_we_full指示FIFO写满的状态。

Data_a_rd_nop指示FIFO读空的状态。

2 CPLD代码

module fifo_8B (

clk,

reset_n,

data_a_in,

data_a_we_pulse,

data_a_we_full,

data_a_out,

data_a_rd_pulse,

data_a_rd_nop

);

input clk;

input reset_n;

input [7:0] data_a_in;

input data_a_we_pulse;

output data_a_we_full;

output [7:0] data_a_out;

input data_a_rd_pulse;

output data_a_rd_nop;

//////////////////////////FIFO 写入数据逻辑////////////////////////////

reg [7:0] fifo_mem [7:0]; //FIFO空间,8个8bit的空间

reg [2:0] fifo_we_addr; //FIFO写地址寄存器

reg fifo_we_addr_reverse_pulse; //FIFO写地址翻转状态寄存器,用于指示写//地址是否从最大地址翻转回到最小地址

always@(posedge clk or negedge reset_n)

begin

if(reset_n == 1'b0)

begin

fifo_we_addr <= 3'h0;

fifo_we_addr_reverse_pulse <= 1'b0;

end

else if((data_a_we_pulse == 1'b1)&&(fifo_we_addr != 3'h7)&&(data_a_we_full == 1'b0)) begin

fifo_mem[fifo_we_addr] <= data_a_in; //对应写地址,写入相应的值

fifo_we_addr <= fifo_we_addr+3'h1;

end

else if((data_a_we_pulse == 1'b1)&&(fifo_we_addr == 3'h7)&&(data_a_we_full == 1'b0)) begin

fifo_mem[fifo_we_addr] <= data_a_in;

fifo_we_addr <= fifo_we_addr+3'h1;

fifo_we_addr_reverse_pulse <= ~fifo_we_addr_reverse_pulse;

end

else;

end

//////////////////////////FIFO 读出数据逻辑////////////////////////////

reg [2:0] fifo_rd_addr; //FIFO读地址寄存器

reg fifo_rd_addr_reverse_pulse; //FIFO读地址翻转状态寄存器,用于指示读//地址是否从最大地址翻转回到最小地址

reg [7:0] data_a_out;

always@(posedge clk or negedge reset_n)

begin

if(reset_n == 1'b0)

begin

fifo_rd_addr <= 3'h0;

fifo_rd_addr_reverse_pulse <= 1'b0;

end

else if((data_a_rd_pulse == 1'b1)&&(fifo_rd_addr != 3'h7)&&(data_a_rd_nop == 1'b0)) begin

data_a_out <= fifo_mem[fifo_rd_addr]; //对应读地址,读出相应的值

fifo_rd_addr <= fifo_rd_addr+3'h1;

end

else if((data_a_rd_pulse == 1'b1)&&(fifo_rd_addr == 3'h7)&&(data_a_rd_nop == 1'b0)) begin

data_a_out <= fifo_mem[fifo_rd_addr];

fifo_rd_addr <= fifo_rd_addr+3'h1;

fifo_rd_addr_reverse_pulse <= ~fifo_rd_addr_reverse_pulse;

end

else;

end

//////////////////////////FIFO 满空逻辑////////////////////////////

wire fifo_addr_reverse_flag;

assign fifo_addr_reverse_flag = (fifo_we_addr_reverse_pulse^fifo_rd_addr_reverse_pulse == 1'b1) ? 1'b1 : 1'b0;

reg data_a_we_full;

reg data_a_rd_nop;

always@(posedge clk or negedge reset_n)

begin

if(reset_n == 1'b0)

begin

data_a_we_full <= 1'b0;

data_a_rd_nop <= 1'b1;

end

else if((fifo_rd_addr == fifo_we_addr)&&(fifo_addr_reverse_flag ==1'b1))

begin

data_a_we_full <= 1'b1;

data_a_rd_nop <= 1'b0;

end

else if((fifo_rd_addr == fifo_we_addr)&&(fifo_addr_reverse_flag ==1'b0))

begin

data_a_we_full <= 1'b0;

data_a_rd_nop <= 1'b1;

end

else

begin

data_a_we_full <= 1'b0;

data_a_rd_nop <= 1'b0;

end

end

endmodule

3 仿真结果

3.1 正常写入读取FIFO仿真

如下红色圆框,红色圆框表示向FIFO写入3个字节数据,红色方框表示从FIFO读取出2个字节数据。

其中绿色圆框,表示初始状态无数据,FIFO空,写入一个数据后,空状态无效。

3.2 FIFO写满标志产生

如下红色和绿色圆框,表示写入和读出的数据及顺序,最终FIFO存入8个数据后,FIFO满标志有效,如红色方框所示。

3.3 FIFO读空标志产生

如下红色圆框和绿色方框,表示写入和读出的数据及顺序,最终FIFO数据倍读完,FIFO空标志有效,如红色方框所示。

3.4 正常读写中的空满标志

如下绿色圆框和红色方框,分别表示正常读写状态下,产生的读空标志产生与恢复。