FIFO设计

高速环形FIFO的设计

高速环形FIFO的设计高速环形FIFO(First-In-First-Out)是一种存储器件,用于在数字电路中存储数据。

这种存储器的主要作用是在数据传输时帮助控制信号的流动,并确保信号的有序传输,以防止数据的丢失和混乱。

在这篇文章中,我们将讨论高速环形FIFO的设计。

设计原理高速环形FIFO是一种存储数据的方式,它使用一个环形的缓存来存储数据。

当数据到达时,它被写入环的末端,然后在每个时钟周期内向前移动一个位置。

当数据被读取时,它从环的开头被读取,并在每个时钟周期内向前移动一个位置。

由于这种存储器结构使数据的流动非常有序,所以它可以用于高速数据传输。

高速环形FIFO的设计需要考虑以下几个方面:1. 吞吐量高速环形FIFO的吞吐量取决于它的容量和读写速度。

容量增加时,吞吐量也会相应增加,但是读写速度也会减慢。

因此,需要在容量和速度之间取得平衡。

2. 数据保护在数据传输过程中,需要确保数据的安全和完整性。

因此,在高速环形FIFO的设计中,需要考虑如何保护数据。

一种常见的保护方式是添加一个校验和,以确保数据的完整性。

此外,还可以使用冗余数据来纠正错误,并确保数据的准确性。

3. 数据处理在高速环形FIFO的设计中,还需要考虑如何处理数据。

数据可以通过添加一个处理单元来处理。

该单元可以对数据进行解码、检测和修整等操作,从而提高数据的质量和准确性。

4. 流水线高速环形FIFO的设计可以采用分步处理的流水线方式。

流水线可以加速处理速度,并使处理过程更加高效。

在流水线的每个阶段中,可以添加一个处理单元来处理数据。

这样可以大大提高数据的处理效率。

设计步骤在进行高速环形FIFO的设计时,需要按照下面的步骤进行:1. 确定FIFO的容量和速度要求在开始设计高速环形FIFO之前,需要确定FIFO的容量和速度要求。

容量取决于需要存储的数据量,速度取决于数据传输的速度。

在FIFO的设计中,需要平衡容量和速度,以获得最佳效果。

一般工程上fifo的深度

一般工程上fifo的深度标题:从理论到实际——一般工程中FIFO的深度探究引言:FIFO(First In, First Out)是一种常见的数据存储和传输方式,即先进入队列的数据首先被处理。

在工程应用中,FIFO的深度是一个重要的参数,它决定了存储能力和数据传输的效率。

本文将一步一步回答“一般工程上FIFO的深度”这一主题,介绍FIFO深度的概念、计算方法以及实际应用中的相关考虑因素。

一、认识FIFO的深度FIFO深度是指FIFO队列中可以同时存储的数据数量。

它与队列的大小直接相关,通常以寄存器或存储单元的个数表示。

在设计FIFO深度时,需要考虑数据传输速率、处理要求和缓冲需求等因素。

二、计算FIFO深度的方法1. 根据数据传输速率:FIFO深度应该能够满足数据传输速率的需求。

根据数据传输频率和每个数据包的大小,可以通过以下公式来计算FIFO深度:FIFO深度= (数据传输速率×数据包延迟) / 数据包大小2. 根据处理要求:如果数据需要进行处理或加工,FIFO深度应能够存储足够长的时间,以便处理完成。

此时,可以通过以下公式计算FIFO深度:FIFO深度= 处理时间/ 数据传输周期3. 根据缓冲需求:FIFO深度还可以根据缓冲需求来计算。

如果需要缓冲一定数量的数据,以平衡生产者和消费者之间的速率差异,可以采用以下公式计算FIFO深度:FIFO深度= 缓冲区数据量/ 数据传输速率三、实际应用中的考虑因素1. 数据流量波动性:如果数据流量具有明显的波动性,FIFO深度应能够适应最高峰值,以防止数据丢失。

因此,在设计FIFO深度时,应考虑到流量的峰值和波动范围。

2. 系统延迟要求:如果系统对延迟有严格要求,FIFO深度应足够大,以防止数据在传输过程中发生堆积,导致发送和接收之间的延迟增加。

3. 成本和资源限制:FIFO深度的增加会带来成本和资源的增加,包括电路面积、功耗以及芯片上可用的存储单元数量等。

一种读写深度可配置的异步FIFO设计

引 言

随着设计复杂度 的不断 提高 , 现 代 电子信 息设计 中,

单 一 时 钟 驱 动 已无 法 满 足 设 计 与 应 用 的 需 求 。 基 于 多 时 钟 驱 动 的设 计 已经 越 来 越 普 遍 , 在异 步 时钟域 的设计 中,

Байду номын сангаас

模 块 和读 地址 逻 辑 模 块 是 两 个 相 互 独 立 的 时 钟 域模 块 。 F I F O的空/ 满状态 的 判断 是 F I FO 设 计 中 的 一 个 关 键部分 , 主要 通 过对 读 / 写地 址 的 比较 来 实 现 。鉴 于 读 / 写

状态标 志 的产 生 , 同 时 通

F I F O 的存 储 资 源 没 有 使 用 , 造 成 硬件 资 源 的 浪 费 。

针对这一现状, 本 文 提 出 一 种 读 写 深 度 可 配 置 的 FI F O 设 计 。通 过 对 寄 存 器 的配 置 , 来设定产生有效 F I F O

地 址 的控 制 逻 辑 分 别 工 作 在 各 自 的 时 钟 域 下 , 进 行 比 较

时, 通常将二进制码 的地址 转换 为格雷 码 的编码 方式 , 传 输 到 异 步 时 钟 域 再 进 行 比较 , 以使 亚 稳 态 的 产 生 处 于 可 以

跨 时钟 域 数 据 信 号 传 输 是 必 须 考 虑 的 一 个 问题 。控 制 信 号一般使用握手协议来 实现异步传输 , 对 于 异 步 时 钟 域 大

态时就开始读操作 , 防 止 写 满 后 禁 止 写 操 作 再

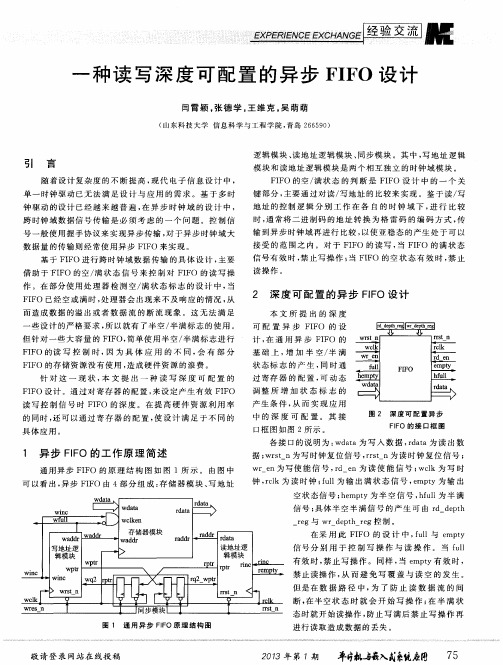

图 1 通用异步 F l F O原 理 结构 图

进 行 读 取 造 成 数 据 的 丢失 。

敬请登录网站在线投稿

FPGA异步fifo设计完整报告

FPGA异步fifo设计完整报告1、名目一、技术规范31、设计完成的功能:32、系统整体框图:33、I/O管脚的描述:34、验证和测试工具选择:45、说明关键模块:46、拟选用的FPGA类型:4二、FIFO总体设计方案5系统功能描述:5电路结构图:5系统的总体输入输出设定6系统时序分析:6关键模块设计分析:7三、FIF0验证方案8FIFO功能:81、概述:82、预确认:83、模块运行确认:94、系统运行确认:9四、仿真激励代码10五、电路设计FIFO源代码11六、FPGA设计FIF0综合布局布线报告:16综合引脚安排:16电路布局布线:16七、时序仿真报告17时序仿真波形:17八、FIFO下载代码和引脚分布17系统输入输出引 2、脚分布:21九、心得体会21技术规范1、设计完成的功能:本试验完成的是8位异步FIFO的设计,其中写时钟100MHz,读时钟为5MHz,其中RAM的深度为256。

当写时钟脉冲上升沿到来时,推断写信号是有效,则写一个八位数据到RAM中;当读时钟脉冲上升沿到来时,推断读信号是有效,则从RAM中把一个八位数据读出来。

当RAM中数据写满时产生一个满标志,不能再往RAM再写数据;当RAM 中数据读空时产生一个满标志,不能再从RAM读出数据。

2、系统整体框图:3、I/O管脚的描述:管脚名称方向H/L电平位宽功能描述rst_ninput3.3V/01全局复位信号rd_eninput3.3V/01读使能低有3、效wr_eninput3.3V/01写使能低有效rd_emptyoutput3.3V/01读空标志高有效wr_fuIIoutput3.3V/01写满标志高有效rd_dataoutput3.3V/08数据输出wr_datainput3.3V/08数据写入cIk_1OOMinput3.3V/01写数据时钟cIk_5Minput3.3V/01读数据时钟4、验证和测试工具选择:ModelsimSE6.If进行前仿真和后仿。

基于FPGA的FIFO存储器设计

基于FPGA的FIFO存储器设计一.FIFO的设计原理FIFO(First In First Out)是先进先出存储器的缩写,它是一种实现数据先进先出的存储器件,通常用作数据缓冲器。

FIFO一般用于不同时钟之间的数据传输,比如FIFO的一端是AD数据采集,另一端是计算机的PCI总线,在两个不同的时钟域间就可以采用FIFO来作为数据缓冲。

另外,对于不同宽度的数据接口也可以用FIFO,例如单片机为8位输出,DSP为16位输出,在单片机与DSP连接时就可以使用FIFO来达到数据匹配的目的。

在实际工作中,对FIFO的数据操作是靠其满/空标志来实现的。

所谓满标志,指的是当对FIFO写数时,如果数据足够多,多到FIFO的内存已经装满了,此时便由FIFO内部状态电路送出一个表示内存已满的信号以阻止对FIFO的写操作。

同理,所谓空标志,指的是当从FIFO读数时,如果数据被读完了,便有FIFO内部状态电路送出一个空标志信号以阻止对FIFO的读操作。

总之,在控制FIFO的读写操作时,必须把握一个原则:写满不溢出,读空不多读。

根据FIFO工作的时钟域不同,可以将FIFO分为同步FIFO和异步FIFO两大类。

同步FIFO是指读时钟和写时钟为同一个时钟,在时钟沿来临时同时发生读写操作;异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

和同步时钟相比,特别是在网络接口、图像处理等方面,异步FIFO应用空间更为广泛。

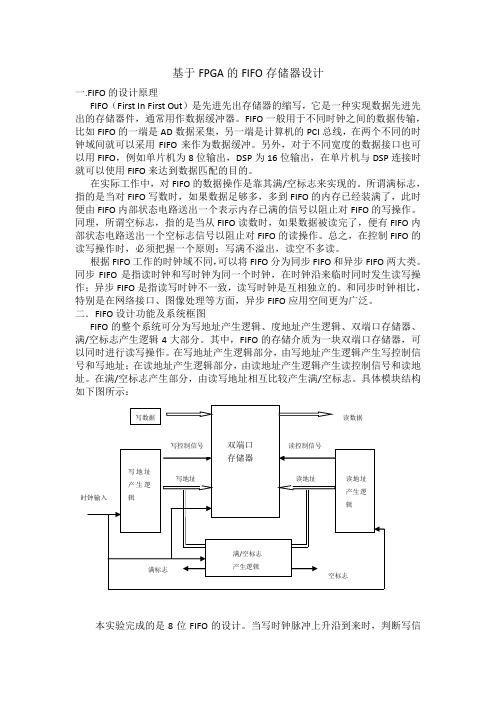

二.FIFO设计功能及系统框图FIFO的整个系统可分为写地址产生逻辑、度地址产生逻辑、双端口存储器、满/空标志产生逻辑4大部分。

其中,FIFO的存储介质为一块双端口存储器,可以同时进行读写操作。

在写地址产生逻辑部分,由写地址产生逻辑产生写控制信号和写地址;在读地址产生逻辑部分,由读地址产生逻辑产生读控制信号和读地址。

在满/空标志产生部分,由读写地址相互比较产生满/空标志。

具体模块结构如下图所示:本实验完成的是8位FIFO的设计。

异步FIFO设计

异步FIFO设计2011.6.22摘要本文采用格雷码设计了一个异步FIFO,经过DC综合的结果如下:时钟频率:1.1GHz面积:10744.447um2功耗:7.791mw目录1. 异步FIFO的设计 (2)1.1 异步FIFO简介 (2)1.2 FIFO的参数 (2)1.3 FIFO的设计原理 (2)1.4 FIFO的设计模块 (6)1.5 用modelsim仿真FIFO (11)1.6 用DC对FIFO进行综合 (13)2.参考文献 (15)1. 异步FIFO的设计1.1 异步FIFO简介FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,它与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

根均FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。

同步FIFO是指读时钟和写时钟为同一个时钟。

在时钟沿来临时同时发生读写操作。

异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

异步FIFO(Asynchronous FIFO),一般用于不同时钟域之间的数据传输,比如FIFO 的一端连接频率较低的AD数据采样信号,另一端与计算机的频率较高的PCI总线相连。

另外,对于不同宽度的数据接口也可以用AFIFO,例如单片机为8位数据输出,而DSP可能是16位数据输入,在单片机与DSP连接时就可以使用AFIFO来达到数据匹配的目的。

由于实际中,异步FIFO比较常见。

为了便于描述,在后面的章节中将异步FIFO 简称为FIFO.1.2 FIFO的参数FIFO的宽度:进行一次读写操作的数据的位宽。

FIFO的深度:双口存储器中能容纳的数据的总数。

满标志:FIFO已满或将要满时由FIFO的状态电路送出的一个信号,以阻止FIFO的写操作继续向FIFO中写数据而造成溢出。

FIFO设计

• 4) FULL信号控制进程 • 如何判断FULL信号为‘1’;

• 1、当前没有读/写数据有效信号,FIFO数 据已满 • 2、当前没有读有效信号,有写有效信号, 而且FIFO还差一个就满了。

• 4) FULL信号控制进程

•

Process(clk,reset) begin if reset='1' then full_mid<='1'; elsif rising_edge(clk) then if (rd_enable='0' and (fifo_cnt(8 downto 1) = "11111111") and ((fifo_cnt(0)='1') or (wr_enable='1'))) then full_mid<='1'; else full_mid<='0'; end if; end if; end process;

同步FIFO的操作

1、 同步FIFO的操作 当FIFO不满且wr_en有效时,向FIFO写数据,并 置写使能wr_enable有效; 当FIFO不空且rd_en有效时,从FIFO从读出数据 并置读使能rd_enable有效; 当FIFO满且wr_en有效时,置写使能wr_enable

无效且作废此次写操作; 当FIFO空且rd_en有效时,置读使能rd_enable 无效且作废此次读操作。

异步FIFO的设计

• 异步FIFO的数据读、写受不同时钟的控制; • 异步FIFO的空、满状态不能依靠计数的方 式进行,因为读、写均需要对计数器进行 操作; • 如何判断异步FIFO的空、满情形?如何操 作?

异步FIFO的设计文档

异步FIFO的设计版本v1.02011-05-06异步FIFO的设计一.功能描述本设计用16*8 RAM实现一个异步FIFO,具体功能定义如下:1. 异步复位。

2. FIFO不为满时,当写使能有效时,在写时钟的上升沿向FIFO中写入数据。

3. FIFO不为空时,当读使能有效时,在读时钟的上升沿从FIFO中读出数据。

4. 当FIFO写满的时候,产生满信号;当FIFO读空的时候,产生空信号。

5. FIFO一旦空或者满时候,复位FIFO;二.输入输出信号描述信号名输入/输出目标/源功能描述Rclk Input Pin 读时钟频率,10M ,占空比1:1。

Wclk Input Pin 写时钟,频率10M ,占空比1:1。

data_in[7:0] Input Pin 8位的输入数据rd_en Input Pin 读使能,高电平有效,在FIFO非空时,CLK上升沿读入数据;wr_en Input Pin 写使能,高电平有效,在FIFO非满时,CLK上升沿写入数据;Rst Input Pin 异步清零,低电平有效,低电平时读地址,写地址,计数器都清零。

三顶层划分图1 系统框图顶层模块说明:1.RAM :存储器模块,用于存放及输出数据;2.Waddr_Reg : 保存访问RAM的写地址;3.Raddr_Reg : 保存访问RAM的写地址;4.Wbin_addr : 计算RAM下一个写地址;5.Rbin_addr : 计算RAM下一个读地址;6.Gwaddr_reg : 将写地址的二进制编码转换成格雷码,并保存;7.Graddr_reg : 将读地址的二进制编码转换成格雷码,并保存;8.Syn_Rfield : 将写地址同步到读时钟域,并产生空标志;9.Syn_Wfield : 将读地址同步到写时钟域,并产生满标志;10、Reset_Unit : 复位信号产生单元设计思想说明:1、由于实现的异步FIFO,分别用不同的读、写时钟产生读写地址,因此FIFO 的判空和判满是本设计中的一个难点。

高速异步FIFO设计-

课程设计报告高速异步FIFO设计目录技术规范 (3)FIFO的功能描述 (3)FIFO的引脚定义 (3)总体方案设计 (4)电路设计方框图 (4)电路设计连接图 (4)电路模块及其功能简介 (4)电路设计思想 (5)仿真方案及其仿真激励源代码 (8)仿真方案 (8)仿真激励源代码 (8)电路描述代码 (9)功能仿真 (14)分块仿真 (14)双口RAM仿真 (14)读数据控制电路仿真 (15)写数据控制电路仿真 (16)锁存器电路仿真 (16)满空标志电路仿真 (17)总体仿真 (18)综合与布局布线 (18)综合布局布线报告 (19)报告数据分析 (19)时序仿真 (19)实验心得 (20)一、技术规范1、FIFO的功能描述高速异步FIFO(First In First out)深度为256,数据宽度为8位(最大可存储256byte),可实时给出FIFO的满空标志,并可实现数据的平滑输出,其写时钟为带间隔的100MHz,读时钟为5MHz,从而实现了FIFO的异步数据传输。

2、FIFO的应交定义(3)写数据控制器引脚对照表:(4)读数据控制器引脚对照表:二、总体设计方案1、电路设计方框图(如图2.1所示)图2.12、电路设计连接图(如图2.2所示)3、电路模块及其功能简介双口256*8bit的RAM:用于存储FIFO的缓冲数据写数据控制器:用于控制FIFO中数据的写时序操作FIFO 读数据控制器:用于控制FIFO数据中的读时序操作锁存器:用于锁存上一个clock时的读写地址指针FIFO满空标志电路:用于实时标志FIFO的满空状态4、电路设计思想设计高速异步FIFO,首先,考虑如何实现数据的先进先出问题;为了解决这个问题,设计中就必须有一个可用于随机存取的存储器,又要实现异步,即异步读写,所以本设计中存储器选择采用双口RAM;其次,考虑如何实现在不同时钟下,实现读数据和写数据,在设计中,使用独立电路模块,分别控制读写操作;最后,一个要考虑的问题也是本设计中的难点,即对于高速异步FIFO来说,如何高速、实时判断FIFO的满和空。

高速异步FIFO的设计和实现

万方数据路中,这一信号最终会朝着0和1两个稳态转换,变成稳定的信号。

这一变换所需的时间取决于寄存器的结构和参数,通常在一个时钟周期内可以完成这一从亚稳态到稳态的转换。

所以,在设计中普遍采用两级寄存器串接的同步器来对信号进行同步,如图1所示。

图1解决亚稳态的同步器电路2.2毛刺单根信号的同步采用图1所示的同步电路即可消除亚稳态问题。

然而,对多位总线信号的同步,除了亚稳态外,还有一个重要的问题就是毛刺现象。

如果需要同步的总线的多位同时发生变化,由于在实际电路中各位的延时不可能完全一致,因此中间就可能会产生毛刺现象。

而用另一个频率相位完全不同的时钟采样的时候就有可能采样到毛刺信号,造成错误的同步。

例如,FIFO的读写指针是一个二进制计数器,当它从l计数到2时,位0从1变成0,位l从0变成1。

如果位0从1变成0的延时比位1从0变1要大,就会在1和2中间多出一个毛刺3,而如果直接用图l的同步电路同步,就有可能错误地在另一个时钟域得到一个3的结果。

对于FIFO的设计来说,这样的同步错误是致命的,会造成空满判断的失误。

解决这一问题就是需要采用无毛刺的电路结构,无毛刺电路要求信号同步前必须被寄存器锁存,并且每次只有一位发生变化。

例如,文献[2]中设计的FIFO就采用格雷码来避免这一问题。

3高速异步FIFO结构3.1基本结构本文设计的高速异步FIFO结构如图2所示,主要包括数据通路reg—file和控制模块fifo—eft两个部分。

reg—file模块是FIFO的存储器部分;fifo_eft模块负责FIFO的读写控制,如读写指针的产生和空满信号的产生。

图2高速异步FWO结构框图本设计的外部端口如表l所示。

3.2reg__file模块设计FIFO的存储器部分可以采用双端口SRAM或者用DFF寄存器搭建存储部分。

由于本设计为32×32的FIFC,存储器容量不大,采用双端口SRAM由于powerring等因素,面积会比用寄存器搭建要大,速度也不容易达86到500MHz的高速。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

异步FIFO的设计

FIFO体的描述

读指针被写时钟采样的模块

写指针被读时钟采样的模块

判 别 为 空 的 设 计 模 块

FIFO

判 别 为 满 的 设 计 模 块

FIFO

异 步 结 构

FIFO

关于异步FIFO设计更多的资料

//FIFO读操作 if ((Rreq==1’b1) && (Count >0)) begin RData <= FIFO[Rptr]; Rptr <= (Rptr +1 ) %N; REn <= 1’b1; end else REn <= 1’b0;

1. HDL设计描述是否存在问题?

//Count 计数 if ((Rreq==1) && (Wreq!=1) && Count >0) Count = Count -1; if ((Wreq==1) && (Rreq!=1) && Count <N) Count = Count +1;

同步FIFO的操作

FIFO 的初始化只进行一次,FIFO的读进程、 写进程、Count的计数进程相互之间并行。 如何将上述进程(算法)转化为相应的硬件 实现?

同步FIFO设计

• 根据FIFO的大小N,决定Count、Wptr、 Rptr的位宽log2N; • 设置寄存器分别保存Count、Wptr、Rptr的 值; • 同步FIFO必须有异步Reset; • 当FIFO复位时,Count=0,Wptr=0, Rptr=0; • FIFO正常操作时,受时钟控制。

异步FIFO的设计

• 异步FIFO的数据读、写受不同时钟的控制; • 异步FIFO的空、满状态不能依靠计数的方 式进行,因为读、写均需要对计数器进行 操作; • 如何判断异步FIFO的空、满情形?如何操 作?

如何判断异步FIFO的空、满?

异步FIFO为空条件: Reset情形下,异步FIFO为空; 在正常读、写情形,当读指针追上写指针, 异步FIFO为空。 异步FIFO为满条件: 在正常读、写情形,读、写指针相同,且 写指针追上读指针时。 读、写指针均相同时,FIFO到底是空还是满?

HDL 设计描述实例

----FIFO设计

国防科技大学计算机学院微电子研究所610室

曾献君

FIFO类型

• 同步控制的FIFO FIFO的读写时钟相同。 • 异步控制的FIFO 用于跨时钟域的数据交换; FIFO的读写时钟不同、读写时钟之间不一 定存在相位、周期方面的约束关系;

同步FIFO设计

同步FIFO存在3种状态: 空; 满; 非空非满 FIFO为空,不可从FIFO读数据,但可写; FIFO为满,不可向FIFO写数据,但可读; 非空非满时,FIFO可读、可写。 FIFO的读写受同一时钟控制; FIFO的大小为N字

同步FIFO的操作

1、 同步FIFO的外部接口信号

时钟信号clk:控制FIFO的读写; 写请求信号Wreq: 向FIFO发送写请求信号; 写数据WData[Size-1:0] : 写数据; 写有效信号WEn:WEn=1表示写有效,否则写无 效,作废写请求,并使写请求等待; 读请求信号Rreq: 向FIFO发送读请求信号; 读数据RData[Size-1:0] : 读数据; 读有效信号REn:REn=1表示读有效,否则读无 效,作废读请求,并使读请求等待;

同步FIFO的操作

• FIFO的操作可用下述几个进程表示: 1)初始化进程: Count = Wptr = Rptr =0; 2)FIFO读进程: if (Rreq ==1 && Count >0) begin RData = FIFO[Rptr]; Rptr = (Rptr +1 )mod N; REn = 1; end

always @(posedge clk or negedge Reset) if (~Reset) REn <= 1’b0; else //FIFO读操作 begin if ((Rreq==1’b1) && (Count >0)) begin RData <= FIFO[Rptr]; Rptr <= (Rptr +1 ) %N; REn <= 1’b1; end else REn <= 1’b0; end

module Synch_FIFO(clk, Reset, Wreq, WData, Rreq, RData, WEn, REn); parameter Size = 64; input clk; input Reset; input Wreq; input [Size-1] WData; input Rreq; output [Size-1] RData; output WEn; output REn;

end

2. 问题出现在哪里?

3. 如何改进设计描述?

always @(posedge clk or negedge Reset) if (~Reset) begin always @(posedge clk or negedge Reset) Count <= 0; if (~Reset) //初始化 Wptr <= 0; WEn = 1’b0; Rptr <= 0; else end begin // FIFO 写操作 else if ( (Wreq ==1’b1) && (Count < N)) begin //Count 计数 begin if ((Rreq==1) && (Wreq!=1) && Count >0) FIFO[Wptr] <= WData; Count = Count -1; Wptr <= (Wptr +1) % N; if ((Wreq==1) && (Rreq!=1) && Count <N) WEn <= 1’b1; Count = Count +1; end end else WEn <= 1’b0; end

同步FIFO的操作

3) FIFO 写进程

if (Wreq==1 && Count < N) begin FIFO[Wptr] = WData; Wptr = (Wptr +1) mod N; WEn = 1; end

4) Count 计数进程

if (Wreq ==1 && Count < N && Rreq !=1) Count = Count +1; if (Rreq == 1 && Count >0 && Wreq !=1) Count = Count -1;

同步FIFO的操作

1、 同步FIFO的操作

当FIFO不满且Wreq有效时,向FIFO写数据,并 置写使能WEn有效; 当FIFO不空且Rreq有效时,从FIFO从读出数据 并置读使能REn有效; 当FIFO满且Wreq有效时,置写使能WEn无效且 作废此次写操作; 当FIFO空且Rreq有效时,置读使能REn无效且作 废此次读操作。

同步FIFO的操作

问题: 1. 如何判断FIFO为空、满? 2. FIFO的读写操作的位置如设置一个Count计数器,用于计数FIFO中的 元素的个数,Count<=N; 设置FIFO的读指针Rptr,0<=Rptr <= N-1; 设置FIFO的写指针Wptr,0<=Wptr <= N-1; FIFO初始操作时,Count=0, Rptr = Wptr = 0.

parameter L = log2N ; reg [Size-1] RData; reg WEn, REn; reg [L-1:0] Count; reg [L-1:0] Wptr; reg [L-1:0] Rptr;

always @(posedge clk or negedge Reset) if (~Reset) //初始化 begin Count <= 0; Wptr <= 0; Rptr <= 0; end else begin // FIFO 写操作 if ( (Wreq ==1’b1) && (Count < N)) begin FIFO[Wptr] <= WData; Wptr <= (Wptr +1) % N; WEn <= 1’b1; end else WEn <= 1’b0;