第六章时序逻辑电路-习题

触发器及时序电路(5-6章)练习题2015 - 副本

触发器及时序电路(5-6章)练习题姓名:_______________________________ 学号:_________________________________一、是非题(请判断下列各题内容正确与否,分别用√及×填在题末( )内。

共计6小题,每小题1分)1. 凡是时序电路,一定有公共的时钟信号CP . ( )2.触发器的输出状态完全取决于同一时刻的输入状态。

( ) 3. 对于图示某时序电路的状态转换图,可以判定该电路的循环长度为5,且可以自启动.( ) 4. 计数器的模就是构成计数器的触发器个数. ( )5. 当时序电路的状态图确定后,若用SSI 电路设计时,应选择触发器的数目k ≥log 2r ,r 为状态数目. ( )6.对JK 及D 两种触发器来说,令D=J=K 时,这时两种触发器的功能完全等效。

( )二、单项选择题(请选择正确答案,将其代号填入题末空格内。

共计8小题,每小题1分) 7. 下列触发器中,不能构成移位寄存器的是 。

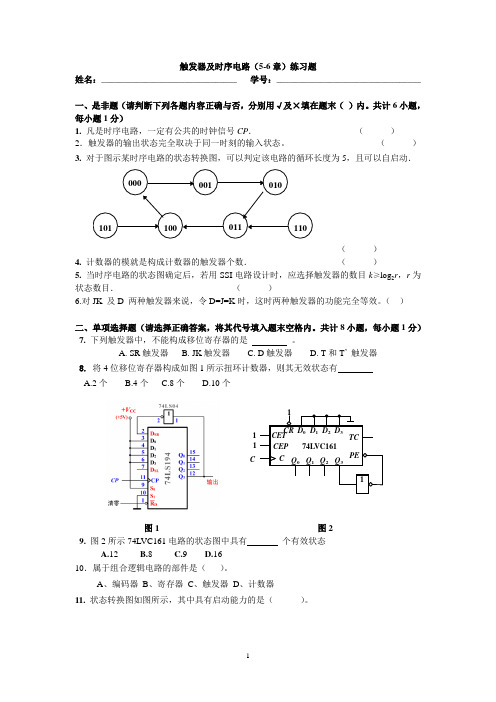

A. SR 触发器B. JK 触发器C. D 触发器D. T 和T ’ 触发器 8. 将4位移位寄存器构成如图1所示扭环计数器,则其无效状态有 A.2个 B.4个 C.8个 D.10个图1 图29. 图2所示74LVC161电路的状态图中具有 个有效状态A.12B.8C.9D.16 10.属于组合逻辑电路的部件是( )。

A 、编码器B 、寄存器C 、触发器D 、计数器 11. 状态转换图如图所示,其中具有启动能力的是( )。

C P12.同步计数器和异步计数器比较,同步计数器的显著优点是( )A 、工作速度高B 、触发器利用率高C 、电路简单D 、不受时钟CP 控制。

13.某移位寄存器的时钟脉冲频率为100KHZ ,欲将存放在该寄存器中的数左移8位,完成该操作需要( )时间。

A 、10μSB 、80μSC 、100μSD 、800ms 14.某电视机水平-垂直扫描发生器需要一个分频器将31500HZ 的脉冲转换为60HZ 的脉冲,欲构成此分频器至少需要( )个触发器。

第6章 时序逻辑电路

J 和 K 接为互反,相当于一个D触发器。时钟相连 是同步时序电路。

电路功能: 有下降沿到来时,所有Q端更新状态。

2、移位寄存器 在计算机系统中,经常要对数据进行串并转换,移 位寄存器可以方便地实现这种转换。

左移移位寄存器

•具有左右移位功能的双向移位寄存器

理解了前面的左移移位寄存器,对右移移位寄存器 也就理解了,因位左右本身就是相对的。实际上,左右 移位的区别在于:N触发器的D端是与 Q N+1相连,还是 与Q N-1相连。

第六章 时序逻辑电路

如前所述,时序逻辑电路的特点是 —— 任一时刻 的输出不仅与当前的输入有关,还与以前的状态有关。

时序电路以触发器作为基本单元,使用门电路加以 配合,完成特定的时序功能。所以说,时序电路是由组 合电路和触发器构成的。

与学习组合逻辑电路相类似,我们仍从分析现成电 路入手,然后进行时序逻辑电路的简单设计。

状态化简 、分配

用编码表示 给各个状态

选择触发器 的形式

确定各触发器 输入的连接及 输出电路

NO 是否最佳 ?

YES

设计完成

下面举例说明如何实现一个时序逻辑的设计:

书例7-9 一个串行输入序列的检测电路,要求当序

列连续出现 4 个“1”时,输出为 1,作为提示。其他情 况输出为 0。

如果不考虑优化、最佳,以我们现有的知识可以很

第二步: 状态简化

前面我们根据前三位可能的所有组合,设定了 8 个

状态A ~ H,其实仔细分析一下,根本用不了这么多状态。

我们可以从Z=1的可能性大小的角度,将状态简化为

4 个状态:

a

b

c

d

A 000

B 100

D 110

习题课时序逻辑电路分析

习 题 课

例题一

画出图1 所示电路的状态图和时序图(设初始状态为00,X为输 入控制信号,可分别分析X=0和X=1时的情况)。

2013-8-3

时序电路

2

例题二

画出图2 所示电路的状态图,简要说明电路的功能特点。

2013-8-3

时序电路

3

例题三

分析图3 所示电路的逻辑功能。

2013-8-3

图6 (a)(b) 所示电路的计数长度N是多少?能否自启动?

图6 (a)

2013-8-3

时序电路

9

图6 (b)

2013-8-3

时序电路 10

认 真 复 习

迎 接 考 试

数 字 电 路

2013-8-3 时序电路 11

时序电路

4

例题四

画出图3(a)电路中B、C端的波形。输入端A、CP波形如图(b) 所示,触发器起始状态为零状态。2013-8-3Fra bibliotek时序电路5

2013-8-3

时序电路

6

例题五

分析图5(a) (b)所示电路的逻辑功能。

图5(a)

2013-8-3

时序电路

7

图5 (b)

2013-8-3

时序电路

8

例题六

习题6答案——精选推荐

习题6答案习题 66.1 试分析图6.83所⽰同步时序电路,写出驱动⽅程、状态⽅程和输出⽅程,并作出状态转换图,设初始状态全为0。

答案6.111001100011010D Q Q ,D Q ,Q Q Q ,Q Q ,Y Q Q ++=====n n 。

状态转换图见图P6.16.2 试分析图6.84(a)所⽰电路,写出驱动⽅程、状态⽅程和输出⽅程,并画出对应输⼊信号X 的输出Q 2、Q 1和Y 的波形(设起始状态为00)。

答案6.2 时序图见图P6.2。

驱动⽅程X K X J X K XQ J 22121====状态⽅程221n 21121n 1Q X XQ Q Q X Q XQ Q +=+=++ 输出⽅程1XQ Y =6.3 试分析图6.85所⽰电路的计数顺序,画出电路的状态转换图,判断是模⼏计数器,有⽆⾃启动功能。

(a) 电路 (b) 输⼊波形图6.84 题图6.2图6.83 题图6.1第6章时序逻辑电路98图6.85 题图6.3答案 6.3 2323123312121231Q Q Y Q K Q Q J Q Q K Q J 1K Q Q J =======模七进制6.4 试分析图6.86时序电路的逻辑功能,写出电路的驱动⽅程、状态⽅程和输出⽅程,画出电路的状态转换图。

答案6.4 驱动⽅程1K Q Q J 1K 1J 1K Q J 321322131======状态⽅程3121n 3121n 2131n 1Q Q Q Q Q Q Q Q Q Q =↓?==+++6.5 试分析图6.87所⽰的时序电路,写出电路的驱动⽅程、状态⽅程和输出⽅程,画出电路的状态转换图,设初始状态全为0。

答案6.5 D 0 = A ⊕Q 0,T 1 = Q 0,Y = AQ 1,状态转换图见图P6.5。

图6.86 题图6.4 图6.87 题图6.56.6 试分析图6.88所⽰的时序电路,画出在时钟CLK 作⽤下,Q 1的输出波形。

时序逻辑电路练习题

一、填空题1. 基本RS触发器,当R、S都接高电平时,该触发器具有____ ___功能。

2.D 触发器的特性方程为___ ;J-K 触发器的特性方程为______。

3.T触发器的特性方程为。

4.仅具有“置0”、“置1”功能的触发器叫。

5.时钟有效边沿到来时,输出状态和输入信号相同的触发器叫____ _____。

6. 若D触发器的D端连在Q端上,经100 个脉冲作用后,其次态为0,则现态应为。

7.JK触发器J与K相接作为一个输入时相当于触发器。

8. 触发器有个稳定状态,它可以记录位二进制码,存储8 位二进制信息需要个触发器。

9.时序电路的次态输出不仅与即时输入有关,而且还与有关。

10. 时序逻辑电路一般由和两部分组成的。

11. 计数器按内部各触发器的动作步调,可分为___ ____计数器和____ ___计数器。

12. 按进位体制的不同,计数器可分为计数器和计数器两类;按计数过程中数字增减趋势的不同,计数器可分为计数器、计数器和计数器。

13.要构成五进制计数器,至少需要级触发器。

14.设集成十进制(默认为8421码)加法计数器的初态为Q4Q3Q2Q1=1001,则经过5个CP脉冲以后计数器的状态为。

15.欲将某时钟频率为32MHz的CP变为16MHz的CP,需要二进制计数器个。

16. 在各种寄存器中,存放N位二进制数码需要个触发器。

17. 有一个移位寄存器,高位在左,低位在右,欲将存放在该移位寄存器中的二进制数乘上十进制数4,则需将该移位寄存器中的数移位,需要个移位脉冲。

18.某单稳态触发器在无外触发信号时输出为0态,在外加触发信号时,输出跳变为1态,因此其稳态为态,暂稳态为态。

19.单稳态触发器有___ _个稳定状态,多谐振荡器有_ ___个稳定状态。

20.单稳态触发器在外加触发信号作用下能够由状态翻转到状态。

21.集成单稳态触发器的暂稳维持时间取决于。

22. 多谐振荡器的振荡周期为T=tw1+tw2,其中tw1为正脉冲宽度,tw2为负脉冲宽度,则占空比应为_______。

时序电路练习题

时序电路习题一、填空1、寄存器存放数据的方式有____________和___________;取出数据的方式有____________和___________。

2、双拍工作方式的数码寄存器工作时需_____________。

3、按计数器中各触发器翻转时间可分为_________,________。

4、触发器有______个稳定状态,所以也称____________。

5、时序电路主要由________和 ________所构成,是一种具有_______功能的逻辑电路,常见的时序电路类型有___________和__________6、计数器的功能是_______________________,按计数时个触发器状态转换与计数脉冲是否同步,可分为__________和________。

_________计数器是各种计数器的基础。

7、4个触发器构成的8421BCD 码计数器,共有_______个无效状态,即跳过二进制数码_______到_______6个状态。

8、具有3个触发器的二进制计数器,他又_______种计数状态;具有4个触发器的二进制计数器,它有_____种计数状态。

9、10. 1n n n Q JQ KQ +=+是_______触发器的特性方程。

11、1n n Q S RQ +=+是________触发器的特性方程,其约束条件为__________。

12、1n n n Q TQ TQ +=+是_____触发器的特征方程。

13、我们可以用JK 触发器转换成其他逻辑功能触发器,令__________________,即转换成T 触发器;令_______________,即转换为'T触发器;令________________,即转换成D触发器。

二、选择1、存储8位二进制信息要()个触发器。

A.2B.4C.8D.162、对于T触发器,若原态Qn=0,欲使新态Qn+1=1,应使输入T=()。

高等院校 数字逻辑 习题六

习题六6.1填空题1.时序电路在逻辑功能上的特点是,电路在任一时刻的输出状态不仅取决于该时刻的,而且与有关。

2.分析异步时序电路不同于同步时序电路,必须同时分析每个触发器的信号。

3.计数器按照计数脉冲输入方式分为计数器、计数器。

4.一个逻辑电路,如果某一给定时刻的输出不仅决定于该时刻的输入,而且还与该时刻前电路所处的状态有关,则此电路为电路。

5.一个逻辑电路,如果某一给定时刻的输出仅决定于该时刻的输入,而与该时刻前电路所处的状态无关,则此电路为电路。

6.型时序电路的输出不仅与电路的内部状态有关,而且与外输入有关。

型时序电路的输出仅与电路的内部状态有关,而与外输入无关。

7.用n级触发器构成的计数器,计数容量最多可为。

8.用来表示时序电路的状态转移规律及相应的输入、输出关系的图形称为。

9.计数器中有效状态的数目,称为计数器的。

10.用二进制异步计数器从0计数到十进制数186,则最少需要个触发器。

11.单向移位寄存器工作于串行输入/并行输出方式,可实现数据的变换。

12.具有8个和12个触发器的异步二进制计数器,它们分别各有和状态。

13.若最简状态表中的状态数为10,则所需的状态变量至少应为。

14.8位移位寄存器,串行输入时经个CP脉冲后,8位数码全部移入寄存器中。

若该寄存器已存满8位数码,欲将其并行输出,则需个CP脉冲后,数码能全部输出;欲将其串行输出,则需个CP脉冲后,数码能全部输出。

15.时序电路一般由和两部分组成。

16.按电路状态的改变方式,时序电路分为和两种;按输入与输出关系,时序电路分为和两种。

17.如果一个计数器能够从无效状态返回到有效状态,就称为该计数器有,否则称为。

6.2选择题1.四位二进制计数器的计数容量是()A、2B、4C、10D、162.能实现数据串行——并行和并行——串行转换的电路是()A、二进制译码器B、数据分配器C、移位寄存器D、编码器3.用n个触发器构成计数器,可得到的最大计数长度为()A、nB、2nC、n2D、2 n4.下列电路中()个不是时序电路。

第六章时序逻辑电路

CLK异0为步计计数数输器入与端、同Q步0为计输数出器端比,二,进具制有计如数下器 特点: CLK* 1电为计路数简输单入;端、Q3为输出端,五进制计数器 CLK* 1速与Q度0慢相连;、CLK0为输入端、Q3为输出端,十进制计数器

四、任意进制计数器的构成方法 设已知计数器的进制为N,要构成的任意进制计数

圆圈表示电路的各个状态,箭头表示状态表示的方向, 箭头旁注明转换前的输入变量取值和输出值

三、状态机流程图(SM图) 采用类似于编写计算机程序时使用的程序流程图的形

式,表示在一系列时钟脉冲作用下时序电路状态的流程以及 每个状态下的输入和输出。

四、时序图 在输入信号和时钟脉冲序列作用下,电路状态、

输出状态随时间变化的波形图。

电路在某一给定时刻的输出

取决于该时刻电路由的触输发入器保存 还取决于前一时刻电路的状态

时序电路: 组合电路 + 触发器

电路的状态与时间顺序有关

例:串行加法器电路

利用D触发器 把本位相加后 的进位结果保 存下来

时序电路在结构上的特点:

(1)包含组合电路和存储电路两个组成部分

(2)存储输出状态必须反馈到组合电路的输入端,与输入 信号共同决定组合逻辑电路的输出

串行进位方式以低位片的进位输出信号作为高位片的时 钟输入信号;

并行进位方式以低位片的进位输出信号作为高位片的 工作状态控制信号(计数的使能信号),两片的CLK同时接 计数输入信号。

二、异步计数器

B、减法计数器

二、异步计数器

B、减法计数器

根据T触发器的翻转规律即可画出在一系列CLK0脉冲信号 作用下输出的电压波形。

2、异步十进制计数器

J K端悬空相当于接逻辑1电平 将4位二进制计数器在计数过程中跳过从1010到1111这6个状态。

康华光《电子技术基础-数字部分》(第5版)笔记和课后习题(含考研真题)详解-时序逻辑电路【圣才出品】

号。同步时序电路的时钟脉冲 CP 或 CP 一般是不作为输入变量考虑的。

②找出所有可能的状态和状态转换之间的关系,则建立起原始状态图。 ③根据原始状态图建立原始状态表。 (2)状态化简 原始状态图或原始状态表很可能隐含多余的状态,去除多余状态的过程称为状态化简, 其目的是减少电路中触发器及门电路的数量,但不能改变原始状态图或原始状态表所表达的 逻辑功能。 状态化简建立在等价状态的基础上:如果两个状态作为现态,其任何相同输入所产生的 输出及建立的次态均完全相同,则这两个状态称为等价状态。凡是两个等价状态都可以合并 成一个状态而不改变输入-输出关系。 (3)状态分配 对每个状态指定一个特定的二进制代码,称为状态分配或状态编码。 ①要确定状态编码的位数。

3 / 61

圣才电子书 十万种考研考证电子书、题库视频学习平台

2.米利型和穆尔型时序电路 电路输出是输入变量及触发器状态的函数,这类时序电路称为米利型电路或米利型状态 机,它的一般化模型如图 6-2 所示。 电路输出仅仅取决于各触发器的状态,而不受电路当时的输入信号影响或没有输入变 量,这类电路称为穆尔型电路或穆尔型状态机,其模型如图 6-3 所示。

第六章 时序逻辑电路计数器

EP ET

CLK Q0 Q1 Q2

C LD LD R D RD Q3

(b)功能表

图6.3.9 4注:74161和74LS161只是内部电路结构有些区别。74LS163 也是4位二进制加法计数器,但清零方式是同步清零

01

01

0

6.3.2 计数器

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

Ti Qi 1Qi 2 ...Q0 T0 1

T 触发器

1.定义: 凡在时钟信号作用下,具有表5.6.3所示功能的触 发器称为T 触发器 表5.6.3

在数字电路中,凡在 CP 时钟脉冲 控制下,根据输入信号T取值的不 同,具有保持和翻转功能的电路 ,即当 T=0 时能保持状态不变 , T=1 时一定翻转的电路,都称为 T 触发器。 2.特性方程: 由特性表可得

(a)逻辑图形符号 (b)功能表 图6.3.12 同步十六进制可逆计数器74LS193的图形符号及功能表

6.3.2 计数器

2. 同步十进制计数器:

①加法计数器 基本原理:在四位二 进制计数器基础上修 改,当计到1001时, 则下一个CLK电路状 态回到0000。

T1 Q0 Q0Q3

6.3.2 计数器

K1 & T3 J Q3 6 7 8 9 10 11 0 0 0 0 1 0 0 0 0 0 1 1 0 0 0 1 0 1 0 1 3 2 1 0 9 0 0 0 1 0

C K1

6.3.2 计数器

其逻辑电路如图6.3.15所示

驱动方程:

T0 1 (Q3 Q2 Q1 ) T1 Q0 Q0 (Q1 Q2 Q3 ) T2 Q1 Q1 Q0 T3 Q2