VHDL语言按键去抖动电路的设计

基于VHDL的按键消抖程序设计

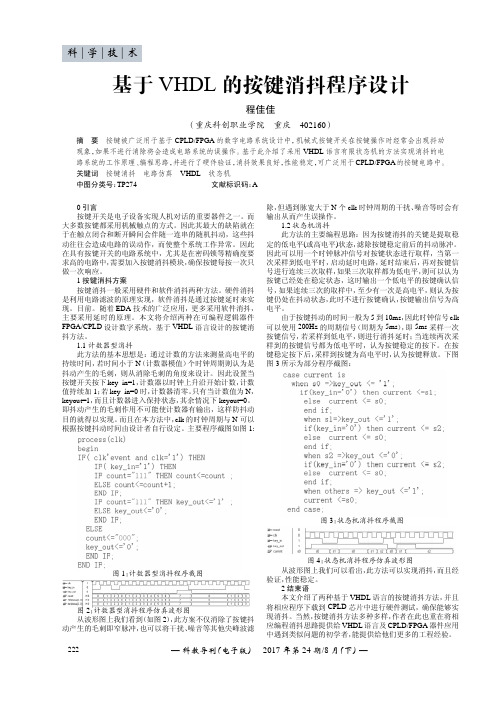

—科教导刊(电子版)·2017年第24期/8月(下)—222基于VHDL 的按键消抖程序设计程佳佳(重庆科创职业学院重庆402160)摘要按键被广泛用于基于CPLD/FPGA 的数字电路系统设计中,机械式按键开关在按键操作时经常会出现抖动现象,如果不进行消除将会造成电路系统的误操作。

基于此介绍了采用VHDL 语言有限状态机的方法实现消抖的电路系统的工作原理、编程思路,并进行了硬件验证,消抖效果良好,性能稳定,可广泛用于CPLD/FPGA 的按键电路中。

关键词按键消抖电路仿真VHDL 状态机中图分类号:TP274文献标识码:A 0引言按键开关是电子设备实现人机对话的重要器件之一。

而大多数按键都采用机械触点的方式。

因此其最大的缺陷就在于在触点闭合和断开瞬间会伴随一连串的随机抖动,这些抖动往往会造成电路的误动作,而使整个系统工作异常。

因此在具有按键开关的电路系统中,尤其是在密码锁等精确度要求高的电路中,需要加入按键消抖模块,确保按键每按一次只做一次响应。

1按键消抖方案按键消抖一般采用硬件和软件消抖两种方法。

硬件消抖是利用电路滤波的原理实现,软件消抖是通过按键延时来实现。

目前。

随着EDA 技术的广泛应用,更多采用软件消抖,主要采用延时的原理。

本文将介绍两种在可编程逻辑器件FPGA/CPLD 设计数字系统,基于VHDL 语言设计的按键消抖方法。

1.1计数器型消抖此方法的基本思想是:通过计数的方法来测量高电平的持续时间,若时间小于N (计数器模值)个时钟周期则认为是抖动产生的毛刺,则从消除毛刺的角度来设计。

因此设置当按键开关按下key_in=1,计数器以时钟上升沿开始计数,计数值持续加1;若key_in=0时,计数器清零。

只有当计数值为N ,keyout=1,而且计数器进入保持状态,其余情况下keyout=0。

即抖动产生的毛刺作用不可能使计数器有输出,这样防抖动目的就得以实现。

而且在本方法中,clk 的时钟周期与N 可以根据按键抖动时间由设计者自行设定。

消抖电路原理及实现

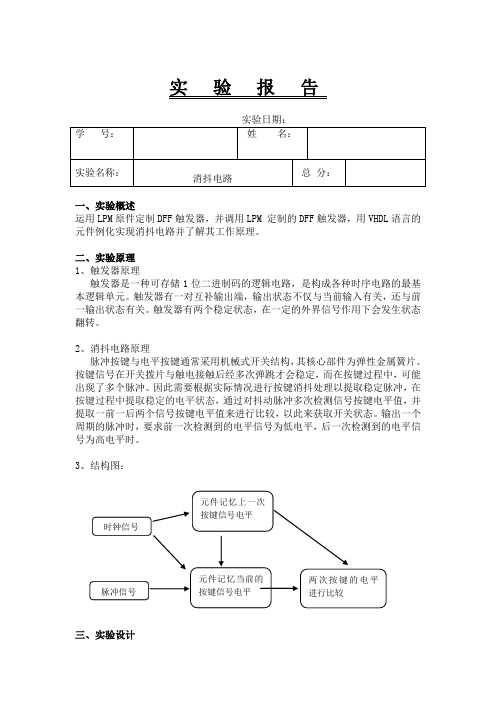

实 验 报 告实验日期: 学 号:姓 名:实验名称:消抖电路总 分:一、实验概述运用LPM 原件定制DFF 触发器,并调用LPM 定制的DFF 触发器,用VHDL 语言的元件例化实现消抖电路并了解其工作原理。

二、实验原理 1、触发器原理触发器是一种可存储1位二进制码的逻辑电路,是构成各种时序电路的最基本逻辑单元。

触发器有一对互补输出端,输出状态不仅与当前输入有关,还与前一输出状态有关。

触发器有两个稳定状态,在一定的外界信号作用下会发生状态翻转。

2、消抖电路原理脉冲按键与电平按键通常采用机械式开关结构,其核心部件为弹性金属簧片。

按键信号在开关拨片与触电接触后经多次弹跳才会稳定,而在按键过程中,可能出现了多个脉冲。

因此需要根据实际情况进行按键消抖处理以提取稳定脉冲,在按键过程中提取稳定的电平状态,通过对抖动脉冲多次检测信号按键电平值,并提取一前一后两个信号按键电平值来进行比较,以此来获取开关状态。

输出一个周期的脉冲时,要求前一次检测到的电平信号为低电平,后一次检测到的电平信号为高电平时。

3、结构图:三、实验设计时钟信号 元件记忆当前的按键信号电平 元件记忆上一次按键信号电平 两次按键的电平进行比较 脉冲信号1、LPM元件定制DFF触发器(1)设置lpm_ff元件选择Installed Plug-Ins→Storage→lpm_ff项。

(2)LPM元件定制步骤,设置输入data为1位,clock为时钟信号,类型为D 型。

(3)添加异步清零和异步置1。

(4)aclr异步清零且高电平有效,aset异步置1且高电平有效,二者无效时,q输出由clock上升沿触发更新为data。

(5)调出其vhd文件添加至消抖电路的工程中。

(6)仿真验证并下载。

功能仿真波形分析参数:end time 为2.0ns,grid size为100ns;信号:alcr 异步清零且高电平有效,二进制;aset异步置1且高电平有效,二进制;二者无效,q(二进制)输出由clock(二进制)上升沿触发更新为data(二进制)。

(整理)VHDL键盘去抖动计数器.

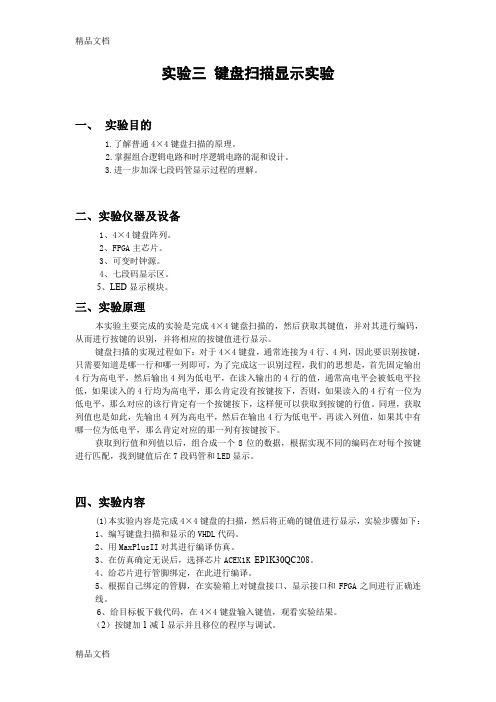

实验三键盘扫描显示实验一、实验目的1.了解普通4×4键盘扫描的原理。

2.掌握组合逻辑电路和时序逻辑电路的混和设计。

3.进一步加深七段码管显示过程的理解。

二、实验仪器及设备1、4×4键盘阵列。

2、FPGA主芯片。

3、可变时钟源。

4、七段码显示区。

5、LED显示模块。

三、实验原理本实验主要完成的实验是完成4×4键盘扫描的,然后获取其键值,并对其进行编码,从而进行按键的识别,并将相应的按键值进行显示。

键盘扫描的实现过程如下:对于4×4键盘,通常连接为4行、4列,因此要识别按键,只需要知道是哪一行和哪一列即可,为了完成这一识别过程,我们的思想是,首先固定输出4行为高电平,然后输出4列为低电平,在读入输出的4行的值,通常高电平会被低电平拉低,如果读入的4行均为高电平,那么肯定没有按键按下,否则,如果读入的4行有一位为低电平,那么对应的该行肯定有一个按键按下,这样便可以获取到按键的行值。

同理,获取列值也是如此,先输出4列为高电平,然后在输出4行为低电平,再读入列值,如果其中有哪一位为低电平,那么肯定对应的那一列有按键按下。

获取到行值和列值以后,组合成一个8位的数据,根据实现不同的编码在对每个按键进行匹配,找到键值后在7段码管和LED显示。

四、实验内容(1)本实验内容是完成4×4键盘的扫描,然后将正确的键值进行显示,实验步骤如下:1、编写键盘扫描和显示的VHDL代码。

2、用MaxPlusII对其进行编译仿真。

3、在仿真确定无误后,选择芯片ACEX1K EP1K30QC208。

4、给芯片进行管脚绑定,在此进行编译。

5、根据自己绑定的管脚,在实验箱上对键盘接口、显示接口和FPGA之间进行正确连线。

6、给目标板下载代码,在4×4键盘输入键值,观看实验结果。

(2)按键加1减1显示并且移位的程序与调试。

五、实验数据记录与分析1、4×4键盘的扫描VHDL代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity scanf isport( clk : in std_logic;-------------扫描时钟信号start : in std_logic;-------------开始信号,高电平有效kbcol : in std_logic_vector(3 downto 0);--------------行扫描信号kbrow : out std_logic_vector(3 downto 0);-------------列扫描信号seg7_out : out std_logic_vector(6 downto 0);-------------七段显示控制信号(abcdefg) scan : out std_logic_vector(2 downto 0));-------------数码管地址选择控制信号end scanf;architecture one of scanf issignal count : std_logic_vector(1 downto 0);signal sta : std_logic_vector(1 downto 0);signal seg7 : std_logic_vector(6 downto 0);signal dat : std_logic_vector(4 downto 0);signal fn : std_logic;------------------按键标志位,判断是否有键被按下beginscan<="000";---------------只使用一个数码管显示---------------------循环扫描计数器process(clk)beginif clk'event and clk='1' then count<=count+1;end if;end process;---------------------循环列扫描process(clk)beginif clk'event and clk='1' thencase count iswhen "00"=>kbrow<="0001";sta<="00";when "01"=>kbrow<="0010";sta<="01";when "10"=>kbrow<="0100";sta<="10";when "11"=>kbrow<="1000";sta<="11";when others=>kbrow<="1111";end case;end if;end process;---------------------行扫描译码process(clk,start)if start='0' then seg7<="0000000";elsif clk'event and clk='1' thencase sta iswhen "00"=>case kbcol iswhen "0001"=>seg7<="1111001";dat<="00011";-----3 when "0010"=>seg7<="1101101";dat<="00010";-----2when "0100"=>seg7<="0110000";dat<="00001";-----1when "1000"=>seg7<="1111110";dat<="00000";-----0when others=>seg7<="0000000";dat<="11111";end case;when "01"=>case kbcol iswhen "0001"=>seg7<="1110000";dat<="00111";-----7 when "0010"=>seg7<="1011111";dat<="00110";-----6when "0100"=>seg7<="1011011";dat<="00101";-----5when "1000"=>seg7<="0110011";dat<="00100";-----4when others=>seg7<="0000000";dat<="11111";end case;when "10"=>case kbcol iswhen "0001"=>seg7<="0011111";dat<="01011";-----b when "0010"=>seg7<="1110111";dat<="01010";-----awhen "0100"=>seg7<="1111011";dat<="01001";-----9when "1000"=>seg7<="1111111";dat<="01000";-----8when others=>seg7<="0000000";dat<="11111";end case;when "11"=>case kbcol iswhen "0001"=>seg7<="1000111";dat<="01111";-----f when "0010"=>seg7<="1001111";dat<="01110";-----ewhen "0100"=>seg7<="0111101";dat<="01101";-----dwhen "1000"=>seg7<="1001110";dat<="01100";-----cwhen others=>seg7<="0000000";dat<="11111";end case;when others=>seg7<="0000000";end case;end if;end process;fn<=not(dat(0)and dat(1)and dat(2)and dat(3)and dat(4));-------------------产生按键标志位,用于存储按键信息process(fn)if fn'event and fn='1' then------------按键信息存储seg7_out<=seg7;end if;end process;end one;从实验的结果可以看出,当使能端处于高电平即有效电平时,把时钟输出按键打开,此时按。

按键去抖动程序

按键去抖动一、实验目的1、学习基于VHDL 描述状态机的方法;2、学习 VHDL 语言的规范化编程,学习按键去抖动的原理方法。

二、实验平台微机一台(Windows XP 系统、安装QuartusⅡ等相关软件)、CPLD 学习板一块、5V 电源线一个、下载线一条。

三、设计要求机械式轻触按键是常用的一种外围器件,由于机械原因导致的抖动会使得按键输入出现毛刺。

设计一个按键去抖动电路,并用按键作为时钟,结合计数器观察去抖动前后的效果有什么不同。

四设计方案思路提示:按键去抖动通常采用延时判断的方法,去除按键过程中出现的毛刺。

其实现过程是:当查询到按键按下时,延时一段时间再去判断按键是否仍然被按下,若是则此次按键有效,否则看作是干扰。

这可以利用状态机来实现,library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity qudou isport(clk, en: in std_logic;sp: out integer range 0 to 7);end qudou ;architecture behave of qudou istype state is (S0,s1,s2);signal z: std_logic;signal q: integer range 0 to 2; signal a: integer range 0 to 7; signal s: state;beginp1:process(clk)beginif(clk'event and clk = '1') thenif en='1' thenif q=2 thenq<=q;else q<=q+1;end if;else q<=0;end if;if q=2 thenz<='1';else z<='0';end if;case s iswhen s0=>if (z = '0') thens<=s0;a<=a;elses<=s1;a<=a+1;end if;when s1=>if (z='0') thens<=s0;a<=a;elses<=s2;a<=a;end if;when s2=>if (z='0') thens<=s0;a<=a;elses<=s2;a<=a;end if;end case;sp<=a;end if;end process p1;end behave;五.实验结果:。

按键消抖的原理和基于verilog的消抖设计

按键消抖的原理和基于verilog的消抖设计按键开关是各种电子设备不可或缺的人机接口。

在实际应用中,很大一部分的按键是机械按键。

在机械按键的触点闭合和断开时,都会产生抖动,为了保证系统能正确识别按键的开关,就必须对按键的抖动进行处理。

在系统设计中,有各种各样的消除按键抖动的设计方法,硬件电路和软件设计都很成熟。

不过我们这里要从另外一个角度来讨论按键的消抖,并给出一个用verilog给出一个具体的实现。

首先,看一个普通的机械按键的触点在闭合与断开时的波形(用示波器抓取)。

下面的四张图都是按键在闭合的时候抓到的波形。

可以看到两个明显的趋势:1. 按键在几个us之内就可以达到稳定状态,从高电平转换到底电平;2. 在高电平转换到低电平的过程中,触点有非常明显的抖动。

下面的两张图是按键在断开的时候抓到的波形。

也可以看到两个明显的趋势:1. 按键的变化趋势比较缓慢,从低电平变为高电平需要大概10~20ms的时间;2. 按键断开时没有闭合时那么大的抖动下面两张图是用手迅速闭合按键然后就断开时,按键的输出波形。

在处理按键抖动的程序中,必须同时考虑消除闭合和断开两种情况下的抖动。

所以,对于按键消抖的处理,必须按最差的情况来考虑。

我们从上面的图上可以看到,按键输出的信号的跳变时间(上升沿和下降沿)最大是在20ms左右。

按键一次闭合最短的时间大概是120ms 左右。

如果我们把按键的输出做为一个时钟域(时钟频率未知,但信号的slow rate是已知的,既最大20ms左右)的信号,用另外一个时钟来采集这个按键的输出,则就可以把按键的消抖归结为一个最基本的CDC问题来处理。

而问题的核心是如何确定采集时钟的频率。

假设采集时钟的周期小于20ms,那么,采集时钟就有可能两次采到按键断开时的不。

基于VHDL的开关消抖电路的研究

V D n sn sl r vn T ec ci pr r ne bu t cue nine ee c ,sq et oprt n t a a H La dt t gr ut a e i e s e ̄ e. h i ut e omacsaot r t ,at i r rn e e uni coeai ,e . r a - r f su r ・ tf M o c en l e n i usd T epo oe i u shv ihpat ait a dcneunl a nihe tdns ncru ei . y dadds se . h rp sdc ci aehg rc cb i n osq et cnel t s et o i id s n z c r t i ly y g n u ct g

ie  ̄ et n l hn / 检测 时钟到 f l vn adc k k=1 te /

t l mp <:k / 当前 时刻的开关值 存入 t p ; / m l中

t 2<=t l / 前 一个 时刻 的开关值移入 tp mp mp ; / m 2中

收 稿 日期 :2 0 O 2 0 9~ 9— 5

此 ,在 开关 信 号送 人 此类 电路前 ,必 须对 其进 行 预

处理 ,以消 除 开 关 的 抖 动 。 本 文 归 纳 了 3种 基 于

V L( HSC H rw r D sr t nL n ag ) 实 HD V I ad ae eci i a ga e 的 po

时钟 ; 为消抖后 的输 出信号。在 c Y l k上升沿时刻 检 测 ,若连 续 检测 到 2个 输 入 高 电平 ( 次 寄 存 在 依 te2 m p m p 、t e l中 ) 才 可 认 为 开 关 稳 定 闭合 。J 时 , Y输 出高 电平 ;只 要检 测 到 低 电平 ,即认 为 开 关 断

基于VHDL语言的几种消抖电路的设计

图1是N为3的波形仿真图,当按键持续时间大于3个时钟周期,计数器输出一个单脉冲,其宽度为1个时钟周期,小于3个时钟周期的窄脉冲用作模拟抖动干扰,从图1可以看出,抖动不能干扰正常的单脉冲输出。

该方案的特点是能很好消除按键抖动产生的窄脉冲,还可以滤去干扰、噪音等其他尖峰波,但遇到脉宽大于N个Tclk时钟周期的干扰、噪音等时会有输出从而产生误操作,而对于按键操作要求按键时间必须大于N个Tclk时钟周期,否则按键操作也没有输出。

1.2计数器型消抖电路(二)计数器型消抖电路(二)是控制计数器工作一个循环周期(N+1个状态),且仅在计数器为0时输出为“1”。

电路设计了连锁控制设施。

在计数器处于状态0时,此时若有按键操作,则计数器进入状态1,同时输出单脉冲(其宽度等于时钟周期)。

计数器处于其他状态,都没有单脉冲输出。

计数器处于状态N时,控制en='0',导致计数器退出状态N,进入状态0。

计数器能否保持状态0,取决于人工按键操作,若按键key_in='1',控制en='1'(计数器能正常工作),key_in='0',计数器状态保持。

显见计数器处于状态0,人工不按键,则计数器保持状态0。

图2是N为7的波形仿真图。

在计数器状态为0时,key_in有按键操作,计数器开始连续计数直到计数器状态为0;计数器状态为1-7时,key_in任何操作对计数器工作无影响,计数器在状态为1时,输出一个单脉冲,脉冲宽度为1个时钟周期。

该设计方案的特点是能很好消除按键抖动产生的连续脉冲,对按键时间没有要求,缺点是在计数器状态为0时,遇到干扰、噪音等时会有输出,从而产生误操作。

2D触发器型消抖电路D触发器型消抖电路设计了三个D触发器与一个三输入与门。

三个D触发器串行连接,其Q输出端分别与三输入与门的输入端连接,D触发器型消抖电路RTL电路如图3所示。

图4为D触发器型消抖电路波形仿真图,由图可见,当按键操作时间大于或等于clk 时钟周期的3倍时,输出一个正脉冲,正脉冲的宽度比key_in少2个clk时钟周期。

VHDL――按键消抖

VHDL——按键消抖按键检测需要消抖,一般有硬件和软件两种方式。

硬件就是加去抖动电路,这样从根本上解决按键抖动问题。

除了用专用电路以外,用可编程FPGA或者CPLD设计相应的逻辑和时序电路,对按键信号进行处理,同样可以达到去抖动的目的。

本例中用状态机实现了消抖电路:端口描述:clk输入检测时钟;reset复位信号;din原始按键信号输入;dout去抖动输出信号。

VHDL源码如下:LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_unsigned.all;ENTITY xiaod ISPORT(clk:IN STD_LOGIC ;reset:IN STD_LOGIC ;din:IN STD_LOGIC ;dout:OUT STD_LOGIC);END ENTITY; ARCHITECTURE RTL OF xiaod IS TYPE state IS( s0,s1,s2,s3); SIGNAL pre_s, next_s:state;BEGINP0:PROCESS( reset, clk ) BEGINif reset = '0' thenpre_s <= s0;elsif rising_edge( clk ) thenpre_s <= next_s;elsenull;end if;END PROCESS P0;P1:PROCESS( pre_s, next_s, din ) BEGINcase pre_s isdout <= '1';if din = '1' then next_s <= s0; elsenext_s <= s1; end if;when s1 => dout <= '1';if din = '1' then next_s <= s0; elsenext_s <= s2; end if;when s2 => dout <= '1';if din = '1' then next_s <= s0; elsenext_s <= s3; end if;dout <= '0';if din = '1' thennext_s <= s0;elsenext_s <= s1;end if;end case;END PROCESS P1;END RTL;多按键去抖动电路VHDL源码,按键个数参数化,每个按键处理调用了上面的模块:LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_arith.all;USE ieee.std_logic_unsigned.all;ENTITY Nxiaod ISGENERIC( width:positive:= 5 );PORT(clk:IN STD_LOGIC ;reset:IN STD_LOGIC ;din:IN STD_LOGIC_VECTOR( width - 1 DOWNTO 0); dout:OUT STD_LOGIC_VECTOR( width - 1 DOWNTO 0) );END ENTITY;ARCHITECTURE RTL OF Nxiaod IS COMPONENT xiaod ISPORT(clk:IN STD_LOGIC ;reset:IN STD_LOGIC ;din:IN STD_LOGIC ;dout:OUT STD_LOGIC);END COMPONENT;BEGINg1: FOR i IN 0 to width - 1 GENERATEux:xiaod port map( clk => clk, reset => reset, din => din(i), dout =>dout(i)); END GENERATE;END RTL;。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

--状态机复位,dout输出信 状态机复位, 状态机复位 输出信 号复位。 号复位。

--按键按下 按键按下

--按键按下 按键按下

--按键释放 按键释放

仿真结果

S0

S1

S0

S0

S1

S2

S2

S0

维持3个周期的低电平时 变成低电平, 当din维持 个周期的低电平时,dout变成低电平,表示有 维持 个周期的低电平时, 变成低电平 按键按下。 按键按下。

c lk res et key 1 key 2 key 3 key 4

ins t

led1 led2 led3 led4

clk:时钟,50MHz; :时钟, ; reset:复位信号; :复位信号; key1, key2, key3, key4:按键信号 : 输入; 输入; 输出信号: 输出信号: led1, led2, led3, led4:发光二极管 : 信号输出。 信号输出。

--key2按下 按下

--key3按下 按下

--key4按下 按下

--没有键被按下 没有键被按下

仿真结果

clk reset key 3

INPUT VCC

dout

din inst9 debounce clk reset dout

该设计包含分频模块、 该设计包含分频模块、去抖 动模块和按键扫描模块组成。 动模块和按键扫描模块组成。

key 4

INPUT VCC

din inst10

按键扫描程序

--key1按下 按下

50MHz

clk

INPUT VCC

Parameter Value Type n 250000 Signed Integer

f div 200hz clkin clkout

Parameter Value Type n 5000000 Signed Integer

f div 10hz clkin clkout

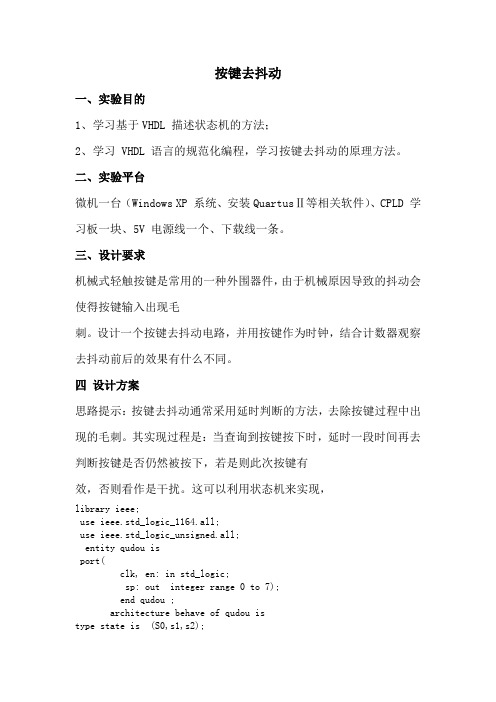

去抖动电路设计原理

设计原理: 滤除前沿和后延抖动毛刺,提取稳定的按键信息。 设计方法: 对一个按键信号,对它进行取样,如果连续两次 取样都为低电平,则认为信号已经处于稳定状态, 这时输出一个低电平的按键信号。否则只要有一 次取样不为低电平,则认为是抖动,将其丢弃。

设计方法

可以用一个状态机来设计这个去抖电路。

led1 led2 led3 led4

dout

key 1 key 2 key 3 key 4

reset din inst7 debounce clk reset dout

去

inst3

抖 动 电 路 按键扫描 电路

key 2

INPUT VCC

din inst8 debounce

如图所示,为顶层原理图。 如图所示,为顶层原理图。

去抖动电路的应用

设计要求: 设计一个4路独立键盘输入电路,读取键盘 的键值并通过发光二极管显示出来。 输入为时钟信号CLK(50MHz),按键状 态KEY1,KEY2,KEY3,KEY4。 输出为D1,D2,D3,D4。根据按键的状 态控制发光二极d

输入信号: 输入信号:

分频器1 分频器

(200hz,5ms) , )

inst inst1

分频器2 分频器

(10hz,100ms) , )

ctrl

debounce clk10hz clk reset key 1

INPUT VCC INPUT VCC

led1 led2 led3 led4

OUTPUT OUTPUT OUTPUT OUTPUT

x/y:表示输入和输出。‘/’左侧的为输入信号,‘/’右侧的为输出 信号。 当按键按下时,为低电平。按键松开后为高电平。

去抖动电路模块

debounce

输入信号: 输入信号:

clk reset din inst dout

clk:时钟; :时钟; reset:复位信号; :复位信号; din:按键信号输入; :按键信号输入; 输出信号: 输出信号: dout:按键去抖动信号输出。 :按键去抖动信号输出。

注:由于按键抖动的时间一般为5到10ms,因此输入时钟 clk使用200Hz时钟脉冲(周期为5ms),即5ms采样一次按 键信号,当连续两次采样到的按键信号都为低电平时,认 为按键稳定的按下。在按键稳定按下后,采样到按键为高 电平时,认为按键释放。

去抖动电路VHDL程序

--200HZ时钟 时钟

--定义状态机类型 定义状态机类型state 定义状态机类型

专题二. 经典模块设计

——按键去抖动电路设 计

按键电平抖动

通常使用的按键都是机械弹性开关,按下时闭合, 通常使用的按键都是机械弹性开关,按下时闭合, 松开后自动断开。 松开后自动断开。 在键盘操作时, 在键盘操作时,在触点闭合和开启的瞬间会出现 电压抖动,如图所示。 电压抖动,如图所示。为了保证按键识别的准确 必须进行去抖动处理,消除抖动部分的信号。 性,必须进行去抖动处理,消除抖动部分的信号。