余三码计数器

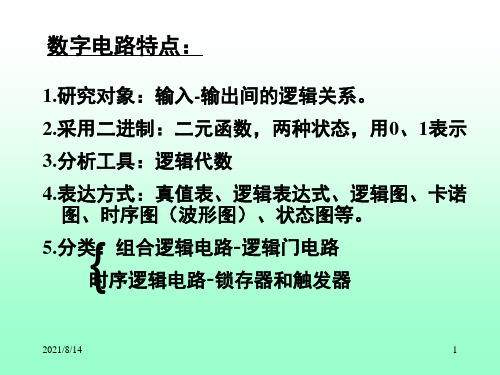

数字集成电路考试 知识点

数字集成电路考试知识点一、数字逻辑基础。

1. 数制与编码。

- 二进制、十进制、十六进制的相互转换。

例如,将十进制数转换为二进制数可以使用除2取余法;将二进制数转换为十六进制数,可以每4位二进制数转换为1位十六进制数。

- 常用编码,如BCD码(8421码、余3码等)。

BCD码是用4位二进制数来表示1位十进制数,8421码是一种有权码,各位的权值分别为8、4、2、1。

2. 逻辑代数基础。

- 基本逻辑运算(与、或、非)及其符号表示、真值表和逻辑表达式。

例如,与运算只有当所有输入为1时,输出才为1;或运算只要有一个输入为1,输出就为1;非运算则是输入和输出相反。

- 复合逻辑运算(与非、或非、异或、同或)。

异或运算的特点是当两个输入不同时输出为1,相同时输出为0;同或则相反。

- 逻辑代数的基本定理和规则,如代入规则、反演规则、对偶规则。

利用这些规则可以对逻辑表达式进行化简和变换。

- 逻辑函数的化简,包括公式化简法和卡诺图化简法。

卡诺图化简法是将逻辑函数以最小项的形式表示在卡诺图上,通过合并相邻的最小项来化简逻辑函数。

二、门电路。

1. 基本门电路。

- 与门、或门、非门的电路结构(以CMOS和TTL电路为例)、电气特性(如输入输出电平、噪声容限等)。

CMOS门电路具有功耗低、集成度高的优点;TTL门电路速度较快。

- 门电路的传输延迟时间,它反映了门电路的工作速度,从输入信号变化到输出信号稳定所需要的时间。

2. 复合门电路。

- 与非门、或非门、异或门等复合门电路的逻辑功能和实现方式。

这些复合门电路可以由基本门电路组合而成,也有专门的集成电路芯片实现其功能。

三、组合逻辑电路。

1. 组合逻辑电路的分析与设计。

- 组合逻辑电路的分析方法:根据给定的逻辑电路写出逻辑表达式,化简表达式,列出真值表,分析逻辑功能。

- 组合逻辑电路的设计方法:根据逻辑功能要求列出真值表,写出逻辑表达式,化简表达式,画出逻辑电路图。

2. 常用组合逻辑电路。

模拟信号与数字信号知识介绍

模拟信号

3V

模数转换器 0 000 001 1 数字输出

10

20

30

40

50

60

70

80

90

100

t/ms

0000 0100 0000 0011 0000 0010

1.1.4.数字信号的描述方法

1. 二值数字逻辑及其表示 二值数字逻辑 在数字电路中, 0、1组成二进制数可以表示数量大小,也 可以表示两种对立的逻辑状态。 0、1表示的两种对立逻辑状态的逻辑关系----二值数字逻辑 表示方式 (1) 在电路中用低、高电平表示0、1两种逻辑状态

常用方法是“按权相加”。 二、十进制数转换成二进制数: 小数部分 1. 整数部分用“辗转相除” 法: 将十进制数连续不断地除以2 , 直至商为零, 所得余数由低位到高位排列,即为所求二进制数 2 .小数部分用“辗转相乘”法:

整数部分

例如: (11)10==( ? )2

2 2 2 2 11 5 2 1 0

二、一般表达式:

系数

( N )10

i

K 10 ,

i i

位权

K i [0 9]

在数字电路中,计数的基本思想是要把电路的状 态与数码一一对应起来。显然,采用十进制是十分不 方便的。它需要十种电路状态与之对应。要想严格区 分这十种状态是很困难的。

1.2. 2

一、特点

二进制

六、优点 :

十六进制在数字电路中,尤其在计算机中得到广泛的应用, 因为:

第一、与二进制之间的转换容易

第二、计数容量较其它进制都大。假如同样采用四位数码, 二进制最多可计至 1111

B

= 15

《数字电路与逻辑设计》综合练习题及解答

《数字电路与逻辑设计》综合练习题及解答第一部分习题一、填空1.将十进制数转换成等值的二进制数、十六进制数。

10 = 2= 162.10= 余3BCD= 8421BCD 3.16= 24.一位二进制数只有2个数,四位二进制数有个数;为计64个数,需要位二进制数。

5.二进制数2的等值八进制数是8。

6.二进制数2的等值十进制数是10。

7.欲对100个对象进行二进制编码,则至少需要位二进制数。

8.二进制数为000000~111111能代表个十进制整数。

9.为将信息码10110010配成奇校验码,其配奇位的逻辑值为;为将信息码01101101配成偶校验码,其配偶位的逻辑值为。

10.格雷码的特点是。

11.n变量函数的每一个最小项有个相领项。

12.当ij时,同一逻辑函数的两个最小项mimj=。

2n113.n变量的逻辑函数,mi为最小项,则有mi=。

i014.逻辑函数FABCD的反函数F=。

15.逻辑函数FA(BC)的对偶函数F是。

16.多变量同或运算时,=0,则xi=0的个数必须为。

17.逻辑函数F(A,B,C)1C18. 逻辑函数F(A,B,C,D)( )。

19.逻辑函数F(A,B,C)(ABC)(ABC)的最简与或式为。

20.巳知函数的对偶式F(A,B,C,D)ABCDBC,则它的原函数F =。

* * * * * 21.正逻辑约定是、。

22.双极型三极管截止状态过渡到饱和状态所需的过渡时间称为时间,它时间和时间两部分组成,可用等式描述。

23.双极型三极管饱和状态过渡到截止状态所需的过渡时间称为时间,它时间和时间两部分组成,可用等式描述。

1。

AB的最小项表达式为F(A,B,C)=m(1,2,3,4,8,10)(0,12,14)的最简与或式为F=24.三极管反相器带灌电流负载时,负载电流的方向是从,此时反相器输出电平。

25.三极管反相器带拉电流负载时,负载电流的方向是从,此时反相器输出电平。

26.输入端的噪声容限说明。

《数字电路制作与测试》习题册(三)

《数字电路制作与测试》习题册(三)项⽬三计数器的设计与调试主要知识点:⼀、填空题1. 时序逻辑电路的输出不仅与有关,⽽且与有关。

2. 时序逻辑电路中的存储电路通常有两种形式:和。

3. 是构成时序逻辑电路中存储电路的主要元件。

4. 锁存器和触发器是构成时序逻辑电路中的主要元件。

5. 按逻辑功能分,触发器有、、、触发器等⼏种。

6. 触发器按照逻辑功能来分⼤致可分为种。

7. 触发器是构成逻辑电路的重要部分。

8. 触发器有两个互补的输出端Q 、Q ,定义触发器的0状态为,1状态为,可见触发器的状态指的是端的状态。

9. 触发器的两个输出端Q 、Q ,当0,1Q Q ==时,我们称触发器处于。

10. 触发器的状态指的是的状态,当1,0Q Q ==时,触发器处于。

11. 触发器有2个稳态,存储4位⼆进制信息要个触发器。

12. 因为触发器有个稳态,6个触发器最多能存储⼆进制信息。

13. ⼀个有与⾮门构成的基本RS 触发器,其约束条件是。

14. ⼀个基本R S 触发器在正常⼯作时,它的约束条件是R +S =1,则它不允许输⼊S = 且R = 的信号。

15. 与⾮门构成的基本RS 锁存器输⼊状态不允许同时出现R = S = 。

16. 与⾮门构成的基本RS 锁存器的特征⽅程是,约束条件是。

17. 由与⾮门构成的基本RS 锁存器其逻辑功能有种。

18. 由与⾮门构成的基本RS 锁存器正常⼯作时有三种状态,分别是01R S =输出为,10R S = 输出为,11R S =输出为。

(0状态/1状态/保持状态)。

19. 与⾮门构成的基本RS 锁存器当Q=1时,R = ,S = 。

20. 与⾮门构成的基本RS 锁存器当Q=0时,R = ,S = 。

21. 锁存器和触发器的区别在于其输出状态的变化是否取决于。

22. 触发器的输出状态变化除了由输⼊信号决定外还取决于。

23. 和共同决定了触发器输出状态的变化。

24. 钟控RS 触发器的约束条件是。

数字逻辑课程三套作业及答案资料

数字逻辑课程作业A、单选题。

1.(4 分)如图xl-229某一译码器的输出端共有臼种不的组颌U其输入端備几个输入线? (A)3;(B J4;(0)5; 1D16A.(A)B.(B)C.(C)D.(D)知识点:第五章解析第五章译码器2.(4 分)如图xl-82F图所示河一逻辑电路,八"是输入端,F是输出端,则其输出与输入关系式是,{AiiA+B}iC+ DiE; .B^A+B+C+p-FE); iC) (A +云)QO+童);(D)AB[CD+Ei(C )A.(A)B.(B)C.(C)D.(D)知识点:第二章解析第二章其他复合逻辑运算及描述3.(4分)N个触发器可以构成最大计数长度(进制数)为(A.NB.2NC.N2次方D.2N次方知识点:第九章解析第九章计数器4.(4分)n个触发器构成的扭环型计数器中,无效状态有(B. B.2nC.C. 2n —1D. D . 2n-2n知识点:第九章解析第九章集成计数器5.(4 分)如图X1-293D )的计数器。

D )个。

在数字系统中其信号系仅貝E与即高电位与低电位两种: 迢】依电压犬小不等而定;依电流大小不等而定;①〕看需要而定A.(A)B.(B)C.(C)D.(D)知识点:第十一章解析第十一章数字系统概述6.(4 分)如图X1-317和项#只式的基本架构矢何?| A A'A ND—MAXD • IB i A XD—OR;(Q AND ―A.(A)B.(B)C.(C)D.(D)知识点:第二章解析第二章其他复合逻辑运算及描述7.(4 分)EPROM 是指( C )A.A、随机读写存储器B. B、只读存储器C.C、光可擦除电可编程只读存储器R? (DiO罠一AND(D )D.D、电可擦可编程只读存储器知识点:第十章解析第十章只读存储器8.(4 分)如图xl-407属于近似的不连续表示法丸?〔A]模拟表示法;|空数字表示法;1匚凰寸数表示法;|=>线性系统)°A.(A)B.(B)C.(C)D.(D)知识点:第十一章解析第十一章数字系统概述9.(4分)为实现将JK触发器转换为D触发器,应使( A )A.J=D,K=D 非B. B. K=D,J=D 非C. C.J=K=DD. D.J=K=D 非知识点:第六章解析第六章各种触发器的比较10.(4分)一位8421BCD码计数器至少需要(B )个触发器。

数字电路-复习大纲(四川大学)

包含2n个方格:2、4、8

包围的方格为矩形块

包围圈越大越好,越少越好

方格可以被重复包围,但每个包围圈内必需有新的方格

所有的1都要被包围住

充分考虑随意项

3.合并后的最小项之和即为最简与或表达式。 P37 习题1.2.2 1.4.2 1.6.1

2021/P8/1644 习题2.1.4 2.2.3 2.2.4

2一021位/8/1的4 权数(位权)是 Ri 。

3

②数制间的转换

二进制与十六进制数、八进制数之间的转换

24=16,四位二进制数对应一位十六进制数。 23=8, 三位二进制数对应一位八进制数。 举例:

3AF.2H = 0011 1010 1111.0010 = 1110101111.001B 3 A F2

2021/8/14

15

LA B A B A B

A

=1

L

B

用与非门实现

A& B

A& B

≥1

L

L A B A B A B A B A B • A B

2021/8/14

A& B

A& B

&

L

16

无反变量输入

LABA B A B A B A A B B

A A B B A B

1.变量值只有0和1,且只表示两种对立的逻辑状态,不表示 数量的大小。

2.表达方式:真值表--将输入变量的各种可能取值和相应函数

值排列在一起而组成的表格。

逻辑符号--规定的图形符号。

逻辑函数表达式--L=f(A、B…)

语句表、梯形图等。

2021/8/14

9

3.逻辑变量有原变量和反变量两类,普通代数中没有反变量。

8421BCD码格雷码余3码编码方法

8421BCD码格雷码余3码编码方法编码是信息处理领域中常见的一种技术,用于将数据转换为特定的编码形式,以便在传输或存储过程中更加高效地使用和处理数据。

在计算机科学和电子通信中,8521BCD码、格雷码和余3码是常用的编码方法之一、下面将详细介绍这三种编码方法。

1.8421BCD码:8421BCD码即二进制码-十进制码。

它使用4位二进制码(对应16进制的0-F)来表示一个十进制数。

8421BCD码的特点是具有固定的位权和容易进行十进制和二进制之间的转换。

其中,每一位的位权从右往左依次为8、4、2、1、例如,十进制数7的8421BCD码表示为01118421BCD码虽然具有固定的位权,但存在编码浪费问题。

由于每一位只能表示4位二进制数,因此在表示一个十进制数时需要使用更多的二进制位数。

例如,十进制数15的8421BCD码表示为00010101,占用了8位二进制数,而十进制数15在二进制中可以用4位数表示(即1111)。

因此,8421BCD码的编码效率较低。

2.格雷码:格雷码又称为反射码,它是一种二进制码的变形,相邻的两个码之间只有一个位数的差异。

格雷码的特点是编码过程中只有一位发生改变,这样在传输或存储过程中更加高效,避免了传统二进制码由于1位变化导致的多位错误。

例如,对于3位格雷码来说,它由000、001、011、010、110、111、101、100这样的序列组成。

格雷码在数字电路设计、数据通信和精确测量等领域具有广泛的应用。

例如,在数字电路设计中,格雷码可以用作计数器的输入,以避免计数器在计数过程中产生不稳定的状态。

3.余3码:余3码是一种类似于格雷码的编码形式,它的特点是相邻的两个码之间只有一位数的差异,并且不能存在三个连续的1或0。

余3码的编码过程通常使用状态转换表来确定。

例如,对于3位余3码来说,它由000、001、010、012、021、022、122、120、110、111、101、100这样的序列组成。

“编码与译码”三级工程项目体系的设计研究

“编码与译码”三级工程项目体系的设计研究作者:樊敏赵灿杨金汪海波鲁世斌来源:《电脑知识与技术》2024年第05期摘要:数字技术基础课程是大电类必修的专业基础课程,编码器与译码器是其中重要的教学内容。

传统的教学方案存在着知识点碎片化、理论与实践分离等问题,文章将编码器与译码器这两部分教学内容进行了融合,用“小-中-大”三级工程训练项目重构教学内容,由浅入深地培养学生形成“知识点-知识链-复杂系统”的工程思维模式,并通过对项目设计方案的不断改进、逐级优化,“螺旋递进”地培养学生解决复杂工程问题的能力,从而实现学以致用、知行合一的教学目标,提高教学效果与人才培养质量。

关键词:三级工程项目训练体系;编码器;译码器;Multisim;数字电路教学中图分类号:TP311 文献标识码:A文章编号:1009-3044(2024)05-0131-040 引言数字电子技术基础课程(以下简称“数电”)是大电类专业必修的专业基础课程,在专业培养课程体系中承上启下、举足轻重[1]。

然而,在传统的教学模式中,每门课都是一个独立的体系,强调的是知识体系的完备性,其中译码器与编码器是非常重要的教学内容[2]。

根据传统的教学方案,“编码器”讲授优先编码器74LS148的管脚功能和扩展[3]。

“译码器”讲授译码器的管脚功能、扩展和利用其实现一般组合逻辑函数的方法,并介绍七段显示译码器。

但是从学生的角度看,知识点繁多且零碎,不知道知识点之间的关联,更不知道学了“有什么用”“怎么用”[4-5]。

所以,本文对编码器与译码器这两个知识点进行了融合优化。

通过采用“小-中-大”三级工程项目训练体系重构教学内容,把零碎的知识点串联起来形成知识链,再由知识链组成复杂系统[6],并通过对项目设计方案的不断改进、逐级优化,“螺旋递进”地培养学生解决复杂工程问题的能力,实现“学以致用、知行合一”的教学目标,提高教学效果与人才培养质量[6]。

1 融合优化思路在传统的教学安排中,一般先讲编码器再讲译码器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

--底层设计实体计数器163

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity v74hc163 is

port( clk,clr_l,ld_l,ctp,ctt : in std_logic;

d: in unsigned (3 downto 0); --置数输入

q : out unsigned (3 downto 0); --计数输出

rco : buffer std_logic); --进位输出end v74hc163 ;

architecture behave of v74hc163 is

signal iq : unsigned (3 downto 0);

begin

process(clk, ctt, iq)

begin

if clk'event and clk='1' then

if clr_l = '0' then

iq <= (others =>'0'); --同步清0

elsif ld_l ='0' then iq<=d; --同步置数

elsif rco ='1' then iq <= d; --计数满重新计数

elsif (ctt and ctp) ='1' then iq<= iq+1 ; --计数end if;

end if;

if (iq=15) and (ctt='1') then rco<='1'; --计到15进位else rco<='0';

end if;

q<=iq;

end process;

end behave ;

--底层设计实体与非门

library ieee;

use ieee.std_logic_1164.all;

entity nand_gate is

port

( a,b:in std_logic;

nand_result:out std_logic);

end nand_gate;

architecture behave of nand_gate is

begin

nand_result<=not(a and b);

end behave;

--底层设计实体非门

library ieee;

use ieee.std_logic_1164.all;

entity not_gate is

port( c:in std_logic;

not_result:out std_logic);

end not_gate;

architecture behave of not_gate is

begin

not_result<=not c;

end behave;

--底层设计实体与门

library ieee;

use ieee.std_logic_1164.all;

entity and_gate is

port( m,n: in std_logic;

and_result: out std_logic);

end and_gate;

architecture behave of and_gate is

begin

and_result<= m and n;

end behave;

--顶层设计实体

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity excess_3_code is --顶层实体

port( cp,ctto,ctpo,clr_lo,lb:in std_logic;

qo:buffer std_logic_vector(3 downto 0);

co:out std_logic);

end excess_3_code;

architecture behave of excess_3_code is

component v74hc163 is --component v74hc163 port(

clk,clr_l,ld_l,ctp,ctt:in std_logic;

d: in unsigned(3 downto 0);

q: buffer unsigned(3 downto 0);

rco: out std_logic);

end component;

component nand_gate is --component 与非port( a,b:in std_logic;

nand_result:out std_logic);

end component;

component not_gate is --component 非port( c:in std_logic;

not_result:out std_logic);

end component;

component and_gate is --component 与port( m,n:in std_logic;

and_result: out std_logic);

end component;

signal c1,c2:std_logic;

begin

G1:v74hc163 port map

(clk=>cp,clr_l=>clr_lo,ctp=>ctpo,ctt=>ctto,

ld_l=>c2,

d(0)=>'1',

d(1)=>'1',

d(2)=>'0',

d(3)=>'0',

q(0)=>qo(0),

q(1)=>qo(1),

q(2)=>qo(2),

q(3)=>qo(3));

G2:nand_gate port map

( a=>qo(2),b=>qo(3),nand_result=>c1);

G3:not_gate port map

( c=>c1, not_result=>co);

G4: and_gate port map

(m=>c1,n=>lb,and_result=>c2);

end behave;。