论文学术第1041期

药学院实习手册

药学院实习手册药学院实习手册徐医药学院药学专业毕业实习成绩表此页有带教教师填写姓名学号实习单位实习时间年月日至年月日项目评分标准10评分8642组织纪律积极参加申请加入政治学习,遵守各项组织机构,不迟到、不早退、不旷实习。

实习学业成绩职业道德受训自觉遵守职业道德,爱岗敬业,履行岗位职责,团结协作,做好本职工作。

实习态度工作积极主动,责任心强,不怕脏、不怕累,积极参加公益性劳动,虚心求教,刻苦钻研,参加业务发展学术活动。

技术操作了解常规仪器的使用及保养,掌握熟练、规范的操作控制技术及标志方法。

业务能力自学能力求知欲强,能经常自学工具书,能较顺利阅读本专业外文书刊。

专业技能能理论联系实际,熟悉和掌握本部门的工作性质、业务范围和操作程序,洞悉各种药品的剂型、剂量、黄疸型及不良反应。

熟悉毒、麻、贵重药品的易碎管理法规和管理方法,提高实际其他工作水平。

能完整、恰当地填写各种表格,根据资料,做出系统的总结和分析,培养科学的思维能力。

资料统计部门实习成绩换班情况实习表现30分业务能力40分出科考试(理论与技能)30分实习总成绩100分应实习天,实际实习天,迟到天,早退次,病假天,事假天,旷实习天。

部门评语带教老师签章负责人签章年月日徐州医学院药学院学生毕业实习总鉴定姓名:班级:学号:实习单位:个人实习鉴定本人签名年月日实习大组鉴定:大组长签名年月日实习单位名称鉴定:实习单位(盖章)年月日药学院提案:盖章年月日学校实习主管部门意见:部门盖章年月日扩展阅读:药学院学生外派手册2药学院本科生毕业实习手册药学院二○○九年十二月前言毕业论文写作是高等学校各专业散文教学计划的重要组成部分,是学生在毕业前进行的全面的综合训练,是刻苦钻研学生综合素质、从事科学研究和解决实际问题能力的一个重要的实践性教学环节。

它在整个教学过程中具有特殊作用。

大学生经过几年的学习,虽然在和实验技能方面受到了一定的训练,但还缺少运用所学知识解决问题的独立工作能力,难以快速适应实际工作的需要。

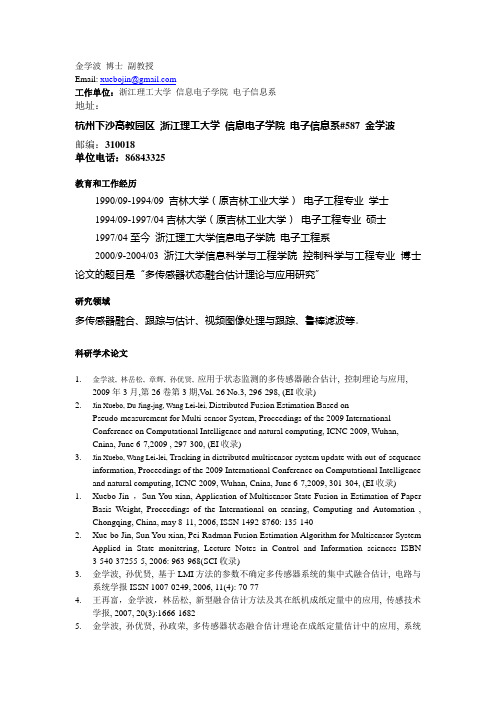

金学波 博士 副教授

金学波博士副教授Email: xuebojin@工作单位:浙江理工大学信息电子学院电子信息系地址:杭州下沙高教园区浙江理工大学信息电子学院电子信息系#587 金学波邮编:310018单位电话:86843325教育和工作经历1990/09-1994/09 吉林大学(原吉林工业大学)电子工程专业学士1994/09-1997/04吉林大学(原吉林工业大学)电子工程专业硕士1997/04至今浙江理工大学信息电子学院电子工程系2000/9-2004/03 浙江大学信息科学与工程学院控制科学与工程专业博士论文的题目是“多传感器状态融合估计理论与应用研究”研究领域多传感器融合、跟踪与估计、视频图像处理与跟踪、鲁棒滤波等。

科研学术论文1.金学波, 林岳松, 章辉, 孙优贤, 应用于状态监测的多传感器融合估计, 控制理论与应用,2009年3月,第26卷第3期,V ol. 26 No.3, 296-298, (EI收录)2.Jin Xuebo, Du Jing-jng, Wang Lei-lei, Distributed Fusion Estimation Based onPseudo-measurement for Multi-sensor System, Proceedings of the 2009 InternationalConference on Computational Intelligence and natural computing, ICNC 2009, Wuhan,Cnina, June 6-7,2009 , 297-300, (EI收录)3.Jin Xuebo, Wang Lei-lei, Tracking in distributed multisensor system update with out-of-sequenceinformation, Proceedings of the 2009 International Conference on Computational Intelligence and natural computing, ICNC 2009, Wuhan, Cnina, June 6-7,2009, 301-304, (EI收录)1.Xuebo Jin ,Sun You-xian, Application of Multisensor State Fusion in Estimation of PaperBasis Weight, Proceedings of the International on sensing, Computing and Automation , Chongqing, China, may 8-11, 2006, ISSN 1492-8760: 135-1402.Xue-bo Jin, Sun You-xian, Pei-Radman Fusion Estimation Algorithm for Multisensor SystemApplied in State monitering, Lecture Notes in Control and Information sciences ISBN 3-540-37255-5, 2006: 963-968(SCI收录)3.金学波, 孙优贤, 基于LMI方法的参数不确定多传感器系统的集中式融合估计, 电路与系统学报ISSN 1007-0249, 2006, 11(4): 70-774.王再富,金学波,林岳松, 新型融合估计方法及其在纸机成纸定量中的应用, 传感技术学报, 2007, 20(3):1666-16825.金学波, 孙优贤, 孙政荣, 多传感器状态融合估计理论在成纸定量估计中的应用, 系统工程理论与实践, 2005, 25(3), ISSN 1000-6788: 112-118(EI收录)6.金学波, 孙优贤, 参数不确定系统鲁棒H∞保代价滤波器设计新方法, 电路与系统学报2005, 10(4) ISSN 1007-0249,: 116-1207.Jin Xue-bo, Sun You-xian, Centralized and distributed robust state fusion estimation, 2005International Conference on Machine Learning and Cybernetics ISBN 0-7803-9091-1, 2005: 1037-1041(EI收录)8.金学波, 孙优贤, 集中式与分布式鲁棒状态融合估计, 控制理论与应用ISSN 1000-8152,2005, 22(6): 865-869(EI收录)H Decomposed-Composed (D-C) State Fusion9.Jin Xue-bo,Sun You-xian, RobustEstimation for Multisensor System with Uncertain Correlated Measurement Covariance, IEEE International Conference on Industrial Technology, 14-17 December 2005, ISBN: 0-7803-9484-4: 424-427(EI收录)10.Jin Xue-bo,Sun You-xian, Application of multisensor state fusion in estimation of paperbasis weight, IEEE International Conference on Industrial Technology, 14-17 December 2005, ISBN: 0-7803-9484-4: 424-427(EI收录)11.金学波林岳松, 真丝纤维微观结构研究中的新技术, 纺织学报ISSN 0253-9721,CN11-5167/TS, 2004, 25(2): 32-3412.金学波, 孙优贤, 多传感器系统分布式不相关优化融合估计算法, 第五界全球智能控制与自动化大会ISBN:0-7803-8273-0, 2004: 1575-1579 (EI收录)13.Jin Xue-bo, State fusion estimation covariance of measurement fusion, Advances inModelling Series B: Signal Processing and Pattern Recognition, 2004 V ol 47 nº 6: 43-52(EI 收录)14.Jin Xue-bo, Sun You-xian, Optimal Estimation for Multilevel Multisensor Data Fusion inCorrelated Measurement Noise, Proceedings of 2002 6th International Conference on Signal Processing Proceedings ISBN 0-7803-7488-6, 2002: 1641-1644 (ISTP收录)15.Jin Xue-bo, Sun You-xian, Optimal Fusion Estimation Covariance of Multisensor DataFusion on Tracking Problem, Proceedings of the 2002 IEEE International Conference on Control Applications ISBN 0-7803-7386/02, 2002: 1288-1289, (EI、ISTP收录)16.Jin Xue-bo, Sun You-xian, Estimation Covariance of Measurement Fusion on Track-to-TrackProblem, 2002 IEEE Region 10 Conference On Computer, Communication, Control and Power Engineering Proceedings ISBN 0-7803-7490-8, ISBN 7-900091-55-6, 2002: 1650-1652, (EI、ISTP收录)17.金学波, 孙优贤, 相关测量噪声的多传感器最优融合状态估计, 浙大学报ISSN1008-973X, 2003, 37(1): 60-64(EI收录)18.Jin Xue-bo, Sun You-xian, Optimal centralized state fusion estimation for multi-sensorsystem with correlated measurement noise, Proceedings of 2003 IEEE Conference on Control Applications ISBN 0-7803-7729-X, ISSN 1085-1992, 2003.6: 770-772 (EI收录)19.Jin Xue-bo, Sun You-xian, Multisensor state fusion estimation with correlated measurementnoise, 2003 International Conference on Machine Learning and Cybernetics ISBN 0-7803-7865-2, 2003.11: 1000-1003(EI收录)20.Jin Xue-bo, Sun You-xian, Covariance Comparison of State-vector Fusion and MeasurementFusion, 2003 International Conference on Machine Learning and Cybernetics ISBN 0-7803-7865-2, 2003.11: 2067-2070(EI收录)21.Jin Xue-bo, Sun You-xian, Covariance Comparison of State-vector Fusion and MeasurementFusion, Advances in Modeling & Analysis C: System Analysis Control & Design Simulation,ISSN 1240-4535, 2003, 58(2), 35-46 (EI收录)22.Jin Xue-bo, Sun You-xian, State Fusion Estimation for Mutlilevel Multisensor System,Journal of Systems Engineering and Electronics,, Vol.14,No.4,2003: 77-83(EI收录)主持的科学研究项目1.分布式多源复杂时序数据融合估计研究(60971119), 经费额度为28万, 经费来源为国家自然科学基金, 2010.1-2012.12, 主持。

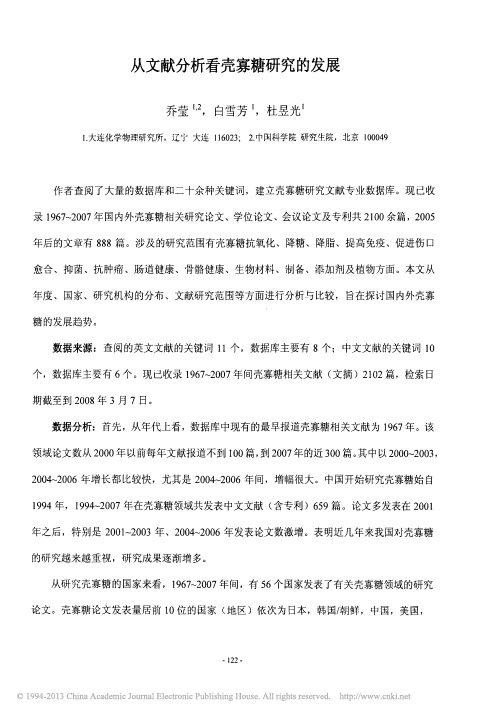

从文献分析看壳寡糖研究的发展_乔莹

几 丁 质酶的研 究

,

发表 的文 章数 占到 了

。

。

近些 年 国 内外对 壳寡糖 的研 究 处 于飞 速 发展 阶段

,

由于 壳寡糖 具

、

有 许 多独 特 的理 化 性 质 和 生 理 功 能

现 已 广 泛应 用 于 食 品

、

医药

、

化妆 品

、

农业生产

环保

等领域

余篇

、

年 后 的文 章有

愈合 年度

、

篇

抗 肿瘤

。

涉 及 的研 究 范 围有壳寡糖 抗氧 化

肠 道健 康

、

、

、

降糖

制备

、

降脂

、

提 高免 疫

促进 伤 口

。

抑菌

国家

、

、

骨骼 健 康

、

生 物 材料

、

、

添 加剂 及 植 物 方面

,

本 文从

、

、

研 究 机构 的 分 布

。

文献研 究范 围等 方面进 行分 析与 比 较

篇 文章 的 中 国海 洋大 学

随 后是 浙江 大学

,

发表

文章

篇

。

从 壳 寡糖 的研 究 范 围来划分

,

目前对 壳寡糖 研 究 最 多的 为壳 寡糖的制备

,

,

发表 的文章 数

。

占到壳 寡糖研 究 论文总量 的

。

其 次是 壳寡糖在植 物方 面 的应 用 发表 的文章 数 占到 了

、

随后 为 降解 壳 聚 糖 的一 些 壳聚 糖酶 从 以 上 分 析 可 以看 出

旨在 探 讨 国 内外 壳 寡

北宋灭亡的主客观因素分析-中国古代史论文-历史论文

北宋灭亡的主客观因素分析-中国古代史论文-历史论文——文章均为WORD文档,下载后可直接编辑使用亦可打印——中国自古以来就是一个多民族的国家,民族关系也是每一个王朝必须面对的重要问题。

通常民族关系处理得当,、经济和文化也会处于健康向上的发展态势,处理不当则往往会处于的境地,甚至陷入危亡之中。

宋代是一个特殊的朝代,从现有研究看,过去所说的积贫积弱观点已受到学术界的质疑和反思。

李裕民先生认为宋代无论经济还是科技、文化等方面与唐代相比,均有过之而不及,谈不上积贫; 而就积弱来说,宋朝与辽、金、西夏以及后来的蒙古在军事上也是旗鼓相当,才不致很快被灭亡。

①可是从对外政策来看,宋庭绝大多数情况下奉行的是保守的以进为退的防守策略。

在与辽、西夏和金乃至后来的蒙古人的战争中,胜少败多,这样的结果要说民族自信心不受影响很难令人信服,一个不自信的民族在处理民族关系时就多少显得有些底气不足,也为其最终的失败买下了伏笔。

北宋政府面对的最大危险主要是来自于辽、西夏和金。

辽和西夏互相借重对方势力来胁迫北宋答应他们提出的议和条件。

宋也往往通过重赏和贿赂等政策来瓦解夏辽同盟,乃至于后来兴起的金人往往借机趁火打,而面对金人的步步紧逼,宋庭又在决策上出现重大失误。

末期的北宋犹如沉疴在身的病人,积重难返。

北宋就在这样一种被动防御、的尴尬处境中被金人结束了160 多年的统治。

具体而论,北宋灭亡既有客观方面难以克服的困难有关,也有主观方面因循守旧、不思进取等原因造成。

一、客观原因(一)都城偏居开封,对西部、北部鞭长莫及宋朝都城远在开封,整个西北乃至北部的广大疆域均被西夏和辽及后来兴起的金占领,导致中原地区时常危机四伏。

1004 年宋辽订立《澶渊之盟》后割幽云十六州给辽,宋北鄙失去屏障,辽人遂能长驱直入,如骨鲠在喉,长期受辽掣肘。

所以钱穆认为:建都开封,尤使宋室处一极不利的形势下。

藩篱尽撤,本根无庇。

[1]531不仅对东北显豁呈露,易受威胁。

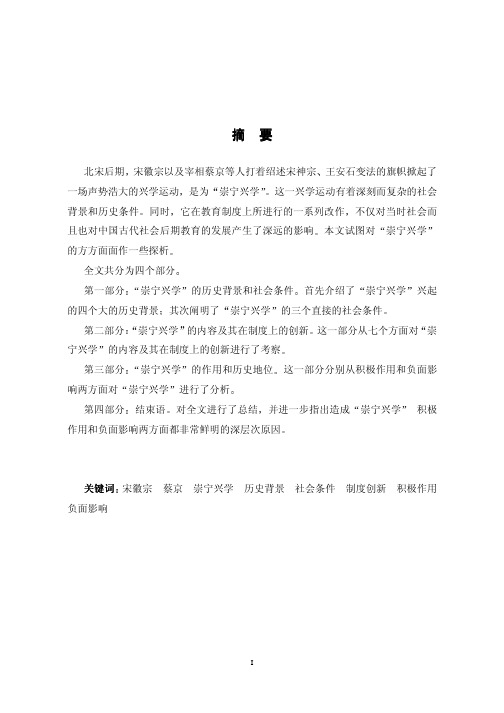

“崇宁兴学”研究

摘 要北宋后期宋徽宗以及宰相蔡京等人打着绍述宋神宗王安石变法的旗帜掀起了一场声势浩大的兴学运动是为崇宁兴学这一兴学运动有着深刻而复杂的社会背景和历史条件同时它在教育制度上所进行的一系列改作不仅对当时社会而且也对中国古代社会后期教育的发展产生了深远的影响本文试图对崇宁兴学的方方面面作一些探析全文共分为四个部分 第一部分崇宁兴学的历史背景和社会条件首先介绍了崇宁兴学兴起的四个大的历史背景其次阐明了崇宁兴学的三个直接的社会条件第二部分崇宁兴学的内容及其在制度上的创新这一部分从七个方面对崇宁兴学的内容及其在制度上的创新进行了考察第三部分崇宁兴学的作用和历史地位这一部分分别从积极作用和负面影响两方面对崇宁兴学进行了分析第四部分结束语对全文进行了总结并进一步指出造成崇宁兴学积极作用和负面影响两方面都非常鲜明的深层次原因关键词宋徽宗 蔡京 崇宁兴学 历史背景 社会条件 制度创新 积极作用 负面影响AbstractOn the later stage of Northern Song Dynasty, Emperor Huizong and Primer Minister Cai Jing raised a gigantic and vigorous movement of setting up schools, the aim of which they claimed was to inherit the unfulfilled wish of Emperor Shenzong and Wang Anshi’s Reform. This movement is called “Setting up Schools During Chongning Period”. This movement has deep and complicated historical background and social terms. At the same time, a series of reforms carried on toward education system, have not only brought a far-reaching influence on the society at that time, but also produced a far-reaching influence on the development of the education system on the later stage of ancient society of China. This paper attempts to do some analysis in every aspect in “Setting up Schools During Chongning Period”.There are four sections in the paper.Section I the historical background and social terms of “Setting up Schools During Chongning Period”. In this section, an introduction is made firstly to the historical background from four aspects. Then three direct social terms are explained for “Setting up Schools During Chongning Period”.Section II the content and system innovation of “Setting up Schools DuringChongning Period”. This section renders a successive investigation of the content and system innovation of “Setting up Schools During Chongning Period” from seven aspects.Section III the role and historical status of “Setting up Schools During Chongning Period”. This section makes an analysis on the role and historical status of “Setting up Schools During Chongning Period” from two aspects, which are positive and negative effects.Section IV the conclusion. This section summarizes full texts, and points out the profound reasons why both positive and negative effects of “Setting up Schools During Chongning Period” are very distinct.Key words emperor Huizong; Cai Jing; setting up schools during Chongning period; historical background; social terms; system innovation;positive role; negative effects独创性声明本人声明所呈交的学位论文是我个人在导师指导下进行的研究工作及取得的研究成果尽我所知除文中已经标明引用的内容外本论文不包含任何其他个人或集体已经发表或撰写过的研究成果对本文的研究做出贡献的个人和集体均已在文中以明确方式标明本人完全意识到本声明的法律结果由本人承担学位论文作者签名日期年月日学位论文版权使用授权书本学位论文作者完全了解学校有关保留使用学位论文的规定即学校有权保留并向国家有关部门或机构送交论文的复印件和电子版允许论文被查阅和借阅本人授权华中科技大学可以将本学位论文的全部或部分内容编入有关数据库进行检索可以采用影印缩印或扫描等复制手段保存和汇编本学位论文保密在年解密后适用本授权书本论文属于不保密请在以上方框内打学位论文作者签名指导教师签名日期年月日日期年月日引 言北宋后期宋徽宗赵佶以及宰相蔡京等人打着绍述宋神宗王安石变法的旗帜掀起了一场声势浩大的兴学运动是为崇宁兴学相对于此前宋仁宗时期由范仲淹主持的庆历兴学和宋神宗时期由王安石主持的熙宁兴学而言由于宋徽宗蔡京等人在历史上臭名昭著学术界对崇宁兴学并没有给予应有的重视或者认为这只不过是宋徽宗蔡京集团在打击元祐党人的同时借以要结士誉买觅人情[1]的一种手段从而予以简单的否定实际上尽管崇宁兴学的目的与此前的庆历兴学和熙宁兴学有着较大的不同但由于它的兴起有着更为复杂的社会背景和历史条件同时这场兴学运动前后持续了近20年因此无论从兴学规模持续时间影响程度来看都是前两次兴学运动所无法比拟的崇宁兴学固然是宋徽宗蔡京等人玩弄权柄的重要手段之一但如果把它置于整个中国古代教育发展史的长河中来看我们就会发现教育发展自身的逻辑已使这一兴学运动并非其表象所呈现给我们的那么简单甚至可以说它写下了中国古代教育史上浓墨重彩的一笔本文拟就这次兴学的历史背景和社会条件制度上的变化以及它在历史上的作用与地位等几方面来对崇宁兴学作一些探讨1 崇宁兴学的历史背景和社会条件北宋时期兴学运动之所以一浪高过一浪是有其独特的社会大背景的对于崇宁兴学我们同样得将它置于这一大的社会背景进行考查1.1 崇宁兴学的历史背景1.1.1 北宋长期以来的右文政策宋代是一个重文轻武的时代宋代重文轻武的政策肇始于北宋初年这一政策形成后有着巨大的历史惯性被奉为祖宗家法为宋朝历代统治者所遵循北宋是继唐末五代长期的分裂割据之后建立起来的一个相对统一的王朝北宋建立之前战乱连年政权频繁更迭造成这种局面的根源就是武人权重往往依靠武力改朝换代北宋建立者赵匡胤本人也正是以殿前都点检的身份和后周最高军事统帅的权力在陈桥驿黄袍加身而称帝代周的对国家分裂所造成的灾害和武人之祸身历其境的赵匡胤是再清楚不过的赵匡胤在建立宋朝后为了不使赵宋政权成为继后周之后第六个短命王朝实现天下长治久安采取了稍夺其权制其钱谷收其精兵[2]的措施其中重点是收夺武将兵权抑制武人其主要做法就是以文人典兵权以文人知州军与文臣共谋国事亦即变过去武人的天下为文人的天下从此文人大得进用满朝朱紫贵尽是读书人[3]这一做法被称为兴文教抑武事[4]以文化成天下[5]这样看来宋初重文轻武乃宋初形势发展的必然纵观中国古今治国用人文武并用为治道之常但如果在二者之中有所倚重势必造成抑此扬彼宋初之所以重文一个重要原因就在于抑武抑武不是针对某些个人而是针对整个武人社会群体正如宋史文苑传所云艺祖革命首用文吏而夺武臣之权宋之尚文端本乎此[6]宋初重文轻武政策的出台一方面是宋初形势发展的必然另一方面与当时最高统治者尤其是宋太祖对文人及文治之认识是密不可分的,因为任何政策的制定都是受制定者的认识所支配的宋朝之国策法度基本上确立于太祖朝以后各帝仅为奉守略有发展赵匡胤本人虽是武人出身的皇帝其皇位也是通过军权而篡得但其素质显然高于此前许多武人出身的皇帝例如他在陈桥兵变后回军开封时一改往日武将叛乱杀戮掳掠的做法令士兵秋毫无犯并善待柴氏伐南唐时嘱主将曹彬不准杀戮不得加害李煜一门由此可见他对武所发挥作用的局限性有着清醒的认识与之同时他对读书人重要性的认识却在逐步提高乾德改元赵匡胤曾对宰相说年号须是前代没有用过的而乾德三年965赵匡胤在宫内偶尔看到一面镜子背后有乾德四年铸的字样便召来大臣询问结果只有学士窦仪答得上来此必蜀物昔伪蜀王衍有此号当是其岁所铸也赵匡胤因而感叹道宰相须用读书人由是益重儒臣矣[7]基于宋太祖自身的素质和他对文与武的认识宋初顺应时势崇尚文治是自然的而且在此之后宋代诸帝大体都能遵守祖法史载太宗真宗在藩邸时就有好学之名太宗锐意文史真宗喜文学多著述并作劝学诗宣扬读书的好处书中自有黄金屋书中自有千钟粟书中车马多如簇书中自有颜如玉自时厥后子孙相承上之为人君者无不典学[8]由宋朝建立者及其继承者所倡导的这样一股重文之风伴随着宋代社会的发展逐渐在整个社会弥漫开来以往为社会上层所垄断的文化开始向社会下层移动社会下层文化素质明显提高这样一种浓厚的文化氛围就使得文化事业的勃兴成为可能这主要表现在尊孔重儒重视文化典籍的搜求和整理以及兴建学校发展教育等方面 1.1.2 唐宋之际中国传统社会结构的变迁除赵宋王朝建立之后所形成的重文之风外唐宋之际中国古代传统社会结构所发生的深刻变化也推动了学校教育的发展首先汉魏以来影响中国达数百年之久的门阀政治彻底终结以往那种由世家大族世代垄断政权的局面完全改观封建政权的开放程度大大地提高与此同时汉唐时期流行的门第等级观念开始被部分地抛弃取士不问门第婚姻不问阀阅[9]等等成为一种新的社会风尚其次由于商品货币经济的发展传统的均田制和租庸调制走向崩溃土地自由买卖的私有化程度进一步提高为此赵宋王朝实行了不抑兼并的土地政策地主阶级可以自由自在地购买田产就连官府也把所掌握的官田公田拿来出租以弥补财政之不足私有经济的发展有了较大的空间和自由度再次唐中期以来两税法的推行使得生产者对国家和地主的人身依附关系获得了较大程度的解放凡此种种社会政治和经济结构的变迁使得这一时期的社会心理和价值观念发生了一些新的变化由此直接推动了以学校教育为主要内容之一的宋代社会文化的发展在学术文化上自宋代初年以来一股经学变古思潮日渐发展壮大人们不再笃守汉唐以来的章句训诂之学这在一定程度上意味着传统的统治思想发生了某种变化因此宋朝统治者虽然一方面实行着较为开明的文化政策而另一方面尤其是到了北宋中后期随着社会危机的加剧统治者也在着力加强思想控制强调所谓一道德这一点将在后面详细展开来谈当然北宋兴学运动一再兴起更为直接的社会原因恐怕还是这一历史时期社会文化结构的变迁唐宋社会政治经济结构的变迁所导致的最终结果便是平民社会的到来享受文化教育不再是少数门阀士族的特权而且这时人们追求实际注重实用讲求功利重视个人才能这就使得一般民众和普通士人依靠个人奋斗也可进入上层社会这种奋斗主要就是参加科举考试这一时期许多出身寒门的人士通过个人奋斗取得成功例如曾主持过庆历兴学的范仲淹其幼年的生活十分贫困两岁丧父母亲带着他改嫁淄州长山今山东邹平长大后他发愤自强赴南京应天府书院求学以至冬月惫甚以水沃面食不给至以糜粥继之人不能堪仲淹不苦也[10]后来考中进士官至参知政事欧阳修也是幼年孤贫依叔父家于随州经过勤奋学习终于考中进士在嘉祐六年1060做了参知政事而且蓄道德而能文章[11]成为一代散文宗师这种情况在宋以前是较少见的但在宋代这样一个平民社会这种情况是常有的事许多读书人并以此作为自身发愤图强的精神动力1.1.3 科举制度的进一步完善上面提到宋代社会经济政治的变化最终导致宋代平民社会的到来社会各阶层之间壁垒森严的界限逐渐被打破在这一过程中科举制度发挥了重要作用通常认为科举制度草创于隋代但作为一种系统制度的确立应始于唐代科举制度在唐代虽构建起最基本的框架并对大唐帝国的发展产生过十分积极的作用同时它的局限性也还相当突出例如唐代科举有所谓公荐即要想考中得有权臣向主考官推荐结果导致行卷之风盛行另外以诗赋取士缺乏严谨录取标准考试科目多达十二种过于繁复缺乏监督制约机制等情况也存在这就难保公平科举制度的优越性也就大打折扣实际上从选官制度整体而言唐代是门荫制度与科举制度并重的时代科举制度发展到宋代则趋于完备关于宋代科举制度的相关情况张希清先生在其中国科举考试制度一书中曾作过专门研究总的来说宋代科举制度的创新主要表现在以下几个方面首先是对科举科目的定型北宋前期承唐及五代之制贡举科目主要有进士明经诸科其中诸科又包括九经五经三礼三传三史学究开元礼后改为开宝通礼明法等科名目繁多既缺乏规范性又无定制北宋庆历年间1041-1048范仲淹推行新政其中一项措施就是精贡举要求进士科先策论后诗赋重视政治素质和实际才能的考查北宋中期经王安石变法贡科科目发生重大变化罢诸科而独存明法[12]他们的改革虽然都以失败告终但对科举科目的简化起到了促进作用几经反复到宋徽宗统治时期完全成为进士一科举士其次是科举类型的定制上宋初承唐及五代之制仍分解试省试两级考试即地方性的资格考试解试和中央部门级的资格考试省试唐代也曾有过皇帝亲蒞的殿试但只是偶一为之未成制度乾德四年966宋太祖曾亲试下第举人以平不公之怨开宝五年972礼部省试宋太祖召对讲武殿始放榜[13]开宝六年973因权知贡举李昉用情取舍非当宋太祖乃令于下第者中择一百九十五人另定考官乙亥上御讲武殿亲阅之得进士二十六人又赐准钱二十万以张宴会责昉为太常少卿考官右赞善大夫杨可法等皆坐责自兹殿试遂为常式[14]这样解试省试殿试三级考试制度得以确立此外科举贡举考试时间经历了一个由不定期到定期的发展变化过程宋英宗治平三年1060十月六日诏曰今后宜每三年一开科场应天下人所解进士并以本处旧额四分解三分[15]从此三年一开科场遂成为不易之制在具体考试时间上唐代各级考试尚未完全固定时间北宋时期逐渐形成定制解试一般是八月上旬锁院中旬引试九月中开院省试锁院引试和放榜的具体日期一般是正月上旬或中旬锁院锁院后十日左右引试二月底或三月初奏名放榜殿试日期一般在三月至于贡举考试地点也逐渐走向固定北宋中期以后诸州开始陆续创建贡院作为解试场所这些贡院颇具规模少则数十间多则三五百间甚至上千间礼部贡院宋神宗时以开宝寺为之徽宗崇宁11021106以后乃有定所自宋太祖创立殿试制度以来初以讲武殿为考场讲武殿后改名为崇政殿自神宗熙宁三年1070殿试改于集英殿宋代对科举考试制度最具建设性的贡献在于创设了一系列保障公平的机制宋代先后颁布了科场法亲试进士条例考校进士程式等法律性规定采取各种办法防止权贵干扰对付考试中的循私舞弊行为 太宗淳化三年992正月六日以翰林学士承旨苏易简等权知贡举易简等以贡举重柄义在无私受诏之日五人便赴尚书省锁宿更不归私第以杜绝请托物论嘉之[16]从此隔离考官和外界的锁院就成为一项制度普遍实行于解试省试及殿试这是一项十分重要的制度为应举人公平竞争提供了重要保障此外对于有朝廷官员子弟登第的宋太祖于乾德三年965下令礼部必须报告并对登第者再行复试此后成为制度后来对于考试官的亲戚故旧另设考场单独规定录取人数的别头试普遍实行于解试省试为了防止应举人在考场作弊北宋时实行挟书传义代笔之禁所谓挟书之禁即严禁挟带书籍有专门的官吏搜查一旦查实严加处罚如真宗景德二年1005二月二十三日礼部贡院言昨考试诸科举人就座搜获怀挟书册节义者十七人准例挟出准条殿两举[17]殿两举即取消两次参加科举考试的资格传义类似于我们今天考场上常见的交头接耳传递字纸条等作弊行为宋太祖乾德二年964宋廷规定如有遥口相授传与人者即时遣出不在试限[18]代笔之禁在宋代亦屡申严之如宋太宗雍熙二年985十二月三十日诏曰今后如有倩人撰述文字应举者许人告言送本处色役永不得仕进同保人知者殿四举不知者殿两举受情者在官停任选人殿三选举保人殿五举诸色人量事科罪[19]这些制度普遍施行于解试省试及殿试对保证科举考试的公正公平公开必定产生积极影响以上制度为保证考试顺利进行提供了条件要使考试结果客观公正试卷的评定也是十分重要的一环太宗淳化三年992宋太宗根据大臣的建议在殿试中糊名考校即把考卷上的名字序号等标记封起来以避免通关节但糊名之后阅卷人还可以辨认卷子的笔迹后来又采取将考生的试卷另行謄录后阅卷的办法据现有史料殿试的謄录始见于宋真宗景德二年1005以后逐渐推广此后宋真宗大中祥符四年1011新定亲试进士条例明确规定举人纳试卷内臣收之先付编排官去其卷首乡贯状以字号第之待考定等第后始取乡贯状字号合之乃第其姓名差次并试卷以闻遂临轩唱第[20]这样考试官在评定试卷时看不到举人的姓名乡贯难以作弊这些制度在防止考校作弊中起了关键作用欧阳修曾评价道窃以国家取士之制比于前世最号至公糊名謄录而考之使主司莫知为何方之人谁人之子不得有所受憎薄厚于其间故议者谓国家科场之制虽未复古法而便于今世其无情如造化至公好权衡祖宗以来不可易之制也[21]由上可见发轫于隋唐的科举取士制度到了宋代已日趋完善成为一项十分成熟的取士制度从而为社会普通士人跻身社会上层创造了一个相对公平的环境这就极大地激发了社会各阶层读书入仕的热情推动了学校教育的大发展1.1.4 北宋后期加强思想统治的需要如果说北宋长期以来的右文政策唐宋之际中国传统社会结构的变迁以及科举取士制度在北宋的成熟使崇宁兴学成为可能那么北宋后期思想专制的加强则使之成为一种必然趋势当然如果仅有前述三方面的社会背景也就很难说明崇宁兴学与此前的庆历兴学以及熙宁兴学有什么大的区别了提到中国古代思想专制人们自然会想到秦始皇的焚书坑儒汉武帝的罢黜百家独尊儒术以及明清时期的大兴文字狱很少会提到北宋时期其实在封建君主专制条件下必然会导致思想专制否则高高在上的皇权就失去了它赖以生存的思想土壤诚然由于北宋建立之初特殊的历史条件使得赵宋王权采取了相对开明的文化政策但这终究不是长久之策到了北宋中后期即宋真宗以后随着宋王朝内忧外患的日渐加深思想专制之风也日趋盛行北宋统治走下坡路是从宋真宗统治时期开始的到宋仁宗统治时期赵宋王朝的统治已经危机四伏正如欧阳修所指出的那样从来所患者夷狄今夷狄叛矣所恶者盗贼今盗贼起矣所忧者水旱今水旱作矣所赖者民力今民力困矣所须者财用今财用乏矣[22]宋仁宗至和二年1055六月欧阳修在与贾黯的联名上疏中再度指出了纪刚日坏政令日乖国日益贫民日益困流民满野滥官满朝的严酷事实[23]宋仁宗嘉祐四年1059王安石在给皇帝所上万言书中指出当时的形势内则不能无以社稷为忧外则不能无惧于夷狄天下之财力日以困穷而风俗日以衰坏四方之士諰諰然常恐天下之久不安[24]与这样一种每况愈下的朝政相表里的是整个社会缺乏一种共同的价值理想缺乏凝聚人心的道德力量思想混乱人心不一学术不一一人一义十人十义[25]这样一种思想混乱的状况已危及到中央集权的统治秩序引起了当时士人的注意程颐曾以方今人执私见家为异说支离经训无复统一[26]加以形容于是乎一道德而同风俗的要求随之产生到了宋神宗时期为了推行新法对这样一种思想状况更是无法容忍所以熙宁五年1072正月宋神宗正式向王安石提出颁行新经义的要求经术今人人求异何以一道德卿有所著可以颁行令学者定于一[27]翌年三月宋神宗又说举人对策多欲朝廷早修经义使义理归一[28]宋政府还专门设立经义局训释诗书周礼三经义命王安石提举经义局熙宁八年1075元月三经义修成奏御随后颁行天下作为全国学校统一教材和科举考试标准至此王氏新学作为宋王朝一道德的工具在北宋后期独行于世者六十年[29]其间随着北宋后期政局的变动尤其是宋哲宗朝高太后当政时期新学的地位一度发生动摇但由于没有更好的意识形态工具新学依旧在意识形态领域占居主导地位由上可见赵宋王朝在建国之初实行相对开明的思想文化政策但中后期明显地加强了思想意识形态领域的控制这是一个大的趋势北宋中期宋王朝开始强化思想意识形态领域的专制在很大程度上是为了改变内忧外患所引起的思想上的混乱状况而且这种必要性应当说在北宋整个后期都是存在的但随着宋徽宗继位蔡京拜相宋徽宗蔡京集团的形成这种必要性更多地让位于为宋徽宗蔡京集团的腐朽统治服务的现实性关于宋徽宗蔡京集团的形成罗家祥教授在其专著朋党之争与北宋政治中作了很好的分析他从宋徽宗蔡京各自的个人禀性上的诸多契合点以及历史的机遇等方面阐明了二人结成一体的必然性当宋徽宗蔡京集团形成之后他们打着恢复新法的幌子大肆排斥和打击异已将持不同政见或不与他们狼狈为奸的朝臣包括已去世的文彦博司马光苏轼等人在内的120人打成奸党崇宁三年1104奸党人数增加到309人皆石刻姓名颁之天下[30]史称元祐党人宋徽宗蔡京等人之所以大兴党禁其目的用其臣僚们的话说就是要使天下可以无为而治天下之气平纷纷之论息让所有异论者销声匿迹最终达到该集团实行为所欲为的独裁统治在宋徽宗蔡京集团大兴党禁不遗余力地打击异已迫害忤其意旨者的同时宋廷又打着绍述的旗帜处心积虑地为其统治培养奴才和驯服工具为此蔡京请以学校为今先务乞天下并置学养士[31]当然蔡京的建议明显受了元符上书的启发宋神宗死后宋朝政局一再反复有鉴于此宋徽宗蔡京集团便想以兴学来要结士誉买觅人情[32]从而达到稳定其统治的目的这也反映在崇宁兴学对于教学内容的改作上例如宋廷曾明令元祐学术政事不得教授学生[33]如若以元祐学术政事聚徒传授者委监司察举必罚无赦[34]关于这方面的内容将在下文中作更进一步的分析说明总之蔡京主持的崇宁兴学。

区块链技术驱动智慧图书馆智慧增值服务路径研究

2021年第1040区块链技术驱动智慧图书馆智慧增值服务路径研究*杨 群 黎雪松 王毅菲(四川轻化工大学图书馆 四川自贡 643000)〔摘 要〕 基于区块链技术去中心化、防篡改、可追溯性、共识机制等特点,文章提出了一种区块链技术驱动智慧增值服务模式及应用路径,实现用户在资源获取方式、学习交流平台以及时间空间上的转变,并有效解决智慧图书馆在信息资源收集、安全存储和共享传播等方面的问题,满足以用户需求为中心的智慧增值服务。

智慧图书馆应利用区块链技术实施变革,如开展区块链在图书馆的应用、加强区块链技术规划研究、制定区块链数据标准以及培养智慧图书馆区块链技术专业人才等,改善资源的服务内容,提高资源服务质量,迎接区块链技术变革,进一步推进智慧增值服务模式上新台阶。

〔关键词〕 区块链技术 智慧图书馆 智慧增值服务〔中图法分类号〕 G252〔引用本文格式〕 杨群,黎雪松,王毅菲.区块链技术驱动智慧图书馆智慧增值服务路径研究[J].图书馆,2021(1):40—48.区块链的出现始于2008年末一个自称为中本聪(Satoshi Nakamoto)的人或者团体发表在比特币论坛的一篇论文Bitcoin: A peer-to-peer electronic cash system [1]。

该文指出区块链技术是构建比特币系统的基础技术,是比特币系统底层支撑技术之一,区块链记录了所有元数据和加密交易信息,建立一个完全通过点对点技术实现的电子现金系统,交易双方不需要通过第三方参与直接进行交易。

作为比特币底层技术的区块链一直被当作配角,并未引起学界的关注,到2015年12月,Linux 基金会发起了Hyperledger 开源区块链项目,目的是发展跨行业的商业区块链平台[2]。

2016 年10月,工信部信息化和软件服务业司指导编写了《中国区块链技术和应用发展白皮书》,对区块链技术的发展提供政策支持[3],作为比特币系统底层的区块链技术逐步得到重视,成为各国政府、科研院所关注的焦点,区块链技术的研究由此拉开了序幕。

收集国外体育类核心期刊

最近学校的学术风气越来越浓了,根据学校的最新政策,发表学术论文不但能够在考研复试中获得额外加分,还能在保研中获得优惠,同时,出国是科研学术水平最大因素之一,也正因为这样,最近有不少同学都在问我如何发表,我今天就把自己几年来的发表心得与大家分享一下:首先,期刊分为核心期刊和普通期刊,标准是北大每四年出版一回的《中文核心期刊目录总览》,一般的核心期刊较普通期刊不但要求高出许多,而且审稿时间一般为三个月,之后还要再排三到六个月的队(总计六到九个月),以及一千多元一篇的版面费。

我的个人建议是,核心期刊也分三六九等,如果你是希望这个以后对你一直都比较有用的话,尽量选择在要目总览的排序中,每类排序的前一半,因为学术腐败,如臭名昭著的商业现代化这类事件,通常发生在排名较为靠后的核心期刊上面。

同时,好的核心期刊的要求较高,建议大家先从普通期刊开始投起,同时多读一些顶级期刊的论文,最后一定会成功的。

以下是我投过的学术刊物,为大家提供一些自己的经历,希望可以帮到大家国外篇:1.Cambridge Quarterly of Healthcare Ethics SCI收录期刊,不需要版面费,不过由于是季刊,时间较长,而且由于是顶级期刊,要求文章质量极高,社会科学大类的同学可以挑战一下自己2.Hong Kong Journal of Occupational Therapy SCI收录期刊,收版面费,视文章质量而定,难度较上一个较低,建议学医学和体育学的同学尝试这个期刊还有个插曲,寄论文过去之后,一个香港中文大学的教授找到我,貌似是这个刊物的编委或者学术顾问吧,说让我把他加成二作者,他出所有的钱还能保证我当月就能发表,囧的我。

3.LEISTUNGSSPORT 这个德国期刊是我投过的国外期刊里唯一一个给我大量稿费的期刊,一页纸50—100欧元的稿费,不过要翻译成德文才可以。

国内篇:1.《中国财经信息资料》之所以第一个说他,是因为他是我见过的核心期刊里唯一一个给稿费的期刊。

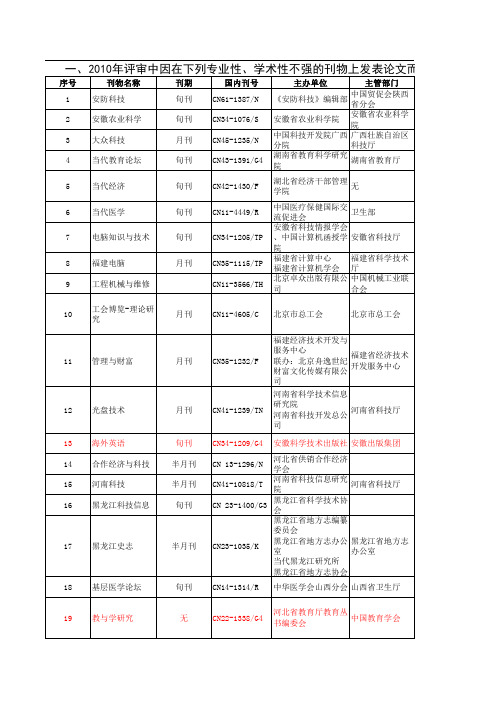

不合格期刊

CN11-2939/G4 CN11-2939/G4 CN14-1358N

光明日报社 光明日报报业集团 太原科技战略研究院 太原市科技局

25

月刊

CN42-1665/T

湖北省科技厅

湖北省科技厅

26

科技风

半月刊

CN13-1322/N

河北省科技咨询服务 河北省科学技术 中心 协会 湖北省科学技术协会 中国科学技术协 会

CN32-1427/N CN11-4688/T CN53-1125/N CN22-1221/F CN42-1616/F CN43-1027/F CN14-1279/TU CN14-1108/R CN11-3456/GO CN62-1110/C CN14-1298/R CN23-1464/D CN61-1019/G8 CN12-1392/G2

旬刊 半月刊 旬刊

CN53-1179/N CN50-1129/R

现代物业杂志社

云南省建设厅

重庆厂矿卫生管理协 重庆卫生局 会 山东省教育厅

CN 37-1333/G4 曲阜师大 CN14-1453/O1 山西省期刊协会

双月刊 半月刊 双月刊 双月刊

CN11-2697/TP CN23-1106/D CN22-11302/D CN42-1387/R

旬刊 半月刊 半月刊 月刊

CN32-1032/C CN22-1041/I CN15-1336/GO CN22-1010/C

延边州文学艺术界联 延边州文化局 合会 文苑杂志社 吉林省社会科学院 内蒙古新华报业中心

48 49 50 51 52 53 54 55

现代物业 现代医药卫生 现代语文 新课程学习(综 合) 信息与电脑 学理论 延边党校学报 医学与社会

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Design of the Temperature Control System Based on AT89C51ABSTRACTThe principle and functions of the temperature control system based on micro controller AT89C51 are studied, and the temperature measurement unit consists of the 1-Wire bus digital temperature sensor DS18B20. The system can be expected to detect the preset temperature, display time and save monitoring data. An alarm will be given by system if the temperature exceeds the upper and lower limit value of the temperature which can be set discretionarily and then automatic control is achieved, thus the temperature is achieved monitoring intelligently within a certain range. Basing on principle of the system, it is easy to make a variety of other non-linear control systems so long as the software design is reasonably changed. The system has been proved to be accurate, reliable and satisfied through field practice. KEYWORDS: AT89C51; micro controller; DS18B20; temperature1 INTRODUCTIONTemperature is a very important parameter in human life. In the modern society, temperature control (TC) is not only used in industrial production, but also widely used in other fields. With the improvement of the life quality, we can find the TC appliance in hotels, factories and home as well. And the trend that TC will better serve the whole society, so it is of great significance to measure and control the temperature. Based on the AT89C51 and temperature sensor DS18B20, this system controls the condition temperature intelligently. The temperature can be set discretionarily within a certain range. The system can show the time on LCD, and save monitoring data; and automatically control the temperature when the condition temperature exceeds the upper and lower limit value. By doing so it is to keep the temperature unchanged. The system is of high anti-jamming, high control precision and flexible design; it also fits the rugged environment. It is mainly used in people's life to improve the quality of the work and life. It is also versatile, so that it can be convenient to extend the use of the system. So the design is of profound importance. The general design, hardware design and software design of the system are covered.1.1 IntroductionThe 8-bit AT89C51 CHMOS microcontrollers are designed to handle high-speed calculations and fast input/output operations. MCS 51 microcontrollers are typically used for high-speed event control systems. Commercial applications include modems, motor-control systems, printers, photocopiers, air conditioner control systems, disk drives, and medical instruments. The automotive industry use MCS 51 microcontrollers in engine-control systems, airbags, suspension systems, and antilock braking systems (ABS). The AT89C51 is especially well suited to applications that benefit from its processing speed and enhanced on-chip peripheral functions set, such as automotive power-train control, vehicle dynamic suspension, antilock braking, and stability control applications. Because of these critical applications, the market requires a reliable cost-effective controller with a low interrupt latency response, ability to service the high number of time and event driven integrated peripherals needed in real time applications, and a CPU with above average processing power in a single package. The financial and legal risk of having devices that operate unpredictably is very high. Once in the market, particularly in mission critical applications such as an autopilot or anti-lock braking system, mistakes are financially prohibitive. Redesign costs can run as high as a $500K, much more if the fix means 2 back annotating it across a product family that share the same core and/or peripheral design flaw. In addition, field replacements of components is extremely expensive, as the devices are typically sealed in modules with a total value several times that of the component. To mitigate these problems, it is essential that comprehensive testing of the controllers be carried out at both the component level and system level under worst case environmental and voltage conditions. This complete and thorough validation necessitates not only a well-defined process but also a proper environment and tools to facilitate and execute the mission successfully. Intel Chandler Platform Engineering group provides post silicon system validation (SV) of various micro-controllers and processors. The system validation process can be broken into three major parts. The type of the device and its application requirements determine which types of testing are performed on the device.1.2 The AT89C51 provides the following standard features4Kbytes of Flash, 128 bytes of RAM, 32 I/O lines, two 16-bittimer/counters, a five vector two-level interrupt architecture, a full duple ser-ial port, on-chip oscillatorand clock circuitry. In addition, the AT89C51 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port and interrupt sys -tem to continue functioning. The Power-down Mode saves the RAM contents but freezes the oscil–lator disabling all other chip functions until the next hardware reset.1.3Pin DescriptionVCC Supply voltage.GND Ground.Port 0:Port 0 is an 8-bit open-drain bi-directional I/O port. As an output port, each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high impedance inputs. Port 0 may also be configured to be the multiplexed low order address/data bus during accesses to external program and data memory. In this mode P0 has internal pull ups. Port 0 also receives the code bytes during Flash programming, and outputs the code bytes during program verification. External pull ups are required during program verification.Port 1:Port 1 is an 8-bit bi-directional I/O port with internal pull ups. The Port 1 output buffers can sink/so -urce four TTL inputs. When 1s are written to Port 1 pins they are pulled high by the internal pull ups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pullups. Port 1 also receives the low-order address bytes during Flash programming and verification.Port 2:Port 2 is an 8-bit bi-directional I/O port with internal pull ups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins they are pulled high by the internal pull ups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pull ups. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pull ups. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX@DPTR). In this application, it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register. Port 2 also receives the high-orderaddress bits and some control signals durin Flash programming and verification.Port 3:Port 3 is an 8-bit bi-directional I/O port with internal pull ups. The Port 3 output buffers can sink/sou -rce four TTL inputs. When 1s are written to Port 3 pins they are pulled high by the internal pull ups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (IIL) because of the pull ups.Port 3 also serves the functions of various special features of the AT89C51 as listed below:RST:Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device.ALE/PROG:Address Latch Enable output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming. In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency, and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped duri-ng each access to external Data Memory. If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.PSEN:Program Store Enable is the read strobe to external program memory. When theAT89C51 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.EA/VPP:External Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset. EA should be strapped to VCC for internal program executions. This pin alsreceives the 12-volt programming enable voltage (VPP) during Flash programming, for parts that require 12-volt VPP.XTAL1:Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2 :Output from the inverting oscillator amplifier. Oscillator CharacteristicsXTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shownin Figure 1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 2.There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed. Idle Mode In idle mode, the CPU puts itself to sleep while all the on chip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the special functions registers remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset. It should be noted that when idle is terminated by a hard ware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory.Power-down ModeIn the power-down mode, the oscillator is stopped, and the instruction that invokes power-down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values until the power-down mode is terminated. The only exit from power-down is a hardware reset. Reset redefines the SFRS but does not change the on-chip RAM. The reset should not be activated before VCC is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize. The AT89C51 code memory array is programmed byte-by byte in either programming mode. To program any nonblank byte in the on-chip Flash Memory, the entire memory must be erased using the Chip Erase Mode.2 Programming AlgorithmBefore programming the AT89C51, the address, data and control signals should be set up according to the Flash programming mode table and Figure 3 and Figure 4. To program the AT89C51, take the following steps.1. Input the desired memory location on the address lines.2. Input the appropriate data byte on the data lines. 3. Activate the correct combination of control signals. 4. Raise EA/VPP to 12V for the high-voltage programming mode. 5. Pulse ALE/PROG once to program a byte in the Flash array or the lock bits. The byte-write cycle is self-timed and typically takes nomore than 1.5 ms. Repeat steps 1 through 5, changing the address and data for the entire array or until the end of the object file is reached. Data Polling: The AT89C51 features Data Polling to indicate the end of a write cycle. During a write cycle, an attempted read of the last byte written will result in the complement of the written datum on PO.7. Once the write cycle has been completed, true data are valid on all outputs, and the next cycle may begin. Data Polling may begin any time after a write cycle has been initiated.2.1Ready/Busy:The progress of byte programming can also be monitored by the RDY/BSY output signal. P3.4 is pulled low after ALE goes high during programming to indicate BUSY. P3.4 is pulled high again when programming is done to indicate READY.Program Verify:If lock bits LB1 and LB2 have not been programmed, the programmed code data can be read back via the address and data lines for verification. The lock bits cannot be verified directly. Verification of the lock bits is achieved by observing that their features are enabled.2.2 Chip Erase:The entire Flash array is erased electrically by using the proper combination of control signals and by holding ALE/PROG low for 10 ms. The code array is written with all “1”s. The chip erase operation must be executed before the code memory can be re-programmed.2.3 Reading the Signature Bytes:The signature bytes are read by the same procedure as a normal verification of locations 030H, 031H, and 032H, except that P3.6 and P3.7 must be pulled to a logic low. The values returned areas follows.(030H) = 1EH indicates manufactured by Atmel(031H) = 51H indicates 89C51(032H) = FFH indicates 12V programming(032H) = 05H indicates 5V programming2.4 Programming InterfaceEvery code byte in the Flash array can be written and the entire array can be erased by using the appropriate combination of control signals. The write operationcycle is self timed and once initiated, will automatically time itself to completion. A microcomputer interface converts information between two forms. Outside the microcomputer the information handled by an electronic system exists as a physical signal, but within the program, it is represented numerically. The function of any interface can be broken down into a number of operations which modify the data in some way, so that the process of conversion between the external and internal forms is carried out in a number of steps. An analog-to-digital converter(ADC) is used to convert a continuously variable signal to a corresponding digital form which can take any one of a fixed number of possible binary values. If the output of the transducer does not vary continuously, no ADC is necessary. In this case the signal conditioning section must convert the incoming signal to a form which can be connected directly to the next part of the interface, the input/output section of the microcomputer itself. Output interfaces take a similar form, the obvious difference being that here the flow of information is in the opposite direction; it is passed from the program to the outside world. In this case the program may call an output subroutine which supervises the operation of the interface and performs the scaling numbers which may be needed for digital-to-analog converter(DAC). This subroutine passes information in turn to an output device which produces a corresponding electrical signal, which could be converted into analog form using a DAC. Finally the signal is conditioned(usually amplified) to a form suitable for operating an actuator. The signals used within microcomputer circuits are almost always too small to be connected directly to the outside world”and some kind of interface must be used to translate them to a more appropriate form. The design of section of interface circuits is one of the most important tasks facing the engineer wishing to apply microcomputers. We have seen that in microcomputers information is represented as discrete patterns of bits; this digital form is most useful when the microcomputer is to be connected to equipment which can only be switched on or off, where each bit might represent the state of a switch or actuator. To solve real-world problems, a microcontroller must have more than just a CPU, a program, and a data memory. In addition, it must contain hardware allowing the CPU to access information from the outside world. Once the CPU gathers information and processes the data, it must also be able to effect change on some portion of the outside world. These hardware devices, called peripherals, are the CPU’s window to the outside.The most basic form of peripheral available on microcontrollers is the generalpurpose I70 port. Each of the I/O pins can be used as either an input or an output. The function of each pin is determined by setting or clearing corresponding bits in a corresponding data direction register during the initialization stage of a program. Each output pin may be driven to either a logic one or a logic zero by using CPU instructions to pin may be viewed (or read.) by the CPU using program instructions. Some type of serial unit is included on microcontrollers to allow the CPU to communicate bit-serially with external devices. Using a bit serial format instead of bit-parallel format requires fewer I/O pins to perform the communication function, which makes it less expensive, but slower. Serial transmissions are performed either synchronously or asynchronously.3 SYSTEM GENERAL DESIGNThe hardware block diagram of the TC is shown in Fig. 1. The system hardware includes the micro controller, temperature detection circuit, keyboard control circuit, clock circuit, Display, alarm, drive circuit and external RAM. Based on the AT89C51, the DS18B20 will transfer the temperature signal detected to digital signal. And the signal is sent to the micro controller for processing. At last the temperature value is showed on the LCD 12232F. These steps are used to achieve the temperature detection. Using the keyboard interface chip HD7279 to set the temperature value, using the micro controller to keep a certain temperature, and using the LCD to show the preset value for controlling the temperature. In addition, the clock chip DS1302 is used to show time and the external RAM 6264 is used to save the monitoring data. An alarm will be given by buzzer in time if the temperature exceeds the upper and lower limit value of the temperature.3.1 HARDWARE DESIGNA. Micro controllerThe AT89C51 is a low-power, high-performance CMOS 8-bit micro controller with 4K bytes of in-system programmable Flash memory. The device is manufactured using At mel’s high-density nonvolatile memory technology and is compatible with the industry-standard 80C51 instruction set and pin out. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional nonvolatile memory programmer. By combining a versatile 8-bit CPU with in-system programmable Flash on a monolithic chip, the At mel AT89C51 is a powerful micro controller which provides a highly-flexible and cost-effective solution to manyembedded control applications. Minimum system of the micro controller is shown in Fig. 2. In order to save monitoring data, the 6264 is used as an external RAM. It is a static RAM chip, low-power with 8K bytes memory.B. Temperature Detection CircuitThe temperature sensor is the key part in the system. The Dallas DS18B20 is used, which supports the 1-Wire bus interface, and the ON-BOARD Patented is used internally. All the sensor parts and the converting circuit are integrated in integrated circuit like a transistor [1]. Its measure range is -55℃~125 ℃, and the precision between -10℃~85℃is ±0.5℃[2 ,3]. The temperature collected by the DS18B20 is transmitted in the 1-Wire bus way, and this highly raises the system anti-jamming and makes it fit in situ temperature measurement of the rugged environment [4]. There are two power supply ways for the DS18B20. The first is external power supply: the first pin of the DS18B20 is connected to the ground; the second pin serves as signal wire and the third is connected to the power. The second way is parasite power supply [5]. As the parasite power supply will lead to the complexity of the hardware circuit, the difficulty of the software control and the performance degradation of the chip, etc. But the DS18B20(s) can be connected to the I/O port of the micro controller in the external power supply way and it is more popular. Therefore the external power supply is used and the second pin is connected to the pin P1.3 of the AT89S51. Actually, if there are multipoint to be detected, the DS18B20(s) can be connected to the 1-Wire bus. But when the number is over 8, there is a concern to the driving and the more complex software design as well as the length of the 1-Wire bus. Normally it is no more than 50m. To achieve distant control, the system can be designed in to a wireless one to breakthe length limit of the 1-Wire bus [6].C. LCD CircuitThe LCD 12232F is used, which can be used to show characters, temperature value and time, and supply a friendly display interface. The 12232F is a LCD with 8192 128×32 pixels Chinese character database and 128 16×8 pixels ASCII character set graphics. It mainly consists of row drive/column drive and 128×32 full lattice LCD with the function of displaying graphics as well as 7.5×2 Chinese characters. It is in a parallel or serial mode to connect to external CPU [7]. In order to economize the hardware resource, the 12232F should be connected to the AT89S51 in serial mode with only 4 output ports used. The LCD grayscale can be changed by adjustingthe variable resistor connected the pin Vlcd of the LCD. CLK is used to transmit serial communication clock. SID is used to transmit serial data. CS is used to enable control the LCD. L+ is used to control the LCD backlight power.D. Clock CircuitThe Dallas DS18B20 is used, which is a high performance, low-power and real-time clock chip with RAM. The DS18B20 serves in the system with calendar clock and is used to monitor the time. The time data is read and processed by the AT89C51 and then displayed by the LCD. Also the time can be adjusted by the keyboard. The DS18B20 crystal oscillator is set at 32768Hz, and the recommended compensation capacitance is 6pF. The oscillator frequency is lower, so it might be possible not to connect the capacitor, and this would not make a big difference to the time precision. The backup power supply can be connected to a 3.6V rechargeable battery.E. Keyboard Control CircuitThe keyboard interface in the system is driven by the HD7279A which has a +5V single power supply and which is connected to the keyboard and display without using any active-device. According to the basic requirements and functions of the system, only 6 buttons are needed. The system's functions are set by the AT89C51 receiving the entered data. In order to save the external resistor, the 1×6 keyboard is used, and the keyboard codes are defined as: 07H, 0FH, 17H, 1FH, 27H, 2FH. The order can be read out by reading the code instruction. HD7279A is connected to the AT89S51 in serial mode and only 4 ports are need. As shown in Fig. 6, DIG0~DIG5 and DP are respectively the column lines and row line ports of the six keys which achieve keyboard monitoring, decoding and key codes identification.F. Alarm CircuitIn order to simplify the circuit and convenient debugging, a 5V automatic buzzer is used in the alarm circuit [8]. And this make the software programming simplified. As shown in Fig. 7, it is controlled by the PNP transistor 9012 whose base is connected to the pin P2.5 of the AT89C51. When the temperature exceeds the upper and lower limit value, the P2.5 output low level which makes the transistor be on and then an alarm is given by the buzzer.G. Drive CircuitA step motor is used as the drive device to control the temperature. The four-phase and eight-beat pulse distribution mode is used to drive motor and thesimple delay program is used to handle the time interval between the pulses to obtain different rotational speed. There are two output states for the step motor. One: when the temperature is over the upper value, the motor rotates reversely (to low the temperature), while when lower than the lower limit value, the motor rotates normally (to raise the temperature); besides not equals the preset value. Two: when the temperature is at somewhere between the two ends and equals the preset value, the motor stops. These steps are used to achieve the temperature control. In addition, the motor speed can also be adjusted by relative buttons. As shown in Fig. 8, the code data is input through ports A11~A8 (be P2.3~P2.0) of the AT89C51 and inverted output by the inverter 74LS04. Finally it is amplified by the power amplifier 2803A to power the motor.3.2 SOFTW ARE DESIGNAccording to the general design requirement and hardware circuit principle of the system, as well as the improvement of the program readability, transferability and the convenient debugging, the software design is modularized. The system flow mainly includes the following 8 steps: POST (Power-on self-test), system initiation, temperature detection, alarm handling, temperature control, clock chip DS18B20 operation, LCD and keyboard operation. The main program flow is shown in Fig. 9. Give a little analysis to the above 8 tasks, it is easy to find out that the last five tasks require the real time operation. But to the temperature detection it can be achieved with timer0 timing 1 second, that is to say temperature detection occurs per second. The system initiation includes global variable definition, RAM initiation, special function register initiation and peripheral equipment initiation. Global variable definition mainly finishes the interface definition of external interface chip connected to the AT89C51, and special definition of some memory units. RAM initiation mainly refers to RAM processing. For example when the system is electrified the time code will be stored in the internal unit address or the scintillation flag will be cleared. The special function register initiation includes loading the initial value of timer and opening the interrupt. For example, when the system is electrified the timer is initialized. The peripheral equipment initiation refers to set the initial value of peripheral equipment. For example, when the system is electrified, the LCD should be initialized, the start-up display should be called, the temperature conversion command should be issued firstly and the clock chip DS18B20 should also be initialized. The alarm handling is mainly the lowering and the raising of temperature to make thetemperature remain with the preset range. When the temperature is between the upper and the lower limit value, it goes to temperature control handling, that is to say the temperature need to be raised or lowered according to the preset value. By doing so make the condition temperature equal to the preset value and hence to reach the temperature target.4 CONCLUSIONThe temperature control system has the advantages of friendly human-computer interaction interface, simple hardware, low cost, high temperature control precision (error in the range of ±1 ℃), convenience and versatility, etc. It can be widely used in the occasions with -55℃to 125℃range, and there is a certain practical value.。