IC集成电路检验标准

IC 集成电路 进料检验标准

1.1 1 1 审核

AQL

1.5

S-1 S-1

期抽查依据第 检测报告或原 商自我宣告保 证书

1. 产品各部分不可有氧化、烫伤、裂痕、破损、变形、扭

曲等异常现象;

2.PIN脚必须确实牢固于内部组件与容器上,不可有变形、

扭曲、松动、脱离、电镀不良、氧化等异常现象;

3.PIN脚上不得沾有任何影响焊接与组装之异物;

4.产品本体必须完全密封于覆盖内,不可有外露现象;

1

外观 5.标识要清晰,字体不能歪斜、断字、重叠;

文件

编号

广州***电声科技股份有限公司

版本

1.1

页数

1

文件名称

IC 集成电路 进料检验标准

修改日期

版本 1.0

修订情况 全面变更

1.1

检验内容及AQL明确化

一.目的明确来料品质验收标准,规范检验动作,使检验、判定标准能达到一致性。

页次 修订

1

审核

二.适用范围适用于 IC/集成电路类 进料检验,仓库库存/样品确认/生产过程出现的不良确认检验。

三.抽样标准:MIL-STD-105E,一般检验Ⅱ; AQL值:CR=S-1 Ma=0.40 Mi=1.5 四.照明条件:光明亮度600-800LUX; 观察距离:30cm; 观察时间:小于5秒;观察角度:30°—60°; 五.W=宽 L=长 H=深度 N=数量 S=面积

检验

No.

项目

标准要求

检验工具/设备

目视

6.产品上不得沾有异物(锡渣、胶块等);

7.元件封装表面材料表面不得有因封装过程留下的沙孔;

8.PIN脚排列整齐、均匀,PIN脚无歪斜、浮、翘不良,无缺

PIN少PIN不良;

ic集成电路)检验标准

√

2、无变形、严重划伤、缺料,无表面污渍现象。

√

3、元件脚无连脚丶脱落、氧化现象。

√

4、元件脚在同一平面,无变形、偏位。

√

结构

1、按照承认书标注尺寸要求,进行尺寸检查。

承认书、试装

√

2、封装样式符合承认书及样板。

√

包装

1、根据来料单据及承认书核对来料包装方式、数量,确认来料标示清楚、完整。

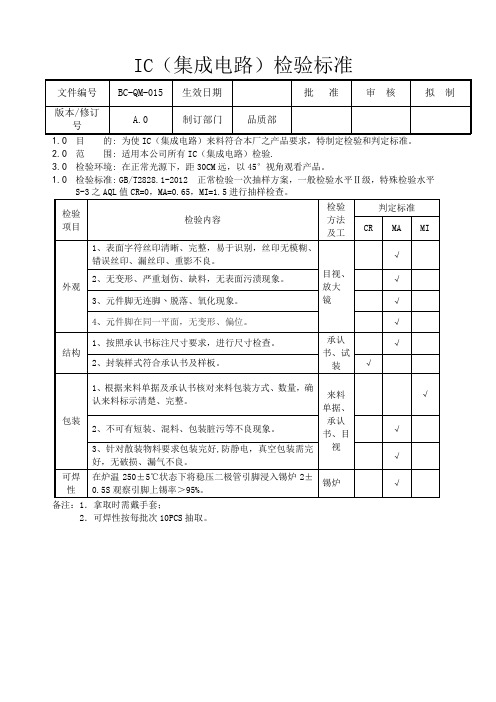

IC(集成电路)检ቤተ መጻሕፍቲ ባይዱ标准

文件编号

BC-QM-015

生效日期

批 准

审 核

拟 制

版本/修订号

A.0

制订部门

品质部

1.0目的:为使IC(集成电路)来料符合本厂之产品要求,特制定检验和判定标准。

2.0范 围:适用本公司所有IC(集成电路)检验.

3.0检验环境:在正常光源下,距30CM远,以45°视角观看产品。

4.0检验标准:GB/T2828.1-2012 正常检验一次抽样方案,一般检验水平Ⅱ级,特殊检验水平S-3之AQL值CR=0,MA=0.65,MI=1.5进行抽样检查。

检验项目

检验内容

检验方法及工具

判定标准

CR

MA

MI

外观

1、表面字符丝印清晰、完整,易于识别,丝印无模糊、错误丝印、漏丝印、重影不良。

来料单据、承认书、目视

√

2、不可有短装、混料、包装脏污等不良现象。

√

3、针对散装物料要求包装完好,防静电,真空包装需完好,无破损、漏气不良。

√

可焊性

在炉温250±5℃状态下将稳压二极管引脚浸入锡炉2±0.5S观察引脚上锡率>95%。

锡炉

√

备注:1.拿取时需戴手套;

集成电路质量检验规范

好好学习社区

更多优惠资料下载: 德信诚培训网

集成电路质量检验规范

(ISO9001-2015)

零件名称 IC (集成电路)

适用范围

所有此类物料

抽样方案

GB/T 2828.1-2012正常检查一次抽样方案,一般检查水平Ⅱ进行(除特殊指定外); AQL=0.01(CR),AQL=1.0(Ma),AQL=2.5(Mi)

检验项目 检验内容及要求 检验要

求及工具

不合格品缺陷

分类 备注/ 抽样水平 CR Ma Mi 包装/标识

1、检查包装及料盘外观,应无破损、变形、淋湿、散乱等现象;

目测

★

2、盘装编带物料应符合要求,无变形、破损、脱胶等现象;其余包装以不伤物料本体为原

则。

目测 ★

3、包装箱上应有物料码、厂家名称、型号、生产日期等标识;

目测 ★ 4、包装内实物应与标识内容一致; 目测 ★ 5、有无环保标识(GREEN PRODUCT 、RoSH 、无铅等)。

目测

★

外观

1、检查元件外观是否有变形、裂纹、缺损等不良现象;

目测 ★ 特殊S-2

2、检查元件端引脚镀层是否完整,引脚表面

应平滑、氧化、脏污、共面性等不良现象; 目测/

显微镜 ★ 特殊S-2 3、元件上标识的规格应与规格书要求一致 目测 ★ 特殊S-2 4、元件外观不能有脏污;

目测 ★ 特殊S-2 尺寸 元器件的封装尺寸符合封装要求,若不能辨别则用游标卡尺或试装检验其尺寸。

目测/ 卡尺

★ 特殊S-2 参数/性

试装在样品上测试其产品各性能是否符合要

样品/ ★

特殊S-2。

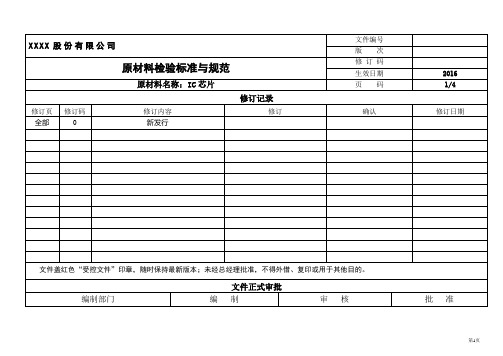

IC芯片检验标准与规范

文件编号

版 次

原材料检验标准与规范

修 订 码

生效日期

2016

原材料名称:IC芯片

页 码

2/4

1.引用标准

GB2828.1-2003《逐批检验计数抽样程序及抽样表(适用于连续批的检验)

2.合格质量充收水准

1. 抽样方案:根据GB2828.1-2003一般检验Ⅱ级水平(LEVEL)及正常检验一次抽样方案。

2 .合格质量水平(AQL):

A类不合格:严重缺点(CRI) AQL:0

B类不合格:主要缺点(MAJ) AQL:0.65

C类不合格:次要缺点(MIN) AQL:1.0

3.常规项目检验标准及检验方法

检验项目

抽样水平

检验方法

检验标准

不良描述

不良判定

检验工具

CR

MA

MI

外观

外包装

全数包装

目视全数外包装

封装形式正确,无混料,包装型号生产批号标识明确

5.检验环境

5.1在本标准中,除气候环境试验和可靠性试验外,其他试验均在下述正常大气条件下进行:

温度:10~35℃

相对湿度:35%~75%

大气压力:86~106kPB

5.2在本标准中,所有目视检验均在40W灯管下1.0米处,1.0以上视力距材料15cm检查10S.

6.相关表格

《进料检验报表》

《进料品质异常单》

√

1.0以上视力

静电环

印字清晰明确

印字模糊不清晰

√

XXXX股份有限公司

文件编号

版 次

原材料检验标准与规范

修 订 码

生效日期

2016

原材料名称:IC芯片

IC(集成电路)来料检验规范

IC(集成电路)检验规范

文件编号:TT-WI-Q-012

版本:1.0

日期:2004-2-15

B、解码板上的解码IC,应注意:2声使用AE、EE、CE;5.1声道使用BE、FE、DE。微码:29F800供电为5V;29L800T 29LV800供电为3.3V(具体情况请参照联络单。

三、检验工具:目视,特别情况下进行测试

四、附件:BOM、样板、相关技术资料、顾客要求

代用情况:1131代有1191;5654代用5954;5608代用6208;1196代用8746、8714、8725、8726可同时代用,内存A43L0161AV-7S不良率较高。

C、庆德IC经常出现有氧化和用错料现象,应特别注意字母HC、LC不可代用(例:74HC123和74LC123)。有的IC丝印型号一样,但所用的机型不一样,它的内部程序是不一样,检查时一定要注意有无标识清楚,尤其是在一次来料中的几种机型时,一定弄清楚并知会品管课相关人员,插件IC一定要试装,另:庆德发料曾打错IC型号,导致领错IC,检查时要以BOM单为准。IC上的每一个数字和字母都是非常重要的,一旦发现有不同的现象,要联络客户确认后才可以使用。

5、IC锡面、接脚间不得有连脚、凹陷损坏,锡面不得有污物、残留杂物、氧化等现象。

6、检查切脚、弯脚,不得有断脚、裂脚情形。

7、如果客户有特别要求则要测试IC的功能

10、注意IC的供电电压与丝印有上锡现象。

A、曾有客户提供的IC出现过引脚氧化和引脚撞弯及使用旧IC(旧的不良率高)现象,主要原因是包装问题(因包装IC的塑料管过大,在运输过程中造成重叠,撞弯IC脚),对管装IC要重点检查。

IC检验标准

检验

项目

接收标准

检验

方法及工具

缺陷描述

缺陷等级

致命(CR)

严重(MA)

轻微(MI)

1

包装

包装必须有标识,外标识与实物一致。

目视

外标识与实物不一致。

√

包装箱不能有破损、脏污现象。

包装箱有破损、脏污现象。

√

同一个规格型号不能有混料现象。

同一个规格型号混有其它规格型号。

√

4

外观

本体无变形、破损、污迹现象。

ic检验标准文件名称ic检验标准生效日期页码1of1使用状态文件编号版本a0审核拟定目的确保本公司电子元器件ic品质符合客户要求

IC检验标准

文件名称

IC检验标准

生效日期

2008 - 7 - 10

页码

1 of 1

使用状态

试用版

文件编号

HW – PZ – WI – 026

版本

A / 0

审核

拟定

陈愈发

目的

确保本公司电子元器件---IC品质符合客户要求。

范围

适应于电子元器件---IC进料入库检验。

抽样标准

MIL-STD-105E单次Ⅱ级正常检验;CR=0;MA=1.0;MI=2.5。

检验环境

在正常光源条件下,距离30cm远检验,以及适宜的角度检验产品。

参照标准

1、GB / T2828.1-2003逐批检查计数抽样及抽样表。

目视

本体有变形、破损、污迹现象。

√

引脚不能有弯曲成螺旋状、折痕现象。

引脚有弯曲成螺旋状、折痕现象。

√

引脚无断裂现象。

引脚有断裂现象。√引无氧化、吃锡良好。引脚有氧化、吃锡不良。

IC(集成电路)进料检验规范

检验依据

缺陷类别

检验方法/工具

1

外观 3.元件脚无连脚丶脱落、氧化现象 4.元件脚在同一平面,无变形丶偏位。 1.按照图纸/承认书标注尺寸要求,进行尺寸检查;

图纸/承认书

MA

目视/显微镜

2

结构/尺寸 2.封装样式符合承认样板和图纸。

图纸/承认书 /样板

MA CR MA

目视/ 卡尺/千分尺

3

功能/电气性能 1.引脚可焊性: 在温度280-310℃的锡炉中浸锡3S,上锡95%以上;

WNVKWANG制作

IC(集成电路)进料检验规范

文件编号 版次 页次 日期 A0 Page 1/1 抽样标准 GB/T2828.1-2012 正常检验 一次抽样 一般检验水平Ⅱ级 CR:0 MA:0.65 MI:1.5 NO. 变更 履历 变更日期 变更内容

允收水准

NO.

检验项目

检验内容

1.表面字符丝印清晰丶完整,易于识别,丝印无模糊丶错误丝印丶漏丝印丶重影不良; 2.无变形、严重划伤、缺料,无表面污渍现象;

图纸/承认书

锡炉 (5PCS/LOT)

1.根据来料单据/图纸/承认书核对来料包装方式、数量,确认来料标示清楚丶完整; 来料单据/ 图纸/承认书

4Leabharlann 包装/标识2.不可有短装、混料、包装脏污等不良现象。 3.针对散装物料要求包装完好,防静电, 真空包装需完好,无破损丶漏气不良。

MA

目视

制作:

审核:

批准:

IC检验细则

检验方式:抽检

抽样水平:MIL-STD-105D

IL=一般Ⅱ级

设备、工具、物品

游标卡尺、小锡炉、IC烧入测试架、IC座、

检验项目

检验标准

检验方法

AQL

MA

MI

0.65

4.0

1、外观

1.外形规格、型号、丝印清晰/丝印字体不易脱落,内容符合工程样品要求.

目视法

#

2.IC脚不可断/变形/生绣.

目视法

#

3.脚脚长度符合工程图纸之要求.

用卡尺测量,结构尺寸需在允许公差内.

.

#

3.功能

每批来料抽取3-5PCS送开发部委托测试.需能正常烧入规定的程式.(适用于可烧IC)

将IC插入测试插座,将烧入设备与PC连接好,把相应程序烤入IC内.

#

IC的控制功能须符合规格要求(适用于有配套IC座的)

将IC插入IC插座与测试架连接好.然后将IC插入IC插座,测试该IC所控制的功能是否正常.

#

4.可焊性

IC引脚需能良好的上锡,不可出现上锡难或不上锡等不良.(焊锡覆盖面积达95%以上)

根据规格要求设置小锡炉的温度,将被测元件引脚浸入焊锡中3~4秒,保持引脚根部距离锡面2~4mm,用目视法看其锡层附着情况。

(每批抽取3-5PCS)。

#

注意事项:*抽检前,应对器件外包装进行检查,外包装应完整(除散装件外),无明显破损现象,并有规格、数量标识,且规格与实物相符,从承认供应商处采购,否则为不合格。

*一些限于本司设备无法测试的邦定IC由供应商定期提供检测报告.

IC集成电路进料检验标准

形、扭曲、松动、脱离、电镀不良、氧化等异常现象;

3.PIN脚上不得沾有任何影响焊接与组装之异物;

4.产品本体必须完全密封于覆盖内,不可有外露现象;

1

外观

5.标识要清晰,字体不能歪斜、断字、重叠; 6.产品上不得沾有异物(锡渣、胶块等);

目视

0.65

7.元件封装表面材料表面不得有因封装过程留下的沙

孔;

8.PIN脚排列整齐、均匀,PIN脚无歪斜、浮、翘不良,

无缺PIN少PIN不良;

9.采自动插件之类,其零件包装方向必须一致,不可有

反向之异常现象。

2

性能 1. 各IC的功能正常;

烙铁/目视

0.40

3

结构 1. 相关尺寸必须符合承认书之规格; 尺寸

卡尺/目视

0.40

4

特性 测试

1.端子脚焊锡良好

烙铁/目视

பைடு நூலகம்

0.40

拟定:

审核:

批准:

文件 编号

版本

A/0

文件名称

IC/集成电路 进料检验标准

页数

1

修改日期

版本 A/0

修订情况 检验内容及AQL明确化

页次

1

一.目的

明确来料品质验收标准,规范检验动作,使检验、判定标准能达到一致性。

二.适用范围

适用于 IC/集成电路类 进料检验,仓库库存/样品确认/生产过程出现的不良确认检验

。

三.抽样标准:MIL-STD-105E,一般检验Ⅱ; AQL值:CR=0 Ma=0.40 Mi=0.65

四.照明条件:光明亮度600-800LUX; 观察距离:30cm; 观察时间:小于5秒;观察角度:30°—60°;

集成电路的质量标准及检验方法

集成电路的质量标准及检验方法集成电路(Integrated Circuit,简称IC)是由数百个或数千个微弱的电子元件(如二极管、晶体管、电阻等)和配套的被联系在一起的导线、测量电流、电压等元器件构成的微电子器件。

IC的质量标准及检验方法对于保证产品的质量与性能至关重要。

下面将详细介绍IC的质量标准及检验方法。

首先,IC的质量标准应包含以下几个方面:1. 尺寸标准:对于IC的外观尺寸、引脚位置、引脚间距等进行明确的规定。

2. 电气性能标准:包括电气参数、工作电压范围、功耗等。

3. 可靠性标准:要求IC在规定的环境条件下具有良好的耐用性,包括温度、湿度、抗辐射等。

4. 效率标准:IC应具有较高的性能效率,包括信号放大倍数、功耗效率等。

5. 一致性标准:IC的生产批次之间的差异应控制在一定的范围内,以保证产品的一致性。

接下来,IC的检验方法主要包括以下几个方面:1. 外观检验:通过目测或显微镜观察IC的外观,检查是否有划痕、裂纹、焊接不良等表面缺陷。

2. 引脚间距检验:使用千分尺或显微镜测量IC引脚之间的间距是否符合规范要求。

3. 电性能检验:使用特定的测试仪器,通过量测IC在不同电压下的电流、电压等参数来判断IC的电性能是否符合标准要求。

4. 可靠性检验:将IC置于不同的环境条件下,例如高温、低温、高湿度等,观察其性能是否受到影响以及是否满足可靠性要求。

5. 一致性检验:通过对生产批次中的多个IC进行抽样测试,对比其性能参数,判断是否在规定的一致性范围内。

6. 功能检验:根据IC所设计的功能,通过电路连接和信号输入,观察IC的功能是否正常。

总结:IC作为重要的电子元件,其质量标准及检验方法直接关系到电子产品的品质与性能。

通过明确的质量标准,可以确保IC 在制造过程中符合规范要求;通过有效的检验方法,可以及时发现IC的缺陷,并采取相应措施进行修正或淘汰。

因此,合理制定和实施IC的质量标准及检验方法是保证IC产品质量的重要保证。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IC(集成电路)检验标准

文件编号

BC-QM-015

生效日期

批 准

审 核

拟 制

版本/修订号

制订部门

品质部

1.0目的:为使IC(集成电路)来料符合本厂之产品要求,特制定检验和判定标准。

2.0范 围:适用本公司所有IC(集成电路)检验.

3.0检验环境:在正常光源下,距30CM远,以45°视角观看产品。

4.0检验标准:GB/ 正常检验一次抽样方案,一般检验水平Ⅱ级,特殊检验水平S-3之AQL值CR=0,MA=,MI=进行抽样检查。

检验项目

检验内容

检验方法及工具

判定标准

CR

MA

MI

外观

1、表面字符丝印清晰、完整,易于识别,丝印无模糊、错误丝印、漏丝印、重影不良。

目视、放大镜

√

2、无变形、严重划伤、缺料,无表面污渍现象。

√

3、针对散装物料要求包装完好,防静电,真空包装需完好,无破损、漏气不良。

√

可焊性

在炉温250±5℃状态下将稳压二极管引脚浸入锡炉2±观察引脚上锡率>95%。

锡炉

√

备注:1.拿取时需戴手套;

2.可焊性按每批次10PCS抽取。

√

3、元件脚无连脚丶脱落、氧化现象。

√

4、元件脚在同一平面,无变形、偏位。

√

结构

1、按照承认书标注尺寸要求,进行尺寸检查。

承认书、试装

√

2、封装样式符合承认书及样板。

√

包装

1、根据来料单据及承认书核对来料包装方式、数量,确认来料标示清楚、完整。

来料单据、承认书、目视

√

2、不可有短装、混料、包装脏污等不良现象。