基于DSP+Builder的时滞混沌系统数字电路设计研究

混沌系统的电路设计与仿真

V(y)

200ms V(z)

Time

5.0V

400ms 500ms

2.5V

0V

0Hz

0.5KHz

V(x)

1.0KHz Frequency

1.5KHz 2.0KHz

2.0V 0V

0V

-2.0V

-2.0V V(z)

0V V(x)

2.0V

-2.0V V(y)

0V V(x)

电路仿真结果

2.0V

报告要求

1. 设计目的(主要介绍混沌的一些基本特征、应 用等,自己查资料充实)。

y 2800(x) 1000xz 100y

参数确定

x 1 x 1 ( y) R1C1 R4C1

y 1 (x) 1 xz 1 y

R8C2

10R6C2

RR10C3

R9C3

x 1000x 1000( y) y 2800(x) 1000xz 100y z 1000(x) y (800/ 3)z

x 10x 10y y 28x 10xz y z 10xy (8 / 3)z

作时间变换尺度后的系统方 程,变换系数0 =100

x 1000x 1000( y)

y 2800(x) 1000xz 100y

z 1000(x) y (800/ 3)z

方程实现

x 1000x 1000( y)

设计举例 (Lorenz系统)

x ax ay y cx xz y z xy bz

3. Matlab仿真

function dx=lorenz(t,x) %定义子函数

a=10; b=8/3;c=28;

%系统参数

%*****************************************

基于DSP Builder的DDS数字系统设计与实现

MAT L A B的 S i mu l i n k系统级 工具 与 Qu a r t u s I I 设计 工具组合 在 一起 来设计 DDS数 字 系统 ,最终 实现

输 出频 率 可调 , 调频 范 围为 1 ~1 8 MHz 的 高精 度 DDS 数 字 系统 。

【 关键词 】  ̄ DD S ; D S P B u i l d e r ; MA T L A B; Q u a r t u s I I ;

用 于 建立 图形 模 块 并 能对其 进 行 仿 频率合成技术 , 是 一 种 新 型 的频 率 合 成 技 术 , 其 电路 的一 个 组成 部分 , 系 统 具有 较 高 的频 率分 辨 率 , 可 以实现 快 速 的频 率 切 真 。D S P B u i l d e r 作为 S i mu l i n k的一 个 控制 字 。每经 过 一 个

时钟 周 期 , 相位 累加 器 的值 递增 K。根 据 D D S基 本 结 构, 若f c 为 时钟 频 率 , f 0为输 出频率 , 则[ 3 卅:

f o= 半 / 2

D S P B u i l d e r 是 Ah e r a公 司 推 出 的一 种 基 于 F P —

换, 并 且 在 频 率 改 变 时 能 够 保 持 相位 的 连续 , 很 容 易 F P G A设 计 D S P系 统 完 全 可 以通 过 S i m u l i n k的 图 形

实现频 率 、 相位 和 幅度 的数 控 调制 。

界 面进 行 建模 、 系统 级 仿 真 , 设计 模 型还 可 以直 接 转

【 摘 要】 : 直接数 字合成器( D Ds ) 是采用数字技术的一种新型频 率合成技 术。针对这个问题提 出

DSP Builder

1.说明DSP Builder的主要功能DSP Builder在算法友好的开发环境中帮助设计人员生成DSP设计硬件表征,从而缩短了DSP设计周期。

已有的MATLAB函数和Simulink模块可以和Altera DSP Builder模块以及Altera知识产权(IP)MegaCore功能相结合,将系统级设计实现和DSP 算法开发相链接。

DSP Builder支持系统、算法和硬件设计共享一个公共开发平台。

设计人员可以使用DSP Builder模块迅速生成Simulink系统建模硬件。

DSP Builder包括比特和周期精度的Simulink模块,涵盖了算法和存储功能等基本操作。

可以使用DSP Builder模型中的MegaCore功能实现复杂功能的集成。

Altera还提供DSP Builder高级模块集,这一Simulink库实现了时序驱动的Simulink综合。

Altera MegaCore是高级参数化IP功能,例如有限冲击响应(FIR)滤波器和快速傅立叶变换(FFT)等,经过配置能够迅速方便的达到系统性能要求。

MegaCore功能支持Altera的IP评估特性,使您在购买许可之前,便可以验证功能及其时序。

Altera IP MegaStore网站上为DSP Builder和IP评估流程提供DSP IP完整介绍DSP Builder SignalCompiler模块读取由DSP Builder和MegaCore模块构建的Simulink建模文件(.mdl),生成VHDL文件和工具命令语言(Tcl)脚本,进行综合、硬件实施和仿真。

图示为DSP Builder设计流程。

DSP Builder是一个系统级(或算法级)设计工具,它构架在多个软件工具之上,并把系统级和RTL级两个设计领域的设计工具连接起来,最大程度地发挥了两种工具的优势【10】。

DSP Builder依赖于Math Works公司的数学分析工具Matlab/Simulink,以Simulink的Blockset出现,可以在Simulink中进行图形化设计和仿真,同时又通过Signal Compiler可以把Matlab/Simulink的设计文件(.mdl)转成相应的硬件描述语言VHDL设计文件(.vhd),以及用于控制综合与编译的TCL脚本。

基于DSP Builder的四维时滞混沌系统数字电路设计与仿真

号 【 F GA指 现 场 可 编 程 门 阵 列 ( il rga l P l 。 FedP o rmme d

为对 自身参 数 扰 动 非 常敏 感 . 系统 配置 不 灵 活 、 备 运 设

行 与维 护都 比较 麻 烦 .从 而 限制 了模 拟 电路 混 沌 系统

的 实 际 应 用 现 在 多 数 算 法 都 能 在 数 字 系 统 ( 如 例

基 于 D P B i e 的 四维 时滞 混沌 系统 S ul r d 数 字 电路 设计 与 仿 真

张之 光 一 , 杨 杰 。 。 李 明

(. 1 中国 人 民解 放 军 6 7 9部 队 , 原 0 2 0 ; . 西理 工 大 学 信 息 _ 学 院 , 州 3 1 0 ; 16 太 3 10 2 江 T程 赣 4 0 0 3 中国 人 民解 放 军 6 9 2部 队 ,I I . 10  ̄J 宜宾 6 4 0 ; . 州 广 播 电 视 大学 , 州 3 10 ) t I 4 00 4 赣 赣 4 0 0

设 计 混 沌 系统 的 固有 缺 陷 . 混 沌 系统 进行 离散 化 处理 . 出基 于 DS ule 软 件 设 计 时 将 提 PB i r d 滞 混 沌 吸 引子 的 方 法 。 通过 数 字 电路 的优 化 设 计 . 数 的 合理 配 置 . 系统 的信 号 幅 度 控 制 参 该

基于DSP Builder的DDS设计

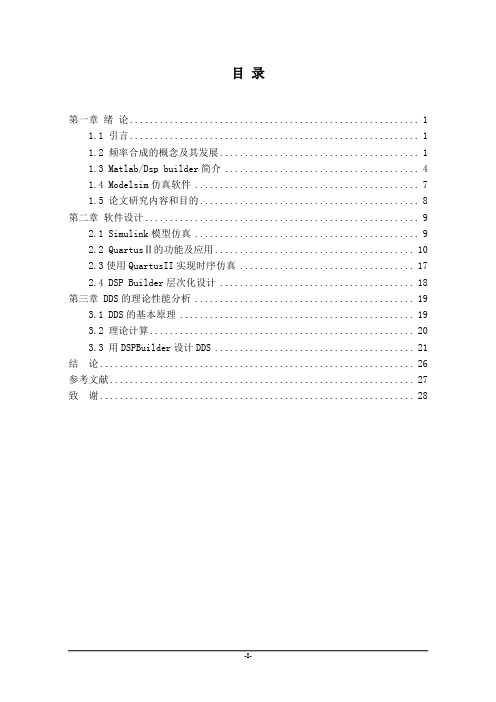

目录第一章绪论 (1)1.1 引言 (1)1.2 频率合成的概念及其发展 (1)1.3 Matlab/Dsp builder简介 (4)1.4 Modelsim仿真软件 (7)1.5 论文研究内容和目的 (8)第二章软件设计 (9)2.1 Simulink模型仿真 (9)2.2 QuartusⅡ的功能及应用 (10)2.3使用QuartusII实现时序仿真 (17)2.4 DSP Builder层次化设计 (18)第三章 DDS的理论性能分析 (19)3.1 DDS的基本原理 (19)3.2 理论计算 (20)3.3 用DSPBuilder设计DDS (21)结论 (26)参考文献 (27)致谢 (28)摘要直接数字频率合成技术(DDS)在数字通信系统中被广泛采用。

DSP Builder是Altera公司推出的一个面向DSP开发的系统级工具,本论文是在研究直接数字频率合成技术基本原理的基础上 ,利用 DSPBuilder对直接数字频率合成器进行算法级建模和硬件实现,而将QuartusⅡ作为底层设计工具置于后台,从而最大程度地发挥了这三种工具的优势。

本设计采用DSP Builder作为Simulink中的一个工具箱,使得用FPGA设计DSP系统完全可以通过Simulink的图形化界面进行,并给出了设计过程和仿真,直到把设计文件下载到FPGA中实现硬件。

关键词:直接数字频率合成DSPBuilder Simulink QuartusII FPGAABSTRACTDirect Digital Synthesis Technology (DDS) in digital communications systems that are widely used. DSP Builder is Altera has introduced a DSP-oriented development of system-level tools, in this paper is on Direct Digital Synthesis technology on the basis of basic principles, using DSPBuilder on Direct Digital Synthesis for algorithm-level modeling and hardware, And will Quartus Ⅱ design tools at the bottom as a background to maximize the advantages of these three tools. This design uses a DSP Builder Simulink in a tool box, making DSP with FPGA design system is entirely possible through the Simulink graphical interface, and gives the design process and simulation, until the design documents downloaded to the FPGA to achieve hardware.Key words: Direct Digital Synthesis DSPBuilder Simulink QuartusII FPGA第一章绪论1.1 引言1971年,美国学者J.Tierney等人撰写的“A Digital Frequency Synthesizer”-首次提出了以全数字技术,从相位概念出发直接合成所需波形的一种新合成原理。

基于DSP Builder的数字调制器的设计

基于DSP Builder的数字调制器的设计杨西西;徐建城;任自钊【期刊名称】《科学技术与工程》【年(卷),期】2011(011)002【摘要】设计使用DSP Builder实现了基于现场可编程门阵列(Field-Programmable Gates Array,FPGA)的数字调制器.首先,在Simulink中采用DSP Builder的模块建立直接数字频率合成器(Direct Digital Synthesizer,DDS)子系统模型,根据它分别建立四相相移键控(Quaternary Phase Shift Keying,QPSK)和十六进制正交幅度调制(16-Quadrature Amplitude Modulation,16QAM)系统模型;然后使用Signal Compiler工具生成与其对应的HDL设计文件和TCL脚本;最后使用Quartus II和ModelSim共同完成功能和时序仿真.仿真结果表明该设计方法正确有效,可广泛应用于数字调制技术的FPGA实现.%FPGA-based digital modulator was implemented using DSP Builder. First, modules in Simulink/ DSP Builder were used to establish DDS subsystem model, then system models of QPSK and 16QAM modulators were built based on the DDS model respectively; next Signal Compiler was used to generate their corresponding HDL design files and TCL scripts; finally Quartus Ⅱ and ModelSim co-complete functional and timing simulation.The simulation results show that this design method was correct and effective, which can be widely used in the implement of digital modulation techniques on FPGA.【总页数】5页(P355-358,362)【作者】杨西西;徐建城;任自钊【作者单位】西北工业大学电子信息学院,西安,710129;西北工业大学电子信息学院,西安,710129;西北工业大学电子信息学院,西安,710129【正文语种】中文【中图分类】TN741【相关文献】1.基于DSP Builder的数字调制器设计 [J], 许碧荣;吴祯芸2.一种基于DSP Builder的软件无线电调制器的设计与实现 [J], 孙旭;李哲英;钮文良3.基于DSP Builder的QPSK数字调制器的设计 [J], 姜维民;迟宗涛4.基于DSP Builder的OQPSK调制器设计及FPGA实现 [J], 郑希;王和明5.基于DSP Builder的数字调制器设计 [J], 许碧荣;吴祯芸因版权原因,仅展示原文概要,查看原文内容请购买。

基于DSPBuilder的混沌跳频通信系统设计

基于DSPBuilder的混沌跳频通信系统设计杨田;盛利元;张占锋【期刊名称】《计算机测量与控制》【年(卷),期】2012(20)1【摘要】根据混沌迭代方程简单,对初始值的敏感依赖性,利用DDS高频率分辨力并在频率切换时能保持相位连续的优点来产生频率髋变的载波信号,然后基于BPSK 调制解调原理,设计了一个频点数为256、起始频率为1.5MHz、频率间隔为25kHz的混沌跳频通信系统;用Matlab/Simulink下的DSPBuilder工具箱内的模块对设计进行建模并仿真,仿真结果验证了设计的正确性;此设计修改方便,只要对DSPBuilder模块库中的模块参数进行设置即可完成,加快了研究速度.%According to the simple of chaotic iterative equation and sensitive dependence on initial value, based on the advantage of the DDS' s fine frequency resolution and it could maintain the phase continuity in the switch-over of different frequency code, the carrier signal of frequency hopping is generated. And then the chaotic frequency hopping communication system based on the principle of BPSK modulation and demodulation is implemented. The system have 256 frequencies, initial frequency is 1.5MHz, frequency interval is 25KHz. By using the modules in Altera DSPHuilder toolbox under the Matlab/Simulink, the design is simulated. The simulation result shows that the design is corrective and convenient to modify, just to set the parameters of DSPBuilder modules. Accelerated the speed of research.【总页数】3页(P225-227)【作者】杨田;盛利元;张占锋【作者单位】中南大学物理科学与技术学院,湖南长沙410083;中南大学物理科学与技术学院,湖南长沙410083;中南大学物理科学与技术学院,湖南长沙410083【正文语种】中文【中图分类】TN914.4【相关文献】1.基于混沌序列的射频隐身跳频周期设计方法 [J], 杨宇晓;左瑞芹2.基于FPGA和Si4463的跳频语音通信系统设计与实现 [J], 李昌华;姬中凯;王艳峰;王平3.基于Simulink HDL Coder的跳频通信系统设计与实现 [J], 杜广超;孙慧慧;杨云升;杨志飞4.基于nRF905的无线跳频通信系统设计 [J], 林静;李新超5.基于回声状态网络优化的宽间隔混沌跳频码预测 [J], 陈建华;马玉芳因版权原因,仅展示原文概要,查看原文内容请购买。

基于DSP Builder数字信号处理器的FPGA设计

器 由 于 以顺 序 方 式 工 作 使 得 数 据 处 理 速 度 较 低, 在 功 能 重 且

构 及 应用 目标 的 修 改 方 面缺 乏 灵 活 性 。而 使用 具 有 并 行 处 理 特 性 的 F G 实现 数 字 信 号 处 理 系 统 , 有 很 强 的 实 时性 和 PA 具 灵活性 , 因此 利 用 n A 实 现 数 字 信 号 处 理 成 为 数 字 信 号 处

号 处理 器设 计 方 法 。并按 照 Maa/i u n S u dr u r sI 计 流程 , 计 了一 个 l t bSm l  ̄D PB i e/ at 1设 l i l Q u 设 2阶 兀R低 通数 字滤 波 器 。 通过 Q au ur s时序 仿 真及 嵌 入 式逻 辑 分 析仪 Sga a I 件 测 试 对 设 计 进行 了验 证 。 结果 表 明 。 设 计 的 nR 滤 波 t i l pI硬 nT 所

FPGA e i n o i ia i a r c s o s d n DSP l r d sg fd g t lsg lp o e s r ba e o n Bui de

L INe g fn E n- g a

( eate tfPyi n lc oi E gnei , ia ec esU i ri, ia 10 0 C /a D p r n o hs sadEet n ni r gWennTahr nv sy Wenn7 40 , hn ) m c rc e n e t

pa t a s ae nSg aT pI T ers ls o sted sg e l ri c re t nfn t na dg o e oma c . rci lt tb sd o in la c e I. h eut h w ein d ft orc ci n o d i p r r n e h ie s i u o n f

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

+ 上满足条件: ∞) ∞, 1 ) ( ( t , x ( t ) ) ( , 其中 μ ‖x ‖) ≤V ≤υ ‖x ‖) , 为 K类函数; μ υ d V 2 ) ( t ) V ( t )+ b ( t ) s u p V ( ) , 其 ≤a θ 3 ) t - ( t ) τ ≤θ ≤t d t( 中a ( t ) , b ( t ) 是连续函数, a ( t ) 0 , b ( t ) ≤- α< ≥0 且 b ( t ) 1 , 这里 w是常实数, 则系统( 3 ) 零 ≤w< | a ( t ) |

V ( x ( t ) ) ( V ( x ( t ) ) )+ ≤T

1 1 2 2 W( s ( ) + s ( ) ) ( 6 ) u px u px θ θ 2 3 - - τ ≤θ ≤t τ ≤θ ≤t 2t 2t 现已知

第 9卷第 4期 2 0 1 1年 1 2月 1 6 7 2 6 5 5 3 / 2 0 1 1 / 0 9 3 5 7 6 ⑷/

动力学与控制学报

J O U R N A LO FD Y N A M I C SA N DC O N T R O L

V o l . 9N o . 4 D e c . 2 0 1 1

基于 D S PB u i l d e r 的时滞混沌系统数字电路设计研究

陈志燕 朱晓锦 高志远 王划

( 上海大学机电工程与自动化学院, 上海市电站自动化技术重点实验室, 上海 2 0 0 0 7 2 )

摘要 采用一阶差分方程对时滞 L o r e n z 混沌系统进行预处理, 提出了基于 D S PB u i l d e r 的时滞混沌系统数字 电路设计方法. 此方法克服了用模拟电路设计混沌系统时, 对元器件偏差及环境影响较敏感的缺陷, 同时对 时滞混沌系统的混沌抑制问题进行了讨论, 针对系统模型描述, 设计了线性控制器, 并在系统离散化的基础 上进行了系统数字电路设计; 最后进行了数值仿真实验, 验证了所提方法的有效性和可行性. 关键词 时滞混沌, D S PB u i l d e r , 数字电路, 线性控制

x ( t )= r x ( t )- x ( t - )- x ( t ) x ( t )- u ( t ) τ 2 1 2 1 3 2 x ( t )= x ( t ) x ( t )- b x ( t - )- u ( t ) τ 3 1 2 3 3 ( 2 )

T 其中 m , r , b 为系统参数, u = ( u , u , u ) 为待定的 1 2 3

即 ( 3 )

·

n n n 其中 f : R× R × R 且f ( t , 0 , 0 ) ≡ →R 是连续函数,

m- r2 m+ r + 1 2 V ( x ( t ) ) ( k ) x- ( k ) x ≤- 1+ 2- 2- 2 1 2 b 2 12 b2 k x + x( t - )+ x ( t - )( 5 ) ( τ τ 3- ) 2 3 22 23

1 ] L o r e n z 混沌 [ 系统是典型的混沌系统, 该系 性等.

D S PB u i l d e r 是一个算法级 系统成为一种新趋势. a t l a b的一个 S i m u l i n k工具箱, 设计工具, 它作为 m 帮助设计者完成基于 F P G A器件的 D S P系统设计. 目前利用 D S PB u i l d e r 平台实现混沌数字电路产生 李云飞等人在文献[ 7 ] 中介绍了 了一些有效成果. D S Pb u i l d e r 优点, 并给出基于该平台的数字电路信

其中: 是系统( 2 ) 中时滞, = ( t ) ( 0 ( t ) ; τ τ τ ≤τ ≤τ m) u 是控制器, 因为线性控制器的简单易实现性而备 受工程人员所青睐, 本文拟设计线性控制器, 即:

T u = ( u , u , u ) = 1 2 3 T ( k x ( t ) , k x ( t ) , k x ( t ) ) 1 1 2 2 3 3

m+ r 2 2 2 ( x+ x)- ( m+ k ) x 1+ 1 2 1 2

1 2 2 b 2 2 ( x+ x( t - ) )- k x x+ τ 2 2+ ( 2 3 2 2 2

2 2 ( t - ) )- k x x τ 3 3 3

{

x ( t )= f ( t , x ( t ) , x ( t - ( t ) ) ) τ x ( t )= ( t ) , t φ ∈I 0

是系统时滞 . 从参考文献[ 6 ] 可以看 控制输入; τ 出, 通过选择不同的时滞, 系统( 2 ) 可以产生混沌 图 1是 m=1 0 , r =2 8 , b=8 / 3 , u=( u , u , 现象. 1 2

T u ) 和τ = 0 . 1 5时系统( 2 ) m a t l a b 仿真结果图. 3

解渐近稳定. 现针对上述系统( 2 ) , 进行控制器设计, 使得 混沌现象消除, 实现混沌抑制. 考虑下述正定函数 12 12 12 V ( x ( t ) )= x + x+ x 21 22 23 沿着时滞混沌系统( 2 ) 对其求导可得:

·

其中 m , r , b 为系统参数, 当 m= 1 0 , r = 2 8 , b = 8 / 3 时, 系统可以产生混沌吸引子. 文献[ 6 ] 讨论了含有时滞的 L o r e n z 系统, 其数 学模型为: x ( t )= m ( x ( t )- x ( t ) )- u ( t ) 1 2 1 1

V ( x ( t ) )= x [ m ( x ( t )- x ( t ) )- u ( t ) ]+ 1 2 1 1 x [ r x ( t ) - x ( t - ) - x ( t ) x ( t ) - u ( t ) ] + τ 2 1 2 1 3 2 x [ x ( t ) x ( t )- b x ( t - )- u ( t ) ] τ 3 1 2 3 3 ( 4 )

12 12 12 V ( x ( t ) ) ( x + x + x)+ ≤T 21 22 23 12 12 W( x ( t - )+ x ( t - ) ) τ τ 22 23

第 4期

陈志燕等: 基于 D S PB u i l d e r 的时滞混沌系统数字电路设计研究

3 5 9

因此:

·

N表示时滞 τ经离散化后在数字电路的值, 其中, 根据采样的定义知, N=τ / T ; T为采样时间. 从 Δ Δ ( 1 0 ) 式可以看出, 离散后的系统主要是几个数乘 和二次相乘运算, 计算量很小, 很适合在数字系统 中实现.

引言

非线性科学是一门研究非线性现象共性的基 础科学, 其中混沌理论是非线性科学的一个重要分 支; 近些年来, 对混沌系统的控制成为学术研究的 热点, 而如何有效地抑制有害混沌和引导有益混 随着人类对混沌 沌, 也成为控制领域研究的难点. 现象的不断探索, 对其动力学行为和基本特性有了 一定的了解: 确定性系统产生的随机性, 初值敏感

8 ] 号处理方法; 李国辉等人 [ 在D S PB u i l d e r 平台上,

e r k混沌系统的数字电路实现; 2 0 0 7 完成整数阶 J

9 ] 年吴蕾等人 [ 在研究混沌系统的基础上, 基于 D S P

, 采用一种数字差分算法和一种简易时滞环 B u i l d e r 节, 实现了 L o r e n z 吸引子和类陈氏吸引子.

1 系统模型描述

L o r e n z 系统 起 源 于 大 气 对 流 模 型, 自从发现 L o r e n z 系统以来, 人们已经对这个系统进行了大量 而深入的研究. L o r e n z 系统的动力学方程表示如下:

沌系统的研究中, 如反馈线性化方法, 自适应控制 法, 滑模控制法, 微分几何方法, 模糊控制法等, 同

3 - 5 ] 被引用到时滞混 混沌控制学的发展, 许 PB u i l d e r 平台实现时 本文针对 滞混沌 系 统 的 文 献 报 道 还 比 较 少 见. L o r e n z 时滞混沌系统, 提出基于 D S PB u i l d e r 的数 字离散化方法, 并且设计出线性控制器对时滞混沌 系统进行控制. 基于 D S PB u i l d e r 设计的数字电路 直观明了, 参数修改简单方便, 易于仿真及后续的 F P G A电路实现.

3 5 8

动 力 学 与 控 制 学 报

2 0 1 1年第 9卷

{ {

g ( t )= m ( g ( t )- g ( t ) ) 1 2 1 g ( t )= r g ( t )- g ( t )- g ( t ) g ( t ) 2 1 2 1 3 g ( t )= g ( t ) g ( t )- b g ( t ) 3 1 2 3 ( 1 )

图1 时系统( 2 ) 混沌状态图 F i g . 1 C h a o t i c a t t r a c t o r o f s y s t e m( 2 )

则

·

V ( x ( t ) ) ≤

2 线性控制器的设计

在设计控制器之前, 先介绍一个重要引理.

[ 1 1 ] 引理 1 考虑如下时滞微分系统

0 ; 时滞 τ 满足 0 ( t ) I [ t t ] , ( t ) ≤τ ≤τ τ φ m, 0= 0- m, 0 设系统的解存在, 且唯一. 如 是I 0 上的连续函数,

n n n 果存在 R × R ( t , x ( t ) ) 在(- → R 的连续函数 V

令 m r m+ r + b T 1 = m a x { ( k ) , ( k ) , ( k ) } 1+ 2 3 2 2 2 2 W 1 b = m a x ( , ) ; 2 2 2 则

[ 1 0 ] D S PB u i l d e r 在数字电路设计中发挥了越来