RCD箝位设计

RCD钳位电路分析及参数设计

RCD钳位电路分析及参数设计RCD (Residual Current Device)钳位电路是一种用于保护人身安全的电气装置。

它可以检测电流泄露,并在泄露电流超过设定值时切断电流供应,以防止电击事故的发生。

本文将对RCD钳位电路的分析及参数设计进行详细介绍。

RCD钳位电路由三个主要组成部分组成:差动变压器、电流互感线圈和电子比例装置。

差动变压器是其关键组件,主要用于检测电流泄露。

它由两个绕组组成,一个绕组由额定电流通过,称为主绕组;另一个绕组则检测差动电流,称为次级绕组。

在正常工作情况下,主绕组的电流与次级绕组的电流一致,若有电流泄露,两个绕组的电流将不再一致,从而触发电子比例装置切断电流。

参数设计是RCD钳位电路设计的重要部分,其主要目标是确定适当的额定电流和动作时间。

额定电流是指RCD钳位电路能够持续工作的最大电流。

一般来说,在家庭用电中,额定电流为30mA或100mA。

较低额定电流可以更有效地防止电击事故的发生,但也会增加虚警的可能性。

因此,在确定额定电流时,需要根据具体情况进行综合考虑。

动作时间是指RCD钳位电路切断电流的时间。

根据不同应用的要求,动作时间可以有所不同。

对于家庭用电来说,一般要求动作时间在0.1秒至0.3秒之间,以确保及时切断电流。

设计RCD钳位电路的参数还需要考虑安装环境的条件。

例如,在湿度较高的环境中,可能会增加电流泄露的风险,因此额定电流可能需要调整为较低的值。

此外,还需要考虑电流泄露的容忍程度。

对于一些特殊应用,如医疗设备,对电流泄露的容忍程度可能较低,需要更高的额定电流和更快的动作时间。

总之,RCD钳位电路是一种重要的电气安全设备,可以有效防止电击事故的发生。

在设计RCD钳位电路的时候,需要根据具体情况确定合适的额定电流和动作时间,并考虑安装环境的条件,以确保其可靠性和有效性。

RCD箝位反激变换器的设计与实现

RCD箝位反激变换器的设计与实现

摘要:论述了峰值电流控制RCD 箝位反激变换器的原理,介绍了UC3843 电流控制型脉宽调制器的各种设置,由UC3843 构成的逆变器辅助开关电源,具有电路简单、易于多路输出、过载与短路能力强、可靠性高等优点。

关键词:电流控制;RCD 箝位;反激变换器DesignandDevelopmentofRCDClampedFlybackConverter

图1RCD 箝位反激式变换器电路拓扑

1 引言

反激变换器具有电路拓扑简洁、输入输出电气隔离、电压升/降范围宽、易于多路输出等优点,因而是逆变器辅助开关电源理想的电路拓扑。

然而,反激变换器功率开关关断时由漏感储能引起的电压尖峰必须用箝位电路加以抑制。

由于RCD 箝位电路比LCD 箝位、有源箝位电路更简洁且易实现,因而RCD 箝位反激变换器在小功率变换场合更具有实用价值。

将RCD 箝位反激变换器

与峰值电流控制技术结合在一起,便可获得高性能的逆变器辅助开关电源。

本文主要论述RCD 箝位反激式变换器的原理,介绍了UC3843 电流控制型脉宽调制器的各种设置,并给出了设计实例与试验结果。

2RCD 箝位反激式变换器的原理

2.1 功率电路

采用RCD 箝位的反激变换器,如图1 所示。

当功率开关S 关断时,变压器T 漏感的储能将转移到箝位电容C 中,并在电阻R 上消耗,从而使功率开关S 关断时产生的电压尖峰得到了有效的抑制。

然而,箝位电路参数对反激变换器的性能有重要的影响。

选取不同R、C 值时,箝位电容电压波形如图2 所示。

图2(a)中,C 取值较大,C 上电压缓慢上。

反激式变换器中RCD箝位电路的设计分析

反激式变换器中RCD箝位电路的设计分析反激式变换器是一种常见的DC-DC变换器拓扑结构,具有简单、高效的特点。

在反激式变换器的设计中,RCD箝位电路扮演着非常重要的角色。

本文将从设计和分析的角度探讨RCD箝位电路在反激式变换器中的作用、设计原则以及优化方法。

首先,让我们来了解一下RCD箝位电路在反激式变换器中的作用。

反激式变换器的基本原理是利用输入电感储存能量,并通过控制开关管的开关周期实现能量的传递。

箝位电路的作用是限制开关管的电压峰值,以确保开关管能够正常工作,同时减小电压应力和电流应力,提高系统的可靠性和效率。

在设计RCD箝位电路时,首先要确定电容C、电感L和电阻R的合适取值。

理想的RCD箝位电路应该具有良好的限压、保护开关管的功能,同时要保证电路的稳定性和效率。

设计原则之一是要选择合适的电感L。

选择合适的电感值可以在箝位电路中产生合适的电感电流,以保证开关管正常工作。

一般来说,电感的电流应该在稳态工作状态下不超过其可承受的最大电流。

另外,电感值的选择还应考虑反激式变换器的输入电压、输出电压和负载条件,以及电感的尺寸和成本。

设计原则之二是要选择合适的电容C。

电容C的选择要考虑三个方面:限制开关管的电压峰值、储存能量和抑制电压尖峰。

合适的电容值可以限制开关管的电压峰值,以保护开关管不受电压应力过大的影响。

另外,电容的容量也会影响电路的能量储存和输出效率。

较大的电容值可以增加能量储存,但也会增加电路的成本和尺寸。

此外,电容的选择还需要考虑电容的ESR(壳体电阻)和ESL(壳体电感),以提高电路的性能和稳定性。

设计原则之三是要选择合适的电阻R。

电阻R的作用是限制开关管的电流,以保护开关管不受电流应力过大的影响。

合适的电阻值要根据开关管的最大电流和电路的工作条件来确定。

较小的电阻值可以减小电流应力,但也会降低电路的效率和稳定性。

因此,需要在保护开关管的同时兼顾效率和稳定性。

在实际的设计中,可以通过仿真和实验来验证和优化RCD箝位电路的设计。

RCD钳位电路分析及参数设计

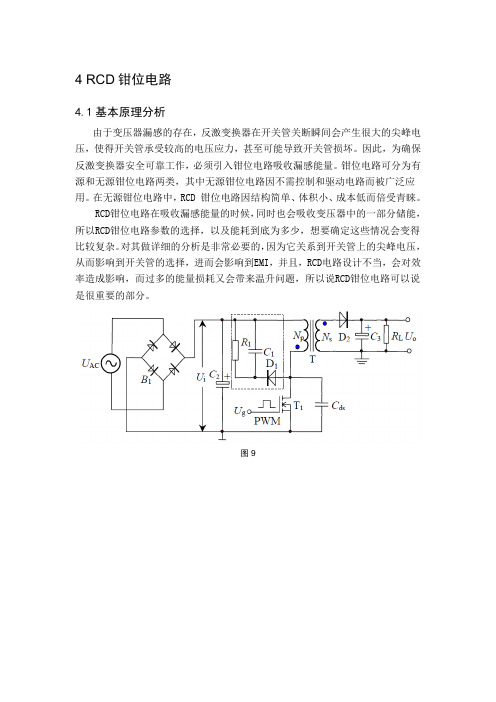

4 RCD钳位电路4.1基本原理分析由于变压器漏感的存在,反激变换器在开关管关断瞬间会产生很大的尖峰电压,使得开关管承受较高的电压应力,甚至可能导致开关管损坏。

因此,为确保反激变换器安全可靠工作,必须引入钳位电路吸收漏感能量。

钳位电路可分为有源和无源钳位电路两类,其中无源钳位电路因不需控制和驱动电路而被广泛应用。

在无源钳位电路中,RCD 钳位电路因结构简单、体积小、成本低而倍受青睐。

RCD钳位电路在吸收漏感能量的时候,同时也会吸收变压器中的一部分储能,所以RCD钳位电路参数的选择,以及能耗到底为多少,想要确定这些情况会变得比较复杂。

对其做详细的分析是非常必要的,因为它关系到开关管上的尖峰电压,从而影响到开关管的选择,进而会影响到EMI,并且,RCD电路设计不当,会对效率造成影响,而过多的能量损耗又会带来温升问题,所以说RCD钳位电路可以说是很重要的部分。

图9图10图11反激变换器RCD 钳位电路的能量转移过程可分成5 阶段,详细分析如下:1)t0-t1阶段。

开关管T1导通,二极管D1、D2因反偏而截止,钳位电容C1通过电阻R1释放能量,电容两端电压UC下降;同时,输入电压Ui加在变压器原边电感LP两端,原边电感电流ip线性上升,其储能随着增加,直到t1时刻,开关管T1关断,ip增加到最大值。

此阶段变换器一次侧的能量转移等效电路如图2(a)所示。

2)t1-t2阶段。

从t1时刻开始,开关管进入关断过程,流过开关管的电流id 开始减小并快速下降到零;同时,此阶段二极管D2仍未导通,而流过变压器原边的电流IP首先给漏源寄生电容Cds恒流充电(因LP很大),UDS快速上升(寄生电容Cds较小),变压器原边电感储存能量的很小一部份转移到Cds;直到t2时刻,UDS 上升到Ui+Uf(Uf为变压器副边向原边的反馈电压)。

此阶段变换器一次侧的能量转移等效电路如图2(b)所示,钳位电容C1继续通过电阻R1释放能量。

毕设 RCD箝位正激变换器 后期仿真

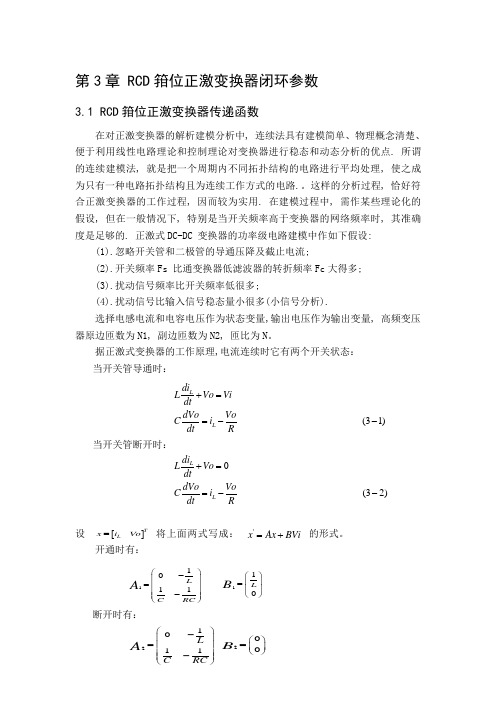

第3章 RCD 箝位正激变换器闭环参数3.1 RCD 箝位正激变换器传递函数在对正激变换器的解析建模分析中, 连续法具有建模简单、物理概念清楚、便于利用线性电路理论和控制理论对变换器进行稳态和动态分析的优点. 所谓的连续建模法, 就是把一个周期内不同拓扑结构的电路进行平均处理, 使之成为只有一种电路拓扑结构且为连续工作方式的电路.。

这样的分析过程, 恰好符合正激变换器的工作过程, 因而较为实用. 在建模过程中, 需作某些理论化的假设, 但在一般情况下, 特别是当开关频率高于变换器的网络频率时, 其准确度是足够的. 正激式DC-DC 变换器的功率级电路建模中作如下假设:(1).忽略开关管和二极管的导通压降及截止电流;(2).开关频率Fs 比通变换器低滤波器的转折频率Fc 大得多;(3).扰动信号频率比开关频率低很多;(4).扰动信号比输入信号稳态量小很多(小信号分析).选择电感电流和电容电压作为状态变量,输出电压作为输出变量, 高频变压器原边匝数为N1, 副边匝数为N2, 匝比为N 。

据正激式变换器的工作原理,电流连续时它有两个开关状态:当开关管导通时:当开关管断开时:设 将上面两式写成: 的形式。

开通时有:断开时有:(31)L L di L Vo Vi dtdVo Vo C i dt R +==--0(32)L L di L Vo dtdVo Vo C i dt R +==--[]T L x i Vo ='x Ax BVi =+11011L C RC A ⎛⎫- ⎪= ⎪ ⎪- ⎪⎝⎭110L B ⎛⎫ ⎪= ⎪⎝⎭21011L C RC A ⎛⎫- ⎪= ⎪ ⎪- ⎪⎝⎭200B ⎛⎫= ⎪⎝⎭求变量在一个周期内的平均值:A=D ·A1+(1-D)A2 B=D ·B1+(1-D )B2求得:当C=[0 1]时正激变换器的传递函数:3.2 RCD 箝位正激变换器闭环校正DC-DC 变换器只有连接反馈控制回路才能构成开关调压系统, 实现稳压或稳流. 本文设计的正激式开关电源利用开关电源集成控制器SG3525 作为反馈回路主元件,对电路进行电压闭环负反馈。

反激式变换器中RCD箝位电路设计方案工科

反激式变换器中RCD箝位电路设计方案工科反激式变换器是一种常用于电源系统中的降压变换器,它具有结构简单、成本低、效率高等优点,在电源系统中得到了广泛应用。

而RCD箝位电路则是反激式变换器中常用的一种保护电路,能有效地保护开关管和二极管,增加系统的可靠性。

本文将针对反激式变换器中RCD箝位电路的设计方案进行探讨,以期能在实际应用中提供一定的参考价值。

设计目标:设计一个能够满足工业应用需求的反激式变换器RCD箝位电路,其设计目标如下:1.保护开关管和二极管,避免过电压和过电流的损害;2.提高系统的效率;3.控制开关管的开关频率,并实现电压的稳定输出;4.降低系统的谐振噪声。

设计步骤:1.选择合适的开关管和二极管:根据输入电压和输出电流的要求,选择合适的开关管和二极管。

开关管应具有低导通电阻和低开关损耗,二极管应具有低反向恢复电压和低开关损耗。

2.确定电感和电容数值:根据输入电压、输出电压和输出电流的要求,确定合适的电感和电容数值。

电感应具有合适的饱和电流和低直流电阻,电容应具有合适的容值和低ESR。

3.设计RCD箝位电路:RCD箝位电路由一个电阻、一个电容和一个二极管组成。

其作用是在开关管关闭后提供一条反向电流通路,以保护开关管和二极管,并降低谐振噪声。

电容的选择应满足箝位电压的要求,电阻的选择应确保电容在关断期间能够完全放电。

4.控制开关管的开关频率:反激式变换器中的开关管的开关频率对整个系统的稳定性和效率有着很大的影响。

通过合理的控制开关管的开关频率,可以实现电压的稳定输出。

常见的控制方法有固定频率控制、变频控制和自适应控制等。

5.进行电路仿真和实验:根据设计的参数,进行电路的仿真和实验,验证设计的可行性和稳定性。

通过仿真和实验结果的分析,对设计进行进一步的改进和优化。

总结:通过以上设计步骤,可以设计出一个满足工业应用要求的反激式变换器RCD箝位电路。

在实际应用中,还需要根据具体的应用场景和要求来优化设计参数,以进一步提高系统的性能和可靠性。

如何设计RCD钳位电路控制原边振铃

简介反激电源是最常用的拓扑之一。

其变压器漏感常会引起原边振铃,并导致会损坏 MOSFET 的电压尖峰。

因此,通过变压器和MOSFET 组件的合理设计来控在反激电路中,一旦 MOSFET 管关断,变压器就会将原边的能量传输到副边,但漏感能量却无法被转移,这会导致电路中的杂散电容产生振铃。

漏感是产生振铃的根本原因,它占总电感量的 1% 至 5%,但却无法完全消除。

不过,我们可以通过特殊的绕线方法来降低漏感。

图 1 显示的三明治绕线法(夹心绕线法)是降低漏感的一种传统方法。

与制作三明治的过程类似,原边绕组(N P )被一分为二,然后将副边绕组(N S )依次缠绕在一半的N P 、辅助绕组和剩下的一半N P 上。

图 1:降低漏感的夹心绕线法图2显示了MOSFET 关断后的逆变电路,此时MOSFET 两端的电压由三部分组成:最大输入电压(V INMAX )、副边折射电压(V OR = n x V O )和振铃产生的峰值电压(V SPIKE )。

在输入输出电压、匝数比(n )和MOSFET 选定的情况下,应尽可能抑制V SPIKE ,以确保MOSFET 工作在应力范围之内。

工程师通常会选择制振铃非常重要。

针对如何降低漏感,RCD 钳位电路设计如何设计RCD 钳位电路控制原边振铃RCD 钳位电路来抑制振铃,因为它设计简单、成本低廉并且能够有效抑制电压尖峰。

图 2:抑制峰值电压以确保 MOS 工作在应力范围之内正确选择 RCD 钳位电路至关重要,因为不理想的电阻和电容值会增加MOSFET 的应力或电路功耗。

图 3 显示出,当 MOSFET 导通时,能量存储在励磁电感 (L M) 和漏电感 (L S) 中;当 MOSFET 关断时,L M中的能量被转移到副边,但漏感能量不会转移。

漏感会被释放以导通D1,并为 C1充电。

一旦充电电压达到 V CLAMP,则D1关断,C1通过R1放电。

图 3:MOSFET 导通/关断时的能量传输选择R 1 时,需要考虑电阻功率 1/3的降额。

RCD 钳位电路设计指南说明书

Application Note AN-4147Design Guidelines for RCD Snubber of Flyback ConvertersAbstractThis article presents some design guidelines for the RCD snubber of flyback converters. When the MOSFET turns off,a high-voltage spike occurs on the drain pin because of a res-onance between the leakage inductor (L lk ) of the main trans-former and the output capacitor (C OSS ) of the MOSFET. The excessive voltage on the drain pin may lead to an avalanche breakdown and eventually damage the MOSFET. Therefore,it is necessary to add an additional circuit to clamp the volt-age.IntroductionOne of the most simple topologies is a flyback converter. Itis derived from a buck-boost converter by replacing filter inductors with coupled inductors, such as gapped core trans-formers. When the main switch turns on, the energy is stored in the transformer as a flux form and is transferred to output during the main switch off-time. Since the transformer needs to store energy during the main switch on-time, the core should be gapped. Since flyback converters need very few components, it is a very popular topology for low- and medium-power applications such as battery chargers, adapt-ers, and DVD players.Figure 1 shows a flyback converter operating in continuousconduction mode (CCM) and discontinuous conduction mode (DCM) with several parasitic components, such as pri-mary and secondary leakage inductors, an output capacitor of MOSFET, and a junction capacitor of a secondary diode.Figure 1. Flyback Converter; (a) Configuration with Parasitic Components, (b) CCM Operation, (c) DCM OperationWhen the MOSFET turns off, the primary current (i d)charges C OSS of the MOSFET in a short time. When thevoltage across C OSS (V ds) exceeds the input voltage plusreflected output voltage (V in+nV o), the secondary diodeturns on, so that the voltage across the magnetizing inductor(L m) is clamped to nV o. There is, therefore, a resonancebetween L lk1 and C OSS with high-frequency and high-volt-age surge. This excessive voltage on the MOSFET maycause failure. In the case of the CCM operation, the second-ary diode remains turned on until the MOSFET is gated on.When the MOSFET turns on, a reverse recovery current ofthe secondary diode is added to the primary current, andthere is a large current surge on the primary current at theturn-on instance. Meanwhile, since the secondary currentruns dry before the end of one switching period in the case ofthe DCM operation, there is a resonance between L m andC OSS of the MOSFET.Snubber designThe excessive voltage due to resonance between L lk1 andC OSS should be suppressed to an acceptable level by an addi-tional circuit to protect the main switch. The RCD snubbercircuit and key waveforms are shown in Figures 2 and 3. TheRCD snubber circuit absorbs the current in the leakageinductor by turning on the snubber diode (D sn) when V dsexceeds V in+nV o. It is assumed that the snubber capacitanceis large enough that its voltage does not change during oneswitching period.When the MOSFET turns off and V ds is charged to V in+nV o,the primary current flows to C sn through the snubber diode(D sn). The secondary diode turns on at the same time. There-fore, the voltage across L lk1 is V sn-nV o. The slope of i sn is asfollows:Figure 2. Flyback Converter with RCD SnubberFigure 3. Key Waveforms of t he Flyback Converter withRCD Snubber in DCM Operationwhere i sn is the current that flows into the snubber circuit,V sn is the voltage across the snubber capacitor C sn, n is theturns ratio of the main transformer, and L lk1 is the leakageinductance of the main transformer. The time t s is obtainedby:where i peak is the peak current of the primary current.The snubber capacitor voltage (V sn) should be determined atthe minimum input voltage and full-load condition. Once V snis determined, the power dissipated in the snubber circuit atthe minimum input voltage and full-load condition isobtained by:where f s is the switching frequency of the flyback converter.V sn should be 2~2.5 times of nV o. Very small V sn results in asevere loss in the snubber circuit, as shown in the aboveequation.(1)(2)(3)On the other hand, since the power consumed in the snubber resistor (R sn) is V sn2/R sn, the resistance is obtained by:The snubber resistor with the proper rated power should be chosen based on the power loss. The maximum ripple of the snubber capacitor voltage is obtained as follows:In general, 5~10% ripple is reasonable. Therefore, the snub-ber capacitance is calculated using the above equation. When the converter is designed to operate in CCM, the peak drain current, together with the snubber capacitor voltage, decreases as the input voltage increases. The snubber capaci-tor voltage under maximum input voltage and full-load con-dition is obtained as follows:where f s is the switching frequency of the flyback converter, L lk1 is the primary-side leakage inductance, n is the turns ratio of the transformer, R sn is the snubber resistance, and I peak2 is the primary peak current at the maximum input volt-age and full-load condition. When the converter operates in CCM at the maximum input voltage and full-load condition, the I peak2 is obtained as follows:When the converter operates in DCM at the maximum input voltage and full-load condition, the I peak2 is obtained by: where P in is the input power, L m is the magnetizing induc-tance of the transformer, and V DC max is the rectified maxi-mum input voltage in DC value.Verify that the maximum value of V ds is below 90% and 80% of the rated voltage of the MOSFET (BV dss), at the transient period and steady-state period, respectively. The voltage rating of the snubber diode should be higher than BV dss. Usually an ultra-fast diode with 1A current rating is used for the snubber circuit. ExampleAn adapter using FSDM311 has following specifications: 85V ac to 265V ac input voltage range, 10W output power, 5V output voltage, and 67kHz switching frequency. When the RCD snubber uses a 1nF snubber capacitor and 480kΩ snub-ber resistor, Figure 4 shows several waveforms with 265V ac at the instance of the AC switch turn-on.Figure 4. Start-up Waveforms with 1nF Snubber Capacitor and 480kΩ Snubber ResistorIn Figures 4-7, Channel 1 through 4 stand for the drain volt-age (V ds, 200V/div), the supply voltage (V CC, 5V/div), the feedback voltage (V fb, 1V/div), and the drain current (I d, 0.2A/div), respectively. The maximum voltage stress on the internal SenseFET is around 675V, as shown in Figure 4. The voltage rating of FSDM311 is 650V, according to the datasheet. There are two reasons for the excess of the voltage ratings: the wrong transformer design and/or the wrong snubber design. Figure 5 shows the reason.Figure 5. Steady-State Waveforms with 1nF SnubberCa pacitor and 480kΩ Snubber Resistor(5)(6)(7)(8) (6)也可得此公式For the reliability, the maximum voltage stress at the steadystate should be equal to 80% of the rated voltage (650V * 0.8 = 520V). Figure 5 shows the voltage stress on the internal SenseFET is above 570V with V in = 265V ac at steady state. However, the fact that V in+nV o is around 450V (= 375V + 15 * 5V) implies the turns ratio of the transformer is 15, which is a reasonable value. Therefore, the snubber circuit should be redesigned.Let V sn be twice that of nV o, 150V, and L lk1 and i peak is 150µH and 400mA by measuring, respectively. Obtain the snubber resistance as follows:The power emission from R sn is calculated as follows:Let the maximum ripple of the snubber capacitor voltage be 10% and the snubber capacitance is obtained as follows: The results with 14kΩ (3W) and 10nF are shown in Figures 6 and 7.Figure 6. Start-up Waveforms with 10nF Snubber Capacitor and 14kΩ Snubber ResistorFigure 7. Steady-State Waveforms with 10nF Snubber Capacitor and 14kΩ Snubber ResistorThe voltage stresses on the internal SenseFET are 593V and 524V at the startup and steady state, respectively. These are around 91.2% and 80.6% of the rated voltage of FSDM311, respectively.(9)(10)(11)DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a) are intended for surgical implant into the body, or(b) support or sustain life, or(c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected tocause the failure of the life support device or system, or to affect its safety or effectiveness.by Gwan-Bon Koo/ Ph. DFPS Application Group / Fairchild Semiconductor Phone +82-32-680-1327Fax +82-32-680-1317****************************.kr。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一种有效的反激钳位电路设计方法

2007-02-01 13:39

0 引言

单端反激式开关电源具有结构简单、输入输出电气隔离、电压升/降范围宽、易于多路输出、可靠性高、造价低等优点,广泛应用于小功率场合。

然而,由于漏感影响,反激变换器功率开关管关断时将引起电压尖峰,必须用钳位电路加以抑制。

由于RCD钳位电路比有源钳位电路更简洁且易实现,因而在小功率变换场合RCD钳位更有实用价值。

1 漏感抑制

变压器的漏感是不可消除的,但可以通过合理的电路设计和绕制使之减小。

设计和绕制是否合理,对漏感的影响是很明显的。

采用合理的方法,可将漏感控制在初级电感的2%左右。

设计时应综合变压器磁芯的选择和初级匝数的确定,尽量使初级绕组可紧密绕满磁芯骨架一层或多层。

绕制时绕线要尽量分布得紧凑、均匀,这样线圈和磁路空间上更接近垂直关系,耦合效果更好。

初级和次级绕线也要尽量靠得紧密。

2 RCD钳位电路参数设计

2.1 变压器等效模型

图1为实际变压器的等效电路,励磁电感同理想变压器并联,漏感同励磁电感串联。

励磁电感能量可通过理想变压器耦合到副边,而漏感因为不耦合,能量不能传递到副边,如果不采取措施,漏感将通过寄生电容释放能量,引起电路电压过冲和振荡,影响电路工作性能,还会引起EMI问题,严重时会烧毁器件,为抑制其影响,可在变压器初级并联无源RCD钳位电路,其拓扑如图2所示。

2.2 钳位电路工作原理

引入RCD钳位电路,目的是消耗漏感能量,但不能消耗主励磁电感能量,否则会降低电路效率。

要做到这点必须对RC参数进行优化设计,下面分析其工作原理:

当S1关断时,漏感Lk释能,D导通,C上电压瞬间充上去,然后D截止,C通过R放电。

1)若C值较大,C上电压缓慢上升,副边反激过冲小,变压器能量不能迅速传递到副边,见图3(a);

2)若C值特别大,电压峰值小于副边反射电压,则钳位电容上电压将一直保持在副边反射电压附近,即钳位电阻变为死负载,一直在消耗磁芯能量,见图

3(h);

3)若RC值太小,C上电压很快会降到副边反射电压,故在St开通前,钳位电阻只将成为反激变换器的死负载,消耗变压器的能量,降低效率,见图3(c):

4)如果RC值取得比较合适,使到S1开通时,C上电压放到接近副边反射电压,到下次导通时,C上能量恰好可以释放完,见图3(d),这种情况钳位效果较好,但电容峰值电压大,器件应力高。

第2)和第3)种方式是不允许的,而第1)种方式电压变化缓慢,能量不能被迅速传递,第4)种方式电压峰值大,器件应力大。

可折衷处理,在第4)种方式基础上增大电容,降低电压峰值,同时调节R,,使到S1开通时,C上电压放到接近副边反射电压,之后RC继续放电至S1下次开通,如图3(e)所示。

2.3 参数设计

S1关断时,Lk释能给C充电,R阻值较大,可近似认为Lk与C发生串联谐振,谐振周期为TLC=2π、LkC,经过1/4谐振周期,电感电流反向,D截止,这段时间很短。

由于D存在反向恢复,电路还会有一个衰减振荡过程,而且是低损的,时间极为短暂,因此叮以忽略其影响。

总之,C充电时间是很短的,相对于整个开关周期,可以不考虑。

对于理想的钳位电路工作方式,见图3(e)。

S1关断时,漏感释能,电容快速充电至峰值Vcmax,之后RC放电。

由于充电过程非常短,可假设RC放电过程持续整个开关周期。

RC值的确定需按最小输入电压,最大负载,即最大占空比条件工作选取,否则,随着D的增大,副边导通时间也会增加,钳位电容电压波形会出现平台,钳位电路将消耗主励磁电感能量。

对图3(c)工作方式,峰值电压太大,现考虑降低Vcmax。

Vcmax只有最小值限

制,必须大于副边反射电压

可做线性化处理来设定Vcmax,如图4所示,由几何关系得

为保证S1开通时,C上电压刚好放到需满足

将(1)式代入(2)式可得

对整个周期RC放电过程分析,有

根据能量关系有

式中:Ipk/Lk释能给C的电流峰值将式(1)和式(4)代人式(5),得

结合式(3),得

电阻功率选取依据。