对称多处理机 同步与顺序一致性

VxWorks-SMP多核编程指南

VxWorks SMP多核编程指南本文摘自vxworks_kernel_programmers_guide_6.8 第24章1.介绍VxWorks SMP是风河公司为VxWorks设计的symmetric multiprocessing(SMP)系统。

它与风河公司的uniporcessor(UP)系统一样,具备实时操作系统的特性。

本章节介绍了风河VxWorks SMP系统的特点。

介绍了VxWorks SMP的配置过程、它与UP编程的区别,还有就是如何将UP代码移植为SMP代码.2.关于VxWorks SMP多核系统指的是一个系统中包含两个或两个以上的处理单元。

SMP是多核技巧中的一个,它的主要特点是一个OS运行在多个处理单元上,并且内存是共享的.另一种多核技巧是asymmetric multiprocessing(AMP)系统,即多个处理单元上运行多个OS。

(1)技术特点关于CPU与处理器的概念在很多计算机相关书籍里有所介绍。

但是,在此我们仍要对这二者在SMP系统中的区别进行详细说明。

CPU:一个CPU通常使用CPU ID、物理CPU索引、逻辑CPU索引进行标示。

一个CPU ID通常由系统固件和硬件决定。

物理CPU索引从0开始,系统从CPU0开始启动,随着CPU个数的增加,物理CPU索引也会增加。

逻辑CPU索引指的是OS实例。

例如,UP系统中逻辑CPU的索引永远是0;对于一个4个CPU的SMP系统而言,它的CPU逻辑索引永远是0到3,无论硬件系统中CPU的个数.处理器(processor):是一个包含一个CPU或多个CPU的硅晶体单元.多处理器(multiprocessor):在一个独立的硬件环境中包含两个以上的处理器。

单核处理器(uniprocessor):一个包含了一个CPU的硅晶体单元。

例如:a dual—core MPC8641D指的是一个处理器上有两个CPU;a quad-core Broadcom 1480指的是一个处理器上有四个CPU.在SMP系统上运行UP代码总会遇到问题,即使将UP代码进行了更新,也很难保证代码很好的利用了SMP系统的特性。

Linux 和对称多处理

存(1 级缓存)。

CMP 紧密耦合的本质使处理器与内存之间的物理距离很短,因此可提供最小的内存访问延迟和更高的性能。

此类架构在多线程应用程序中运行良好,该类应用程序中线程可能被分配给多个处理器以实现并行操作。

这种方法被称作线程级并行(TLP)。

由于这种多处理器架构的流行,很多供应商都生产了 CMP 设备。

表 1 列出了一些 Linux 支持的流行变种。

表 1. CMP 设备样例供应商设备说明IBM POWER4SMP,双 CPUIBM POWER5SMP,双 CPU,四个并发线程AMD AMD X2SMP,双 CPUIntel®Xeon SMP,双 CPU 或四 CPUIntel Core2 Duo SMP,双 CPUARM MPCore SMP,最多四 CPUIBM Xenon SMP,三个 Power PC CPUIBM Cell Processor不对称多处理(Asymmetric multiprocessing,ASMP),九 CPU内核配置为了在支持 SMP 的硬件上通过 Linux 使用 SMP,必须适当地配置内核。

内核配置期间必须启用CONFIG_SMP选项,以使内核感知 SMP。

通过在多 CPU 主机上运行感知 SMP 的内核,可使用proc 文件系统了解处理器的数目及类型。

首先,使用grep在 /proc 下的 cpuinfo 文件中检索处理器的数目。

如清单 1 所示,使用计数选项(-c)来统计以单词processor开头的行。

然后显示cpuinfo文件的内容。

显示的示例来自一个二芯片的 Xeon 主板。

清单 1. 使用 proc 文件系统检索 CPU 信息mtj@camus:~$ grep -c ^processor /proc/cpuinfo8mtj@camus:~$ cat /proc/cpuinfoprocessor : 0vendor_id : GenuineIntelcpu family : 15model : 6model name : Intel(R) Xeon(TM) CPU 3.73GHzstepping : 4cpu MHz : 3724.219cache size : 2048 KBphysical id : 0siblings : 4core id : 0cpu cores : 2fdiv_bug : nohlt_bug : nof00f_bug : nocoma_bug : nofpu : yesfpu_exception : yescpuid level : 6wp : yesflags : fpu vme de pse tsc msr pae mce cx8 apic sep mtrrpge mca cmov pat pse36 clflush dts acpi mmx fxsr sse sse2 ss ht tmpbe nx lm pni monitor ds_cpl est cid xtprbogomips : 7389.18...processor : 7vendor_id : GenuineIntelcpu family : 15model : 6model name : Intel(R) Xeon(TM) CPU 3.73GHzstepping : 4cpu MHz : 3724.219cache size : 2048 KBphysical id : 1siblings : 4core id : 3cpu cores : 2fdiv_bug : nohlt_bug : nof00f_bug : nocoma_bug : nofpu : yesfpu_exception : yescpuid level : 6wp : yesflags : fpu vme de pse tsc msr pae mce cx8 apic sep mtrrpge mca cmov pat pse36 clflush dts acpi mmx fxsr sse sse2 ss ht tmpbe nx lm pni monitor ds_cpl est cid xtprbogomips : 7438.33mtj@camus:~$SMP 和 Linux 内核在 Linux 2.0 的早期,SMP 支持由一个 “大锁” 组成,这个 “大锁” 对跨系统的访问进行串行化。

SMP 对称多处理

SMPSMP,英文缩写,有.对称多处理,移动智能网,系统边际电价,共享内存多处理器,SMP公司,标准管理规程等的英文简写。

目录简介平时所说的双CPU系统,实际上是对称多处理机系统中最常见的一种,通常称为2路对称多处理,它在普通AMD Athlon 64 X2的商业、家庭应用之中并没有太多实际用途,但在专业制作,如3DMaxStudio、Photoshop等软件应用中获得了非常良好的性能表现,是组建廉价工作站的良好伙伴。

随着用户应用水平的提高,只使用单个的处理器确实已经很难满足实际应用的需求,因而各服务器厂商纷纷通过采用对称多处理系统来解决这一矛盾。

在中国国内市场上这类机型的处理器一般以4个或8个为主,有少数是16个处理器。

但是一般来讲,SMP结构的机器可扩展性较差,很难做到100个以上多处理器,常规的一般是8个到16个,不过这对于多数的用户来说已经够用了。

这种机器的好处在于它的使用方式和微机或工作站的区别不大,编程的变化相对来说比较小,原来用微机工作站编写的程序如果要移植到SMP机器上使用,改动起来也相对比较容易。

SMP结构的机型可用性比较差。

因为4个或8个处理器共享一个操作系统和一个存储器,一旦操作系统出现了问题,整个机器就完全瘫痪掉了。

而且由于这个机器的可扩展性较差,不容易保护用户的投资。

但是这类机型技术比较成熟,相应的软件也比较多,因此现在中国国内市场上推出的并行机大量都是这一种。

PC服务器中最常见的对称多处理系统通常采用2路、4路、6路或8路处理器。

目前UNIX服务器可支持最多64个CPU的系统,如Sun公司的产品Enterprise10000。

SMP系统中最关键的技术是如何更好地解决多个处理器的相互通讯和协调问题。

系统结构对称多处理机的系统结构,主要指处理器、存储器、输入输出(I/O)设备三者之间的连接,它对我们更好地理解多处理机操作系统是非常必要的。

多处理器与存储器之间的连接:1、多端口存储器方式:这是最简单的连接。

并行计算(陈国良版)课后答案解析

第三章互连网络3.1 对于一颗K级二叉树(根为0级,叶为k-1级),共有N=2^k-1个节点,当推广至m-元树时(即每个非叶节点有m个子节点)时,试写出总节点数N的表达式。

答:推广至M元树时,k级M元树总结点数N的表达式为:N=1+m^1+m^2+...+m^(k-1)=(1-m^k)*1/(1-m);3.2二元胖树如图3.46所示,此时所有非根节点均有2个父节点。

如果将图中的每个椭圆均视为单个节点,并且成对节点间的多条边视为一条边,则他实际上就是一个二叉树。

试问:如果不管椭圆,只把小方块视为节点,则他从叶到根形成什么样的多级互联网络?答:8输入的完全混洗三级互联网络。

3.3 四元胖树如图3.47所示,试问:每个内节点有几个子节点和几个父节点?你知道那个机器使用了此种形式的胖树?答:每个内节点有4个子节点,2个父节点。

CM-5使用了此类胖树结构。

3.4 试构造一个N=64的立方环网络,并将其直径和节点度与N=64的超立方比较之,你的结论是什么?答:A N=64的立方环网络,为4立方环(将4维超立方每个顶点以4面体替代得到),直径d=9,节点度n=4B N=64的超立方网络,为六维超立方(将一个立方体分为8个小立方,以每个小立方作为简单立方体的节点,互联成6维超立方),直径d=6,节点度n=63.5 一个N=2^k个节点的de Bruijin 网络如图3.48。

试问:该网络的直径和对剖宽度是多少?答:N=2^k个节点的de Bruijin网络直径d=k 对剖宽带w=2^(k-1)3.6 一个N=2^n个节点的洗牌交换网络如图3.49所示。

试问:此网络节点度==?网络直径==?网络对剖宽度==?答:N=2^n个节点的洗牌交换网络,网络节点度为=2 ,网络直径=n-1 ,网络对剖宽度=43.7 一个N=(k+1)2^k个节点的蝶形网络如图3.50所示。

试问:此网络节点度=?网络直径=?网络对剖宽度=?答:N=(k+1)2^k个节点的蝶形网络,网络节点度=4 ,网络直径=2*k ,网络对剖宽度=2^k3.9 对于如下列举的网络技术,用体系结构描述,速率范围,电缆长度等填充下表中的各项。

服务器三大体系SMP、NUMA、MPP介绍

服务器三大体系SMP、NUMA、MPP介绍发表时间:2010-5-17 11:58:25 来源:网界网作者:佚名点击数:57 评论数:0 【查看评论】摘要:从系统架构来看,目前的商用服务器大体可以分为三类,即对称多处理器结构、非一致存储访问结构以及海量并行处理结构。

本文关键字:服务器SMP NUMA MPP从系统架构来看,目前的商用服务器大体可以分为三类,即对称多处理器结构(SMP:Symmetric Multi-Processor),非一致存储访问结构(NUMA:Non-Uniform Memory Access),以及海量并行处理结构(MPP:Massive Parallel Processing)。

它们的特征分别描述如下:SMP(Symmetric Multi-Processor)所谓对称多处理器结构,是指服务器中多个CPU对称工作,无主次或从属关系。

各CPU 共享相同的物理内存,每个CPU访问内存中的任何地址所需时间是相同的,因此SMP也被称为一致存储器访问结构(UMA:Uniform Memory Access)。

对SMP服务器进行扩展的方式包括增加内存、使用更快的CPU、增加CPU、扩充I/O(槽口数与总线数)以及添加更多的外部设备(通常是磁盘存储)。

SMP服务器的主要特征是共享,系统中所有资源(CPU、内存、I/O等)都是共享的。

也正是由于这种特征,导致了SMP服务器的主要问题,那就是它的扩展能力非常有限。

对于SMP服务器而言,每一个共享的环节都可能造成SMP服务器扩展时的瓶颈,而最受限制的则是内存。

由于每个CPU必须通过相同的内存总线访问相同的内存资源,因此随着CPU数量的增加,内存访问冲突将迅速增加,最终会造成CPU资源的浪费,使CPU性能的有效性大大降低。

实验证明,SMP服务器CPU利用率最好的情况是2至4个CPU。

NUMA(Non-Uniform Memory Access)由于SMP在扩展能力上的限制,人们开始探究如何进行有效地扩展从而构建大型系统的技术,NUMA就是这种努力下的结果之一。

计算机系统结构作业答案

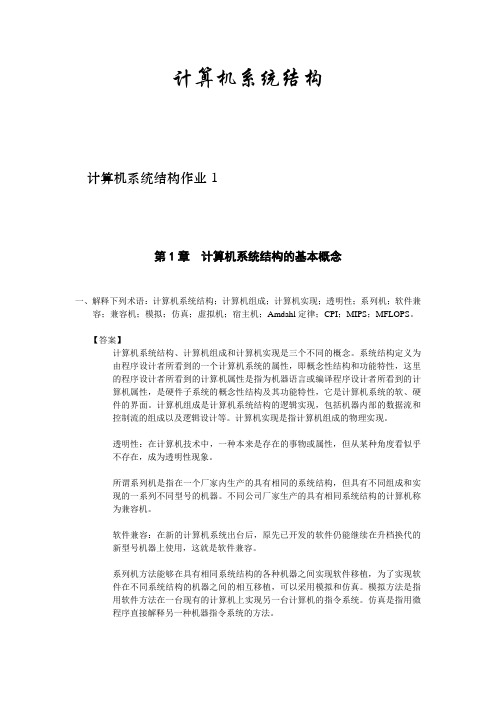

计算机系统结构计算机系统结构作业1第1章计算机系统结构的基本概念一、解释下列术语:计算机系统结构;计算机组成;计算机实现;透明性;系列机;软件兼容;兼容机;模拟;仿真;虚拟机;宿主机;Amdahl定律;CPI;MIPS;MFLOPS。

【答案】计算机系统结构、计算机组成和计算机实现是三个不同的概念。

系统结构定义为由程序设计者所看到的一个计算机系统的属性,即概念性结构和功能特性,这里的程序设计者所看到的计算机属性是指为机器语言或编译程序设计者所看到的计算机属性,是硬件子系统的概念性结构及其功能特性,它是计算机系统的软、硬件的界面。

计算机组成是计算机系统结构的逻辑实现,包括机器内部的数据流和控制流的组成以及逻辑设计等。

计算机实现是指计算机组成的物理实现。

透明性:在计算机技术中,一种本来是存在的事物或属性,但从某种角度看似乎不存在,成为透明性现象。

所谓系列机是指在一个厂家内生产的具有相同的系统结构,但具有不同组成和实现的一系列不同型号的机器。

不同公司厂家生产的具有相同系统结构的计算机称为兼容机。

软件兼容:在新的计算机系统出台后,原先已开发的软件仍能继续在升档换代的新型号机器上使用,这就是软件兼容。

系列机方法能够在具有相同系统结构的各种机器之间实现软件移植,为了实现软件在不同系统结构的机器之间的相互移植,可以采用模拟和仿真。

模拟方法是指用软件方法在一台现有的计算机上实现另一台计算机的指令系统。

仿真是指用微程序直接解释另一种机器指令系统的方法。

虚拟机是被模拟的机器;宿主机是进行模拟的机器。

Amdahl 定律:系统中某一部件由于采用某种更快的执行方式后整个系统性能的提高与这种执行方式的使用频率或占总执行时间的比例有关。

Fe=(改进前可改进部分占用的时间)/(改进前整个任务的执行时间) Se=(改进前可改进部分的执行时间)/(改进后改进部分的执行时间) 则,改进后整个系统加速比为ee e n S F F s /)1(1+-=。

多核处理器的并行算法研究及应用

多核处理器的并行算法研究及应用随着科技的飞速发展,计算机的处理速度也越来越快。

而作为现代计算机系统中的重要组成部分,处理器也在不断的发展和升级中。

多核处理器的问世,使得计算机系统的处理速度得到了大幅度提升。

对于程序开发者来说,利用多核处理器的优势,采用并行算法编写程序已经成为必备技能之一。

一、多核处理器的优势传统的单核处理器一次只能处理一个指令序列,处理速度有限。

而多核处理器中,集成了多个独立且完整的处理器,在同一时刻可以同时处理不同的指令,大幅度提升了处理速度。

多核处理器不仅可以更好地应对大数据量的计算任务,还能有效地节省处理器能量和减少系统响应时间。

多核处理器主要有两种设计方式,一种是对称多处理器(SMP),另一种是非对称多处理器(ASMP)。

对称多处理器的核心思想是:每个处理器的运行状态是相同的,都可以访问相同的内存空间。

非对称多处理器则是由多个不同类型的处理器组成的,每个处理器的运行状态都有所不同。

对于并行计算而言,对称多处理器更具有优势,应用范围也更广泛。

二、并行算法的概念并行算法,是指能够充分利用多核处理器的性能特点,通过同时执行多个计算任务,以最短的时间完成计算任务的一种算法。

在计算机科学领域中,许多经典算法都有着并行算法的实现方式。

比如排序算法、矩阵乘法等等。

并行算法的实现需要满足一定的条件:首先,任务之间应该具有独立性,任务之间不存在前后依赖关系。

其次,任务之间应该要有相同的计算量和运算方式。

最后,程序设计时需要避免不同处理器之间发生数据竞争现象,确保并行执行的正确性。

三、常见并行算法1、并行排序算法排序算法是计算机科学领域中的一类重要算法。

传统的排序算法主要是单线程执行的,无法满足大数据量的计算需求。

为了提高排序效率,研究人员开发出了各种性能优异、可扩展性强的并行排序算法。

其中,基于SMP多核处理器的算法应用范围最广,如快速排序算法、归并排序算法等。

2、并行矩阵乘法算法矩阵乘法算法也是一类常见的算法。

第四章对称多处理机系统

第四章对称多处理机系统第四章对称多处理机系统 (1)4.1引言 (2)4.2高速缓存一致性问题和存储一致性模型 (3)4.2.1高速缓存一致性问题 (3)4.2.2高速缓存一致性和存储系统一致性 (5)4.3侦听高速缓存一致性协议 (6)4.3.1基本高速缓存一致性协议 (6)4.3.2三态回写无效协议(MSI) (9)4.3.3四态回写无效协议(MESI) (11)4.3.4四态回写更新协议(Dragon) (12)4.4基本高速缓存一致性协议的实现 (14)4.4.1正确性要求 (14)4.4.2基本的高速缓存一致性设计 (15)4.5多级高速缓存 (19)4.5.1维护包含性 (20)4.5.2层次高速缓存一致性的传播 (21)*4.6分事务总线 (21)4.6.1基本设计 (22)4.6.2支持多级高速缓存 (24)4.7同步问题 (26)4.7.1基本问题 (26)4.7.2互斥操作 (27)4.7.3点到点事件同步 (30)4.7.4全局事件同步 (31)4.8实例分析:SGI Challenge (33)4.8.1 SGI处理器和主存子系统 (33)4.8.2 SGI I/O子系统 (34)4.9小结 (35)习题 (35)参考文献 (37)对称多处理机SMP(Symmetric Multiprocessor)是一类最主要的共享存储的并行计算机系统,一般利用系统总线作为互连网络实现通信,它在现今的并行服务器中几乎普遍被采用,且越来越多的出现在桌面上。

在本章中,首先讨论了基于总线的SMP机器设计的一些问题,主要包括高速缓存一致性问题、存储一致性模型、侦听高速缓存一致性协议;然后分别介绍了基于单级高速缓存和原子总线、多级高速缓存和分事务总线的高速缓存一致性协议的实现;最后,介绍了同步问题及一个具体实例SGI Challenge系统。

4.1引言对称多处理机SMP (Symmetric MultiProcessor )结构在现今的并行服务器中几乎普遍采用,并且已经越来越多的出现在桌面上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一个包含Cache,写缓存和乱序执行能力的系统是否可以 提供一个顺序一致的内存呢? 后面有更多这个方面的介绍

多个消费者的例子

Provess(R)

这些代码有什么问题吗?

多个消费者的例子

临界区: 需要被一个消费者自动执行=>加锁

Hale Waihona Puke 锁或信号量一个信号量是一个不表示否定的整数,有以下的操作: P(s):如果s>0,把s的值减1,否则等待 V(s):把s的值加1,唤醒一个等待的进程 P操作,V操作是原子操作, 不能被打断,也不可以被其他的进程抢占s资源

有什么问题吗?

互斥:第二次尝试

为了避免死锁,让进程在等待的时候放弃预留(例:进程 1把c1设置为0)

死锁是不可能的了 又会出现什么样的错误了?

这是一个最有希望的解决办法,但是,仍然有一个有界等待问题.假设, 当进程i在等待时,进程j在离开它的出口协议以后不停的再进入它的入口协 议.那么在进程i暂时性的清除它的标志的时候,很有可能进程j就反复的到 达这个循环测试.我们不能对这种情况的发生次数设置一个界限.

程序的编写者假设如果步骤3的发生在2之后,那么4就发生在1之后

顺序的前后一致:一种存储模型

"一个系统是顺序前后一致的,如果每次执行的结果 都和所有的进程在不同的顺序中执行的结果一样,并 且每个单独的进程按照程序指定的顺序执行" Leslie Lamport

一致的顺序= 顺序-保存在交叉存储器里程序,可任意交叉访问

一个互斥协议

这个协议是建立在三个共享的变量c1,c2,turn基础上的. 同样对c1,c2初始化为0

turn=i确保了只有进程I 可以等待 变量c1,c2确保了互斥

多个进程的互斥

如果当前进程被选择就等待 如果进程有一个号且就绪就等待

执行问题

SC的执行被两个问题复杂化了 无序执行的能力:

Cache: 高速缓冲存储器可以防止一个堆栈被其他的进程看到

存储防护: 串行内存访问指令 带松散的,弱内存模型的处理器(例:容许不同地址的 装入和存储重新排序)需要内存防护指令以强制内存访 问串行执行 带松散的,弱内存模型的处理器:

内存防护开销很大,然而,我们只是在需要 的时候才会这样做

使用存储防护

这是用来确保什么的?

这是用 来确保 什么的?

确保尾指针不在X存储以前更新 确保R不在X存储以前被装入.

�

生产者

消费者

一个生产者-消费者例子

程序的编写是假设了所有的命令都是顺序执行的 会出现什么样的问题了? 什么问题呢? 假设头指针在项目X保存之前被更新了? 又假设R在项目X被保存之前就被装入了了?

一个生产者-消费者例子

程序的编写者假设如果步骤3的发生在2之后,那么4就发生在1之后 程序是: 顺序:2,3,4,1 顺序:4,1,2,3

临界区 s的初始值是多少?

在临界区里的进程的最大个数. 一个信号量是一个虚拟系统在各自占有2个标志时用来发送消息的

信号量实现

信号量(互斥)可以使用顺序一致内存模型中普通的装入 和存储指令实现 然而,互斥的协议是很难设计的. 一个简单的解决方法: 原子的:读—修改—写 结构 举例:(a是一个存储器地址,R是一个寄存器)

多个消费者的例子

其他的原子 读—修改—写 结构(交换,获取&加,等等)也 可以完成P,V操作 这些代码的问题是什么? 如果进程在临界区停止或者被交换出去会怎么样?

不分块的同步

装入预留&条件存储

不分块同步

一个特定的寄存器(s)用来保存预留标志,地址和条件 装入的输出

互斥使用装入/存储

一个基于两个共享变量c1和c2的协议,初始化都是0(不 是忙状态)

对称的多处理器:

同步和顺序一致性

对称多处理器 处理机 CPU存储总线 桥 I/O总线 存储器 I/O管理器 对称 .所有的存储器和处理机的距 离是一样远 .所有是处理机可以处理所有 的I/O操作(建一个DMA 转换) I/O管理器 I/O管理器 处理机

同步

只要一个系统中存在着并行的处理机,就存在同步的问题 (甚至是在一个单处理机系统中也是这样的.) 分岔和连接:在一个并行的程序中,一个并行的 分岔 处理机可能需要等待一些事情的发生 生产者-消费者:一个消费者程序必须等待一个 P1 P2 生产者程序产生数据 连接 资源的互斥使用:操作系统必须保证在一个特定 的时刻只有一个处理机在使用特定的 资源

一致的顺序:

并行的任务有:T1,T2 共享变量:X,Y(初始化:X=0,Y=0)

A,B合理的答案将是什么???

( A, B ) ∈ {(1,11) , ( 0,10 ) , (1,10 ) , ( 0,11)}

(0,11)不是合理的

一致的顺序:

除了单处理器下程序相关约束外顺序一致性附加有额外的 存储顺序约束